JP4848153B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法Info

- Publication number

- JP4848153B2 JP4848153B2 JP2005231473A JP2005231473A JP4848153B2 JP 4848153 B2 JP4848153 B2 JP 4848153B2 JP 2005231473 A JP2005231473 A JP 2005231473A JP 2005231473 A JP2005231473 A JP 2005231473A JP 4848153 B2 JP4848153 B2 JP 4848153B2

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- semiconductor wafer

- back surface

- semiconductor

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Mechanical Treatment Of Semiconductor (AREA)

- Dicing (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

Description

(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

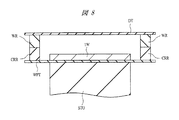

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

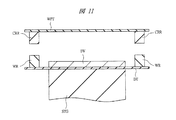

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープと、第3の主面、前記第3の主面とは反対側の第4の主面、第2の外周および第2の内周を有し、前記第2の内周が前記半導体ウエハの前記外周を取り囲む大きさのリング状の第2の搬送治具とを用意する工程、

(f)前記(d)工程後、前記第2の搬送治具の前記第3の主面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第2の搬送治具の前記第2の内周が前記半導体ウエハの前記外周を取り囲むように前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第1の搬送治具の前記第2の主面と前記第2の搬送治具の前記第4の主面とを対向させる工程、

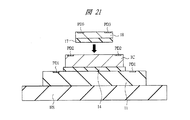

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含む。

(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープと、第3の主面、前記第3の主面とは反対側の第4の主面、第2の外周および第2の内周を有し、前記第2の内周が前記半導体ウエハの前記外周を取り囲み、前記第2の外周が前記第1の搬送治具の前記第1の内周より小さいかもしくは前記第2の内周が前記第1の搬送治具の第1の外周より大きいリング状の第2の搬送治具とを用意する工程、

(f)前記(d)工程後、前記第2の搬送治具の前記第3の主面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第2の搬送治具の前記第2の内周が前記半導体ウエハの前記外周を取り囲み、前記第2の搬送治具の前記第2の外周が前記第1の搬送治具の前記第1の内周の内側に配置されるかもしくは前記第1の搬送治具の第1の外周が前記第2の搬送治具の第2の内周の内側に配置されるように前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付する工程、

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含む。

(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープを用意する工程、

(f)前記(d)工程後、前記第1の搬送治具の前記第2の主面および前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付する工程、

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含む。

項1.(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープと、第3の主面、前記第3の主面とは反対側の第4の主面、第2の外周および第2の内周を有し、前記第2の内周が前記半導体ウエハの前記外周を取り囲む大きさのリング状の第2の搬送治具とを用意する工程、

(f)前記(d)工程後、前記第2の搬送治具の前記第3の主面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第2の搬送治具の前記第2の内周が前記半導体ウエハの前記外周を取り囲むように前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第1の搬送治具の前記第2の主面と前記第2の搬送治具の前記第4の主面とを対向させる工程、

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含むことを特徴とする半導体装置の製造方法。

項2.(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープと、第3の主面、前記第3の主面とは反対側の第4の主面、第2の外周および第2の内周を有し、前記第2の内周が前記半導体ウエハの前記外周を取り囲み、前記第2の外周が前記第1の搬送治具の前記第1の内周より小さいかもしくは前記第2の内周が前記第1の搬送治具の第1の外周より大きいリング状の第2の搬送治具とを用意する工程、

(f)前記(d)工程後、前記第2の搬送治具の前記第3の主面を前記ダイシングテープの前記第2の粘着面に貼付し、前記第2の搬送治具の前記第2の内周が前記半導体ウエハの前記外周を取り囲み、前記第2の搬送治具の前記第2の外周が前記第1の搬送治具の前記第1の内周の内側に配置されるかもしくは前記第1の搬送治具の第1の外周が前記第2の搬送治具の第2の内周の内側に配置されるように前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付する工程、

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含むことを特徴とする半導体装置の製造方法。

項3.(a)分割領域によって主面が複数のチップ領域に区画され、前記複数のチップ領域の各々に半導体素子が形成された半導体ウエハを用意する工程、

(b)前記半導体ウエハの前記主面より大きな面積を有し、前記半導体ウエハの前記主面を覆う第1の粘着面を有する保護テープと、第1の主面、前記第1の主面とは反対側の第2の主面、第1の外周および第1の内周を有し、前記第1の内周が前記半導体ウエハの外周を取り囲む大きさのリング状の第1の搬送治具とを用意する工程、

(c)前記半導体ウエハの前記主面を前記保護テープの前記第1の粘着面に貼付し、前記第1の搬送治具の前記第1の内周が前記半導体ウエハの前記外周を取り囲むように前記第1の搬送治具の前記第1の主面を前記保護テープの前記第1の粘着面に貼付する工程、

(d)前記保護テープの前記第1の粘着面に前記半導体ウエハの前記主面および前記第1の搬送治具が貼付された状況下において、前記半導体ウエハの裏面を研削する工程、

(e)前記半導体ウエハの裏面より大きな面積を有し、前記半導体ウエハの前記裏面を覆う第2の粘着面を有するダイシングテープを用意する工程、

(f)前記(d)工程後、前記第1の搬送治具の前記第2の主面および前記半導体ウエハの裏面を前記ダイシングテープの前記第2の粘着面に貼付する工程、

(g)前記(f)工程後、前記半導体ウエハの前記主面から前記保護テープを剥離する工程、

(h)前記(g)工程後、前記半導体ウエハの前記裏面に前記ダイシングテープが貼付された状況下で前記半導体ウエハを前記分割領域に沿って分割する工程、

を含むことを特徴とする半導体装置の製造方法。

項4.項1〜3のいずれか1項に記載の半導体装置の製造方法において、

前記(d)工程は、回転しつつ前記半導体ウエハの前記裏面を研削する研削手段と、回転しつつ前記半導体ウエハを保持するウエハ保持手段とを含むインフィード方式の研削装置を用いて実施し、

前記半導体ウエハと接する前記ウエハ保持手段のウエハ保持面は、前記ウエハ保持手段の回転軸が通る中心から外周へ向かう方向へ傾斜が形成されていることを特徴とする半導体装置の製造方法。

項5.項4記載の半導体装置の製造方法において、

前記ウエハ保持手段の前記回転軸は、前記(d)工程時に前記半導体ウエハの裏面と接触する前記研削手段の研削面に対して第1の角度だけ傾いていることを特徴とする半導体装置の製造方法。

項6.項1〜3のいずれか1項に記載の半導体装置の製造方法において、

前記(d)工程は、

(d1)第1の研削手段を用いて前記半導体ウエハの前記裏面を研削する工程、

(d2)前記(d1)工程後、前記第1の研削手段より前記半導体ウエハの前記裏面を細かく研削できる第2の研削手段を用いて前記半導体ウエハの前記裏面を研削する工程、

を含むことを特徴とする半導体装置の製造方法。

項7.項1〜3のいずれか1項に記載の半導体装置の製造方法において、

前記(d)工程時には、前記第1の搬送治具は、前記半導体ウエハの前記裏面より相対的に前記半導体ウエハの前記裏面を研削する研削手段から大きく離間して保持されていることを特徴とする半導体装置の製造方法。

項8.項7記載の半導体装置の製造方法において、

前記(d)工程時に前記半導体ウエハはウエハ保持手段によって保持され、

前記ウエハ保持手段は、前記半導体ウエハを吸着する第1の吸着面と、前記第1の搬送治具を吸着する第2の吸着面とを有し、

前記第2の吸着面は、前記第1の吸着面より相対的に前記研削手段から大きく離間して形成されていることを特徴とする半導体装置の製造方法。

項9.項7記載の半導体装置の製造方法において、

前記(d)工程時に前記半導体ウエハはウエハ保持手段によって保持され、

前記ウエハ保持手段は、前記半導体ウエハを吸着する第1の吸着面を有し、

前記第1の搬送治具は、第1の固定手段によって前記第1の吸着面より相対的に前記研削手段から大きく離間して保持されることを特徴とする半導体装置の製造方法。

(1)薄型化したウエハを割れおよび欠けを生じさせることなく搬送することができる。

(2)半導体パッケージの製造工程において、ウエハに割れおよび欠けを生じさせることなく薄型のチップを安価に製造することができる。

1W ウエハ

11 実装基板

14 接着材

17 接着材

18 チップ

19、20 ワイヤ

21 モールド樹脂

22 バンプ電極

23 チップ

25 接着材

26 ワイヤ

CR 切断領域(分離領域)

CRR キャリアリング(第1の搬送治具)

DT ダイシングテープ

GW グラインディングホイール(研削手段)

HS 加熱ステージ

KS1 保持面(ウエハ保持面、第1の吸着面)

KS2 保持面(第2の吸着面)

KT 保持具(第1の固定手段)

KTU 上端部

N ノッチ

PD1、PD2、PD3、PD4 パッド

RA1 回転軸

RS1 裏面

STG ステージ

US1 上面

WPT ウエハ保護テープ(保護テープ)

WR、WR2 ウエハリング(第2の搬送治具)

WSG ウエハステージ(ウエハ保持手段)

Claims (9)

- (a)分割領域によって複数のチップ領域が区画形成された第1主面、および前記第1主面とは反対側の第1裏面を有する半導体ウエハの前記第1主面に保護テープを貼り付ける工程、

(b)前記(a)工程の後、平面視においてリング状の第1搬送治具の内周が前記半導体ウエハの外周を取り囲むように前記第1搬送治具の第2主面が前記保護テープに固定された状態で、前記半導体ウエハの前記第1裏面を研削する工程、

(c)前記(b)工程の後、前記半導体ウエハの前記第1裏面側にダイシングテープを固定する工程、

(d)前記(c)工程の後、前記保護テープのうちの前記半導体ウエハの前記第1主面と対向する面とは反対側の面に前記第1搬送治具の前記内周以下の径を有するステージを押し付けることで前記半導体ウエハの前記第1裏面に前記ダイシングテープを貼り付け、前記半導体ウエハの前記第1主面と前記第1搬送治具の前記第2主面から前記保護テープを剥離する工程、

(e)前記(d)工程の後、前記半導体ウエハの前記分割領域に沿って、前記半導体ウエハを分割する工程、

を含み、

前記(c)工程では、前記半導体ウエハの前記第1裏面に前記ダイシングテープが貼り付けられていないことを特徴とする半導体装置の製造方法。 - 請求項1において、

前記半導体ウエハの前記複数のチップ領域のそれぞれには、半導体素子が形成されていることを特徴とする半導体装置の製造方法。 - 請求項1において、

前記(b)工程では、前記半導体ウエハが固定された前記保護テープをウエハステージ上に配置し、前記保護テープに固定され、前記半導体ウエハの厚さよりも厚く形成された前記第1搬送治具の前記第2裏面を前記半導体ウエハの前記第1裏面より低くし、グラインディングホイールを用いて前記半導体ウエハの前記第1裏面を研削することを特徴とする半導体装置の製造方法。 - 請求項3において、

前記(b)工程では、回転する前記グラインディングホイールを、回転する前記ウエハステージ上に配置された前記半導体ウエハの一部と前記第1搬送治具の一部を覆うように接触させることで、前記半導体ウエハの前記第1裏面を研削することを特徴とする半導体装置の製造方法。 - 請求項4において、

前記ウエハステージは、前記半導体ウエハの下側に位置する第1保持面と、前記第1保持面よりも低く、前記第1搬送治具の下側に位置する第2保持面とを有し、

前記第1搬送治具を前記第2保持面に向かって引き下げることで、前記第1搬送治具の前記第2裏面を前記半導体ウエハの前記第1裏面より低くすることを特徴とする半導体装置の製造方法。 - 請求項5において、

前記保護テープは、前記ウエハステージの前記第1保持面に吸着されていることを特徴とする半導体装置の製造方法。 - 請求項5において、

前記ウエハステージの前記第1保持面は、傾斜していることを特徴とする半導体装置の製造方法。 - 請求項1において、

前記(c)工程では、前記半導体ウエハの前記第1裏面に前記ダイシングテープが貼り付かないように、前記第1搬送治具の前記第2裏面に前記ダイシングテープを貼り付けて固定することを特徴とする半導体装置の製造方法。 - 請求項1において、

前記(c)工程では、前記半導体ウエハの前記第1裏面に前記ダイシングテープが貼り付かないように、前記ダイシングテープに固定された第2搬送治具を前記第1搬送治具の前記第2裏面に接触させることを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005231473A JP4848153B2 (ja) | 2005-08-10 | 2005-08-10 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005231473A JP4848153B2 (ja) | 2005-08-10 | 2005-08-10 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007048920A JP2007048920A (ja) | 2007-02-22 |

| JP2007048920A5 JP2007048920A5 (ja) | 2008-09-18 |

| JP4848153B2 true JP4848153B2 (ja) | 2011-12-28 |

Family

ID=37851506

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005231473A Expired - Fee Related JP4848153B2 (ja) | 2005-08-10 | 2005-08-10 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4848153B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102006000687B4 (de) | 2006-01-03 | 2010-09-09 | Thallner, Erich, Dipl.-Ing. | Kombination aus einem Träger und einem Wafer, Vorrichtung zum Trennen der Kombination und Verfahren zur Handhabung eines Trägers und eines Wafers |

| JP2007294748A (ja) * | 2006-04-26 | 2007-11-08 | Tokyo Seimitsu Co Ltd | ウェーハ搬送方法 |

| JP4729003B2 (ja) * | 2007-06-08 | 2011-07-20 | リンテック株式会社 | 脆質部材の処理方法 |

| JP5276823B2 (ja) * | 2007-10-04 | 2013-08-28 | 株式会社ディスコ | ウェーハの研削加工装置 |

| JP5272397B2 (ja) * | 2007-12-13 | 2013-08-28 | 日立化成株式会社 | 接着フィルムの貼付装置及び接着フィルムの貼付方法 |

| JP5253996B2 (ja) * | 2008-12-26 | 2013-07-31 | 株式会社ディスコ | ワーク分割方法およびテープ拡張装置 |

| EP2402981B1 (de) | 2009-03-18 | 2013-07-10 | EV Group GmbH | Vorrichtung und Verfahren zum Ablösen eines Wafers von einem Träger |

| JP5415181B2 (ja) * | 2009-08-19 | 2014-02-12 | 株式会社ディスコ | ウエーハの研削装置 |

| EP2706562A3 (de) * | 2009-09-01 | 2014-09-03 | EV Group GmbH | Vorrichtung und Verfahren zum Ablösen eines Halbleiterwafers von einem Trägersubstrat mittels Kippens eines Filmrahmens |

| EP2381464B1 (de) | 2010-04-23 | 2012-09-05 | EV Group GmbH | Vorrichtung und Verfahren zum Ablösen eines Produktsubstrats von einem Trägersubstrat |

| JP2012160515A (ja) * | 2011-01-31 | 2012-08-23 | Disco Abrasive Syst Ltd | 被加工物の加工方法 |

| JP6087565B2 (ja) * | 2012-10-03 | 2017-03-01 | 株式会社ディスコ | 研削装置および研削方法 |

| JP5580439B2 (ja) * | 2013-01-29 | 2014-08-27 | アギア システムズ インコーポレーテッド | 注入された不純物を用いて半導体ウエハを個々の半導体ダイに分離する方法 |

| JP6822857B2 (ja) * | 2017-01-17 | 2021-01-27 | 株式会社ディスコ | 搬出機構 |

| JP7404073B2 (ja) * | 2018-02-07 | 2023-12-25 | リンテック株式会社 | 半導体加工用粘着テープ |

| KR20200102612A (ko) | 2019-02-21 | 2020-09-01 | 세메스 주식회사 | 기판 처리 장치 및 기판 처리 방법 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3097619B2 (ja) * | 1997-10-02 | 2000-10-10 | 日本電気株式会社 | 電界放射冷陰極の製造方法 |

| JP4731050B2 (ja) * | 2001-06-15 | 2011-07-20 | 株式会社ディスコ | 半導体ウエーハの加工方法 |

| JP4152295B2 (ja) * | 2003-10-23 | 2008-09-17 | Necエンジニアリング株式会社 | テープ貼付装置 |

-

2005

- 2005-08-10 JP JP2005231473A patent/JP4848153B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007048920A (ja) | 2007-02-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4848153B2 (ja) | 半導体装置の製造方法 | |

| TWI284960B (en) | Manufacturing method of semiconductor device | |

| TWI420640B (zh) | 半導體封裝裝置、半導體封裝結構及其製法 | |

| JP3701542B2 (ja) | 半導体装置およびその製造方法 | |

| KR100517075B1 (ko) | 반도체 소자 제조 방법 | |

| US8394677B2 (en) | Method of fabricating semiconductor device | |

| JP5798834B2 (ja) | 半導体装置の製造方法 | |

| TWI733049B (zh) | 半導體封裝及其製造方法 | |

| US20070275543A1 (en) | Manufacturing method of a semiconductor device | |

| JP4992904B2 (ja) | 半導体装置の製造方法 | |

| US8546244B2 (en) | Method of manufacturing semiconductor device | |

| US20050208734A1 (en) | Thin flip-chip method | |

| JP2001168275A (ja) | 小型集積回路パッケージおよびその製造方法 | |

| JPWO2008038345A6 (ja) | 半導体装置の製造方法 | |

| JP2001338932A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2010010174A (ja) | 半導体装置の製造方法 | |

| US20050196901A1 (en) | Device mounting method and device transport apparatus | |

| JP4057875B2 (ja) | 半導体装置の製造方法 | |

| JP5054954B2 (ja) | 半導体装置の製造方法 | |

| JP5286303B2 (ja) | 半導体装置の製造方法 | |

| US20100289129A1 (en) | Copper plate bonding for high performance semiconductor packaging | |

| JP3621908B2 (ja) | ベアチップ実装方法および実装システム | |

| US20070114672A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2007134489A (ja) | 半導体装置の製造方法及び半導体装置 | |

| JP4483136B2 (ja) | 半導体デバイスの実装方法及び半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080806 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080806 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110301 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110427 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110920 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111017 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141021 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |