JP4707056B2 - 集積型電子部品および集積型電子部品製造方法 - Google Patents

集積型電子部品および集積型電子部品製造方法Info

- Publication number

- JP4707056B2 JP4707056B2 JP2005252596A JP2005252596A JP4707056B2 JP 4707056 B2 JP4707056 B2 JP 4707056B2 JP 2005252596 A JP2005252596 A JP 2005252596A JP 2005252596 A JP2005252596 A JP 2005252596A JP 4707056 B2 JP4707056 B2 JP 4707056B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- coil

- wiring

- integrated electronic

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title description 18

- 239000000758 substrate Substances 0.000 claims description 133

- 239000004020 conductor Substances 0.000 claims description 113

- 238000005260 corrosion Methods 0.000 claims description 16

- 230000007797 corrosion Effects 0.000 claims description 16

- 239000011347 resin Substances 0.000 claims description 12

- 229920005989 resin Polymers 0.000 claims description 12

- 238000007789 sealing Methods 0.000 claims description 11

- 238000000034 method Methods 0.000 description 63

- 238000009713 electroplating Methods 0.000 description 40

- 239000003990 capacitor Substances 0.000 description 36

- 230000008569 process Effects 0.000 description 24

- 239000000463 material Substances 0.000 description 19

- 238000012986 modification Methods 0.000 description 17

- 230000004048 modification Effects 0.000 description 17

- 239000000919 ceramic Substances 0.000 description 13

- 230000003071 parasitic effect Effects 0.000 description 13

- 230000001629 suppression Effects 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 7

- 239000004065 semiconductor Substances 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 6

- 239000003989 dielectric material Substances 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 239000000470 constituent Substances 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 229910052737 gold Inorganic materials 0.000 description 5

- 229920002577 polybenzoxazole Polymers 0.000 description 5

- 239000010453 quartz Substances 0.000 description 5

- 239000003566 sealing material Substances 0.000 description 5

- 229910052709 silver Inorganic materials 0.000 description 5

- 239000011248 coating agent Substances 0.000 description 4

- 238000000576 coating method Methods 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 238000005459 micromachining Methods 0.000 description 4

- 229920002120 photoresistant polymer Polymers 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 239000012776 electronic material Substances 0.000 description 3

- 239000007769 metal material Substances 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 229910017103 Fe—Al—O Inorganic materials 0.000 description 2

- 229910013641 LiNbO 3 Inorganic materials 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical class C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000002500 effect on skin Effects 0.000 description 2

- 230000005672 electromagnetic field Effects 0.000 description 2

- 230000005674 electromagnetic induction Effects 0.000 description 2

- 230000006698 induction Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000000696 magnetic material Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 238000000992 sputter etching Methods 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/06—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including a plurality of individual components in a non-repetitive configuration

- H01L27/0688—Integrated circuits having a three-dimensional layout

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H7/00—Multiple-port networks comprising only passive electrical elements as network components

- H03H7/38—Impedance-matching networks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F17/00—Fixed inductances of the signal type

- H01F17/0006—Printed inductances

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5227—Inductive arrangements or effects of, or between, wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/095—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00 with a principal constituent of the material being a combination of two or more materials provided in the groups H01L2924/013 - H01L2924/0715

- H01L2924/097—Glass-ceramics, e.g. devitrified glass

- H01L2924/09701—Low temperature co-fired ceramic [LTCC]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

Description

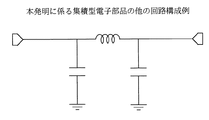

複数の受動部品と、

外部接続用の複数のパッド部と、

立体配線と、を備え、

前記複数の受動部品は、前記基板上に設けられた多段コイルインダクタを含み、当該多段コイルインダクタは、多段配置された複数のコイルを有し、且つ、隣り合うコイル導線が空隙を介して離隔し、

前記立体配線は、前記基板に接して延びる第1配線部と、前記基板から離隔して当該基板に沿って延びる第2配線部と、当該第1および第2配線部に接続する第3配線部と、を含む、集積型電子部品。

(付記2)前記多段コイルインダクタは、空隙を介して互いに離隔する複数のスパイラルコイルを有する、付記1に記載の集積型電子部品。

(付記3)前記多段コイルインダクタはソレノイドコイルまたはトロイダルコイルである、付記1に記載の集積型電子部品。

(付記4)前記基板は、半導体基板、絶縁膜が表面に形成された半導体基板、石英基板、ガラス基板、圧電基板、セラミック基板、SOI基板、SOQ基板、またはSOG基板である、付記1から3のいずれか一つに記載の集積型電子部品。

(付記5)前記複数の受動部品は、キャパシタおよび/または抵抗を含む、付記1から4のいずれか一つに記載の集積型電子部品。

(付記6)前記キャパシタは、相対向する第1電極および第2電極を有し、前記第1電極は、前記基板上に設けられ、前記第2電極は、前記基板から離隔して前記基板に沿って設けられている、付記5に記載の集積型電子部品。

(付記7)前記多段コイルインダクタにおける、前記基板に最も近いコイルは、前記基板から離隔している、付記1から6のいずれか一つに記載の集積型電子部品。

(付記8)前記多段コイルインダクタにおける、前記基板に最も近いコイルは、前記基板上にパターン形成されている、付記1から6のいずれか一つに記載の集積型電子部品。

(付記9)前記複数の受動部品は、LCRフィルタ、SAWフィルタ、FBARフィルタ、および機械共振を利用したフィルタからなる群より選択されるフィルタを含む、付記1から8のいずれか一つに記載の集積型電子部品。

(付記10)前記複数の受動部品および前記立体配線を前記基板上にて封止するための封止樹脂を更に備える、付記1から9のいずれか一つに記載の集積型電子部品。

(付記11)前記封止樹脂は、前記多段コイルインダクタにおける隣り合うコイル導線の間に入り込む部位を有する、付記10に記載の集積型電子部品。

(付記12)前記多段コイルインダクタおよび/または前記立体配線は、耐食性膜および磁性体膜から選択される膜または当該膜を含む多層膜により被覆されている部位を有する、付記1から11のいずれか一つに記載の集積型電子部品。

(付記13)前記基板は凹部を有し、前記多段コイルインダクタは当該凹部に設けられている、付記1から12のいずれか一つに記載の集積型電子部品。

(付記14)電気めっき法により下位導体部を形成する工程と、

前記下位導体部の上位に上位導体部を形成するための、開口部を有する第1レジストパターンを、前記下位導体部の一部が前記開口部にて露出するように、形成する工程と、

前記第1レジストパターンの表面、および、前記下位導体部において前記開口部にて露出する表面にわたり、シード層を形成する工程と、

開口部を有する第2レジストパターンを第1レジストパターンの上位に形成する工程と、

電気めっき法により、前記第2レジストパターンの前記開口部にて上位導体部を形成する工程と、

前記第2レジストパターンを除去する工程と、

前記シード層を除去する工程と、

前記第1レジストパターンを除去する工程と、を含む、集積型電子部品製造方法。

S 基板

10,10A,10B 多段コイルインダクタ

11,12 スパイラルコイル

13 連絡部

20 キャパシタ

21 第1電極

22 第2電極

23 誘電体層

30 立体配線

31 第1配線部

32 第2配線部

33 第3配線部

40,40A,40B,40C,40D パッド部

50 封止材

Claims (8)

- 基板と、

前記基板上に設けられ、隣り合うコイル導線が空隙を介して離隔した第1段のコイルとその上に設けられた第2段のコイルとを含むインダクタと、

前記基板の表面に接した2つの第1配線部と、前記2つの第1配線部のうち、一方の第1配線部と接続し、前記基板から離隔して当該基板に沿って延びる第2配線部と、前記一方の第1配線部および前記第2配線部を接続し、前記基板の前記表面と交差する方向に延びる第3配線部とを有し、

前記第1段のコイルおよび前記第2段のコイルは前記基板と垂直な方向で重なっており、

前記第1段のコイルの一端が前記他方の第1配線部と直接に接続され他端が前記基板の前記表面と交差する方向に延びる連結部により前記第2段のコイルの一端に接続され、前記第2段のコイルの他端が前記第2配線部に接続されている、集積型電子部品。 - 前記第1段および第2段のコイルはスパイラルコイルにより構成され、それぞれの段のコイルで電流の方向が同一である、請求項1に記載の集積型電子部品。

- 前記第1段のコイルは前記基板から離隔している、請求項1または2に記載の集積型電子部品。

- 前記第1段のコイルは前記基板上に直接形成されている、請求項1または2に記載の集積型電子部品。

- 前記第1段のコイルおよび前記第3配線部の少なくとも一部が前記基板上にて封止される封止樹脂を更に備える、請求項1から4のいずれか一つに記載の集積型電子部品。

- 前記基板は凹部を有し、前記第1段および第2段のコイルは当該凹部に設けられている、請求項1から5のいずれか一つに記載の集積型電子部品。

- 前記第1段および第2段のコイルまたは前記第1〜第3配線部には耐食性膜が形成されている、請求項1から6のいずれか一つに記載の集積型電子部品。

- 前記第1段および第2段のコイルは磁性体膜で被覆されている、請求項1から6のいずれか一つに記載の集積型電子部品。

Priority Applications (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005252596A JP4707056B2 (ja) | 2005-08-31 | 2005-08-31 | 集積型電子部品および集積型電子部品製造方法 |

| EP06254301.2A EP1760731B1 (en) | 2005-08-31 | 2006-08-16 | Integrated electronic device |

| KR1020060079679A KR100730672B1 (ko) | 2005-08-31 | 2006-08-23 | 집적형 전자 부품 및 집적형 전자 부품 제조 방법 |

| US11/509,577 US7948056B2 (en) | 2005-08-31 | 2006-08-25 | Integrated electronic device and method of making the same |

| CN2006101288079A CN1925321B (zh) | 2005-08-31 | 2006-08-30 | 集成电子器件及其制造方法 |

| US13/064,347 US8518789B2 (en) | 2005-08-31 | 2011-03-21 | Integrated electronic device and method of making the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005252596A JP4707056B2 (ja) | 2005-08-31 | 2005-08-31 | 集積型電子部品および集積型電子部品製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008137019A Division JP4795385B2 (ja) | 2008-05-26 | 2008-05-26 | 集積型電子部品 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007067236A JP2007067236A (ja) | 2007-03-15 |

| JP2007067236A5 JP2007067236A5 (ja) | 2008-07-10 |

| JP4707056B2 true JP4707056B2 (ja) | 2011-06-22 |

Family

ID=37401147

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005252596A Active JP4707056B2 (ja) | 2005-08-31 | 2005-08-31 | 集積型電子部品および集積型電子部品製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7948056B2 (ja) |

| EP (1) | EP1760731B1 (ja) |

| JP (1) | JP4707056B2 (ja) |

| KR (1) | KR100730672B1 (ja) |

| CN (1) | CN1925321B (ja) |

Families Citing this family (71)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4842052B2 (ja) | 2006-08-28 | 2011-12-21 | 富士通株式会社 | インダクタ素子および集積型電子部品 |

| GB2463806B (en) | 2007-05-08 | 2012-07-18 | Scanimetrics Inc | Ultra high speed signal transmission/reception |

| JP5090117B2 (ja) | 2007-09-28 | 2012-12-05 | 太陽誘電株式会社 | 電子部品 |

| JP5090118B2 (ja) | 2007-09-28 | 2012-12-05 | 太陽誘電株式会社 | 電子部品 |

| JP2009088161A (ja) * | 2007-09-28 | 2009-04-23 | Fujitsu Media Device Kk | 電子部品 |

| TWI397930B (zh) * | 2007-11-06 | 2013-06-01 | Via Tech Inc | 螺旋電感元件 |

| JP5172287B2 (ja) * | 2007-11-19 | 2013-03-27 | 株式会社東芝 | 集積回路装置 |

| JP5058770B2 (ja) * | 2007-12-12 | 2012-10-24 | 太陽誘電株式会社 | 電子部品 |

| KR100922551B1 (ko) * | 2007-12-26 | 2009-10-21 | 주식회사 동부하이텍 | 반도체 소자 및 그 제조방법 |

| JP5133047B2 (ja) | 2007-12-28 | 2013-01-30 | 太陽誘電株式会社 | 電子部品の製造方法 |

| JP5154262B2 (ja) * | 2008-02-26 | 2013-02-27 | 太陽誘電株式会社 | 電子部品 |

| JP5133091B2 (ja) | 2008-02-28 | 2013-01-30 | 太陽誘電株式会社 | 電子部品及びその製造方法 |

| US20090236689A1 (en) * | 2008-03-24 | 2009-09-24 | Freescale Semiconductor, Inc. | Integrated passive device and method with low cost substrate |

| JP4656196B2 (ja) | 2008-07-11 | 2011-03-23 | 株式会社村田製作所 | インダクタおよびフィルタ |

| US9599591B2 (en) | 2009-03-06 | 2017-03-21 | California Institute Of Technology | Low cost, portable sensor for molecular assays |

| US20110175602A1 (en) * | 2009-12-23 | 2011-07-21 | California Institute Of Technology | Inductors with uniform magnetic field strength in the near-field |

| US9444213B2 (en) | 2009-03-09 | 2016-09-13 | Nucurrent, Inc. | Method for manufacture of multi-layer wire structure for high efficiency wireless communication |

| US9232893B2 (en) | 2009-03-09 | 2016-01-12 | Nucurrent, Inc. | Method of operation of a multi-layer-multi-turn structure for high efficiency wireless communication |

| US9306358B2 (en) | 2009-03-09 | 2016-04-05 | Nucurrent, Inc. | Method for manufacture of multi-layer wire structure for high efficiency wireless communication |

| EP4234001A3 (en) | 2009-03-09 | 2023-10-18 | NuCurrent, Inc. | System and method for wireless power transfer in implantable medical devices |

| US9439287B2 (en) | 2009-03-09 | 2016-09-06 | Nucurrent, Inc. | Multi-layer wire structure for high efficiency wireless communication |

| US9208942B2 (en) * | 2009-03-09 | 2015-12-08 | Nucurrent, Inc. | Multi-layer-multi-turn structure for high efficiency wireless communication |

| US11476566B2 (en) | 2009-03-09 | 2022-10-18 | Nucurrent, Inc. | Multi-layer-multi-turn structure for high efficiency wireless communication |

| US9300046B2 (en) | 2009-03-09 | 2016-03-29 | Nucurrent, Inc. | Method for manufacture of multi-layer-multi-turn high efficiency inductors |

| JP5589313B2 (ja) * | 2009-06-23 | 2014-09-17 | 富士通株式会社 | 集積型電子部品 |

| KR101215303B1 (ko) * | 2009-07-21 | 2012-12-26 | 한국전자통신연구원 | 엘티씨씨 인덕터를 포함하는 전자 장치 |

| CN103975398B (zh) * | 2011-08-18 | 2017-07-04 | 温彻斯特技术有限责任公司 | 具有大电感可调谐性的静电可调谐磁电电感器 |

| US8378776B1 (en) * | 2011-08-26 | 2013-02-19 | National Semiconductor Corporation | Semiconductor structure with galvanically-isolated signal and power paths |

| US20130140671A1 (en) * | 2011-12-06 | 2013-06-06 | Win Semiconductors Corp. | Compound semiconductor integrated circuit with three-dimensionally formed components |

| US8552828B1 (en) | 2012-09-07 | 2013-10-08 | Infineon Technologies Ag | System and method for a coreless transformer |

| TWI649980B (zh) * | 2013-03-08 | 2019-02-01 | 美商紐克倫有限公司 | 用於高效率無線通信之多層導線結構 |

| TWI596915B (zh) * | 2013-03-08 | 2017-08-21 | 紐克倫有限公司 | 用於高效率無線通信之多層多匝結構 |

| FR3004289B1 (fr) * | 2013-04-08 | 2015-05-15 | Soitec Silicon On Insulator | Composant a ondes acoustiques de surface et sa methode de fabrication |

| US9136822B2 (en) | 2013-08-19 | 2015-09-15 | Harris Corporation | Microelectromechanical system with a micro-scale spring suspension system and methods for making the same |

| US9093975B2 (en) | 2013-08-19 | 2015-07-28 | Harris Corporation | Microelectromechanical systems comprising differential inductors and methods for making the same |

| US9172352B2 (en) * | 2013-08-19 | 2015-10-27 | Harris Corporation | Integrated microelectromechanical system devices and methods for making the same |

| US9123493B2 (en) | 2014-01-23 | 2015-09-01 | Harris Corporation | Microelectromechanical switches for steering of RF signals |

| US9343403B2 (en) * | 2014-04-04 | 2016-05-17 | Qualcomm Incorporated | Stress mitigation structure for wafer warpage reduction |

| US10236115B2 (en) * | 2014-06-16 | 2019-03-19 | Stmicroelectronics S.R.L. | Integrated transformer |

| US9583433B2 (en) | 2015-02-25 | 2017-02-28 | Qualcomm Incorporated | Integrated device package comprising conductive sheet configured as an inductor in an encapsulation layer |

| US9941743B2 (en) | 2015-08-07 | 2018-04-10 | Nucurrent, Inc. | Single structure multi mode antenna having a unitary body construction for wireless power transmission using magnetic field coupling |

| US10063100B2 (en) | 2015-08-07 | 2018-08-28 | Nucurrent, Inc. | Electrical system incorporating a single structure multimode antenna for wireless power transmission using magnetic field coupling |

| US9948129B2 (en) | 2015-08-07 | 2018-04-17 | Nucurrent, Inc. | Single structure multi mode antenna for wireless power transmission using magnetic field coupling having an internal switch circuit |

| US10636563B2 (en) | 2015-08-07 | 2020-04-28 | Nucurrent, Inc. | Method of fabricating a single structure multi mode antenna for wireless power transmission using magnetic field coupling |

| US10658847B2 (en) | 2015-08-07 | 2020-05-19 | Nucurrent, Inc. | Method of providing a single structure multi mode antenna for wireless power transmission using magnetic field coupling |

| US9960628B2 (en) | 2015-08-07 | 2018-05-01 | Nucurrent, Inc. | Single structure multi mode antenna having a single layer structure with coils on opposing sides for wireless power transmission using magnetic field coupling |

| US11205848B2 (en) | 2015-08-07 | 2021-12-21 | Nucurrent, Inc. | Method of providing a single structure multi mode antenna having a unitary body construction for wireless power transmission using magnetic field coupling |

| US9941590B2 (en) | 2015-08-07 | 2018-04-10 | Nucurrent, Inc. | Single structure multi mode antenna for wireless power transmission using magnetic field coupling having magnetic shielding |

| US9941729B2 (en) | 2015-08-07 | 2018-04-10 | Nucurrent, Inc. | Single layer multi mode antenna for wireless power transmission using magnetic field coupling |

| US9960629B2 (en) | 2015-08-07 | 2018-05-01 | Nucurrent, Inc. | Method of operating a single structure multi mode antenna for wireless power transmission using magnetic field coupling |

| WO2017031348A1 (en) | 2015-08-19 | 2017-02-23 | Nucurrent, Inc. | Multi-mode wireless antenna configurations |

| US9893048B2 (en) * | 2015-09-14 | 2018-02-13 | Qualcomm Incorporated | Passive-on-glass (POG) device and method |

| WO2017188062A1 (ja) * | 2016-04-25 | 2017-11-02 | 株式会社村田製作所 | 弾性波フィルタ装置およびマルチプレクサ |

| CN107545081A (zh) * | 2016-06-24 | 2018-01-05 | 上海北京大学微电子研究院 | 一种rf螺旋电感高精度集总参数模型及参数提取方法 |

| US10903660B2 (en) | 2016-08-26 | 2021-01-26 | Nucurrent, Inc. | Wireless connector system circuit |

| US10868444B2 (en) | 2016-12-09 | 2020-12-15 | Nucurrent, Inc. | Method of operating a system having a substrate configured to facilitate through-metal energy transfer via near field magnetic coupling |

| US11264837B2 (en) | 2017-02-13 | 2022-03-01 | Nucurrent, Inc. | Transmitting base with antenna having magnetic shielding panes |

| US11283295B2 (en) | 2017-05-26 | 2022-03-22 | Nucurrent, Inc. | Device orientation independent wireless transmission system |

| JP6909060B2 (ja) * | 2017-06-08 | 2021-07-28 | 太陽誘電株式会社 | 電子部品 |

| US10832848B2 (en) * | 2017-06-26 | 2020-11-10 | Qualcomm Incorporated | Low DC resistance and high RF resistance power amplifier choke inductor |

| US10419128B2 (en) * | 2017-07-19 | 2019-09-17 | Axalume, Inc. | Low-Q inductive-peaking optical front-end |

| JP7266996B2 (ja) | 2018-11-20 | 2023-05-01 | 太陽誘電株式会社 | インダクタ、フィルタおよびマルチプレクサ |

| US11227712B2 (en) | 2019-07-19 | 2022-01-18 | Nucurrent, Inc. | Preemptive thermal mitigation for wireless power systems |

| US11271430B2 (en) | 2019-07-19 | 2022-03-08 | Nucurrent, Inc. | Wireless power transfer system with extended wireless charging range |

| US11056922B1 (en) | 2020-01-03 | 2021-07-06 | Nucurrent, Inc. | Wireless power transfer system for simultaneous transfer to multiple devices |

| JP7200956B2 (ja) * | 2020-01-27 | 2023-01-10 | 株式会社村田製作所 | インダクタ部品 |

| US11283303B2 (en) | 2020-07-24 | 2022-03-22 | Nucurrent, Inc. | Area-apportioned wireless power antenna for maximized charging volume |

| US11881716B2 (en) | 2020-12-22 | 2024-01-23 | Nucurrent, Inc. | Ruggedized communication for wireless power systems in multi-device environments |

| US11876386B2 (en) | 2020-12-22 | 2024-01-16 | Nucurrent, Inc. | Detection of foreign objects in large charging volume applications |

| US11695302B2 (en) | 2021-02-01 | 2023-07-04 | Nucurrent, Inc. | Segmented shielding for wide area wireless power transmitter |

| US11831174B2 (en) | 2022-03-01 | 2023-11-28 | Nucurrent, Inc. | Cross talk and interference mitigation in dual wireless power transmitter |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US644309A (en) * | 1898-10-20 | 1900-02-27 | Albert White | Knitting-machine. |

| JPH0461264A (ja) | 1990-06-29 | 1992-02-27 | Nippon Telegr & Teleph Corp <Ntt> | Lc複合素子 |

| JPH04290212A (ja) * | 1991-03-18 | 1992-10-14 | Murata Mfg Co Ltd | 半導体装置 |

| JPH05190333A (ja) * | 1992-01-13 | 1993-07-30 | Sharp Corp | 重層型スパイラルインダクタ |

| JPH05335487A (ja) * | 1992-05-28 | 1993-12-17 | Rohm Co Ltd | 伝送回路素子 |

| JP3036233B2 (ja) * | 1992-06-22 | 2000-04-24 | 松下電器産業株式会社 | 半導体装置およびその製造方法 |

| JPH06334137A (ja) * | 1993-05-20 | 1994-12-02 | Hitachi Ltd | ハイブリッド集積回路およびその製造方法 |

| US5370766A (en) | 1993-08-16 | 1994-12-06 | California Micro Devices | Methods for fabrication of thin film inductors, inductor networks and integration with other passive and active devices |

| TW262595B (ja) * | 1993-11-17 | 1995-11-11 | Ikeda Takeshi | |

| US5629533A (en) | 1995-02-06 | 1997-05-13 | Motorola | Optical sensor and method |

| KR100243658B1 (ko) * | 1996-12-06 | 2000-02-01 | 정선종 | 기판 변환기술을 이용한 인덕터 소자 및 그 제조 방법 |

| JPH10335590A (ja) * | 1997-06-04 | 1998-12-18 | Nec Corp | 受動素子回路 |

| JP3620623B2 (ja) * | 1997-10-21 | 2005-02-16 | 富士電機デバイステクノロジー株式会社 | 平面型磁気素子 |

| US6008102A (en) * | 1998-04-09 | 1999-12-28 | Motorola, Inc. | Method of forming a three-dimensional integrated inductor |

| KR20000011585A (ko) * | 1998-07-28 | 2000-02-25 | 윤덕용 | 반도체소자및그제조방법 |

| US6885275B1 (en) * | 1998-11-12 | 2005-04-26 | Broadcom Corporation | Multi-track integrated spiral inductor |

| US6303423B1 (en) * | 1998-12-21 | 2001-10-16 | Megic Corporation | Method for forming high performance system-on-chip using post passivation process |

| JP2000306732A (ja) * | 1999-04-22 | 2000-11-02 | Ricoh Co Ltd | インダクタおよびその製造方法 |

| KR20010026587A (ko) * | 1999-09-07 | 2001-04-06 | 구자홍 | 마이크로머신드 튠어블 필터 및 제조 방법 |

| JP2002050519A (ja) * | 2000-08-04 | 2002-02-15 | Sony Corp | 高周波コイル装置及びその製造方法 |

| SE0004794L (sv) * | 2000-12-22 | 2002-06-23 | Ericsson Telefon Ab L M | En flerskikts-symmetreringstransformatorstruktur |

| KR100368930B1 (ko) * | 2001-03-29 | 2003-01-24 | 한국과학기술원 | 반도체 기판 위에 높이 떠 있는 3차원 금속 소자, 그 회로모델, 및 그 제조방법 |

| JP3579000B2 (ja) * | 2001-04-05 | 2004-10-20 | シャープ株式会社 | 半導体装置 |

| KR100576542B1 (ko) * | 2001-08-07 | 2006-05-03 | 한국전자통신연구원 | 집적형 인덕터 |

| ATE485627T1 (de) * | 2001-08-14 | 2010-11-15 | Nxp Bv | Elektronisches bauelement und verfahren zur herstellung |

| JP2003109819A (ja) * | 2001-09-28 | 2003-04-11 | Toshiba Corp | インダクタを有する半導体装置 |

| KR100400234B1 (ko) * | 2001-11-15 | 2003-10-01 | 삼성전자주식회사 | 송수신용 수동소자와 그 집적모듈 |

| AU2003213570A1 (en) * | 2002-02-26 | 2003-09-09 | The Regents Of The University Of Michigan | Mems-based, computer systems, clock generation and oscillator circuits and lc-tank apparatus for use therein |

| JP2004213196A (ja) * | 2002-12-27 | 2004-07-29 | Fujikura Ltd | 半導体モジュール、非接触icタグ、半導体モジュールの製造方法 |

| JP2004260017A (ja) * | 2003-02-26 | 2004-09-16 | Tdk Corp | 薄膜型コモンモードチョークコイル及びコモンモードチョークコイルアレイ |

| US7005751B2 (en) * | 2003-04-10 | 2006-02-28 | Formfactor, Inc. | Layered microelectronic contact and method for fabricating same |

| CN1830116B (zh) * | 2003-07-28 | 2011-04-13 | Nxp股份有限公司 | 高频组件 |

| JP4762531B2 (ja) * | 2004-11-30 | 2011-08-31 | 太陽誘電株式会社 | 電子部品及びその製造方法 |

| TWI286454B (en) * | 2005-03-09 | 2007-09-01 | Phoenix Prec Technology Corp | Electrical connector structure of circuit board and method for fabricating the same |

-

2005

- 2005-08-31 JP JP2005252596A patent/JP4707056B2/ja active Active

-

2006

- 2006-08-16 EP EP06254301.2A patent/EP1760731B1/en not_active Expired - Fee Related

- 2006-08-23 KR KR1020060079679A patent/KR100730672B1/ko active IP Right Grant

- 2006-08-25 US US11/509,577 patent/US7948056B2/en active Active

- 2006-08-30 CN CN2006101288079A patent/CN1925321B/zh active Active

-

2011

- 2011-03-21 US US13/064,347 patent/US8518789B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8518789B2 (en) | 2013-08-27 |

| US20070045773A1 (en) | 2007-03-01 |

| CN1925321B (zh) | 2011-07-06 |

| CN1925321A (zh) | 2007-03-07 |

| JP2007067236A (ja) | 2007-03-15 |

| KR100730672B1 (ko) | 2007-06-21 |

| EP1760731A3 (en) | 2013-11-27 |

| US20110171806A1 (en) | 2011-07-14 |

| KR20070026027A (ko) | 2007-03-08 |

| EP1760731B1 (en) | 2015-04-01 |

| US7948056B2 (en) | 2011-05-24 |

| EP1760731A2 (en) | 2007-03-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4707056B2 (ja) | 集積型電子部品および集積型電子部品製造方法 | |

| KR100737188B1 (ko) | 전자 부품 및 그 제조 방법 | |

| JP3141562B2 (ja) | 薄膜トランス装置 | |

| KR100763740B1 (ko) | 전자 부품 제조 방법 및 전자 부품 | |

| JP4916715B2 (ja) | 電子部品 | |

| US8988181B2 (en) | Common mode filter with multi-spiral layer structure and method of manufacturing the same | |

| JP4684856B2 (ja) | 電子部品 | |

| KR19990067493A (ko) | 다중층 금속 중합체 구조를 이용한 알에프 변압기 | |

| JP4795385B2 (ja) | 集積型電子部品 | |

| US9007149B2 (en) | Common mode filter with multi spiral layer structure and method of manufacturing the same | |

| JP2006041357A (ja) | 半導体装置およびその製造方法 | |

| JP2006324492A (ja) | コイル部品及びその製造方法 | |

| JP4675662B2 (ja) | 半導体装置 | |

| JP5600095B2 (ja) | 多層らせん構造のコモンモードフィルタ及びその製造方法 | |

| JP4626041B2 (ja) | チップ型コイル部品 | |

| JP4656196B2 (ja) | インダクタおよびフィルタ | |

| JP5600094B2 (ja) | 多層らせん構造のコモンモードフィルタ及びその製造方法 | |

| WO2017138299A1 (ja) | 高周波モジュールとその製造方法 | |

| US11881343B2 (en) | Layered process-constructed double-winding embedded solenoid inductor | |

| JP2002110423A (ja) | コモンモードチョークコイル | |

| JP2007005702A (ja) | 半導体装置およびその製造方法 | |

| JPH03241863A (ja) | 混成集積回路部品 | |

| TWI445021B (zh) | 薄膜式共模濾波器 | |

| JP2001006936A (ja) | 電子部品 | |

| JP2006351686A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071108 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20071108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20071108 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080526 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090730 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090818 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091014 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100525 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100726 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20101029 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101029 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20101129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20101129 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110308 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110309 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4707056 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |