JP4702822B2 - 終端構造及びトレンチ金属酸化膜半導体素子 - Google Patents

終端構造及びトレンチ金属酸化膜半導体素子 Download PDFInfo

- Publication number

- JP4702822B2 JP4702822B2 JP2001292502A JP2001292502A JP4702822B2 JP 4702822 B2 JP4702822 B2 JP 4702822B2 JP 2001292502 A JP2001292502 A JP 2001292502A JP 2001292502 A JP2001292502 A JP 2001292502A JP 4702822 B2 JP4702822 B2 JP 4702822B2

- Authority

- JP

- Japan

- Prior art keywords

- trench

- semiconductor substrate

- metal oxide

- layer

- termination structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000004065 semiconductor Substances 0.000 title claims description 93

- 229910044991 metal oxide Inorganic materials 0.000 title claims description 29

- 150000004706 metal oxides Chemical class 0.000 title claims description 29

- 239000000758 substrate Substances 0.000 claims description 81

- 125000006850 spacer group Chemical group 0.000 claims description 18

- 239000012535 impurity Substances 0.000 claims description 15

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 12

- 239000002184 metal Substances 0.000 claims description 11

- 229910052751 metal Inorganic materials 0.000 claims description 11

- 229910021417 amorphous silicon Inorganic materials 0.000 claims description 10

- 239000000463 material Substances 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 139

- 238000000034 method Methods 0.000 description 40

- 238000005530 etching Methods 0.000 description 9

- 230000003647 oxidation Effects 0.000 description 9

- 238000007254 oxidation reaction Methods 0.000 description 9

- 230000005684 electric field Effects 0.000 description 8

- 238000004519 manufacturing process Methods 0.000 description 7

- 229920002120 photoresistant polymer Polymers 0.000 description 7

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 5

- 239000011529 conductive interlayer Substances 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 4

- 230000007423 decrease Effects 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 241000293849 Cordylanthus Species 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 210000003323 beak Anatomy 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0661—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body specially adapted for altering the breakdown voltage by removing semiconductor material at, or in the neighbourhood of, a reverse biased junction, e.g. by bevelling, moat etching, depletion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

- H01L29/407—Recessed field plates, e.g. trench field plates, buried field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66083—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by variation of the electric current supplied or the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. two-terminal devices

- H01L29/6609—Diodes

- H01L29/66143—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/872—Schottky diodes

- H01L29/8725—Schottky diodes of the trench MOS barrier type [TMBS]

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Electrodes Of Semiconductors (AREA)

Description

【技術分野】

本発明は、半導体装置に関し、特に漏れ電流を防止するためのトレンチ金属酸化膜半導体用の終端構造に関する。

【0002】

【背景技術】

二重拡散金属酸化膜半導体の電界効果トランジスタ(Doubled diffused metal-oxide-semiconductor field effect transistor:以下、DMOSFETという。)、絶縁ゲート型バイポーラトランジスタ(insulated gate bipolar transistor:以下、IGBTという。)、ショットキーダイオードは、重要な電力素子であり、スイッチング電源及び他の高速電力スイッチングの応用における出力整流子として広く使用されている。このような用途には、例えばモータの駆動、通信装置、産業の自動化及び電子的な自動化におけるスイッチング等が含まれる。電力素子は、通常、順方向電流が大きく、逆バイアス耐圧が例えば30V以上と高く、逆バイアス時の漏れ電流が少ないことが要求される。これらの要求に対して、トレンチDMOS、トレンチIGBT、トレンチショットキーダイオードは、プレーナ構造のものよりも優れていることが知られている。

【0003】

パワートランジスタにおいては、大電流を流す活性領域の素子に加えて、活性領域の周囲、通常ダイの端部に終端構造を設け、早期の電圧降伏現象を防止する必要がある。従来の終端構造には、シリコンの選択酸化(local oxidation of silicon:以下、LOCOSという。)、電界プレート(field plate)、ガードリング(guard ring)及びこれらの組合せ等がある。LOCOSは、バーズビーク特性(bird beak characteristic)を有していることが知られている。バーズビークにおいては、衝突電離係数が高いために、電界集中現象(field crowding phenomena)が発生しやすい。この結果、漏れ電流が増加し、活性領域の電気的特性が劣化する。

【0004】

ここで、ショットキーダイオード用のトレンチMOS構造及びトレンチ終端構造が形成された半導体基板の具体例をFIG.1に示す。この半導体基板は、高濃度に拡散形成されたn+基板10と、この上に形成されたエピタキシャル層20を備える。エピタキシャル層20内には、複数のトレンチMOS15が形成されている。エピタキシャル層20、ゲート酸化層25、多結晶シリコン層30を含むトレンチMOS素子は、活性領域5に形成されている。活性領域5からダイの端までの境界は、厚さ約6000ÅのLOCOS領域である。

【0005】

電界集中現象を緩和するために、LOCOS領域の真下には、イオン注入により、p+ドープ領域50が形成されている。p+ドープ領域50は、逆バイアス耐圧を高めるためのガードリングとして機能する。活性領域5の表面からLOCOS領域のp+ドープ領域50に対応する表面に亘って、アノード(金属層)55が設けられている。これは、空乏層の湾曲領域を活性領域5から遠ざけるために設けられている。ガードリング50は、電界集中を緩和し、活性領域5近傍に発生する電界強度の傾きを滑らかにするが、p+ドープ領域50とトレンチMOS15の底部の下側との間の隣接領域60は、円滑な曲線を描かない。このため、漏れ電流が増加し、逆バイアス耐圧が低下する。フィールドプレートとガードリングを組み合わせて用いた場合も同様の状況が発生する。さらに、上述した従来の構造は、製造段階で多数の(少なくとも4回の)フォトマスクプロセスを必要とし、処理が複雑である。さらに、このような構造を形成するためにコストが嵩むという問題もある。

【0006】

【発明が解決しようとする課題】

従来の終端構造のいずれも、上述の問題を解決するものではない。そこで、本発明は、新規な終端構造を提供するものである。本発明が提供する終端構造により、空乏層の湾曲領域を活性領域から遠ざけることができ、空乏層の境界を従来より平坦にすることができる。さらに、本発明は、従来より単純なプロセスで製造できる終端構造及び終端構造の製造方法を提供する。本発明においては、終端構造及びトレンチを同時に形成するため、フォトマスクプロセスは3回ですみ、全体の製造プロセスが単純化され、製造コストも低減できる。

【0007】

【課題を解決するための手段】

本発明に係る終端構造及びトレンチ金属酸化膜半導体素子は、トレンチ金属酸化膜半導体素子用の終端構造及びトレンチ金属酸化膜半導体素子において、第1のトレンチ及び第2のトレンチが形成された半導体基板と、第1のトレンチ内に形成された第1の金属酸化膜半導体ゲート及び第2のトレンチの側壁にスペーサとして形成された第2の金属酸化膜半導体ゲートと、スペーサの一部及び第2のトレンチの底面を覆うように第2のトレンチ内に形成された終端構造酸化層と、半導体基板の背面に半導体基板とオーミック接合を形成する第1の電極を形成し、半導体基板の表面に半導体基板とショットキー接合を形成する第2の電極を形成する導電層とを備え、第1のトレンチは、トレンチ金属酸化膜半導体素子が形成された活性領域内に形成され、第2のトレンチは、活性領域の境界から半導体基板の端部に亘って形成され、第2の電極は、活性領域表面及びスペーサ表面に接触して設けられ、空乏領域の湾曲領域が活性領域の境界から所定の長さ離間するように、活性領域、スペーサ及び終端構造酸化層の一部を覆うように形成され、半導体基板は、第1の種類の導電性不純物が低濃度にドープされた第1の層と、第1の種類の導電性不純物が高濃度にドープされたベース基板とを備え、第1の層の表面を半導体基板の表面とし、ベース基板の背面を半導体基板の背面とするショットキーダイオード用の半導体基板であることを特徴とする。

【0008】

【発明を実施するための最良の形態】

上述の発明の背景において説明したように、従来の終端構造としては、選択酸化、電界プレート、ガードリング及びこれらの組合せ等があるが、このような終端構造のいずれも電界集中の問題を完全に解決するものではない。電界の集中が発生する位置は、設計の違いにより、様々である。本発明は、新規なトレンチ終端構造及びその製造方法を提供する。本発明に基づくトレンチ終端構造は、電界集中の問題を解決する。また、本発明に基づくトレンチ終端構造は、平坦な空乏層境界を実現し、この境界における湾曲領域は、逆バイアス電圧が印加されても、活性領域から遠く離れている。したがって、本発明に基づく終端構造により、降伏現象が早期に発生することを防止することができる。

【0009】

さらに、本発明に基づく終端構造は、ショットキーダイオード、二重拡散金属酸化膜半導体(Doubled diffused metal-oxide-semiconductor:以下、DMOSという。)、絶縁ゲート型バイポーラトランジスタ(insulated gate bipolar transistor:以下、IGBTという。)等、いかなるパワートランジスタにも適用できる。最も重要な点は、トレンチMOS素子をトレンチ終端構造と同時に形成できるという点である。

【0010】

以下、本発明の幾つかの具体的な実施例を順次説明する。

【0011】

まず、第1の好ましい実施例として、ショットキーダイオードとトレンチ終端構造とを同時に形成する方法を説明する。

【0012】

FIG.2は、半導体基板100の断面を示す図であり、半導体基板100は、第1の種類の導電性不純物(例えば、n型不純物)がドープされている第1の層100Aと、第1の種類の導電性不純物が高濃度にドープされているベース基板100Bとを備える。第1の層100Aは、ショットキー接合を形成するためにベース基板100B上にエピタキシャル成長により形成され、ベース基板100Bは、オーミック接触を形成するためであり、その上に金属層が形成される。

【0013】

そして、酸化層101は、第1の層100A上に化学蒸着(chemical vapor deposit:以下、CVDという。)法により2000Å〜10000Åの厚さで形成される。次に、フォトレジスト(図示せず)により酸化層101を覆い、複数の第1のトレンチ110及び1個の第2のトレンチ120を画定(define)する。各第1のトレンチ110は、活性領域の断面において、0.2μm〜2.0μmの幅を有するように形成される。第2のトレンチ120は、第1のトレンチ110からメサ1個分離間し、活性領域の境界から半導体基板(又はダイ)100の端部に亘って形成される。第2のトレンチ120は、空乏境界を平坦にし、電界集中を防止するために設けられる。更に、第1のトレンチ110及び第2のトレンチ120は、0.4μm〜10μmの深さを有するように形成される。

【0014】

FIG.3に示すように、酸化層101を除去した後、高温酸化プロセスによりゲート酸化層125を形成する。ゲート酸化層125は、約150Å〜3000Åの厚みを有し、第1及び第2のトレンチ110、120の側壁110A、120A及び底面110B、120B、及びメサ表面115A上に形成される。これに代えて、高温蒸着法により、ゲート酸化層125を高温酸化(high temperature oxide:以下、HTOという。)蒸着層として形成してもよい。

【0015】

続いて、ゲート酸化層125に対してCVDプロセスを施し、第1のトレンチ110及び第2のトレンチ120を埋め、少なくともメサ表面115Aより高い第1の導電層140を形成する。第1の導電層140は、CVDプロセスにより、半導体基板100の背面にも形成される。第1の導電層140の材料は、金属、多結晶シリコン及び非晶質シリコンからなるグループから選択される。第1の導電層140の厚さは、0.5μm〜3.0μmとするとよい。第1のトレンチ110の内部に空隙(void)が形成されることを防ぐために、ステップカバレッジ(段差被覆性)が良好となるように、第1の導電層140の材料としては、多結晶シリコンを用い、減圧CVD(low-pressure CVD)法により多結晶シリコン層を形成するとよい。なお、第1のトレンチ110のアスペクト比が5以上である場合、非晶質シリコン層をPECVD法により形成するとよい。非晶質シリコンは、多結晶シリコンに比べて、空隙埋込特性(gap filled characteristic)が良好である。なお、非晶質シリコンに導電性を持たせるためには、非晶質シリコン再結晶処理が必要である。

【0016】

次に、FIG.4に示すように、メサ表面115A上のゲート酸化層125をエッチング停止層(etching stop layer)として用いて、異方性エッチングを行い、メサ表面115Aより上の第1の導電層140を除去する。この処理の後、第2のトレンチ120の側壁120Aに第2のトレンチ120の高さと略等しい幅(断面図における横方向の幅)を有するスペーサ122を形成する。

【0017】

次に、終端構造のための誘電層150を形成する。誘電層150は、オルトケイ酸テトラエチル(tetraethylorthosilicate:以下、TEOSという。)、PETEOS、O3−TEOS、HTOのいずれにより形成してもよい。誘電層150の厚さは、0.2μm〜1.0μmとするとよい。

【0018】

次に、誘電層150をフォトレジストパターン155で覆い、ショットキー接合の範囲を画定する。次に、このフォトレジストパターン155をマスクとして用いて、ドライエッチングを行い、メサ表面115A及び第1のトレンチ110の第1の導電層140を露出させる。

【0019】

このフォトレジストパターン155を剥離した後、FIG.5Aに示すように、背面の不要な層を除去し、ベース基板100Bの背面を露出させる。この不要な層とは、誘電層150、第1の導電層140、ゲート酸化層125を含む活性領域の素子を形成するための熱酸化プロセス又はCVDプロセスにより半導体基板100の背面に形成された層である。

【0020】

続いて、スパッタリングプロセスにより、第2の導電層を蒸着させ、第2の導電層と第1の層100Aとの間にショットキー接合領域115を形成し、及び第2の導電層とベース基板100Bの間のオーミック接触となるカソード160を形成する。次に、フォトレジストパターン165を第2の導電層上に形成し、アノード160Aを画定する。この具体例においては、アノード160Aは、活性領域から第2のトレンチ120に亘って、少なくとも活性領域から2.0μm以上延出するように形成される。これにより、空乏領域の湾曲領域を活性領域から遠く離間させることができる。

【0021】

FIG.5Bは、トレンチMOS終端構造(FIG.5Aに示す)の電気特性の具体例を示す図である。ここでは、逆バイアスをシミュレートするために、ショットキーダイオードに逆バイアス電圧を印加している。すなわち、アノード183を0Vとして、カソード160に183Vの電圧を印加する。線180は、等電位線を表している。FIG.5Bにおいては、等電位線180により表される電位は、底部から上部にかけて徐々に低くなっている。等電位線180に直交する線185は、電気力線(electrical force)を表している。FIG.5Bに示すように、漏れ電流は、活性領域のみで発生し、終端領域の下の空乏領域においては、ほとんど発生していない。さらに、空乏領域の境界180Aは、平坦な特性を有し、早期の電圧降伏は発生しない。なお、空乏領域の境界180Aでは、ごく僅かしか漏れ電流が生じない。

【0022】

FIG.5Cは、終端構造を有さないトレンチMOS構造体における逆電流曲線195と、本発明に基づく終端構造を有するトレンチMOS構造体における逆電流曲線190とを比較して示すグラフである。この終端構造により、増加する逆電流は8.8%のみである。これに対し、従来の終端構造であるガードリングとLOCOSの組合せでは、逆電流が12.8%増加する。このように、本発明によれば、特性が著しく向上する。さらに、従来の構造では、少なくとも4回のフォトマスクプロセスが必要であったが、本発明では、フォトマスクプロセスは3回(トレンチの形成(1回目)、ショットキー接合の画定(2回目)、アノードを形成するための第2の導電層のエッチング(3回目))のみでよい。すなわち、本発明によれば、終端構造の製造プロセスを単純化することができる。

【0023】

次に、終端構造を用いて、トレンチDMOS構造及び終端構造を形成する第2の具体例について説明する。

【0024】

FIG.6に示すように、DMOS構造のために、準備される半導体基板200は、ショットキーダイオードを形成する半導体基板100と異なるものであるが、半導体基板200に対して施される処理は極めて似ている。DMOS構造及び終端構造を同時に形成するために、準備された半導体基板200は、上面から底面に向かって、第1の層200Aと、第2の層200Bと、第3の層200Cとを備える。第1の層200A及び第2の層200Bは、第3の層(以下、ベース基板ともいう。)200C上にエピタキシャル成長プロセスを施すことにより形成されている。

【0025】

第1の層200Aは、ベース層としてp型導電性不純物がドープされており、さらに、第1の層200Aの表面には、p型導電性不純物が高濃度にドープされている。第2の層200Bは、n型導電性不純物が低濃度にドープされており、第3の層200Cには、n型導電性不純物が高濃度にドープされている。さらに、FIG.6に示す具体例では、第1の層200Aの表面には、複数のn+領域がイオン注入により形成され、これにより、多くのn+領域204及びp+領域203が形成されている。第1の層200Aの厚さは、0.5μm〜5.0μmであり、第2の層200Bの厚さは、3μm〜30μmである。

【0026】

次に、FIG.7に示すように、第1の具体例において説明した処理と同様に、メサ215を挟んで、複数の第1のトレンチ210と、第2のトレンチ220とを形成する。第1のトレンチ210は、n+領域204を貫通して、活性領域内に形成され、第2のトレンチ220は、活性領域の境界から半導体基板(又はダイ)200の端部に亘って形成されている。更に、第1のトレンチ210及び第2のトレンチ220は、0.4μm〜10μmの深さを有する。

【0027】

次に、高温酸化プロセスを行って、約150Å〜3000Åの厚みを有するゲート酸化層225を形成する。次に、メサ215を越えて、第1の多結晶シリコン(first polysilicon)及び非晶質シリコンのいずれかから選択された第1の導電層240を第1のトレンチ210及び第2のトレンチ220に埋め込む。次に、メサ表面215A上のゲート酸化層225を停止層(stopping layer)として用いて、エッチングプロセスを行うことにより、余分な第1の導電層240を除去する。次に、n+領域204とp+領域203とを停止層(stopping layer)として用いて、メサ表面215A上のゲート酸化層225を除去する。

【0028】

続いて、更なる熱酸化プロセスを施し、第1の導電層240の一部を酸化させることにより、導電層間酸化層(inter-conductive oxide layer)245を形成する。多結晶シリコンの粒界により、酸素高速拡散パス(oxygen fast diffusion paths)が形成されるので、第1のトレンチ210及び第2のトレンチ220内に多結晶シリコン層又は非晶質シリコン層により形成される酸化層は、半導体基板200上のメサ表面215Aに形成される酸化層より厚くなる。

【0029】

次に、FIG.8に示すように、エッチングプロセスにより、第1の層200A、n+領域204及びp+領域203の表面より上の導電層間酸化層(以下、単に熱酸化層ともいう。)245を除去する。なお、第2のトレンチ220のスペーサ240及び第1の導電層240上の熱酸化層245は、このエッチングプロセスの後も残留し、これにより、分離機能(isolation function)が実現される。続いて、全ての領域にTEOS酸化層250が形成される。次に、第1の層200AのTEOS酸化層250上にフォトレジストパターンが形成され、ソース接続領域が画定される。

【0030】

次に、FIG.9に示すように、スパッタリングプロセスを行う前に、半導体基板(すなわちベース基板200C)の背面に形成されている不要な層を除去する。この不要な層には、活性領域内の素子を形成するときにベース基板200Cの背面に同時に形成されたTEOS酸化層250と、導電層間酸化層245と、第1の導電層240と、ゲート酸化層225とが含まれる。

【0031】

続いて、スパッタリングプロセスにより金属層260を堆積し、これにより、第1の層200A上のソース接続及びベース基板200C上のドレイン接続、すなわち半導体基板200の背面が形成される。上述の具体例と同様に、活性領域上に形成される金属層260は、約2.0μm以上終端構造(第2のトレンチ220)に延出し、その端部が活性領域から離間している必要がある。これにより、上述の具体例と同様のリソグラフィプロセス及びエッチングプロセスを続いて行うことができる。

【0032】

次に、終端構造を用いてトレンチIGBT構造と終端構造とを同時に形成する第3の具体例について説明する。FIG.10に示すように、トレンチMOSをIGBT構造として形成するために準備される半導体基板300は、ショットキーダイオードを形成するための半導体基板100とは異なるものであるが、トレンチDMOS構造用に準備される半導体基板200に非常に似ている。さらに、ここでの処理は、トレンチDMOSを製造するための処理と略同一である。IGBT構造及び終端構造を同時に形成するために準備される半導体基板300は、上面から底面に向かって、第1の層300Aと、第2の層300Bと、第3の層300Cと、ベース基板300Dとを備える。第1の層300A、第2の層300B及び第3の層300Cは、ベース基板300D上にエピタキシャル成長プロセスを施すことにより形成されている。

【0033】

第1〜第3の層300A、300B、300Cには、FIG.6に示す半導体基板200と同様の種類の不純物が同様の濃度でドープされている。例えば、第1の層300Aは、p型のベース層であり、p型のベース層302の上部には、n+ドープ領域304とp+ドープ領域303が形成されている。第2の層300Bは、ドリフト層として機能するnドープ層であり、第3の層300Cは、バッファ層として機能するn+ドープ層である。ベース基板300Dは、p型導電性不純物が高濃度にドープされている。第1の層300Aの厚さは、0.5μm〜10.0μmであり、第2の層300Bの厚さは、3μm〜100μmである。

【0034】

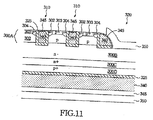

FIG.11に示すように、n+ドープ領域304を貫通して、複数の第1のトレンチ310を形成する。第1のトレンチ310の底面は、p型にドープされたベース層302より深い位置に形成される。さらに、各第1のトレンチ310及び第2のトレンチ320は、0.2μm〜4.0μmのメサ315により離間されている。第2のトレンチ320は、活性領域の境界から半導体基板300の端部に亘って形成されている。更に、第1のトレンチ310及び第2のトレンチ320は、0.4μm〜10μmの深さを有する。

【0035】

150Å〜3000Åの厚みを有するゲート酸化層325を形成する熱酸化プロセスの後、第1のトレンチ310及び第2のトレンチ320に多結晶シリコン又は非晶質シリコン層等の第1の導電材料340の埋込処理を行う。次に、メサ315の表面上のゲート酸化層325を停止層として用いて、エッチバックプロセスを行い、これにより、第1のトレンチ310及び第2のトレンチ320のスペーサのみに第1の導電材料340が残留する。

【0036】

上述の第2の具体例と同様、第1の層300Aの表面上のゲート酸化層325が除去され、そして、更なる熱酸化プロセスが実行され、第1の導電材料340と金属層(後に形成される)の分離のための導電層間酸化層(inter-conductive oxide layer)345が形成される。次に、メサ315の表面上の導電層間酸化層(以下、単に熱酸化層ともいう。)345が除去される。なお、第1のトレンチ310及び第2のトレンチ320内の第1の導電材料340上の熱酸化層345は、導電層間酸化層として残される。

【0037】

さらに、FIG.11に示すように、上述と同様に、全ての領域上にTEOS誘電層350を形成し、これをフォトレジストパターンにより覆う。この後、エッチングプロセスを行い、n+ドープ領域304及びp+ドープ領域303を露出させる。

【0038】

次に、FIG.12に示すように、金属スパッタリングを行う前に、ベース基板300Dの背面に形成されている不要な層を除去する。第2の導電層に続いて、通常、ベース基板300Dの表面に金属層360が形成され、これにより、コレクタ電極が形成される。リソグラフィプロセス及びエッチングプロセスを順次行った後、第1の層300Aの表面にpドープ+領域303とn+ドープ領域304に接続されたエミッタ電極が形成される。エミッタ電極の一方の端部は、活性領域から所定の距離離間した位置に設けられる。

【0039】

本発明の効果は、以下の通りである。

(1)空乏境界が平坦であり、空乏境界の湾曲領域を活性領域から遠く離すことができる。このような特性により早期の電圧降伏現象を防止することができる。

(2)本発明に基づく終端構造に逆バイアス電圧を印加することにより生じる漏れ電流は、従来のLOCOS及びガードリングにより構成される終端構造より小さい(8.8%対12.8%)。

(3)本発明に基づく終端構造を有するトレンチMOS素子は、従来より単純なプロセスで製造できる。本発明によれば、フォトマスクプロセスを減らすことができる。

【0040】

当業者にとって明らかなように、上述した本発明の好ましい実施の形態は、本発明を限定する目的ではなく、例示的に示したものにすぎない。本発明は、添付の請求の範囲に含まれる様々な変形例及び同様の構成を包含する。すなわち、本発明の範囲は、最も広く解釈され、このような変形例及び同様の構造の全てを含むものと解釈される。

【図面の簡単な説明】

【図1】 FIG.1は、LOCOS及びガードリングを終端構造として用いた従来のトレンチショットキーダイオードを示す図である。

【図2】 FIG.2は、本発明に基づいて形成された第1のトレンチ及び第2のトレンチを示す断面図である。

【図3】 FIG.3は、本発明に基づいて、第1のトレンチ及び第2のトレンチに第1の導電材料を埋め込んだ状態を示す断面図である。

【図4】 FIG.4は、本発明に基づいて、終端構造の酸化層を画定し、活性領域及びスペーサを露出させた状態を示す断面図である。

【図5】 FIG.5Aは、半導体基板の両面にアノード電極及びカソード電極を形成し、本発明に基づくショットキーダイオード及び終端構造を完成させた状態を示す断面図である。

【図6】 FIG.5Bは、本発明に基づくショットキーダイオード及び終端構造を用いたシミュレーションにおける等電位線及び電力線を示す図である。

【図7】 FIG.5Cは、本発明に基づく終端構造を有するトレンチショットキーダイオード及び有さないトレンチショットキーダイオードの漏れ電流を比較するシミュレーション結果を示す図である。

【図8】 FIG.6は、DMOS素子及び終端構造のために準備される半導体基

板の断面図である。

【図9】 FIG.7は、第1の導電層をエッチバックし、高温熱酸化プロセスにより導電層間酸化層を形成した状態を示す断面図である。

【図10】 FIG.8は、終端構造酸化層を画定し、活性領域及びスペーサを露出した状態を示す断面図である。

【図11】 FIG.9は、半導体基板の両面にソース電極及びドレイン電極を形成し、DMOS素子及び終端構造を完成させた状態を示す断面図である。

【図12】 FIG.10は、IGBT及び終端構造のために準備される半導体基板の断面を示す図である。

【図13】 FIG.11は、終端構造酸化層を画定し、活性領域及びスペーサを露出させた状態を示す断面図である。

【図14】 FIG.12は、半導体基板の両面にエミッタ電極とコレクタ電極とを形成し、IGBT及び終端構造を完成させた状態を示す断面図である。

Claims (8)

- トレンチ金属酸化膜半導体素子用の終端構造及びトレンチ金属酸化膜半導体素子において、

第1のトレンチ及び第2のトレンチが形成された半導体基板と、

上記第1のトレンチ内に形成された第1の金属酸化膜半導体ゲート及び上記第2のトレンチの側壁にスペーサとして形成された第2の金属酸化膜半導体ゲートと、

上記スペーサの一部及び上記第2のトレンチの底面を覆うように該第2のトレンチ内に形成された終端構造酸化層と、

上記半導体基板の背面に該半導体基板とオーミック接合を形成する第1の電極を形成し、該半導体基板の表面に該半導体基板とショットキー接合を形成する第2の電極を形成する導電層とを備え、

上記第1のトレンチは、上記トレンチ金属酸化膜半導体素子が形成された活性領域内に形成され、上記第2のトレンチは、該活性領域の境界から上記半導体基板の端部に亘って形成され、

上記第2の電極は、上記活性領域表面及び上記スペーサ表面に接触して設けられ、空乏領域の湾曲領域が該活性領域の境界から所定の長さ離間するように、該活性領域、該スペーサ及び上記終端構造酸化層の一部を覆うように形成され、

上記半導体基板は、第1の種類の導電性不純物が低濃度にドープされた第1の層と、第1の種類の導電性不純物が高濃度にドープされたベース基板とを備え、上記第1の層の表面を上記半導体基板の表面とし、上記ベース基板の背面を上記半導体基板の背面とするショットキーダイオード用の半導体基板であることを特徴とする終端構造及びトレンチ金属酸化膜半導体素子。 - 上記第1のトレンチ及び第2のトレンチは、0.4μm〜10μmの深さを有し、上記第1の層内に形成されていることを特徴とする請求項1記載の終端構造及びトレンチ金属酸化膜半導体素子。

- 上記第1の金属酸化膜半導体ゲート及び第2の金属酸化膜半導体ゲートは、

上記第1のトレンチ及び第2のトレンチの底面及び側壁に形成されたゲート酸化層と、

上記ゲート酸化層上に形成され、上記第1のトレンチ及び第2のトレンチを埋める第1の導電層とを備える請求項1記載の終端構造及びトレンチ金属酸化膜半導体素子。 - 上記第1の導電層は、金属、多結晶シリコン及び非晶質シリコンからなるグループから選択された材料から形成されることを特徴とする請求項1記載の終端構造及びトレンチ金属酸化膜半導体素子。

- トレンチ金属酸化膜半導体素子用の終端構造及びトレンチ金属酸化膜半導体素子において、

上記トレンチ金属酸化膜半導体素子が形成された活性領域内に互いに離間して形成された複数の第1のトレンチと、該活性領域の境界から半導体基板の端部に亘って形成された第2のトレンチとを有する半導体基板と、

上記各第1のトレンチに形成された第1の金属酸化膜半導体ゲート及び上記第2のトレンチの側壁にスペーサとして形成された第2の金属酸化膜半導体ゲートと、

上記スペーサの一部及び該第2のトレンチの底面を覆うように該第2のトレンチ内に形成された終端構造酸化層と、

上記半導体基板の背面に該半導体基板とオーミック接合を形成する第1の電極を形成し、該半導体基板の表面に該半導体基板とショットキー接合を形成する第2の電極を形成する導電層とを備え、

上記第2の電極は、上記活性領域表面及び上記スペーサ表面に接触して設けられ、空乏領域の湾曲領域が該活性領域の境界から少なくとも2μm離間するように、該活性領域、該スペーサ及び上記終端構造酸化層の一部を覆うように形成され、

上記半導体基板は、第1の種類の導電性不純物が低濃度にドープされた第1の層と、第1の種類の導電性不純物が高濃度にドープされたベース基板とを備え、上記第1の層の表面を上記半導体基板の表面とし、上記ベース基板の背面を上記半導体基板の背面とするショットキーダイオード用の半導体基板であることを特徴とする終端構造及びトレンチ金属酸化膜半導体素子。 - 上記第1のトレンチ及び第2のトレンチの深さは、0.4μm〜10μmであることを特徴とする請求項5記載の終端構造及びトレンチ金属酸化膜半導体素子。

- 上記第1の金属酸化膜半導体ゲート及び第2の金属酸化膜半導体ゲートは、

上記第1のトレンチ及び第2のトレンチの底面及び側壁に形成されたゲート酸化層と、

該ゲート酸化層上に形成され、該第1のトレンチ及び第2のトレンチを埋める第1の導電層とを備えることを特徴とする請求項5記載の終端構造及びトレンチ金属酸化膜半導体素子。 - 上記第1の導電層は、金属、多結晶シリコン及び非晶質シリコンからなるグループから選択された材料から形成されることを特徴とする請求項7記載の終端構造及びトレンチ金属酸化膜半導体素子。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/668,663 | 2000-09-22 | ||

| US09/668,663 US6396090B1 (en) | 2000-09-22 | 2000-09-22 | Trench MOS device and termination structure |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010044627A Division JP5379045B2 (ja) | 2000-09-22 | 2010-03-01 | トレンチ金属酸化膜半導体素子 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002217426A JP2002217426A (ja) | 2002-08-02 |

| JP2002217426A5 JP2002217426A5 (ja) | 2005-07-14 |

| JP4702822B2 true JP4702822B2 (ja) | 2011-06-15 |

Family

ID=24683263

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001292502A Expired - Lifetime JP4702822B2 (ja) | 2000-09-22 | 2001-09-25 | 終端構造及びトレンチ金属酸化膜半導体素子 |

| JP2010044627A Expired - Lifetime JP5379045B2 (ja) | 2000-09-22 | 2010-03-01 | トレンチ金属酸化膜半導体素子 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010044627A Expired - Lifetime JP5379045B2 (ja) | 2000-09-22 | 2010-03-01 | トレンチ金属酸化膜半導体素子 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6396090B1 (ja) |

| EP (1) | EP1191603A3 (ja) |

| JP (2) | JP4702822B2 (ja) |

| CN (1) | CN1209822C (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010157761A (ja) * | 2000-09-22 | 2010-07-15 | General Semiconductor Inc | 終端構造及びトレンチ金属酸化膜半導体素子 |

Families Citing this family (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2381122B (en) * | 2001-10-16 | 2006-04-05 | Zetex Plc | Termination structure for a semiconductor device |

| JP3631464B2 (ja) * | 2001-12-27 | 2005-03-23 | 株式会社東芝 | 半導体装置 |

| US6828649B2 (en) * | 2002-05-07 | 2004-12-07 | Agere Systems Inc. | Semiconductor device having an interconnect that electrically connects a conductive material and a doped layer, and a method of manufacture therefor |

| US6855593B2 (en) * | 2002-07-11 | 2005-02-15 | International Rectifier Corporation | Trench Schottky barrier diode |

| US7009228B1 (en) * | 2003-03-04 | 2006-03-07 | Lovoltech, Incorporated | Guard ring structure and method for fabricating same |

| US6958275B2 (en) * | 2003-03-11 | 2005-10-25 | Integrated Discrete Devices, Llc | MOSFET power transistors and methods |

| GB0312512D0 (en) | 2003-05-31 | 2003-07-09 | Koninkl Philips Electronics Nv | Termination structures for semiconductor devices and the manufacture thereof |

| US7754550B2 (en) * | 2003-07-10 | 2010-07-13 | International Rectifier Corporation | Process for forming thick oxides on Si or SiC for semiconductor devices |

| US6987305B2 (en) * | 2003-08-04 | 2006-01-17 | International Rectifier Corporation | Integrated FET and schottky device |

| KR100964400B1 (ko) * | 2003-10-01 | 2010-06-17 | 삼성전자주식회사 | 반도체 소자의 콘택 구조체 |

| CN101421832A (zh) * | 2004-03-01 | 2009-04-29 | 国际整流器公司 | 沟槽器件的自对准接触结构 |

| US6927451B1 (en) * | 2004-03-26 | 2005-08-09 | Siliconix Incorporated | Termination for trench MIS device having implanted drain-drift region |

| JP2006120789A (ja) * | 2004-10-20 | 2006-05-11 | Toshiba Corp | 半導体装置 |

| US7598576B2 (en) * | 2005-06-29 | 2009-10-06 | Cree, Inc. | Environmentally robust passivation structures for high-voltage silicon carbide semiconductor devices |

| US7855401B2 (en) * | 2005-06-29 | 2010-12-21 | Cree, Inc. | Passivation of wide band-gap based semiconductor devices with hydrogen-free sputtered nitrides |

| US7525122B2 (en) * | 2005-06-29 | 2009-04-28 | Cree, Inc. | Passivation of wide band-gap based semiconductor devices with hydrogen-free sputtered nitrides |

| US7750398B2 (en) * | 2006-09-26 | 2010-07-06 | Force-Mos Technology Corporation | Trench MOSFET with trench termination and manufacture thereof |

| US7560355B2 (en) * | 2006-10-24 | 2009-07-14 | Vishay General Semiconductor Llc | Semiconductor wafer suitable for forming a semiconductor junction diode device and method of forming same |

| US8017494B2 (en) * | 2007-01-31 | 2011-09-13 | International Rectifier Corporation | Termination trench structure for mosgated device and process for its manufacture |

| KR100861213B1 (ko) * | 2007-04-17 | 2008-09-30 | 동부일렉트로닉스 주식회사 | 반도체 소자 및 그 제조방법 |

| US8269265B2 (en) * | 2008-07-14 | 2012-09-18 | Microsemi Semiconductor (U.S.) Inc. | Trench capacitor for high voltage processes and method of manufacturing the same |

| JP2010098189A (ja) * | 2008-10-17 | 2010-04-30 | Toshiba Corp | 半導体装置 |

| US20110084332A1 (en) * | 2009-10-08 | 2011-04-14 | Vishay General Semiconductor, Llc. | Trench termination structure |

| JP5531620B2 (ja) * | 2010-01-05 | 2014-06-25 | 富士電機株式会社 | 半導体装置 |

| CN101853854B (zh) * | 2010-03-12 | 2012-11-21 | 无锡新洁能功率半导体有限公司 | 一种改进型终端结构的沟槽功率mos器件 |

| US8928065B2 (en) | 2010-03-16 | 2015-01-06 | Vishay General Semiconductor Llc | Trench DMOS device with improved termination structure for high voltage applications |

| US8853770B2 (en) * | 2010-03-16 | 2014-10-07 | Vishay General Semiconductor Llc | Trench MOS device with improved termination structure for high voltage applications |

| TWI455287B (zh) | 2010-11-04 | 2014-10-01 | Sinopower Semiconductor Inc | 功率半導體元件之終端結構及其製作方法 |

| JP5671966B2 (ja) * | 2010-11-17 | 2015-02-18 | 富士電機株式会社 | 半導体装置の製造方法および半導体装置 |

| TWI414070B (zh) * | 2011-06-02 | 2013-11-01 | Anpec Electronics Corp | 半導體功率元件 |

| CN103107193A (zh) * | 2011-11-11 | 2013-05-15 | 上海华虹Nec电子有限公司 | 一种沟槽型绝缘栅场效应管 |

| CN102437188A (zh) * | 2011-11-25 | 2012-05-02 | 无锡新洁能功率半导体有限公司 | 功率mosfet器件及其制造方法 |

| CN103137690B (zh) * | 2011-11-29 | 2016-10-26 | 上海华虹宏力半导体制造有限公司 | 一种沟槽型绝缘栅场效应管及其制造方法 |

| US20130168765A1 (en) * | 2012-01-04 | 2013-07-04 | Vishay General Semiconductor Llc | Trench dmos device with improved termination structure for high voltage applications |

| CN103426910B (zh) | 2012-05-24 | 2016-01-20 | 杰力科技股份有限公司 | 功率半导体元件及其边缘终端结构 |

| US20150123165A1 (en) * | 2012-05-30 | 2015-05-07 | Kyushu Institute Of Technology | High-voltage insulated gate type power semiconductor device and method of manufacturing the same |

| CN103578972B (zh) * | 2012-07-26 | 2016-06-29 | 无锡华润上华半导体有限公司 | 具有场终止结构的igbt背面多晶硅保护层的去除方法 |

| US9812338B2 (en) | 2013-03-14 | 2017-11-07 | Cree, Inc. | Encapsulation of advanced devices using novel PECVD and ALD schemes |

| US9991399B2 (en) | 2012-10-04 | 2018-06-05 | Cree, Inc. | Passivation structure for semiconductor devices |

| US8994073B2 (en) | 2012-10-04 | 2015-03-31 | Cree, Inc. | Hydrogen mitigation schemes in the passivation of advanced devices |

| JP6296445B2 (ja) | 2014-02-10 | 2018-03-20 | ローム株式会社 | ショットキーバリアダイオード |

| US9570542B2 (en) | 2014-04-01 | 2017-02-14 | Infineon Technologies Ag | Semiconductor device including a vertical edge termination structure and method of manufacturing |

| WO2016080322A1 (ja) * | 2014-11-18 | 2016-05-26 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

| US9431205B1 (en) * | 2015-04-13 | 2016-08-30 | International Business Machines Corporation | Fold over emitter and collector field emission transistor |

| JP7433611B2 (ja) * | 2016-04-28 | 2024-02-20 | 株式会社タムラ製作所 | トレンチmos型ショットキーダイオード |

| CN105977256B (zh) * | 2016-06-15 | 2018-11-23 | 武汉新芯集成电路制造有限公司 | 一种dram器件的制备方法 |

| US11081554B2 (en) | 2017-10-12 | 2021-08-03 | Semiconductor Components Industries, Llc | Insulated gate semiconductor device having trench termination structure and method |

| US10439075B1 (en) * | 2018-06-27 | 2019-10-08 | Semiconductor Components Industries, Llc | Termination structure for insulated gate semiconductor device and method |

| US10566466B2 (en) | 2018-06-27 | 2020-02-18 | Semiconductor Components Industries, Llc | Termination structure for insulated gate semiconductor device and method |

| CN109585572A (zh) * | 2018-12-29 | 2019-04-05 | 矽力杰半导体技术(杭州)有限公司 | 半导体器件及其制造方法 |

| CN113809179A (zh) * | 2021-10-20 | 2021-12-17 | 无锡橙芯微电子科技有限公司 | 一种sic dmos器件结构 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06151867A (ja) * | 1992-11-13 | 1994-05-31 | Sharp Corp | 縦型mosトランジスタおよびその製造方法 |

| JPH1174524A (ja) * | 1997-06-30 | 1999-03-16 | Denso Corp | 半導体装置及びその製造方法 |

| JP2000106435A (ja) * | 1998-09-29 | 2000-04-11 | Toshiba Corp | 電力用素子 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04256369A (ja) * | 1991-02-08 | 1992-09-11 | Nissan Motor Co Ltd | 半導体装置 |

| JPH08213606A (ja) * | 1995-02-06 | 1996-08-20 | Fuji Electric Co Ltd | 炭化ケイ素横形高耐圧mosfet |

| DE19636302C2 (de) * | 1995-09-06 | 1998-08-20 | Denso Corp | Siliziumkarbidhalbleitervorrichtung und Verfahren zur Herstellung |

| US6180966B1 (en) * | 1997-03-25 | 2001-01-30 | Hitachi, Ltd. | Trench gate type semiconductor device with current sensing cell |

| JPH11135512A (ja) * | 1997-10-31 | 1999-05-21 | Mitsubishi Electric Corp | 電力用半導体装置及びその製造方法 |

| JP4463888B2 (ja) * | 1998-09-25 | 2010-05-19 | Necエレクトロニクス株式会社 | 絶縁ゲート型半導体装置およびその製造方法 |

| JP3851776B2 (ja) * | 1999-01-11 | 2006-11-29 | フラウンホーファー−ゲゼルシャフト・ツール・フェルデルング・デル・アンゲヴァンテン・フォルシュング・アインゲトラーゲネル・フェライン | パワーmos素子及びmos素子の製造方法 |

| GB0002235D0 (en) * | 2000-02-02 | 2000-03-22 | Koninkl Philips Electronics Nv | Trenched schottky rectifiers |

| US6309929B1 (en) * | 2000-09-22 | 2001-10-30 | Industrial Technology Research Institute And Genetal Semiconductor Of Taiwan, Ltd. | Method of forming trench MOS device and termination structure |

| US6396090B1 (en) * | 2000-09-22 | 2002-05-28 | Industrial Technology Research Institute | Trench MOS device and termination structure |

-

2000

- 2000-09-22 US US09/668,663 patent/US6396090B1/en not_active Expired - Lifetime

-

2001

- 2001-09-21 EP EP01122746A patent/EP1191603A3/en not_active Withdrawn

- 2001-09-24 CN CNB011416785A patent/CN1209822C/zh not_active Expired - Lifetime

- 2001-09-25 JP JP2001292502A patent/JP4702822B2/ja not_active Expired - Lifetime

-

2010

- 2010-03-01 JP JP2010044627A patent/JP5379045B2/ja not_active Expired - Lifetime

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06151867A (ja) * | 1992-11-13 | 1994-05-31 | Sharp Corp | 縦型mosトランジスタおよびその製造方法 |

| JPH1174524A (ja) * | 1997-06-30 | 1999-03-16 | Denso Corp | 半導体装置及びその製造方法 |

| JP2000106435A (ja) * | 1998-09-29 | 2000-04-11 | Toshiba Corp | 電力用素子 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010157761A (ja) * | 2000-09-22 | 2010-07-15 | General Semiconductor Inc | 終端構造及びトレンチ金属酸化膜半導体素子 |

Also Published As

| Publication number | Publication date |

|---|---|

| US6396090B1 (en) | 2002-05-28 |

| CN1209822C (zh) | 2005-07-06 |

| JP2010157761A (ja) | 2010-07-15 |

| JP2002217426A (ja) | 2002-08-02 |

| JP5379045B2 (ja) | 2013-12-25 |

| EP1191603A2 (en) | 2002-03-27 |

| CN1348220A (zh) | 2002-05-08 |

| EP1191603A3 (en) | 2004-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4702822B2 (ja) | 終端構造及びトレンチ金属酸化膜半導体素子 | |

| JP5309058B2 (ja) | トレンチ金属酸化膜半導体素子及び終端構造の製造方法 | |

| JP5154347B2 (ja) | 超接合半導体ディバイスおよび超接合半導体ディバイスの製造方法 | |

| US11652166B2 (en) | Power device having super junction and Schottky diode | |

| US9385202B2 (en) | Semiconductor device having a patterned gate dielectric | |

| US10468402B1 (en) | Trench diode and method of forming the same | |

| TWI412071B (zh) | 自對準電荷平衡的功率雙擴散金屬氧化物半導體製備方法 | |

| KR100731141B1 (ko) | 반도체소자 및 그의 제조방법 | |

| JP2004522319A (ja) | ショットキー障壁を持つ半導体デバイスの製造 | |

| JP2002100772A (ja) | 電力用半導体装置及びその製造方法 | |

| JP2005510088A (ja) | 多結晶シリコンソースコンタクト構造を有するトレンチ金属酸化膜半導体電界効果トランジスタデバイス | |

| US8017494B2 (en) | Termination trench structure for mosgated device and process for its manufacture | |

| CN109755322B (zh) | 碳化硅mosfet器件及其制备方法 | |

| JP2010141310A (ja) | 半導体装置およびその製造方法 | |

| JPH09213951A (ja) | 半導体装置 | |

| TWI803288B (zh) | 集成的平面-溝道閘極功率mosfet | |

| CN113451296B (zh) | 具有横向绝缘栅极双极性晶体管的功率元件及其制造方法 | |

| CN116313787A (zh) | 带有超结结构的绝缘栅双极型晶体管及其制备方法 | |

| CN209766429U (zh) | 碳化硅mosfet器件 | |

| TW456049B (en) | Trench-type metal oxide semiconductor stop structure | |

| CN214203693U (zh) | 一种功率半导体、晶体管及电子器件 | |

| US11222974B2 (en) | Trench gate semiconductor device and method of manufacture | |

| TWI844185B (zh) | 半導體結構及其形成方法 | |

| US7319059B2 (en) | High density FET with self-aligned source atop the trench | |

| KR100776827B1 (ko) | 분할형 애노드를 갖는 절연 게이트 바이폴라 트랜지스터 및그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041112 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080430 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080730 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080804 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080901 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20080909 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20080930 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20081003 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081030 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090901 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20091201 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20091204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100104 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100114 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100201 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100204 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101109 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101220 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110201 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110303 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4702822 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |