JP4471480B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4471480B2 JP4471480B2 JP2000317991A JP2000317991A JP4471480B2 JP 4471480 B2 JP4471480 B2 JP 4471480B2 JP 2000317991 A JP2000317991 A JP 2000317991A JP 2000317991 A JP2000317991 A JP 2000317991A JP 4471480 B2 JP4471480 B2 JP 4471480B2

- Authority

- JP

- Japan

- Prior art keywords

- mos transistor

- electrode

- main electrode

- region

- oxide film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 57

- 238000002955 isolation Methods 0.000 claims description 137

- 238000000926 separation method Methods 0.000 claims description 32

- 239000000758 substrate Substances 0.000 claims description 28

- 239000004020 conductor Substances 0.000 claims description 23

- 239000012535 impurity Substances 0.000 claims description 23

- 230000015572 biosynthetic process Effects 0.000 claims description 19

- 239000010410 layer Substances 0.000 description 101

- 238000009792 diffusion process Methods 0.000 description 63

- 108091006146 Channels Proteins 0.000 description 47

- 238000010586 diagram Methods 0.000 description 34

- 230000005684 electric field Effects 0.000 description 34

- 101100345318 Arabidopsis thaliana MFP2 gene Proteins 0.000 description 17

- 229910052782 aluminium Inorganic materials 0.000 description 17

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 17

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 17

- 229920005591 polysilicon Polymers 0.000 description 17

- 101000896027 Rattus norvegicus 3-hydroxyacyl-CoA dehydrogenase Proteins 0.000 description 14

- 230000015556 catabolic process Effects 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 230000003071 parasitic effect Effects 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 239000000969 carrier Substances 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 230000000903 blocking effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 239000013078 crystal Substances 0.000 description 6

- 230000007547 defect Effects 0.000 description 6

- 239000011229 interlayer Substances 0.000 description 6

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 230000008878 coupling Effects 0.000 description 3

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 230000009977 dual effect Effects 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000003491 array Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 1

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 239000012925 reference material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

- H01L29/404—Multiple field plate structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/763—Polycrystalline semiconductor regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/088—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76286—Lateral isolation by refilling of trenches with polycristalline material

Description

【発明の属する技術分野】

本発明は半導体装置に関し、特に、電力用集積回路装置に内蔵される電力用半導体装置に関する。

【0002】

【従来の技術】

電力用半導体装置(パワーデバイス)と論理回路をワンチップ上に集積した電力用集積回路装置(パワーICあるいはHVIC:High Voltage IC)は、モーター制御をはじめとするメカトロニクス分野で高機能化と低コスト化を図るために欠かせない装置である。

【0003】

特に電力ラインのブリッジ整流を行う上で、ハイサイド(高電位)回路から発信される信号(ハイサイド信号)をローサイド(低電位)回路に伝えるハイサイドレベルシフトデバイスには、通常はPチャネルLHVMOS(Lateral High Voltage MOS)トランジスタや、PチャネルDAD(Dual Action Device)が使われている。

【0004】

PチャネルDADは、PチャネルLHVMOSトランジスタとNチャネルLHVMOSトランジスタを一体的に形成した構造を有し、PチャネルLHVMOSトランジスタと比較してオン電流密度を5倍以上に向上させることができる特徴がある(参考資料:K.Watabe et al.,IEEE Journal of Solid-state circuits,vol.33,No.9,September 1998 "An 0.8μm High-Voltage IC Using a Newly Designed 600-V Lateral P-Channel Dual-Action Device on SOI)。

【0005】

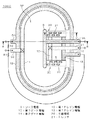

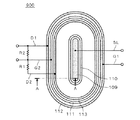

図30に従来のPチャネルDAD900の平面構成を示し、図31に、図30におけるA−A線での断面構成を示す。

【0006】

図30に示すように、PチャネルDAD900は直線状のソース電極109を中央部に有し、その外周を第1ゲート電極110が取り囲み、さらに外周を、第2ドレイン電極113、第2ゲート電極111、第1ドレイン電極112が順に取り囲む構造となっている。なお、何れの電極も長円環状をなしている。

【0007】

なお、ソース電極109、第1ゲート電極110、第2ドレイン電極112、第2ゲート電極111および第1ドレイン電極112にはそれぞれ、ソース配線SL、第1ゲート配線G1、第2ドレイン配線D2、第2ゲート配線G2および第1ドレイン配線D1が接続されている。

【0008】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2と第1ドレイン配線D1とは抵抗R2を介して電気的に接続されている。

【0009】

次に、図31を用いて断面構成について説明する。図31に示すようにPチャネルDAD900は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N型不純を比較的低濃度に含む:N-)が配設されたSOI基板上に形成される。

【0010】

図31において、SOI層102の表面内に、図に向かって左側からP型ウエル領域1031、P型ウエル領域1032およびN型ウエル領域104がそれぞれ独立して配設されている。また、P型ウエル領域1032とN型ウエル領域104との間には、P型ウエル領域1032に連続するようにP型ドレイン領域107(P型不純を比較的低濃度に含む:P-)が形成されている。なお、P型ドレイン領域107の形成深さは、P型ウエル領域1032よりも浅い。

【0011】

そして、P型ウエル領域1031の表面内には、図に向かって左側からP型拡散領域1051(P型不純を比較的高濃度に含む:P+)およびN型拡散領域1061(N型不純を比較的高濃度に含む:N+)が隣接して形成され、N型ウエル領域104の表面内には、図に向かって右側からN型拡散領域1062(N+)およびP型拡散領域1052(P+)が隣接して形成されている。

【0012】

また、SOI層102の第1の主面上には、P型拡散領域1051およびN型拡散領域1061を短絡するように接触して形成された第1ドレイン電極112、P型ウエル領域1032上に接触して形成された第2ドレイン電極113、P型拡散領域1052およびN型拡散領域1062を短絡するように接触して形成されたソース電極109が配設されている。

【0013】

さらに、絶縁ゲート電極として、P型ドレイン領域107の端縁部上から、(P型ドレイン領域107とN型ウエル領域104との間の)SOI層102上、N型ウエル領域104上およびP型拡散領域1052の端縁部上をカバーするように第1ゲート電極110が配設され、また、N型拡散領域1061の端縁部上から、P型ウエル領域1031上、(P型ウエル領域1031とP型ウエル領域1032との間の)SOI層102上、P型ウエル領域1032の端縁部上をカバーするように第2ゲート電極111が配設されている。なお、第1ゲート電極110および第2ゲート電極111はSOI層102との間にゲート絶縁膜GXを有している。

【0014】

また、支持基板100の第2の主面上には、全面に渡って裏面電極114が配設され、通常は接地電位に接続されている。

【0015】

次に動作について説明する。

まず、オフ状態(順方向阻止状態)は、第1ドレイン電極112と裏面電極114とを接地電位に接続して相互に短絡し、ソース電極109に電源電圧を与えて正電位とし、第1ゲート電極110をソース電極109に接続して短絡させることにより実現できる。なお、オフ状態下および以後説明するオン動作においても第2ゲート電極G2はフリー(外部から制御信号が与えられることはない)である。

【0016】

オン状態は、第1ゲート電極110の電位をソース電極109に対してマイナス側に制御することによって実現できる。すなわち、第1ゲート電極110の電位をソース電極109に対して低くすることで、第1ゲート電極110直下のN型ウエル領域104およびSOI層102の表面内でP型チャネルが形成され、P型拡散領域1052からP型ドレイン領域107に向かってホールが注入される。これは通常の横型PチャネルMOSトランジスタと同じ動作である。

【0017】

P型ドレイン領域107に注入されたホールは、第2ドレイン電極113を通り抵抗R1およびR2を経由して第1ドレイン電極112に到達するが、この際に、抵抗R1およびR2中にて発生した電位差が所定の値になった時点で第2ゲート電極111がゲートとして機能し、その直下のP型ウエル領域1031の表面内にN型チャネルが形成される。

【0018】

その結果、N型拡散領域1061からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域104、N型拡散領域1062を経由してソース電極109に到達する。これは横型NチャネルMOSトランジスタと同じ動作である。

【0019】

このように、PチャネルDADとは横型PチャネルMOSトランジスタと横型NチャネルMOSトランジスタとが一体的に複合したデバイスであり、電源側信号(ハイサイド信号)で第1ゲート電極110が制御され、オン状態ではNチャネルMOSFETが動作するので、オン抵抗を低減できるという利点があった。

【0020】

【発明が解決しようとする課題】

しかし、従来のPチャネルDAD900は以上のように構成されているため、P型拡散領域1052、N型ウエル領域104、SOI層102、P型ウエル領域1031、N型拡散領域1061で構成される、P/N/P/N構造を必然的に内蔵してしまい、この構造によって形成される寄生サイリスタがオンしてしまうと、デバイスはラッチアップ状態となり制御不能に陥るという問題があった。

【0021】

図32にPチャネルDAD900の等価回路図を示す。図32において、PチャネルMOSトランジスタQ1のソースにNPN型トランジスタQ3のエミッタが接続され、NPN型トランジスタQ3のコレクタがPNP型トランジスタQ4のベースに接続され、PNP型トランジスタQ4のコレクタがNPN型トランジスタQ3のベースに接続され、PNP型トランジスタQ4のエミッタが、NチャネルMOSトランジスタQ2のドレインに接続され、PチャネルDAD900のソース(S)−ドレイン(D)間にサイリスタが寄生した構成となっている。

【0022】

このような構成において、電子およびホールが高密度に注入されると、モジュレーションを引き起こし、ラッチアップ状態になる可能性がある。

【0023】

本発明は上記のような問題点を解消するためになされたもので、ラッチアップ耐性を向上し、耐電圧特性を安定させたDADを提供することを目的とする。

【0024】

【課題を解決するための手段】

本発明に係る請求項1記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、平面視形状が直線状の第1の主電極と、前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、前記第2のMOSトランジスタは、前記第2のMOSトランジスタの前記第1の主電極の平面視形状が、前記第1のMOSトランジスタの前記第1の主電極を中心部として囲み、前記第1のMOSトランジスタを内包する長円環状であって、その内側に沿って配設され、その開口部に前記第1のMOSトランジスタを配置した平面視形状がC字形状の制御電極と、第2の主電極とを備え、前記第2の主電極は、前記第1のMOSトランジスタの前記第1の主電極と共通の電極であり、前記分離構造は、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る分離領域を備え、前記分離領域は、PN接合分離のための不純物領域によってその外形が規定され、前記不純物領域内に配設され、前記SOI基板を構成する埋め込み酸化膜に達する複数のトレンチを備え、前記複数のトレンチは、前記第1のMOSトランジスタの前記第1の主電極側から前記第2の主電極側に向けて少なくとも一列に配列され、それぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

【0026】

本発明に係る請求項2記載の半導体装置は、前記第2のMOSトランジスタの前記第1の主電極よりも内側の前記SOI層の上部に、前記第1のMOSトランジスタの前記第1の主電極を中心として同心状に複数配設されたマルチフィールドプレートをさらに備え、前記複数のトレンチの前記配列方向に沿ったトレンチ幅およびトレンチ間隔は、前記マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定される。

【0027】

本発明に係る請求項3記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、同心構造の中心をなす第1の主電極と、前記第1の主電極を囲む制御電極と、前記制御電極を囲む第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、前記第1のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1のトレンチ分離壁と、前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第2のトレンチ分離壁とを備え、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

【0028】

本発明に係る請求項4記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、同心構造の最外周をなす第1の主電極と、前記第1の主電極の内側に沿って配設された制御電極と、同心構造の中心をなす第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続されている。

【0029】

本発明に係る請求項5記載の半導体装置は、支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、前記第1のMOSトランジスタが、平面視形状が直線状の第1の主電極と、前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、前記第2のMOSトランジスタは、同心構造の最外周をなす前記第1の主電極と、同心構造の中心をなす第2の主電極と、前記第1の主電極の内側に沿って配設された制御電極とを備え、前記分離構造は、比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、前記第1および第2のトレンチ分離壁のそれぞれは、内壁を覆う内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、第1のトレンチ分離壁は、前記第1のMOSトランジスタの前記第1の主電極、前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1の主電極、前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る側面分離壁と、前記第1のMOSトランジスタの前記第1の主電極および前記第2の主電極の外側に配設された第1および第2の分離壁とを有し、前記側面分離壁と前記第1および第2の分離壁とで前記第1のMOSトランジスタを囲み、前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される。

【0030】

本発明に係る請求項6記載の半導体装置は、前記側面分離壁は、前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数のトレンチを有し、前記複数のトレンチのそれぞれは、前記内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、前記複数のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列される。

【0031】

本発明に係る請求項7記載の半導体装置は、前記側面分離壁が、前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数の第1のトレンチと、前記複数の第1のトレンチの配列の端縁部に配設された平面視形状が矩形の複数の第2のトレンチとを有し、前記複数の第1および第2のトレンチのそれぞれは、前記内壁酸化膜と、前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、前記複数の第1のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列され、前記複数の第2のトレンチは、前記複数の第1のトレンチ間の前記SOI層の端部を塞ぐように配列され、前記複数の第1のトレンチの前記内壁酸化膜と前記複数の第2のトレンチの前記内壁酸化膜とが互いに接合して一体化している。

【0033】

【発明の実施の形態】

<A.実施の形態1>

<A−1.装置構成>

本発明に係る実施の形態1として、図1〜図4を用いてPチャネルDAD(Dual Action Device)1000の構成について説明する。

【0034】

<A−1−1.平面構成>

図1はPチャネルDAD1000の平面構成を示す図である。図1に示すように、PチャネルDAD1000は直線状のソース電極9を中央部に有し、ソース電極9を取り囲むように、長円環状の第1ドレイン電極12が配設されている。また、第1ドレイン電極12の内周に沿ってC字形状の第2ゲート電極11が配設されている。

【0035】

また、ソース電極9に平行するように第1ゲート電極10が配設され、第1ゲート電極10に平行するように第2ドレイン電極13が配設されている。第1ゲート電極10および第2ドレイン電極13はソース電極9の長さを超えない長さの直線状の電極であり、各々の両端部には分離領域20(分離構造)が配設され、2つの分離領域20とソース電極9とで囲まれる領域が、PチャネルMOSトランジスタが形成されるPチャネルMOS領域PRとなる。

【0036】

そして、第2ゲート電極11は2つの分離領域20の手前に端部を有し、PチャネルMOS領域はC字形状の開口部から内側にかけて配設されたレイアウトとなっている。

【0037】

また、ソース電極9と、それを囲む第2ゲート電極11および第1ドレイン電極12によってNチャネルMOSトランジスタが形成され、PチャネルMOS領域PRの3方を囲むようにNチャネルMOS領域NRが配設されたレイアウトとなっている。

【0038】

ソース電極9、第1ゲート電極10および第2ドレイン電極13にはそれぞれソース配線SL、第1ゲート配線G1、第2ドレイン配線D2が接続されている。

【0039】

ソース配線SLおよび第1ゲート配線G1は、例えば第2層アルミ配線で構成され、ソース配線SLは第1ゲート電極10および第2ドレイン電極13上をオーバーラップするように配設され、第1ゲート配線G1は第2ドレイン電極13上をオーバーラップするように配設されている。

【0040】

また、第2ゲート電極11および第1ドレイン電極12には、それぞれ第2ゲート配線G2および第1ドレイン配線D1が接続されている。なお第2ゲート配線G1は、例えば第2層アルミ配線で構成され、第2ドレイン配線D2は、例えば第1層アルミ配線で構成されている。

【0041】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2と第1ドレイン配線D1とは抵抗R2を介して電気的に接続されている。

【0042】

なお、第1ゲート電極10および第2ゲート電極11は不純物を含んだドープトポリシリコンで構成され、第1ゲート配線G1および第2ゲート配線G2とはコンタクトホールにより接続される構成となっている。

【0043】

分離領域20は、平面視形状がほぼ矩形になるように配設されたP型不純物領域内に、トレンチ21が複数配設されたマルチトレンチ構造となっている。各トレンチ21にはポリシリコン等の導電体が充填されており、充填された各導電体は他の特定の部位と電気的に接続されることなく形成されている。なお、分離領域20の構成については後にさらに説明する。

【0044】

<A−1−2.主要部断面構成>

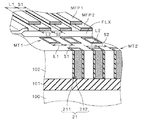

図1におけるB−B線での断面構成を図2に示す。図2に示すようにPチャネルDAD1000は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N型不純を比較的低濃度に含む:N-)が配設されたSOI基板上に形成される。

【0045】

図2において、SOI層102の表面内に、図に向かって左側からP型ウエル領域31、N型ウエル領域4、P型ウエル領域32(P型不純を比較的高濃度に含む:P+)およびP型ウエル領域31が、それぞれ独立して配設されている。なお、左右端にあるP型ウエル領域31は平面視形状が長円環状の連続した不純物領域の断面である。

【0046】

また、P型ウエル領域32とN型ウエル領域4との間には、P型ウエル領域32に連続するようにP型ドレイン領域7(P型不純を比較的低濃度に含む:P-)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域32よりも浅い。

【0047】

そして、図に向かって左側のP型ウエル領域31の表面内には、図に向かって左側からP型拡散領域51(P型不純を比較的高濃度に含む:P+)およびN型拡散領域61(N型不純を比較的高濃度に含む:N+)が隣接して配設され、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62(N+)およびP型拡散領域52(P+)が隣接して配設され、図に向かって右側のP型ウエル領域31の表面内にはP型拡散領域51が配設されている。

【0048】

また、P型ウエル領域31とN型ウエル領域4との間のSOI層102の表面上にはフィールド酸化膜FLXが配設されている。なお、当該フィールド酸化膜FLXは、P型ドレイン領域7およびP型ウエル領域32の表面上にも配設されている。

【0049】

さらに、フィールド酸化膜FLXの上部には、マルチフィールドプレートMFP2が配設されている。なお、マルチフィールドプレートMFP2の構成については後にさらに説明する。

【0050】

そして、SOI層102の第1の主面上には、P型拡散領域51およびN型拡散領域61を短絡するように接触して形成された第1ドレイン電極12、P型ウエル領域32上に接触して形成された第2ドレイン電極13、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極9が配設されている。

【0051】

さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10が配設され、また、N型拡散領域61の端縁部上から、P型ウエル領域31上およびSOI層102上をカバーするように第2ゲート電極11が配設されている。なお、第1ゲート電極10および第2ゲート電極11はポリシリコンで構成され、ゲート絶縁膜GXによって絶縁されている。そして、どちらもフィールド酸化膜FLXの端部に一部が係合している。

【0052】

また、第2ドレイン電極13とフィールド酸化膜FLXとの間のP型ウエル領域32上には、第2ゲート電極11と同じ工程で形成されたゲート電極11aが配設され、N型ウエル領域4の端縁部上部からSOI層102上をカバーするように第1ゲート電極10と同じ工程で形成されたゲート電極10aが配設されている。なお、ゲート電極10aおよび11aはゲート絶縁膜GXによって絶縁され、どちらもフィールド酸化膜FLXの端部に一部が係合している。

【0053】

そして、SOI層102の第1の主面上を覆うように、層間絶縁膜IZが配設されている。なお、層間絶縁膜IZはソース電極9の上部が開口部となっており、ソース配線SLは当該開口部においてソース電極9と接続し、さらに層間絶縁膜IZの上部に配設されている。

【0054】

また、層間絶縁膜IZおよびソース配線SLを覆うようにガラス等の保護膜GZが配設されている。

【0055】

また、支持基板100の第2の主面上には、全面に渡って裏面電極14が配設されている。

【0056】

<A−1−3.分離領域の断面構成>

次に、図1におけるC−C線での断面構成、すなわち分離領域20の断面構成を図3に示す。図3に示すように分離領域20は、N型ウエル領域4とP型ウエル領域31とで挟まれるSOI層102の表面内に、埋め込み酸化膜101に達するように配設されたP型不純物領域33(P型不純を比較的高濃度に含む:P+)と、P型不純物領域33を貫通するように配設された複数のトレンチ21で構成されるマルチトレンチ構造とを有している。

【0057】

このP型不純物領域33は、PN接合分離のための不純物領域であり、PチャネルMOS領域PRとNチャネルMOS領域NRとの電気的な分離は、PN接合分離により達成される。この配設領域が分離領域20の外形を規定している。

【0058】

トレンチ21のそれぞれは、内壁酸化膜211によって壁面が覆われ、内壁酸化膜211で囲まれた領域にドープトポリシリコン等の導電体212が埋め込まれた構成となっている。

【0059】

そして、マルチトレンチ構造部分を覆うようにP型不純物領域33の表面にフィールド酸化膜FLXが配設され、フィールド酸化膜FLXの上部には、ポリシリコンで構成されるマルチフィールドプレートMFP2が配設されている。

【0060】

また、フィールド酸化膜FLXの端部に係合するようにゲート電極10aおよび11aが配設されているが、ゲート電極10aは第1ゲート電極10とは電気的には接続されず、ソース電極9に接続されるか、フローティング状態となり、ゲート電極11aは第2ゲート電極11とは電気的には接続されず、第1ドレイン電極12に接続されるか、フローティング状態となっている。

【0061】

これは、ゲート電極10aおよび11aを電界緩和のためのフィールドプレートとして使用するための構成である。また、分離領域20を挟むN型ウエル領域4およびP型ウエル領域31においては、MOSデバイスとしての機能は不要であるので、P型拡散領域52およびN型拡散領域61も不要となるが、図3中においては位置関係を明白にするため破線で示している。

【0062】

また、分離領域20の上部を覆うように層間絶縁膜IZが配設され、層間絶縁膜IZ上にはマルチフィールドプレートMFP1が配設されている。マルチフィールドプレートMFP1は、ソース電極9および第1ドレイン電極12と同様にアルミニウム等の金属によって構成され、マルチフィールドプレートMFP2の間隙の上部を覆うように配設されている。

【0063】

なお、その他、図2に示す断面構成と同一の構成については同一の符号を付し、重複する説明は省略する。

【0064】

<A−2.動作>

次に図1〜図3を用いてPチャネルDAD1000の動作について説明する。

【0065】

PチャネルDAD1000のオン、オフ動作は、従来のPチャネルDAD900と基本的には同様であるが、オン動作時には、まずPチャネルMOS領域PRにおいて、第1ゲート電極10直下のN型ウエル領域4およびSOI層102の表面内で形成されるP型チャネルを通って、P型拡散領域52からP型ドレイン領域7に向かって注入されるホールは、第2ドレイン電極13に流れ込み、第2ドレイン電極13から第2ドレイン配線D2を通って第1ドレイン電極12に流れる。

【0066】

一方、ホール電流によって抵抗R1およびR2中にて発生した電位差が所定の値になると、第2ゲート電極11がゲートとして機能し、その直下のP型ウエル領域31の表面内に形成されたN型チャネルを通ってN型拡散領域61からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域4、N型拡散領域62を経由してソース電極109に到達するが、PチャネルMOS領域PRは分離領域20によってNチャネルMOS領域NRと電気的に分離され、ホールは直接にNチャネルMOS領域NRを流れることがなく、また電子もPチャネルMOS領域PRを直接に流れることがない。すなわちホールおよび電子は分離領域20によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【0067】

また、分離領域20においてはマルチトレンチ構造により、順方向阻止電圧印加時にソース・ドレイン間で発生する電界を各トレンチ21ごとに分担することができ、分離領域20における電界集中を緩和することができる。

【0068】

さらに、マルチフィールドプレートと組み合わせて用いることで、分離領域20における電界集中をさらに緩和することができる。

【0069】

<A−3.マルチトレンチ構造およびマルチフィールドプレート>

以下、図4〜図15を用いて、マルチトレンチ構造およびマルチフィールドプレートについて説明する。

【0070】

図4に、マルチトレンチ構造およびマルチフィールドプレートの構成を斜視図で示す。

【0071】

図4に示すように、マルチトレンチ構造はトレンチ21の配列を複数有し、隣り合う配列ではトレンチが互い違いになるように配設されている。

【0072】

また、マルチトレンチ構造の上部を覆うフィールド酸化膜FLX上には、ドープトポリシリコンで構成されるマルチフィールドプレートMFP2が配設され、さらに上部には、マルチフィールドプレートMFP2とは互い違いになるように配列されたアルミニウム等の金属で構成されるマルチフィールドプレートMFP1が配設されている。

【0073】

ここで、トレンチ配列のある一列をMT1とし、その配列方向に沿ったトレンチ幅(ライン)およびトレンチ間隔(スペース)を、各々L1およびS1とする。

【0074】

同様に別の一列をMT2とし、そのラインおよびスペースをL2およびS2とする。

【0075】

さらに、マルチフィールドプレートMFP1およびMFP2の、その配列方向に沿ったプレート幅(ライン)およびプレート間隔(スペース)を、それぞれL1およびS1、L2およびS2とすると、トレンチ配列MT2とマルチフィールドプレートMFP2とはラインおよびスペースが一致するので、マルチフィールドプレートMFP2の個々のフィールドプレートが、トレンチ配列MT2の個々のトレンチ21の上部に重なることになり、またトレンチ配列MT1とマルチフィールドプレートMFP1とはラインおよびスペースが一致するので、マルチフィールドプレートMFP1の個々のフィールドプレートが、トレンチ配列MT1の個々のトレンチ21の上部に重なることになる。

【0076】

なお、ラインL1およびL2とスペースS1およびS2は数値的には同じでも良く、例えばラインL1およびL2は何れも10〜20μm、スペースS1およびS2も10〜20μmとすれば良い。その場合、トレンチ配列MT1とMT2との間隔はトレンチ21の間隔で定義すれば2〜3μm、トレンチ21のラインと直交する方向の長さは2〜3μm程度とすれば良い。

【0077】

以上のように配設されたマルチトレンチ構造およびマルチフィールドプレートによる作用効果について図5を用いて説明する。

【0078】

図5は、トレンチ配列MT1とマルチフィールドプレートMFP1との組み合わせによる作用効果を説明する断面図である。なお、図5は図3に示す構成を拡大して示した図であるので、図3と同一の構成については同一の符号を付し、重複する説明は省略する。

【0079】

図5において、順方向阻止電圧印加時にソース・ドレイン間で発生する電界は、その大部分が埋め込み酸化膜101中を通り、さらにトレンチ21の内壁酸化膜211を通ってフィールド酸化膜FLXの上部に達する。このとき、トレンチ配列MT1の上部にはマルチフィールドプレートMFP1が位置するので、電界はマルチフィールドプレートMFP1の各プレートの端縁部に沿って延在し、局所的な電界集中が発生することが防止される。

【0080】

なお、埋め込み酸化膜101中では電界密度が高くなっているが、シリコン酸化膜の絶縁破壊強度は、シリコンの10倍以上あるので、電界集中による耐圧特性の低下を防止できる。

【0081】

このように、トレンチ21の内壁酸化膜211を電界の通過経路とすることで、シリコン層中での局所的な電界の集中を効果的に防止して、耐圧特性の保持と安定化を図ることができる。従って、分離領域20を配設することで耐圧の低下を招く心配がなく、確実にラッチアップ特性の改善を図ることができる。

【0082】

また、マルチトレンチ構造によって分配された電界分布は、マルチフィールドプレートによっても維持され、マルチトレンチ構造との組み合わせにより、シリコン層中での局所的な電界の集中をより効果的に防止することができる。

【0083】

<A−4.マルチトレンチ構造の製造方法>

次に、図6〜図9を用いてマルチトレンチ構造の製造方法について説明する。

【0084】

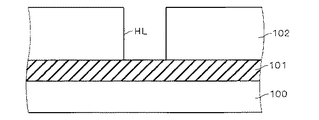

まず、図6に示す工程においてSOI層102を貫通する開口部HLを複数形成する。この複数の開口部HLはトレンチ21の外形形状と配列に合わせて形成すれば良い。

【0085】

次に、図7に示す工程において、開口部HLの壁面に内壁酸化膜211を形成するために、SOI層102の全面に厚さ100nm(1000オングストローム)程度のシリコン酸化膜OX1を形成する。

【0086】

次に、図8に示す工程において、ドープトポリシリコン212を全面に形成した後、エッチバックにより除去して、開口部HL内にのみドープトポリシリコン212を残すようにする。

【0087】

その後、SOI層102上のシリコン酸化膜OX1を除去し、フィールド酸化を行って、フィールド酸化膜FLXを形成することで、フィールド酸化膜FLXの下部にマルチトレンチ構造を有した構成を得る。

【0088】

<A−5.マルチフィールドプレートの変形例1>

以上の説明においては、マルチフィールドプレートMFP1およびMFP2の2層を有する構成について説明したが、マルチフィールドプレートは必ずしも2層である必要はなく、1層または3層以上であっても良い。

【0089】

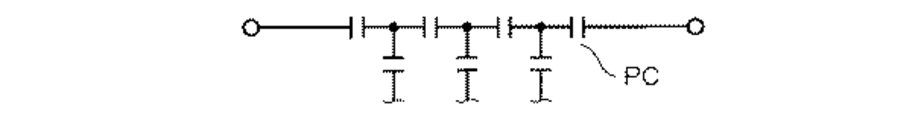

図10には、フィールド酸化膜FLX上にマルチフィールドプレートMFP2だけを有する構成を示す。

【0090】

このような構成を採ることで、マルチフィールドプレートの形成工程を簡略化できるが、容量性結合力は低下する。

【0091】

図11は、図10の構成における容量成分PCを等価回路として示した図である。

【0092】

また、図12は、フィールド酸化膜FLX上にマルチフィールドプレートMFP2を有し、さらに上層にマルチフィールドプレートMFP1を有する構成を示し、図13には、図12の構成における容量成分PCを等価回路として示す。

【0093】

図11と図13とを比較することで、マルチフィールドプレートを複数層有することで、容量性結合を飛躍的に強化できることが判る。

【0094】

従って、マルチフィールドプレートを3層以上とすれば、さらに容量性結合を強化でき、耐圧特性を安定化できるという効果が得られる。

【0095】

<A−6.マルチフィールドプレートの変形例2>

また、図3〜図5においては、マルチフィールドプレートMFP1およびMFP2が、分離領域20の上部にオーバーラップする構成を示したが、マルチフィールドプレートMFP1およびMFP2が、分離領域20の上部においてオーバーラップしない構成であっても良い。

【0096】

すなわち、マルチフィールドプレートは横型高耐圧デバイスにおいて、ソース・ドレイン間の電界緩和のために、ソース・ドレイン間のフィールド酸化膜の上部に配設されるものであり、分離領域20の上部だけに配設されるものではない。

【0097】

図14はマルチフィールドプレートの配設状態を示すためのPチャネルDAD1000の部分平面図である。図14においては、マルチフィールドプレートMFP2だけを示しており、マルチフィールドプレートMFP2がソース電極9と第1ドレイン電極12との間に配設されていることが判る。

【0098】

分離領域20においては、図5を用いて説明したように、マルチトレンチ構造によりソース・ドレイン間の電界を緩和できるので、マルチフィールドプレートを設けずとも、電界緩和が達成できる。

【0099】

逆に、分離領域20においてマルチフィールドプレートを省略することで、図15に示すような構成を採ることも可能となる。

【0100】

図15は、分離領域20上においてはマルチフィールドプレートを形成せず、NチャネルMOS領域NRにおいてはマルチフィールドプレートMFPXを形成し、PチャネルMOS領域PRにおいてはマルチフィールドプレートMFPYを形成する構成となっている。

【0101】

そして、分離領域20においては、外形寸法が異なるトレンチの配列を複数設け、各トレンチ配列ごとにラインおよびスペースを変えた構成としても良い。

【0102】

図15においては、トレンチ21aの配列、トレンチ21bの配列、トレンチ21cの配列の3種類の配列が示されている。なお、NチャネルMOS領域NRに最も近いトレンチ21aのライン(配列方向に沿ったトレンチ幅)が最も長く、PチャネルMOS領域PRに最も近いトレンチ21cのラインが最もラインが短くなるように配設されている。

【0103】

また、マルチフィールドプレートMFPXのプレート幅は、トレンチ21aのラインと同等に設定され、マルチフィールドプレートMFPYのプレート幅は、トレンチ21cのラインと同等に設定されている。

【0104】

このように構成することで、マルチフィールドプレートMFPXとトレンチ21aとの境界部における電界集中を緩和し、耐圧特性を安定化できるという効果が得られる。

【0105】

<B.実施の形態2>

<B−1.装置構成>

本発明に係る実施の形態2として、図16および図17を用いてPチャネルDAD2000の構成について説明する。

【0106】

<B−1−1.平面構成>

図16はPチャネルDAD2000の平面構成を示す図である。図16に示すように、PチャネルDAD2000は、PチャネルMOS領域PRとNチャネルMOS領域NRとがトレンチ分離壁610によって電気的に分離され、さらにPチャネルMOS領域PRがトレンチ分離壁610および620(第1のトレンチ分離壁)によって囲まれて独立し、NチャネルMOS領域NRがトレンチ分離壁610および630(第2のトレンチ分離壁)によって囲まれて独立している。

【0107】

また、ハイサイド(高電位)領域HRもトレンチ分離壁640によって囲まれて独立している。なお、トレンチ分離壁610〜640は、PチャネルMOS領域PRとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。

【0108】

PチャネルMOS領域PRにおいては、直線状のソース電極91Aを中央部に有し、ソース電極91Aを取り囲むように、長円環状の第1ゲート電極10Aが配設され、第1ゲート電極10Aを取り囲むように、長円環状の第2ドレイン電極13Aが配設されてPチャネルMOSトランジスタを構成している。

【0109】

そして、ソース電極91A、第1ゲート電極10Aおよび第2ドレイン電極13Aにはそれぞれソース配線SL1、第1ゲート配線G1、第2ドレイン配線D2が接続されている。

【0110】

ソース配線SL1および第1ゲート配線G1は、例えば第2層アルミ配線で構成され、ソース配線SL1は第1ゲート電極10Aおよび第2ドレイン電極13A上をオーバーラップし、第1ゲート配線G1は第2ドレイン電極13A上をオーバーラップし、さらにトレンチ分離壁620および640上をオーバーラップしてハイサイド領域HRにまで延在している。

【0111】

また、第2ドレイン配線D2は、例えば第1層アルミ配線で構成され、トレンチ分離壁620上をオーバーラップし、ハイサイド領域HR側のPチャネルMOS領域PR外部に延在している。

【0112】

NチャネルMOS領域NRにおいては、直線状の第1ドレイン電極12Aを中央部に有し、第1ドレイン電極12Aを取り囲むように、長円環状の第2ゲート電極11Aが配設され、第2ゲート電極11Aを取り囲むように、長円環状のソース電極92Aが配設されてNチャネルMOSトランジスタを構成している。

【0113】

そして、第1ドレイン電極12A、第2ゲート電極11Aおよびソース電極92Aには、それぞれ第1ドレイン配線D1、第2ゲート配線G2およびソース配線SL2が接続されている。

【0114】

ソース配線SL2および第2ゲート配線G2は、例えば第2層アルミ配線で構成され、ソース配線SL2はトレンチ分離壁620上をオーバーラップし、第2ゲート配線G2はソース電極92A上およびトレンチ分離壁620上をオーバーラップして、ハイサイド領域HR側のNチャネルMOS領域NR外部に延在している。

【0115】

また、第1ドレイン配線D1は、例えば第1層アルミ配線で構成され、第2ゲート電極11Aおよびソース電極92A上をオーバーラップし、さらにトレンチ分離壁620上をオーバーラップして、ハイサイド領域HRとは反対側のNチャネルMOS領域NR外部に延在している。

【0116】

なお、第1ゲート電極10Aおよび第2ゲート電極11Aはドープトポリシリコンで構成され、第1ゲート配線G1および第2ゲート配線G2とはコンタクトホールにより接続される構成となっている。

【0117】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2とソース配線SL2とは抵抗R2を介して電気的に接続されている。

【0118】

なお、以上の説明においては、PチャネルMOSトランジスタおよびNチャネルMOSトランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【0119】

<B−1−2.主要部断面構成>

図16におけるX−X線での断面構成を図17に示す。図17に示すようにPチャネルDAD2000は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N-)が配設されたSOI基板上に形成される。

【0120】

図17に示すように、PチャネルMOS領域PRにおいては、SOI層102の表面内に、図に向かって左側からN型ウエル領域4、P型ウエル領域321(P+)がそれぞれ独立して配設されている。

【0121】

また、P型ウエル領域321とN型ウエル領域4との間には、P型ウエル領域321に連続するようにP型ドレイン領域7(P-)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域321よりも浅い。

【0122】

そして、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62(N+)およびP型拡散領域52(P+)が隣接して配設されている。なお、N型ウエル領域4およびN型拡散領域62(N+)は必ずしも配設する必要はないので破線で示している。

【0123】

また、SOI層102の第1の主面上には、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極91A、P型ウエル領域321上に接触して形成された第2ドレイン電極13A、さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10Aが配設されている。

【0124】

NチャネルMOS領域NRにおいては、SOI層102の表面内に、図に向かって右側からN型ウエル領域611(N+)、P型ウエル領域322(P+)がそれぞれ独立して配設されている。

【0125】

また、P型ウエル領域322の表面内には、N型拡散領域62(N+)が配設されている。

【0126】

また、SOI層102の第1の主面上には、N型拡散領域62およびP型ウエル領域322を短絡するように接触して形成されたソース電極92A、N型ウエル領域611上に接触して形成された第1ドレイン電極12A、さらに、絶縁ゲート電極として、N型拡散領域62の端縁部上から、P型ウエル領域322上およびSOI層102上をカバーするように第2ゲート電極11Aが配設されている。

【0127】

なお、P型ウエル領域322とN型ウエル領域611との間のSOI層102の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P型ドレイン領域7およびP型ウエル領域32の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

【0128】

また、NチャネルMOS領域NRとPチャネルMOS領域PRとの間のトレンチ分離壁610は、SOI層102を貫通して埋め込み酸化膜101に達するトレンチの内壁を内壁酸化膜601で覆い、内壁酸化膜601で囲まれる領域にドープトポリシリコン等の導電体602が埋め込まれた構成となっている。そして、トレンチ分離壁610の上部にはフィールド酸化膜FLXが配設されている。この構造は、トレンチ分離壁620および630においても同様である。

【0129】

なお、トレンチ分離壁610の両側面は、埋め込み酸化膜101に達するP型ウエル領域321および322で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い、デバイス内に結晶欠陥に起因するリーク電流が流れないようにするための構成である。

【0130】

<B−2.動作>

次に図16および図17を用いてPチャネルDAD2000の動作について説明する。

【0131】

PチャネルDAD2000のオン動作は、ハイサイド領域HRからのゲート信号が第1ゲート電極10Aに与えられると、まずPチャネルMOS領域PRにおいて、第1ゲート電極10A直下のN型ウエル領域4およびSOI層102の表面内で形成されるP型チャネルを通って、P型拡散領域52からP型ドレイン領域7に向かってホールが注入される。ホールは、第2ドレイン電極13Aに流れ込み、第2ドレイン電極13Aから第2ドレイン配線D2を通ってソース電極92Aに流れる。

【0132】

一方、ホール電流によって抵抗R1およびR2中にて発生した電位差が所定の値になると、第2ゲート電極11Aがゲートとして機能し、その直下のP型ウエル領域322の表面内に形成されたN型チャネルを通ってN型拡散領域62からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域611を経由して第1ドレイン電極12Aに到達し、図示しないローサイド(低電位)領域に電気的に接続された第1ドレイン電極12Aの電位が制御されることになる。

【0133】

このように、PチャネルMOS領域PRとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることがなく、また電子もPチャネルMOS領域PRを直接に流れることがないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【0134】

なお、図17に示すように、PチャネルMOS領域PRにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

【0135】

<C.実施の形態3>

<C−1.装置構成>

本発明に係る実施の形態3として、図18および図19を用いてPチャネルDAD3000の構成について説明する。

【0136】

<C−1−1.平面構成>

図18はPチャネルDAD3000の平面構成を示す図である。図18に示すように、PチャネルDAD3000は、NチャネルMOS領域NRがトレンチ分離壁650(第2のトレンチ分離壁)によって囲まれて独立し、また、PチャネルMOSトランジスタPTがハイサイド領域HRに形成され、ハイサイド領域HRもトレンチ分離壁640(第1のトレンチ分離壁)によって囲まれて独立している。なお、トレンチ分離壁640および650は、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。

【0137】

PチャネルMOSトランジスタPTは、円形のドレイン電極13Bを中央部に有し、ドレイン電極13Bを取り囲むように、円環状の第1ゲート電極10Bが配設され、第1ゲート電極10Bを取り囲むように、円環状のソース電極91Bが配設されて構成されている。

【0138】

そして、ソース電極91B、第1ゲート電極10Bおよび第2ドレイン電極13Bにはそれぞれソース配線SL1、第1ゲート配線G1、第2ドレイン配線D2が接続されている。

【0139】

ソース配線SL1および第1ゲート配線G1は、例えば第2層アルミ配線で構成され、第1ゲート配線G1はソース電極91B上をオーバーラップして、ハイサイド領域HR内に延在している。

【0140】

また、第2ドレイン配線D2は、例えば第1層アルミ配線で構成され、第1ゲート電極10B、ソース電極91Bおよびトレンチ分離壁620上をオーバーラップして、NチャネルMOS領域NR側のハイサイド領域HR外部に延在している。

【0141】

NチャネルMOS領域NRにおいては、直線状の第1ドレイン電極12Bを中央部に有し、第1ドレイン電極12Bを取り囲むように、長円環状の第2ゲート電極11Bが配設され、第2ゲート電極11Bを取り囲むように、長円環状のソース電極92Bが配設されてNチャネルMOSトランジスタを構成している。

【0142】

そして、第1ドレイン電極12B、第2ゲート電極11Bおよびソース電極92Bには、それぞれ第1ドレイン配線D1、第2ゲート配線G2およびソース配線SL2が接続されている。

【0143】

ソース配線SL2および第2ゲート配線G2は、例えば第2層アルミ配線で構成され、ソース配線SL2はトレンチ分離壁650上をオーバーラップし、第2ゲート配線G2はソース電極92B上およびトレンチ分離壁650上をオーバーラップして、ハイサイド領域HR側のNチャネルMOS領域NR外部に延在している。

【0144】

また、第1ドレイン配線D1は、例えば第1層アルミ配線で構成され、第2ゲート電極11Bおよびソース電極92B上をオーバーラップし、さらにトレンチ分離壁650上をオーバーラップして、ハイサイド領域HRとは反対側のNチャネルMOS領域NR外部に延在している。

【0145】

なお、第1ゲート電極10Bおよび第2ゲート電極11Bはドープトポリシリコンで構成され、第1ゲート配線G1および第2ゲート配線G2とはコンタクトホールにより接続される構成となっている。

【0146】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2とソース配線SL2とは抵抗R2を介して電気的に接続されている。

【0147】

なお、以上の説明においては、NチャネルMOSトランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【0148】

また、PチャネルMOSトランジスタは、円環の同心形状を有するものとして説明したが、この形状に限定されるものではなく、長円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【0149】

<C−1−2.主要部断面構成>

図18におけるY−Y線での断面構成を図19に示す。図19に示すようにPチャネルDAD3000は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N-)が配設されたSOI基板上に形成される。

【0150】

図19に示すように、PチャネルMOSトランジスタPTにおいては、SOI層102の表面内に、図に向かって左側からP型ウエル領域321(P+)、N型ウエル領域4がそれぞれ独立して配設されている。

【0151】

また、P型ウエル領域321とN型ウエル領域4との間には、P型ウエル領域321に連続するようにP型ドレイン領域7(P-)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域321よりも浅い。

【0152】

そして、N型ウエル領域4の表面内には、図に向かって左側からP型拡散領域52(P+)およびN型拡散領域62(N+)が隣接して配設されている。なお、N型ウエル領域4およびN型拡散領域62(N+)は必ずしも配設する必要はないので破線で示している。

【0153】

また、SOI層102の第1の主面上には、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極91B、P型ウエル領域321上に接触して形成された第2ドレイン電極13B、さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10Bが配設されている。

【0154】

NチャネルMOS領域NRにおいては、SOI層102の表面内に、図に向かって右側からN型ウエル領域611(N+)、P型ウエル領域322(P+)がそれぞれ独立して配設されている。

【0155】

また、P型ウエル領域322の表面内には、N型拡散領域62(N+)が配設されている。

【0156】

また、SOI層102の第1の主面上には、N型拡散領域62およびP型ウエル領域322を短絡するように接触して形成されたソース電極92B、N型ウエル領域611上に接触して形成された第1ドレイン電極12B、さらに、絶縁ゲート電極として、N型拡散領域62の端縁部上から、P型ウエル領域322上およびSOI層102上をカバーするように第2ゲート電極11Bが配設されている。

【0157】

なお、P型ウエル領域322とN型ウエル領域611との間のSOI層102の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P型ドレイン領域7およびP型ウエル領域32の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

【0158】

また、トレンチ分離壁650および660は、SOI層102を貫通して埋め込み酸化膜101に達するトレンチの内壁を内壁酸化膜601で覆い、内壁酸化膜601で囲まれる領域にドープトポリシリコン等の導電体602が埋め込まれた構成となっている。そして、トレンチ分離壁650および660の上部にはフィールド酸化膜FLXが配設されている。

【0159】

なお、トレンチ分離壁660の両側面は、埋め込み酸化膜101に達するP型ウエル領域323で覆われ、トレンチ分離壁650の両側面は、埋め込み酸化膜101に達するP型ウエル領域322および323で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い、デバイス内に結晶欠陥に起因するリーク電流が流れないようにするための構成である。

【0160】

<C−2.動作>

次に図18および図19を用いてPチャネルDAD3000の動作について説明する。

【0161】

PチャネルDAD3000のオン動作は、ゲート信号が第1ゲート電極10Bに与えられると、まずPチャネルMOSトランジスタPTにおいて、第1ゲート電極10B直下のN型ウエル領域4およびSOI層102の表面内で形成されるP型チャネルを通って、P型拡散領域52からP型ドレイン領域7に向かってホールが注入される。ホールは、第2ドレイン電極13Bに流れ込み、第2ドレイン電極13Bから第2ドレイン配線D2を通ってソース電極92Bに流れる。

【0162】

一方、ホール電流によって抵抗R1およびR2中にて発生した電位差が所定の値になると、第2ゲート電極11Bがゲートとして機能し、その直下のP型ウエル領域322の表面内に形成されたN型チャネルを通ってN型拡散領域62からSOI層102に向かって電子が注入され、注入された電子はN型ウエル領域611を経由して第1ドレイン電極12Bに到達し、図示しないローサイド(低電位)領域に電気的に接続された第1ドレイン電極12Bの電位が制御されることになる。

【0163】

このように、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることがなく、また電子もPチャネルMOS領域PRを直接に流れることがないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【0164】

なお、図19に示すように、PチャネルMOSトランジスタPTにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

【0165】

また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成されているので、PチャネルMOSトランジスタPTをNチャネルMOS領域NRから電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。

【0166】

<D.実施の形態4>

<D−1.装置構成>

本発明に係る実施の形態4として、図20および図21を用いてPチャネルDAD4000の構成について説明する。

【0167】

<D−1−1.平面構成>

図20はPチャネルDAD4000の平面構成を示す図である。図20に示すように、PチャネルDAD4000は、NチャネルMOS領域NRがトレンチ分離壁670(第2のトレンチ分離壁)によって囲まれて独立し、また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成され、ハイサイド領域HRを囲むトレンチ分離壁680(第1のトレンチ分離壁)と一体になったトレンチ分離壁690(側面分離壁)、691(第1の分離壁)および681(第2の分離壁)によって囲まれて独立している。なお、トレンチ分離壁670〜690、691および681は、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとを電気的に分離するので、分離構造と呼称することができる。

【0168】

PチャネルMOSトランジスタPTは、ハイサイド領域HRの内部側から順に平行に配設された、直線状のソース電極91C、第1ゲート電極10Cおよび第2ドレイン電極13Cで構成されている。

【0169】

そして、ソース電極91C、第1ゲート電極10Cおよび第2ドレイン電極13Cの各々の両端部にはトレンチ分離壁690が配設され、ソース電極91Cよりもハイサイド領域HRの内部側にはトレンチ分離壁691が配設され、第2ドレイン電極13Cよりも外部側にはトレンチ分離壁681が配設されている。

【0170】

そして、ソース電極91C、第1ゲート電極10Cおよび第2ドレイン電極13Cにはそれぞれソース配線SL1、第1ゲート配線G1、第2ドレイン配線D2が接続されている。

【0171】

ソース配線SL1および第1ゲート配線G1は、例えば第2層アルミ配線で構成され、第1ゲート配線G1はソース電極91C上をオーバーラップして、ハイサイド領域HR内に延在し、ソース配線SL1は、トレンチ分離壁691上をオーバーラップして、ハイサイド領域HR内に延在している。

【0172】

また、第2ドレイン配線D2は、例えば第1層アルミ配線で構成され、トレンチ分離壁680上をオーバーラップして、NチャネルMOS領域NR側のハイサイド領域HR外部に延在している。

【0173】

NチャネルMOS領域NRにおいては、直線状の第1ドレイン電極12Cを中央部に有し、第1ドレイン電極12Cを取り囲むように、長円環状の第2ゲート電極11Cが配設され、第2ゲート電極11Cを取り囲むように、長円環状のソース電極92Cが配設されてNチャネルMOSトランジスタを構成している。

【0174】

そして、第1ドレイン電極12C、第2ゲート電極11Cおよびソース電極92Cには、それぞれ第1ドレイン配線D1、第2ゲート配線G2およびソース配線SL2が接続されている。

【0175】

ソース配線SL2および第2ゲート配線G2は、例えば第2層アルミ配線で構成され、ソース配線SL2はトレンチ分離壁670上をオーバーラップし、第2ゲート配線G2はソース電極92C上およびトレンチ分離壁670上をオーバーラップして、ハイサイド領域HR側のNチャネルMOS領域NR外部に延在している。

【0176】

また、第1ドレイン配線D1は、例えば第1層アルミ配線で構成され、第2ゲート電極11Cおよびソース電極92C上をオーバーラップし、さらにトレンチ分離壁670上をオーバーラップして、ハイサイド領域HRとは反対側のNチャネルMOS領域NR外部に延在している。

【0177】

なお、第1ゲート電極10Cおよび第2ゲート電極11Cはドープトポリシリコンで構成され、第1ゲート配線G1および第2ゲート配線G2とはコンタクトホールにより接続される構成となっている。

【0178】

そして、第2ドレイン配線D2と第2ゲート配線G2とは抵抗R1を介して電気的に接続され、第2ゲート配線G2とソース配線SL2とは抵抗R2を介して電気的に接続されている。

【0179】

なお、以上の説明においては、NチャネルMOSトランジスタは、長円環状の同心形状を有するものとして説明したが、この形状に限定されるものではなく、円環状の同心形状、あるいは矩形環状の同心形状であっても良い。

【0180】

<D−1−2.主要部断面構成>

図20におけるZ−Z線での断面構成を図21に示す。図21に示すようにPチャネルDAD4000は、シリコン基板等の支持基板100上に、埋め込み酸化膜101およびSOI層102(N-)が配設されたSOI基板上に形成される。

【0181】

図21に示すように、PチャネルMOSトランジスタPTにおいては、SOI層102の表面内に、図に向かって左側からN型ウエル領域4、P型ウエル領域321(P+)がそれぞれ独立して配設されている。

【0182】

また、P型ウエル領域321とN型ウエル領域4との間には、P型ウエル領域321に連続するようにP型ドレイン領域7(P-)が形成されている。なお、P型ドレイン領域7の形成深さは、P型ウエル領域321よりも浅い。

【0183】

そして、N型ウエル領域4の表面内には、図に向かって左側からN型拡散領域62(N+)およびP型拡散領域52(P+)が隣接して配設されている。なお、N型ウエル領域4およびN型拡散領域62(N+)は必ずしも配設する必要はないので破線で示している。

【0184】

また、SOI層102の第1の主面上には、P型拡散領域52およびN型拡散領域62を短絡するように接触して形成されたソース電極91C、P型ウエル領域321上に接触して形成された第2ドレイン電極13C、さらに、絶縁ゲート電極として、P型ドレイン領域7の端縁部上から、(P型ドレイン領域7とN型ウエル領域4との間の)SOI層102上、N型ウエル領域4上およびP型拡散領域52の端縁部上をカバーするように第1ゲート電極10Cが配設されている。

【0185】

NチャネルMOS領域NRにおいては、SOI層102の表面内に、図に向かって右側からN型ウエル領域611(N+)、P型ウエル領域322(P+)がそれぞれ独立して配設されている。

【0186】

また、P型ウエル領域322の表面内には、N型拡散領域62(N+)が配設されている。

【0187】

また、SOI層102の第1の主面上には、N型拡散領域62およびP型ウエル領域322を短絡するように接触して形成されたソース電極92C、N型ウエル領域611上に接触して形成された第1ドレイン電極12C、さらに、絶縁ゲート電極として、N型拡散領域62の端縁部上から、P型ウエル領域322上およびSOI層102上をカバーするように第2ゲート電極11Cが配設されている。

【0188】

なお、P型ウエル領域322とN型ウエル領域611との間のSOI層102の表面上にはフィールド酸化膜が配設され、当該フィールド酸化膜は、P型ドレイン領域7およびP型ウエル領域322の表面上にも配設され、それらの上部にはマルチフィールドプレートが配設されているが、図示は省略する。

【0189】

また、トレンチ分離壁691、681および670は、SOI層102を貫通して埋め込み酸化膜101に達するトレンチの内壁を内壁酸化膜601で覆い、内壁酸化膜601で囲まれる領域にドープトポリシリコン等の導電体602が埋め込まれた構成となっている。そして、トレンチ分離壁691、681および670の上部にはフィールド酸化膜FLXが配設されている。

【0190】

なお、トレンチ分離壁691の両側面は、埋め込み酸化膜101に達するP型ウエル領域324で覆われ、トレンチ分離壁681の両側面は、埋め込み酸化膜101に達するP型ウエル領域321および323で覆われ、トレンチ分離壁670の両側面は、埋め込み酸化膜101に達するP型ウエル領域322および323で覆われているが、これは、トレンチ近傍で発生する結晶欠陥を覆い、デバイス内に結晶欠陥に起因するリーク電流が流れないようにするための構成である。

【0191】

<D−1−3.トレンチ分離壁の構成および機能>

ここで、トレンチ分離壁690の構成および機能について図22〜図26を用いて説明する。

【0192】

図22はトレンチ分離壁690と、その近傍のPチャネルMOSトランジスタPTの詳細構成を示す平面図である。

【0193】

図22に示すように、トレンチ分離壁690はPチャネルMOSトランジスタPTの各電極に平行に配設された複数のトレンチ22で構成されるマルチトレンチ構造を有している。なお、トレンチ22間はSOI層102であることは言うまでもない。

【0194】

また、PチャネルMOSトランジスタPTにおける第1ゲート電極10Cと、第2ドレイン電極13Cとの間のSOI層102の上部には、マルチフィールドプレートMFPZが配設されている。

【0195】

そして、マルチフィールドプレートMFPZの配列方向に沿ったプレート幅(ライン)およびプレート間隔(スペース)は、マルチトレンチ構造のトレンチ幅(ライン)およびトレンチ間隔(スペース)と一致するように構成されている。

【0196】

このように構成することで、ソース・ドレイン間の電位分布を均一化して、トレンチ分離壁690とPチャネルMOSトランジスタPTとの境界部での電界集中を抑制することができる。

【0197】

その仕組みについて図23〜図25を用いて説明する。

図23はトレンチ22の構成を詳細に示す図であり、図22に示す構成において、トレンチ22を拡大して示し、マルチフィールドプレートMFPZ等は省略している。

【0198】

図23に示すように、各トレンチ22のそれぞれは、内壁酸化膜221によって壁面が覆われ、内壁酸化膜221で囲まれた領域にドープトポリシリコン等の導電体222が埋め込まれた構成となっている。なお、充填された各導電体は他の特定の部位と電気的に接続されることなく形成されている。

【0199】

図24は順方向阻止電圧印加時にソース・ドレイン間で発生する電界分布を示す図であり、ソース・ドレイン間で発生する電界は、トレンチ22の内壁酸化膜221を通ってPチャネルMOSトランジスタPTのソース電極91Cと第2ドレイン電極13Cとの間の領域に分布しており、電界の集中部が存在せず、ほぼ均一な分布となっている。

【0200】

一方、電界が集中する構成の一例を図25に示す。図25は複数のトレンチ22で構成されるトレンチ分離壁690の代わりに、MOSトランジスタPTのソース・ドレイン間の距離にほぼ一致するトレンチ幅を有する単一のトレンチ23を配設した構成を示している。

【0201】

図25においてはトレンチ23の内壁酸化膜231だけを示しており、内壁酸化膜231のソース電極91C側の一辺にはソース電圧(正電位)が与えられ、第2ドレイン電極13C側の一辺は接地電位となっている。

【0202】

このような構成において、内壁酸化膜231で囲まれた領域の導電体内では同電位となるので、ソース・ドレイン間で発生する電界は、内壁酸化膜231の第2ドレイン電極13C側の一辺において集中し、酸化膜の絶縁破壊電圧の超過による絶縁破壊や、シリコンの物性値である臨界電界強度(V/cm)を超えた電界がシリコン中で発生すると、アバランシェ電流が誘起され、空乏層中の空間電荷を補償して、阻止特性(電圧を印加しても電流を流さない特性)を消失させる現象が発生し、所定の耐圧特性が得られなくなる。

【0203】

しかし、マルチトレンチ構造を有するトレンチ分離壁690においては、上述したように電界集中を防止できるので、耐圧特性が低下することはない。

【0204】

また、マルチフィールドプレートMFPZのラインおよびスペースは、マルチトレンチ構造のラインおよびスペースと一致しているので、PチャネルMOSトランジスタPTのソース電極91Cと第2ドレイン電極13Cとの間の領域の電界分布を整えることができる。

【0205】

<D−2.動作>

PチャネルDAD4000の動作は、図18および図19を用いて説明したPチャネルDAD3000と同様であり、PチャネルMOSトランジスタPTとNチャネルMOS領域NRとは電気的に分離されホールは直接にNチャネルMOS領域NRを流れることがなく、また電子もPチャネルMOS領域PRを直接に流れることがないので、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。

【0206】

なお、図21に示すように、PチャネルMOSトランジスタPTにもNチャネルMOS領域NRにも寄生サイリスタ構造が存在しないので、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。

【0207】

また、PチャネルMOSトランジスタPTがハイサイド領域HR内に形成されているので、PチャネルMOSトランジスタPTをNチャネルMOS領域NRから電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。

【0208】

なお、PチャネルDAD4000においては、PチャネルMOSトランジスタPTをトレンチ分離壁690、691および681が近接して取り囲み、トレンチ分離壁内に埋め込まれるように構成されるので、PチャネルMOSトランジスタPTが占有する面積が縮小され、半導体装置の集積度を上げることができる。

【0209】

<D−3.変形例>

図22を用いて説明したトレンチ分離壁690においては、PチャネルMOSトランジスタPTの各電極に平行に複数のトレンチ22が配設されている構成を示した。そして、トレンチ間にはSOI層102が存在し、当該トレンチ間のSOI層102は、PチャネルMOSトランジスタPTのソース・ドレイン間のSOI層102に連続する構成を示した。

【0210】

しかし、この構成ではPチャネルDAD4000のオン動作において、PチャネルMOSトランジスタPTのソース・ドレイン間を流れるホールキャリアが、トレンチ22間のSOI層102に拡散して蓄積し、スイッチング損失の増大を招く可能性がある。

【0211】

これを防止するための構成が、図26に示すトレンチ分離壁690Aである。図26は図22に対応する図であり、同一の構成については同一の符号を付し、重複する説明は省略する。また、便宜的にマルチフィールドプレートMFPZも省略している。

【0212】

図26において、各トレンチ22の間のSOI層102のPチャネルMOSトランジスタPT側の端部には、トレンチ24が配設され、両サイドのトレンチ22と接触するように配設されている。

【0213】

図27にトレンチ分離壁690Aの詳細部分構成を示す。図27に示すように、トレンチ24の第1の辺はトレンチ22間の長さにほぼ等しく、それに直交する第2の辺は、上記第1の辺とほぼ同じ長さであり、平面視形状は矩形となっている。

【0214】

構造的にはトレンチ22と同様であり、内壁酸化膜241によって壁面が覆われ、内壁酸化膜241で囲まれた領域にドープトポリシリコン等の導電体242が埋め込まれた構成となっている。

【0215】

そして、トレンチ24は、その内壁酸化膜241が両サイドのトレンチ22の内壁酸化膜221と接触して一体となるように配設され、トレンチ22の間のSOI層102にPチャネルMOSトランジスタPTからホールキャリアが流入することを防止する構成となっている。

【0216】

なお、トレンチ分離壁690Aに対向するPチャネルMOSトランジスタPTのSOI層102は、正確には図21に示すP型ドレイン領域7(ドリフト領域)であり、ホールキャリアが移動する領域である。

【0217】

トレンチ24の存在により、トレンチ22間のSOI層102にホールキャリアが蓄積することがなく、スイッチング損失の増大を招くことが防止できる。

【0218】

なお、トレンチ分離壁690と同様に、トレンチ分離壁690Aによっても電界集中を防止して、安定した耐圧特性を得ることができることは言うまでもない。

【0219】

次に、図28および図29を用いてトレンチ分離壁690Aの製造方法について説明する。

【0220】

まず、図28に示すように、SOI層102の第1の主面に、トレンチ22および24に対応する開口部OP1およびOP2を形成する。なお、開口部OP1間の間隔は2〜3μm程度である。

【0221】

次に、開口部OP1およびOP2の内面を酸化して、厚さ0.1〜0.2μm(1000〜2000オングストローム)程度の内壁酸化膜221および241を形成する。このとき、内壁酸化膜221および241が一体化することになる。

【0222】

その後、内壁酸化膜221および241で囲まれる領域に、ドープトポリシリコン等の導電体222および242を埋め込むことで、トレンチ分離壁690Aを得ることができる。

【0223】

【発明の効果】

本発明に係る請求項1記載の半導体装置によれば、第1のMOSトランジスタの主電流が、第2のMOSトランジスタの形成領域を通って第1の主電極に流入することを防止するように分離構造が設けられているので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制でき、寄生サイリスタのラッチアップを防止できる。また、第1のMOSトランジスタが第2のMOSトランジスタの形成領域に内包されるような形状において、分離領域のPN接合分離のための不純物領域内に、第1のMOSトランジスタの第1の主電極側から第2の主電極側に向けて少なくとも一列に配列された複数のトレンチを備えているので、順方向阻止電圧印加時に第1および第2の主電極間で発生する電界は、各トレンチの内壁酸化膜を通って分布することになり、電界を各トレンチごとに分担することができ、分離領域における電界集中を緩和して、耐圧特性を安定化できる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

【0225】

本発明に係る請求項2記載の半導体装置によれば、複数のトレンチの配列方向に沿ったトレンチ幅およびトレンチ間隔は、マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定されるので、複数のトレンチで分配された電界分布はマルチフィールドプレートによっても維持され、マルチフィールドプレートと組み合わせて用いることで、分離領域における電界集中をさらに緩和することができる。

【0226】

本発明に係る請求項3記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1および第2のトレンチ分離壁によって第1および第2のMOSトランジスタを電気的に分離するので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立して配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

【0227】

本発明に係る請求項4記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1のMOSトランジスタは第1のトレンチ分離壁で囲まれるハイサイド領域内に配設され、第2のMOSトランジスタは第2のトレンチ分離壁で囲まれて電気的に分離されるので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立して配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタがハイサイド領域に形成されるので、第1のMOSトランジスタを電気的に分離する専用のトレンチ分離壁が不要となり、半導体装置の集積度を上げることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

【0228】

本発明に係る請求項5記載の半導体装置によれば、第1および第2のMOSトランジスタを独立して配設し、第1のMOSトランジスタは第1のトレンチ分離壁で囲まれるハイサイド領域内において、第1のトレンチ分離壁内に埋め込まれるように配設されて電気的に分離されるので、それぞれの主電流を構成するキャリアであるホールや電子は、分離構造によって互いに隔離されることになり、ホールおよび電子が高密度に得られても、モジュレーションの発生を抑制できる。また、第1および第2のMOSトランジスタを独立して配設し、電気的に分離することで、寄生サイリスタ構造が存在せず、ラッチアップが発生することが原理的に防止され、ラッチアップ耐性の向上を図ることができる。また、第1のMOSトランジスタは第1のトレンチ分離壁内に埋め込まれるように配設されるので、第1のMOSトランジスタが占有する面積が縮小され、半導体装置の集積度を上げることができる。また、第1のMOSトランジスタの主電流は、第2の主電極から第1および第2の抵抗成分を経由して第2のMOSトランジスタの第1の主電極に到達するが、この際に、第1および第2の抵抗成分中にて発生した電位差が所定の値になった時点で第2のMOSトランジスタの制御電極が制御され、第2のMOSトランジスタのオン・オフ動作を制御することができる。

【0229】

本発明に係る請求項6記載の半導体装置によれば、順方向阻止電圧印加時に第1および第2の主電極間で発生する電界は、側面分離壁を構成する各トレンチの内壁酸化膜を通って分布することになり、第1のMOSトランジスタの第1および第2の主電極間において、ほぼ均一に分布し、側面分離壁において電界の集中部が存在せず、電界集中を緩和して、耐圧特性を安定化できる。

【0230】

本発明に係る請求項7記載の半導体装置によれば、複数の第2のトレンチが複数の第1のトレンチ間のSOI層の端部を塞ぐように配列され、複数の第1のトレンチの内壁酸化膜と複数の第2のトレンチの内壁酸化膜とが互いに接合して一体化しているので、オン動作において、第1のMOSトランジスタの第1および第2の主電極間を流れるキャリアが、複数の第1のトレンチ間のSOI層に拡散することが防止され、スイッチング損失の増大を招くことを防止できる。

【図面の簡単な説明】

【図1】 本発明に係る実施の形態1の半導体装置の平面構成を示す図である。

【図2】 本発明に係る実施の形態1の半導体装置の断面構成を示す図である。

【図3】 本発明に係る実施の形態1の半導体装置の部分断面構成を示す図である。

【図4】 本発明に係る実施の形態1の半導体装置の部分構成を示す斜視図である。

【図5】 本発明に係る実施の形態1の半導体装置の効果を説明する図である。

【図6】 マルチトレンチの製造工程を示す断面図である。

【図7】 マルチトレンチの製造工程を示す断面図である。

【図8】 マルチトレンチの製造工程を示す断面図である。

【図9】 マルチトレンチの製造工程を示す断面図である。

【図10】 マルチフィールドプレートが1層の場合の構成を示す図である。

【図11】 マルチフィールドプレートの効果を説明する模式図である。

【図12】 マルチフィールドプレートが2層の場合の構成を示す図である。

【図13】 マルチフィールドプレートの効果を説明する模式図である。

【図14】 マルチフィールドプレートの配設状態の一例を示す平面図である。

【図15】 マルチフィールドプレートの配設状態の変形例を示す平面図である。

【図16】 本発明に係る実施の形態2の半導体装置の平面構成を示す図である。

【図17】 本発明に係る実施の形態2の半導体装置の断面構成を示す図である。

【図18】 本発明に係る実施の形態3の半導体装置の平面構成を示す図である。

【図19】 本発明に係る実施の形態3の半導体装置の断面構成を示す図である。

【図20】 本発明に係る実施の形態4の半導体装置の平面構成を示す図である。

【図21】 本発明に係る実施の形態4の半導体装置の断面構成を示す図である。

【図22】 本発明に係る実施の形態4の半導体装置の部分平面構成を示す図である。

【図23】 本発明に係る実施の形態4の半導体装置の部分平面構成を示す図である。

【図24】 本発明に係る実施の形態4の半導体装置の効果を説明する図である。

【図25】 本発明に係る実施の形態4の半導体装置の構成を適用しない場合の問題点を説明する図である。

【図26】 本発明に係る実施の形態4の半導体装置の変形例の部分平面構成を示す図である。

【図27】 本発明に係る実施の形態4の半導体装置の変形例の部分平面構成を示す図である。

【図28】 本発明に係る実施の形態4の半導体装置の変形例の製造工程をす図である。

【図29】 本発明に係る実施の形態4の半導体装置の変形例の製造工程をす図である。

【図30】 従来のDADの平面構成を示す図である。

【図31】 従来のDADの断面構成を示す図である。

【図32】 従来のDADの等価回路を示す図である。

【符号の説明】

9,9A,9B,91C,92C ソース電極、10A,10B,10C 第1ゲート電極、11A,11B,11C 第2ゲート電極、12A,12B,12C 第1ドレイン電極、13A,13B,13C 第2ドレイン電極、20 分離領域、21,22,24 トレンチ、MFP1,MFP2,MFPZ マルチフィールドプレート、610〜690,681,691 トレンチ分離壁、211,221,241 内壁酸化膜、212,222,242 導電体。

Claims (7)

- 支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

平面視形状が直線状の第1の主電極と、

前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、

前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、

前記第2のMOSトランジスタは、

前記第2のMOSトランジスタの前記第1の主電極の平面視形状が、前記第1のMOSトランジスタの前記第1の主電極を中心部として囲み、前記第1のMOSトランジスタを内包する長円環状であって、その内側に沿って配設され、その開口部に前記第1のMOSトランジスタを配置した平面視形状がC字形状の制御電極と、

第2の主電極とを備え、

前記第2の主電極は、前記第1のMOSトランジスタの前記第1の主電極と共通の電極であり、

前記分離構造は、

前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1のMOSトランジスタの前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る分離領域を備え、

前記分離領域は、

PN接合分離のための不純物領域によってその外形が規定され、

前記不純物領域内に配設され、前記SOI基板を構成する埋め込み酸化膜に達する複数のトレンチを備え、

前記複数のトレンチは、

前記第1のMOSトランジスタの前記第1の主電極側から前記第2の主電極側に向けて少なくとも一列に配列され、

それぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。 - 前記第2のMOSトランジスタの前記第1の主電極よりも内側の前記SOI層の上部に、前記第1のMOSトランジスタの前記第1の主電極を中心として同心状に複数配設されたマルチフィールドプレートをさらに備え、

前記複数のトレンチの前記配列方向に沿ったトレンチ幅およびトレンチ間隔は、前記マルチフィールドプレートの配列方向に沿ったプレート幅およびプレート間隔にほぼ一致するように設定される、請求項1記載の半導体装置。 - 支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

同心構造の中心をなす第1の主電極と、

前記第1の主電極を囲む制御電極と、

前記制御電極を囲む第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、

前記第1の主電極の内側に沿って配設された制御電極とを備え、

前記分離構造は、

前記第1のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1のトレンチ分離壁と、

前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第2のトレンチ分離壁とを備え、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。 - 支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

同心構造の最外周をなす第1の主電極と、

前記第1の主電極の内側に沿って配設された制御電極と、

同心構造の中心をなす第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、

前記第1の主電極の内側に沿って配設された制御電極とを備え、

前記分離構造は、

比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。 - 支持基板上に、埋め込み酸化膜およびSOI層を有して構成されるSOI基板上に配設され、主電流が横方向に流れる導電型の異なる第1および第2のMOSトランジスタを備え、

前記第1のMOSトランジスタの主電流に基づく電位により前記第2のMOSトランジスタの制御電極の電位を制御して前記第2のMOSトランジスタのオン・オフ動作を制御する半導体装置であって、

前記第1のMOSトランジスタの主電流が、前記第2のMOSトランジスタの形成領域を通って前記第2のMOSトランジスタの第1の主電極に流入する経路を遮断するように、前記第1のMOSトランジスタと前記第2のMOSトランジスタとを電気的に分離する分離構造を前記SOI層内に備え、

前記第1のMOSトランジスタは、

平面視形状が直線状の第1の主電極と、

前記第1の主電極に平行するように配設され、前記第1の主電極を超えない長さの直線状の制御電極と、

前記制御電極に平行するように配設された、前記制御電極と同等の長さの直線状の第2の主電極とを備え、

前記第2のMOSトランジスタは、

同心構造の最外周をなす前記第1の主電極と、

同心構造の中心をなす第2の主電極と、

前記第1の主電極の内側に沿って配設された制御電極とを備え、

前記分離構造は、

比較的高電位のハイサイド領域および前記第2のMOSトランジスタを囲むように前記SOI層中に配設され、前記埋め込み酸化膜に達する第1および第2のトレンチ分離壁を備え、

前記第1のMOSトランジスタは前記ハイサイド領域内に配設され、

前記第1および第2のトレンチ分離壁のそれぞれは、

内壁を覆う内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた導電体とを有し、

前記第1のトレンチ分離壁は、

前記第1のMOSトランジスタの前記第1の主電極、前記制御電極および前記第2の主電極の両端部にそれぞれ配設され、前記第1の主電極、前記制御電極および前記第2の主電極の一方および他方の端部間にそれぞれ渡る側面分離壁と、

前記第1のMOSトランジスタの前記第1の主電極および前記第2の主電極の外側に配設された第1および第2の分離壁とを有し、

前記側面分離壁と前記第1および第2の分離壁とで前記第1のMOSトランジスタを囲み、

前記第1のMOSトランジスタの前記第2の主電極は、前記第2のMOSトランジスタの前記制御電極に第1の抵抗成分を介して接続され、

前記第2のMOSトランジスタの前記制御電極は、前記第2のMOSトランジスタの前記第1の主電極に第2の抵抗成分を介して接続される、半導体装置。 - 前記側面分離壁は、

前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数のトレンチを有し、

前記複数のトレンチのそれぞれは、

前記内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、

前記複数のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列される、請求項5記載の半導体装置。 - 前記側面分離壁は、

前記第1のMOSトランジスタの各電極に平行に所定間隔で配設された複数の第1のトレンチと、

前記複数の第1のトレンチの配列の端縁部に配設された平面視形状が矩形の複数の第2のトレンチとを有し、

前記複数の第1および第2のトレンチのそれぞれは、

前記内壁酸化膜と、

前記内壁酸化膜で囲まれた領域に埋め込まれた前記導電体とを有し、

前記複数の第1のトレンチは、それぞれの一端が、前記第1のMOSトランジスタの形成領域の端縁部に沿って並ぶように配列され、

前記複数の第2のトレンチは、

前記複数の第1のトレンチ間の前記SOI層の端部を塞ぐように配列され、

前記複数の第1のトレンチの前記内壁酸化膜と前記複数の第2のトレンチの前記内壁酸化膜とが互いに接合して一体化している、請求項5記載の半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000317991A JP4471480B2 (ja) | 2000-10-18 | 2000-10-18 | 半導体装置 |

| US09/835,445 US6603176B2 (en) | 2000-10-18 | 2001-04-17 | Power semiconductor device for power integrated circuit device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000317991A JP4471480B2 (ja) | 2000-10-18 | 2000-10-18 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002124681A JP2002124681A (ja) | 2002-04-26 |

| JP2002124681A5 JP2002124681A5 (ja) | 2006-03-16 |

| JP4471480B2 true JP4471480B2 (ja) | 2010-06-02 |

Family

ID=18796689

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000317991A Expired - Fee Related JP4471480B2 (ja) | 2000-10-18 | 2000-10-18 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6603176B2 (ja) |

| JP (1) | JP4471480B2 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4590884B2 (ja) * | 2003-06-13 | 2010-12-01 | 株式会社デンソー | 半導体装置およびその製造方法 |

| KR20060132808A (ko) * | 2003-09-22 | 2006-12-22 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 전계 효과 장치 및 초음파 장치 |

| US7737524B2 (en) * | 2003-09-30 | 2010-06-15 | Nxp B.V. | Lateral thin-film SOI device having a field plate with isolated metallic regions |

| JP4654574B2 (ja) * | 2003-10-20 | 2011-03-23 | トヨタ自動車株式会社 | 半導体装置 |

| FR2863773B1 (fr) * | 2003-12-12 | 2006-05-19 | Atmel Grenoble Sa | Procede de fabrication de puces electroniques en silicium aminci |

| US20060255401A1 (en) * | 2005-05-11 | 2006-11-16 | Yang Robert K | Increasing breakdown voltage in semiconductor devices with vertical series capacitive structures |

| JP4864344B2 (ja) * | 2005-05-16 | 2012-02-01 | パナソニック株式会社 | 半導体装置 |

| JP4863665B2 (ja) * | 2005-07-15 | 2012-01-25 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| US20070012983A1 (en) * | 2005-07-15 | 2007-01-18 | Yang Robert K | Terminations for semiconductor devices with floating vertical series capacitive structures |

| JP4984579B2 (ja) * | 2006-03-10 | 2012-07-25 | 株式会社日立製作所 | 高耐圧半導体集積回路装置 |

| EP1863081A3 (en) | 2006-03-10 | 2008-03-05 | Hitachi, Ltd. | Dielectric material separated-type, high breakdown voltage semiconductor circuit device, and production method thereof |

| US7605446B2 (en) * | 2006-07-14 | 2009-10-20 | Cambridge Semiconductor Limited | Bipolar high voltage/power semiconductor device having first and second insulated gated and method of operation |

| JP4616856B2 (ja) * | 2007-03-27 | 2011-01-19 | 株式会社日立製作所 | 半導体装置、及び半導体装置の製造方法 |

| JP2008016863A (ja) * | 2007-08-31 | 2008-01-24 | Denso Corp | 縦型ホール素子 |

| JP4797203B2 (ja) * | 2008-12-17 | 2011-10-19 | 三菱電機株式会社 | 半導体装置 |

| JP2011029466A (ja) * | 2009-07-28 | 2011-02-10 | Hitachi Ltd | 半導体装置 |

| US8803232B2 (en) * | 2011-05-29 | 2014-08-12 | Taiwan Semiconductor Manufacturing Co., Ltd. | High voltage and ultra-high voltage semiconductor devices with increased breakdown voltages |

| CN102683262A (zh) * | 2012-04-28 | 2012-09-19 | 东南大学 | 一种基于绝缘体上硅的高压隔离结构 |

| CN103117307A (zh) * | 2013-01-24 | 2013-05-22 | 东南大学 | 一种高可靠性p型绝缘体上硅横向双扩散场效应晶体管 |

| JP6255421B2 (ja) * | 2013-01-30 | 2017-12-27 | マイクロチップ テクノロジー インコーポレイテッドMicrochip Technology Incorporated | Esd自己保護を有するdmos半導体デバイスおよびそれを備えたlinバスドライバ |

| EP2930743B1 (en) * | 2014-04-11 | 2016-09-21 | Nxp B.V. | Semiconductor isolation structure |

| JP6729487B2 (ja) * | 2017-05-15 | 2020-07-22 | 三菱電機株式会社 | 半導体装置、半導体装置の製造方法、および電力変換装置 |

| US10790365B2 (en) * | 2018-02-23 | 2020-09-29 | Vanguard International Semiconductor Corporation | Lateral diffused metal oxide semiconductor field effect transistor |

| CN112993006B (zh) * | 2019-12-12 | 2022-08-12 | 珠海格力电器股份有限公司 | 一种终端结构、其制作方法及电子器件 |

| EP4174922A1 (en) * | 2021-10-29 | 2023-05-03 | Infineon Technologies Austria AG | High-voltage semiconductor device |

| EP4220697A1 (en) * | 2022-01-27 | 2023-08-02 | Infineon Technologies Austria AG | Semiconductor device with trench isolation structures in a transition region and method of manufacturing |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5874768A (en) * | 1994-06-15 | 1999-02-23 | Nippondenso Co., Ltd. | Semiconductor device having a high breakdown voltage |

| JP3378135B2 (ja) * | 1996-02-02 | 2003-02-17 | 三菱電機株式会社 | 半導体装置とその製造方法 |

| JP3575908B2 (ja) * | 1996-03-28 | 2004-10-13 | 株式会社東芝 | 半導体装置 |

| JP3958404B2 (ja) * | 1997-06-06 | 2007-08-15 | 三菱電機株式会社 | 横型高耐圧素子を有する半導体装置 |

| JP3111947B2 (ja) * | 1997-10-28 | 2000-11-27 | 日本電気株式会社 | 半導体装置、その製造方法 |

| US6133610A (en) * | 1998-01-20 | 2000-10-17 | International Business Machines Corporation | Silicon-on-insulator chip having an isolation barrier for reliability and process of manufacture |

| US6150697A (en) * | 1998-04-30 | 2000-11-21 | Denso Corporation | Semiconductor apparatus having high withstand voltage |

-

2000

- 2000-10-18 JP JP2000317991A patent/JP4471480B2/ja not_active Expired - Fee Related

-

2001

- 2001-04-17 US US09/835,445 patent/US6603176B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6603176B2 (en) | 2003-08-05 |

| JP2002124681A (ja) | 2002-04-26 |

| US20020043699A1 (en) | 2002-04-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4471480B2 (ja) | 半導体装置 | |

| US6439514B1 (en) | Semiconductor device with elements surrounded by trenches | |

| KR100315128B1 (ko) | 금속교차선이없이레벨쉬프트동작을하는레벨쉬프트회로,모스페트장치및고전압집적회로 | |

| US6130458A (en) | Power IC having SOI structure | |

| US7655979B2 (en) | High voltage gate driver integrated circuit including high voltage junction capacitor and high voltage LDMOS transistor | |

| US20020179974A1 (en) | High-voltage semiconductor device | |

| US7999333B2 (en) | Semiconductor device | |

| US8390032B2 (en) | Depletion mode field effect transistor for ESD protection | |

| KR100802461B1 (ko) | 반도체 장치 | |

| KR20140006156A (ko) | 전력 반도체 소자 | |

| JP2008547223A (ja) | バルク抵抗制御技法 | |

| JP3730394B2 (ja) | 高耐圧半導体装置 | |

| JP3654872B2 (ja) | 高耐圧半導体装置 | |

| JPH10313064A (ja) | 半導体装置 | |

| US20080006847A1 (en) | Semiconductor protective structure for electrostatic discharge | |

| US7473974B2 (en) | Semiconductor circuit device including a protection circuit | |

| KR19990045214A (ko) | 유전체 분리형 반도체 장치 | |

| JPH1065018A (ja) | 半導体装置 | |

| JP2004006555A (ja) | 半導体装置 | |

| JP2002094033A (ja) | 半導体装置 | |

| JP4479041B2 (ja) | 半導体装置及びその製造方法 | |

| JP4682533B2 (ja) | 半導体装置 | |

| US20240128187A1 (en) | Semiconductor device | |

| JPH10256542A (ja) | 半導体装置 | |

| JPH07115126A (ja) | 半導体集積回路装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060201 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090216 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100113 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100302 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100302 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130312 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130312 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140312 Year of fee payment: 4 |

|

| LAPS | Cancellation because of no payment of annual fees |