JP2011508354A - セルのソースのir降下に対処するためのソース電位の調整 - Google Patents

セルのソースのir降下に対処するためのソース電位の調整 Download PDFInfo

- Publication number

- JP2011508354A JP2011508354A JP2010539660A JP2010539660A JP2011508354A JP 2011508354 A JP2011508354 A JP 2011508354A JP 2010539660 A JP2010539660 A JP 2010539660A JP 2010539660 A JP2010539660 A JP 2010539660A JP 2011508354 A JP2011508354 A JP 2011508354A

- Authority

- JP

- Japan

- Prior art keywords

- source

- page

- voltage

- memory

- memory cell

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000015654 memory Effects 0.000 claims abstract description 224

- 238000003860 storage Methods 0.000 claims abstract description 73

- 238000000034 method Methods 0.000 claims abstract description 28

- 230000008878 coupling Effects 0.000 claims description 12

- 238000010168 coupling process Methods 0.000 claims description 12

- 238000005859 coupling reaction Methods 0.000 claims description 12

- 238000002955 isolation Methods 0.000 claims description 11

- 238000007667 floating Methods 0.000 description 29

- 230000006870 function Effects 0.000 description 9

- 238000013461 design Methods 0.000 description 8

- 230000001419 dependent effect Effects 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 239000008186 active pharmaceutical agent Substances 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 230000001276 controlling effect Effects 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 238000009826 distribution Methods 0.000 description 4

- 238000003491 array Methods 0.000 description 3

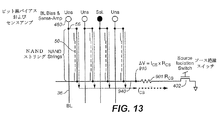

- 238000010586 diagram Methods 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000001105 regulatory effect Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 239000002131 composite material Substances 0.000 description 2

- 239000002784 hot electron Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- 101100015484 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) GPA1 gene Proteins 0.000 description 1

- 230000001154 acute effect Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 239000013643 reference control Substances 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

- 238000009281 ultraviolet germicidal irradiation Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/961,871 US7764547B2 (en) | 2007-12-20 | 2007-12-20 | Regulation of source potential to combat cell source IR drop |

| PCT/US2008/086694 WO2009082637A1 (en) | 2007-12-20 | 2008-12-12 | Regulation of source potential to combat cell source ir drop |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011508354A true JP2011508354A (ja) | 2011-03-10 |

| JP2011508354A5 JP2011508354A5 (enExample) | 2012-01-19 |

Family

ID=40380429

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010539660A Pending JP2011508354A (ja) | 2007-12-20 | 2008-12-12 | セルのソースのir降下に対処するためのソース電位の調整 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US7764547B2 (enExample) |

| EP (1) | EP2223304A1 (enExample) |

| JP (1) | JP2011508354A (enExample) |

| KR (1) | KR20100111666A (enExample) |

| CN (1) | CN101903955A (enExample) |

| TW (1) | TW200945349A (enExample) |

| WO (1) | WO2009082637A1 (enExample) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009163793A (ja) * | 2007-12-28 | 2009-07-23 | Toshiba Corp | 半導体記憶装置 |

| JP5667260B1 (ja) * | 2013-08-20 | 2015-02-12 | ウィンボンド エレクトロニクス コーポレーション | 半導体記憶装置 |

| JP2015049916A (ja) * | 2013-09-02 | 2015-03-16 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR20150103184A (ko) * | 2013-03-14 | 2015-09-09 | 실리콘 스토리지 테크놀로지 인크 | 어드밴스트 나노미터 플래시 메모리의 동적 프로그래밍 |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7606076B2 (en) * | 2007-04-05 | 2009-10-20 | Sandisk Corporation | Sensing in non-volatile storage using pulldown to regulated source voltage to remove system noise |

| US7764547B2 (en) | 2007-12-20 | 2010-07-27 | Sandisk Corporation | Regulation of source potential to combat cell source IR drop |

| US7701761B2 (en) * | 2007-12-20 | 2010-04-20 | Sandisk Corporation | Read, verify word line reference voltage to track source level |

| JP4635066B2 (ja) * | 2008-03-19 | 2011-02-16 | 株式会社東芝 | 半導体記憶装置 |

| KR101053700B1 (ko) * | 2009-05-11 | 2011-08-02 | 주식회사 하이닉스반도체 | 전압 생성 회로 및 이를 구비한 불휘발성 메모리 소자 |

| KR101669550B1 (ko) * | 2009-09-10 | 2016-10-26 | 삼성전자주식회사 | 공통 소스 라인의 노이즈를 줄이는 플래시 메모리 장치, 그것의 동작 방법, 그리고 그것을 포함하는 메모리 시스템 |

| US8169830B2 (en) * | 2009-09-17 | 2012-05-01 | Micron Technology, Inc. | Sensing for all bit line architecture in a memory device |

| US8427886B2 (en) * | 2011-07-11 | 2013-04-23 | Lsi Corporation | Memory device with trimmable power gating capabilities |

| KR101861084B1 (ko) | 2011-07-11 | 2018-05-28 | 삼성전자주식회사 | 비휘발성 메모리 장치, 이의 동작 방법, 및 비휘발성 메모리 장치를 포함하는 전자 장치 |

| US9236102B2 (en) | 2012-10-12 | 2016-01-12 | Micron Technology, Inc. | Apparatuses, circuits, and methods for biasing signal lines |

| US8897054B2 (en) * | 2013-02-18 | 2014-11-25 | Intel Mobile Communications GmbH | ROM device with keepers |

| US9042190B2 (en) * | 2013-02-25 | 2015-05-26 | Micron Technology, Inc. | Apparatuses, sense circuits, and methods for compensating for a wordline voltage increase |

| US9202579B2 (en) * | 2013-03-14 | 2015-12-01 | Sandisk Technologies Inc. | Compensation for temperature dependence of bit line resistance |

| KR20140145367A (ko) * | 2013-06-13 | 2014-12-23 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치, 그것을 포함하는 메모리 시스템 및 그것의 동작 방법 |

| US9177663B2 (en) | 2013-07-18 | 2015-11-03 | Sandisk Technologies Inc. | Dynamic regulation of memory array source line |

| US9672875B2 (en) | 2014-01-27 | 2017-06-06 | Micron Technology, Inc. | Methods and apparatuses for providing a program voltage responsive to a voltage determination |

| US9368224B2 (en) | 2014-02-07 | 2016-06-14 | SanDisk Technologies, Inc. | Self-adjusting regulation current for memory array source line |

| KR102167609B1 (ko) * | 2014-05-13 | 2020-10-20 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그것의 프로그램 방법 |

| KR20160008875A (ko) * | 2014-07-15 | 2016-01-25 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그것의 동작 방법 |

| US9208895B1 (en) | 2014-08-14 | 2015-12-08 | Sandisk Technologies Inc. | Cell current control through power supply |

| US9349468B2 (en) | 2014-08-25 | 2016-05-24 | SanDisk Technologies, Inc. | Operational amplifier methods for charging of sense amplifier internal nodes |

| JP6313252B2 (ja) | 2015-03-16 | 2018-04-18 | 東芝メモリ株式会社 | 半導体メモリ装置 |

| US9892791B2 (en) * | 2015-06-16 | 2018-02-13 | Sandisk Technologies Llc | Fast scan to detect bit line discharge time |

| CN105895153B (zh) * | 2016-03-25 | 2019-07-02 | 上海华虹宏力半导体制造有限公司 | 存储器及其干扰检测和消除的方法、装置 |

| KR102620805B1 (ko) * | 2016-09-22 | 2024-01-04 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

| US10763304B2 (en) * | 2017-06-27 | 2020-09-01 | Taiwan Semiconductor Manufacturing Company Ltd. | Semiconductor structure and method of forming the same |

| JP7091130B2 (ja) * | 2018-05-08 | 2022-06-27 | キオクシア株式会社 | 半導体記憶装置 |

| JP2019200828A (ja) * | 2018-05-16 | 2019-11-21 | 東芝メモリ株式会社 | 半導体記憶装置 |

| KR102555006B1 (ko) | 2019-02-22 | 2023-07-14 | 삼성전자주식회사 | 반도체 메모리 장치 및 이를 포함하는 메모리 시스템 |

| US10984872B1 (en) * | 2019-12-05 | 2021-04-20 | Integrated Silicon Solution, (Cayman) Inc. | Non-volatile memory with source line resistance compensation |

| US11049572B1 (en) * | 2020-03-06 | 2021-06-29 | Macronix International Co., Ltd. | Memory device, source line voltage adjuster and source line voltage adjusting method thereof |

| TWI764104B (zh) * | 2020-03-06 | 2022-05-11 | 旺宏電子股份有限公司 | 記憶體裝置、源極線電壓調整器及其源極線電壓調整方法 |

| US11942179B2 (en) * | 2022-04-11 | 2024-03-26 | Macronix International Co., Ltd. | Threshold voltage variation compensation in integrated circuits |

| JP2024136330A (ja) * | 2023-03-23 | 2024-10-04 | キオクシア株式会社 | 半導体記憶装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10154803A (ja) * | 1996-11-25 | 1998-06-09 | Toshiba Corp | 不揮発性半導体メモリ |

| EP1331644A2 (en) * | 2001-12-28 | 2003-07-30 | STMicroelectronics S.r.l. | Regulation method for the source voltage in a nonvolatile memory cell during programming and corresponding program circuit |

| WO2006105363A1 (en) * | 2005-04-01 | 2006-10-05 | Sandisk Corporation | Non-volatile memory and method with control gate compensation for source line bias errors |

| JP2007080306A (ja) * | 2005-09-09 | 2007-03-29 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2009087432A (ja) * | 2007-09-28 | 2009-04-23 | Toshiba Corp | 不揮発性半導体記憶装置 |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IT1224062B (it) * | 1979-09-28 | 1990-09-26 | Ates Componenti Elettron | Metodo di programmazione per una memoria a semiconduttore non volatile elettricamente alterabile |

| JPS5977700A (ja) * | 1982-10-25 | 1984-05-04 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JPS61137299A (ja) * | 1984-12-07 | 1986-06-24 | Hitachi Ltd | イレ−ザル・プログラマブルrom |

| US5095344A (en) * | 1988-06-08 | 1992-03-10 | Eliyahou Harari | Highly compact eprom and flash eeprom devices |

| US5070032A (en) * | 1989-03-15 | 1991-12-03 | Sundisk Corporation | Method of making dense flash eeprom semiconductor memory structures |

| DE69033438T2 (de) * | 1989-04-13 | 2000-07-06 | Sandisk Corp., Santa Clara | Austausch von fehlerhaften Speicherzellen einer EEprommatritze |

| US5172338B1 (en) * | 1989-04-13 | 1997-07-08 | Sandisk Corp | Multi-state eeprom read and write circuits and techniques |

| US5343063A (en) * | 1990-12-18 | 1994-08-30 | Sundisk Corporation | Dense vertical programmable read only memory cell structure and processes for making them |

| JP3210355B2 (ja) * | 1991-03-04 | 2001-09-17 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US5313421A (en) * | 1992-01-14 | 1994-05-17 | Sundisk Corporation | EEPROM with split gate source side injection |

| US6222762B1 (en) * | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| US5315541A (en) * | 1992-07-24 | 1994-05-24 | Sundisk Corporation | Segmented column memory array |

| US5555204A (en) * | 1993-06-29 | 1996-09-10 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

| KR0169267B1 (ko) * | 1993-09-21 | 1999-02-01 | 사토 후미오 | 불휘발성 반도체 기억장치 |

| US5661053A (en) * | 1994-05-25 | 1997-08-26 | Sandisk Corporation | Method of making dense flash EEPROM cell array and peripheral supporting circuits formed in deposited field oxide with the use of spacers |

| JP2590764B2 (ja) * | 1994-11-29 | 1997-03-12 | 日本電気株式会社 | 不揮発性半導体記憶装置 |

| JP3359209B2 (ja) * | 1995-11-29 | 2002-12-24 | シャープ株式会社 | 半導体記憶装置及びメモリアクセス方法 |

| US5903495A (en) * | 1996-03-18 | 1999-05-11 | Kabushiki Kaisha Toshiba | Semiconductor device and memory system |

| US5768192A (en) * | 1996-07-23 | 1998-06-16 | Saifun Semiconductors, Ltd. | Non-volatile semiconductor memory cell utilizing asymmetrical charge trapping |

| US5986931A (en) * | 1997-01-02 | 1999-11-16 | Caywood; John M. | Low voltage single CMOS electrically erasable read-only memory |

| US6768165B1 (en) * | 1997-08-01 | 2004-07-27 | Saifun Semiconductors Ltd. | Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping |

| JP3486079B2 (ja) * | 1997-09-18 | 2004-01-13 | 株式会社東芝 | 半導体記憶装置 |

| US6087894A (en) * | 1998-03-02 | 2000-07-11 | Motorola, Inc. | Low power precision current reference |

| US6373753B1 (en) * | 1999-02-13 | 2002-04-16 | Robert J. Proebsting | Memory array having selected word lines driven to an internally-generated boosted voltage that is substantially independent of VDD |

| US6055190A (en) * | 1999-03-15 | 2000-04-25 | Macronix International Co., Ltd. | Device and method for suppressing bit line column leakage during erase verification of a memory cell |

| US6118702A (en) * | 1999-10-19 | 2000-09-12 | Advanced Micro Devices, Inc. | Source bias compensation for page mode read operation in a flash memory device |

| US6400638B1 (en) | 2000-02-25 | 2002-06-04 | Advanced Micro Devices, Inc. | Wordline driver for flash memory read mode |

| US6950336B2 (en) * | 2000-05-03 | 2005-09-27 | Emosyn America, Inc. | Method and apparatus for emulating an electrically erasable programmable read only memory (EEPROM) using non-volatile floating gate memory cells |

| US7046568B2 (en) | 2002-09-24 | 2006-05-16 | Sandisk Corporation | Memory sensing circuit and method for low voltage operation |

| US7196931B2 (en) * | 2002-09-24 | 2007-03-27 | Sandisk Corporation | Non-volatile memory and method with reduced source line bias errors |

| US6987693B2 (en) * | 2002-09-24 | 2006-01-17 | Sandisk Corporation | Non-volatile memory and method with reduced neighboring field errors |

| US7443757B2 (en) | 2002-09-24 | 2008-10-28 | Sandisk Corporation | Non-volatile memory and method with reduced bit line crosstalk errors |

| KR100884235B1 (ko) * | 2003-12-31 | 2009-02-17 | 삼성전자주식회사 | 불휘발성 메모리 카드 |

| JP2005285197A (ja) | 2004-03-29 | 2005-10-13 | Renesas Technology Corp | 半導体記憶装置 |

| US7042767B2 (en) * | 2004-08-02 | 2006-05-09 | Spansion, Llc | Flash memory unit and method of programming a flash memory device |

| US7173854B2 (en) * | 2005-04-01 | 2007-02-06 | Sandisk Corporation | Non-volatile memory and method with compensation for source line bias errors |

| US7606076B2 (en) * | 2007-04-05 | 2009-10-20 | Sandisk Corporation | Sensing in non-volatile storage using pulldown to regulated source voltage to remove system noise |

| US7606071B2 (en) * | 2007-04-24 | 2009-10-20 | Sandisk Corporation | Compensating source voltage drop in non-volatile storage |

| US7492640B2 (en) * | 2007-06-07 | 2009-02-17 | Sandisk Corporation | Sensing with bit-line lockout control in non-volatile memory |

| US7489553B2 (en) * | 2007-06-07 | 2009-02-10 | Sandisk Corporation | Non-volatile memory with improved sensing having bit-line lockout control |

| US7701761B2 (en) * | 2007-12-20 | 2010-04-20 | Sandisk Corporation | Read, verify word line reference voltage to track source level |

| US7764547B2 (en) | 2007-12-20 | 2010-07-27 | Sandisk Corporation | Regulation of source potential to combat cell source IR drop |

| US7593265B2 (en) * | 2007-12-28 | 2009-09-22 | Sandisk Corporation | Low noise sense amplifier array and method for nonvolatile memory |

-

2007

- 2007-12-20 US US11/961,871 patent/US7764547B2/en active Active

-

2008

- 2008-12-12 CN CN2008801221659A patent/CN101903955A/zh active Pending

- 2008-12-12 KR KR1020107013249A patent/KR20100111666A/ko not_active Withdrawn

- 2008-12-12 WO PCT/US2008/086694 patent/WO2009082637A1/en not_active Ceased

- 2008-12-12 JP JP2010539660A patent/JP2011508354A/ja active Pending

- 2008-12-12 EP EP08865757A patent/EP2223304A1/en not_active Withdrawn

- 2008-12-19 TW TW097149961A patent/TW200945349A/zh unknown

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10154803A (ja) * | 1996-11-25 | 1998-06-09 | Toshiba Corp | 不揮発性半導体メモリ |

| EP1331644A2 (en) * | 2001-12-28 | 2003-07-30 | STMicroelectronics S.r.l. | Regulation method for the source voltage in a nonvolatile memory cell during programming and corresponding program circuit |

| WO2006105363A1 (en) * | 2005-04-01 | 2006-10-05 | Sandisk Corporation | Non-volatile memory and method with control gate compensation for source line bias errors |

| JP2007080306A (ja) * | 2005-09-09 | 2007-03-29 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2009087432A (ja) * | 2007-09-28 | 2009-04-23 | Toshiba Corp | 不揮発性半導体記憶装置 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009163793A (ja) * | 2007-12-28 | 2009-07-23 | Toshiba Corp | 半導体記憶装置 |

| KR20150103184A (ko) * | 2013-03-14 | 2015-09-09 | 실리콘 스토리지 테크놀로지 인크 | 어드밴스트 나노미터 플래시 메모리의 동적 프로그래밍 |

| KR101697450B1 (ko) | 2013-03-14 | 2017-01-17 | 실리콘 스토리지 테크놀로지 인크 | 어드밴스트 나노미터 플래시 메모리의 동적 프로그래밍 |

| JP5667260B1 (ja) * | 2013-08-20 | 2015-02-12 | ウィンボンド エレクトロニクス コーポレーション | 半導体記憶装置 |

| US9153335B2 (en) | 2013-08-20 | 2015-10-06 | Winbond Electronics Corp. | Clamp voltage generator of a semiconductor memory apparatus |

| JP2015049916A (ja) * | 2013-09-02 | 2015-03-16 | 株式会社東芝 | 不揮発性半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090161433A1 (en) | 2009-06-25 |

| US7764547B2 (en) | 2010-07-27 |

| EP2223304A1 (en) | 2010-09-01 |

| WO2009082637A1 (en) | 2009-07-02 |

| TW200945349A (en) | 2009-11-01 |

| CN101903955A (zh) | 2010-12-01 |

| KR20100111666A (ko) | 2010-10-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7391645B2 (en) | Non-volatile memory and method with compensation for source line bias errors | |

| US7764547B2 (en) | Regulation of source potential to combat cell source IR drop | |

| US7499324B2 (en) | Non-volatile memory and method with control gate compensation for source line bias errors | |

| JP5086443B2 (ja) | ソースレベルを追跡するためのワード線基準レベルの読み出し、ベリファイ | |

| US7239551B2 (en) | Non-volatile memory and method with reduced neighboring field errors | |

| US9368224B2 (en) | Self-adjusting regulation current for memory array source line | |

| US8737132B2 (en) | Charge cycling by equalizing the source and bit line levels between pulses during no-verify write operations for NAND flash memory | |

| US9177663B2 (en) | Dynamic regulation of memory array source line | |

| JP2010522951A (ja) | 不揮発性メモリおよびワード線沿いの電圧降下を補償する方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111124 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111124 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20111124 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20111220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120117 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120321 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120328 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121113 |