JP2010033631A - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP2010033631A JP2010033631A JP2008192470A JP2008192470A JP2010033631A JP 2010033631 A JP2010033631 A JP 2010033631A JP 2008192470 A JP2008192470 A JP 2008192470A JP 2008192470 A JP2008192470 A JP 2008192470A JP 2010033631 A JP2010033631 A JP 2010033631A

- Authority

- JP

- Japan

- Prior art keywords

- power

- voltage

- chip

- reset

- switch element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/20—Initialising; Data preset; Chip identification

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

- G11C5/063—Voltage and signal distribution in integrated semi-conductor memory access lines, e.g. word-line, bit-line, cross-over resistance, propagation delay

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/143—Detection of memory cassette insertion or removal; Continuity checks of supply or ground lines; Detection of supply variations, interruptions or levels ; Switching between alternative supplies

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/20—Memory cell initialisation circuits, e.g. when powering up or down, memory clear, latent image memory

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/22—Modifications for ensuring a predetermined initial state when the supply voltage has been applied

- H03K17/223—Modifications for ensuring a predetermined initial state when the supply voltage has been applied in field-effect transistor switches

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Read Only Memory (AREA)

- Static Random-Access Memory (AREA)

Abstract

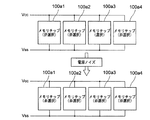

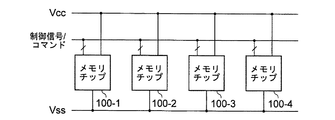

【解決手段】チップアドレス指定されることにより動作する複数のメモリチップを備えた不揮発性半導体記憶装置であって、リセット時においてチップアドレス指定されて動作するように設定されている第1のメモリチップと、リセット時においてチップアドレス指定されず動作しないように設定されている第2のメモリチップと、を備える。第1のメモリチップおよび第2のメモリチップは、電源投入後、電源電圧を検知し、電源電圧が所定値以上になった場合に、その動作を初期化するためのリセット信号を出力するパワーオンリセット回路を、それぞれ有する。

【選択図】図1

Description

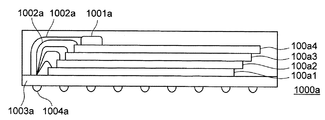

図1は、比較例である4個のメモリチップ100a1〜100a4を積層したマルチチップパッケージ製品(不揮発性半導体記憶装置1000a)の模式的な断面の一例を示す断面図である。

ここで、実施例2と同様に、メモリチップ100−1のパワーオンリセット回路418において、切換回路418bは、信号CADD1(“High”レベル)が入力されるように設定されている。

12 アドレスバッファ

13 カラムデコーダ

14 ロウデコーダ

15 センスアンプ

17 入出力バッファ

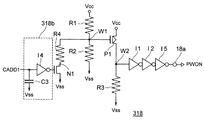

18 パワーオンリセット回路

18a 出力端子

18b 切換回路

19 制御回路

20 電圧生成回路

21 チップアドレスデコード回路

21a 論理和回路

21b インバータ

22 チップアドレスセット回路

100−1〜100−4、100a1〜100a4 メモリチップ

1000、1000a 不揮発性半導体記憶装置

1001、1001a コントローラ

1002、1002a ワイヤ

1003、1003a 基板

1004、1004a 半田ボール

2000 携帯電話

2001 メイン画面

2002 本体上部

2003 キーパッド

2004 本体下部

C1、C2、C3、C4、C5 コンデンサ

F1 フリップフロップ

I1、I2、I3、I4、I5、I6、I7 インバータ

P1、P6 PMOSトランジスタ

P2、P3、P4、P5、N1、N2 スイッチ素子

PWOM リセット信号

Q フリップフロップの出力

R リセット端子

R1 第1の分圧抵抗

R1a、R1b 分圧抵抗

R2 第2の分圧抵抗

R3 出力抵抗

R4 分圧比調整抵抗

R5 調整抵抗

S セット端子

W1 第1の接点

W2 第2の接点

W3 第3の接点

W4 第4の接点

W5 第5の接点

W6 第6の接点

X1、X3 NAND回路

X2 AND回路

Claims (5)

- チップアドレス指定されることにより動作する複数のメモリチップを備えた不揮発性半導体記憶装置であって、

リセット時においてチップアドレス指定されて動作するように設定されている第1のメモリチップと、

リセット時においてチップアドレス指定されず動作しないように設定されている第2のメモリチップと、を備え、

前記第1のメモリチップおよび前記第2のメモリチップは、電源投入後、電源電圧を検知し、前記電源電圧が所定値以上になった場合に、その動作を初期化するためのリセット信号を出力するパワーオンリセット回路を、それぞれ有し、

前記パワーオンリセット回路は、

電源に一端が接続された第1の分圧抵抗と、

前記第1の分圧抵抗の他端と接地との間に接続された第2の分圧抵抗と、

前記電源にソースが接続され、前記第1の分圧抵抗と前記第2の分圧抵抗との間の第1の接点の電圧に応じた電圧がゲートに印加されるPMOSトランジスタと、

前記PMOSトランジスタのドレインと前記接地との間に接続された出力抵抗と、

前記電源と前記第1の接点との間に接続されたスイッチ素子と、

前記電源と前記第1の接点との間で、前記スイッチ素子と直列に接続された分圧比調整抵抗と、

前記スイッチ素子のオン/オフを切り換えるための切換信号を出力する切換回路と、

前記PMOSトランジスタと前記出力抵抗との間の第2の接点に接続され、前記リセット信号を出力するための出力端子と、を含み、

前記第1のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記パワーオンリセット回路の前記スイッチ素子を、オンし、

前記第2のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記パワーオンリセット回路の前記スイッチ素子を、オフする

ことを特徴とする不揮発性半導体記憶装置。 - チップアドレス指定されることにより動作する複数のメモリチップを備えた不揮発性半導体記憶装置であって、

リセット時においてチップアドレス指定されて動作するように設定されている第1のメモリチップと、

リセット時においてチップアドレス指定されず動作しないように設定されている第2のメモリチップと、を備え、

前記第1のメモリチップおよび前記第2のメモリチップは、電源投入後、電源電圧を検知し、前記電源電圧が所定値以上になった場合に、その動作を初期化するためのリセット信号を出力するパワーオンリセット回路を、それぞれ有し、

前記パワーオンリセット回路は、

電源に一端が接続された第1の分圧抵抗と、

前記第1の分圧抵抗の他端と接地との間に接続された第2の分圧抵抗と、

前記電源にソースが接続され、前記第1の分圧抵抗と前記第2の分圧抵抗との間の第1の接点の電圧に応じた電圧がゲートに印加されるPMOSトランジスタと、

前記PMOSトランジスタのドレインと接地との間に接続された出力抵抗と、

前記接地と前記第1の接点との間に接続されたスイッチ素子と、

前記接地と前記第1の接点との間で、前記スイッチ素子と直列に接続された分圧比調整抵抗と、

前記スイッチ素子のオン/オフを切り換えるための切換信号を出力する切換回路と、

前記PMOSトランジスタと前記出力抵抗との間の第2の接点に接続され、前記リセット信号を出力するための出力端子と、を含み、

前記第1のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記スイッチ素子を、オフし、

前記第2のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記スイッチ素子を、オンする

ことを特徴とする不揮発性半導体記憶装置。 - チップアドレス指定されることにより動作する複数のメモリチップを備えた不揮発性半導体記憶装置であって、

リセット時においてチップアドレス指定されて動作するように設定されている第1のメモリチップと、

リセット時においてチップアドレス指定されず動作しないように設定されている第2のメモリチップと、を備え、

前記第1のメモリチップおよび前記第2のメモリチップは、電源投入後、電源電圧を検知し、前記電源電圧が所定値以上になった場合に、その動作を初期化するためのリセット信号を出力するパワーオンリセット回路を、それぞれ有し、

前記パワーオンリセット回路は、

電源に一端が接続された第1の分圧抵抗と、

前記第1の分圧抵抗の他端と接地との間に接続された第2の分圧抵抗と、

前記電源にソースが接続され、前記第1の分圧抵抗と前記第2の分圧抵抗との間の第1の接点の電圧に応じた電圧がゲートに印加されるPMOSトランジスタと、

前記PMOSトランジスタのドレインと接地との間に接続された出力抵抗と、

前記接地と前記第1の接点との間に接続されたスイッチ素子と、

前記接地と前記第1の接点との間で、前記スイッチ素子と直列に接続された分圧比調整抵抗と、

前記スイッチ素子のオン/オフを切り換えるための切換信号を出力する切換回路と、

前記PMOSトランジスタと前記出力抵抗との間の第2の接点に接続され、前記リセット信号を出力するための出力端子と、を含み、

前記第1のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記パワーオンリセット回路の前記スイッチ素子を、オフし、

前記第2のメモリチップの前記パワーオンリセット回路において、前記切換回路は、前記スイッチ素子を、前記電源電圧が設定電圧未満であるときには、オフし、前記電源電圧が前記設定電圧以上であるときには、オンする

ことを特徴とする不揮発性半導体記憶装置。 - 前記切換回路は、チップアドレスに基づいて、前記スイッチ素子のオン/オフを切り換える

ことを特徴とすることを特徴とする請求項1ないし3の何れかに記載の不揮発性半導体記憶装置。 - 前記第1のメモリチップおよび前記第2のメモリチップは、NAND型フラッシュメモリチップである

ことを特徴とする請求項1ないし4の何れかに記載の不揮発性半導体記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192470A JP5086929B2 (ja) | 2008-07-25 | 2008-07-25 | 不揮発性半導体記憶装置 |

| US12/407,938 US7848170B2 (en) | 2008-07-25 | 2009-03-20 | Nonvolatile semiconductor memory |

| KR1020090067628A KR101022127B1 (ko) | 2008-07-25 | 2009-07-24 | 비휘발성 반도체 메모리 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008192470A JP5086929B2 (ja) | 2008-07-25 | 2008-07-25 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010033631A true JP2010033631A (ja) | 2010-02-12 |

| JP5086929B2 JP5086929B2 (ja) | 2012-11-28 |

Family

ID=41568535

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008192470A Active JP5086929B2 (ja) | 2008-07-25 | 2008-07-25 | 不揮発性半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7848170B2 (ja) |

| JP (1) | JP5086929B2 (ja) |

| KR (1) | KR101022127B1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190111430A (ko) * | 2018-03-22 | 2019-10-02 | 에스케이하이닉스 주식회사 | 리셋동작을 수행하는 반도체패키지 및 반도체시스템 |

| US10672433B2 (en) | 2017-03-24 | 2020-06-02 | Toshiba Memory Corporation | Semiconductor memory device |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8605536B2 (en) | 2012-02-13 | 2013-12-10 | Qualcomm Incorporated | Power-on-reset (POR) circuits for resetting memory devices, and related circuits, systems, and methods |

| US8830780B2 (en) | 2013-01-15 | 2014-09-09 | Qualcomm Incorporated | System and method of performing power on reset for memory array circuits |

| KR20170006980A (ko) * | 2015-07-10 | 2017-01-18 | 에스케이하이닉스 주식회사 | 파워 온 리셋 회로 및 이를 포함하는 반도체 메모리 장치 |

| WO2022027403A1 (en) | 2020-08-06 | 2022-02-10 | Yangtze Memory Technologies Co., Ltd. | Multi-die peak power management for three-dimensional memory |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09167217A (ja) * | 1995-12-14 | 1997-06-24 | Hitachi Ltd | マルチチップicカード及びそれを用いたicカードシステム |

| JPH11120075A (ja) * | 1997-10-20 | 1999-04-30 | Toshiba Corp | 半導体記憶装置及び半導体記憶システム |

| JPH11150452A (ja) * | 1997-11-17 | 1999-06-02 | Toshiba Microelectronics Corp | レベル変換回路および液晶表示装置 |

| JP2002100974A (ja) * | 2000-09-21 | 2002-04-05 | Toshiba Corp | 半導体装置 |

| JP2002150788A (ja) * | 2000-11-06 | 2002-05-24 | Fujitsu Ltd | 半導体装置及び半導体装置初期設定方法 |

| JP2002329791A (ja) * | 2001-04-27 | 2002-11-15 | Toshiba Corp | 電圧発生回路 |

| US20030218479A1 (en) * | 2000-09-02 | 2003-11-27 | Actel Corporation, A California Corporation | Tileable field-programmable gate array architecture |

| JP2004152405A (ja) * | 2002-10-30 | 2004-05-27 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2008077779A (ja) * | 2006-09-22 | 2008-04-03 | Toshiba Corp | 半導体記憶装置 |

| JP2008077834A (ja) * | 2007-12-10 | 2008-04-03 | Toshiba Corp | 不揮発性半導体記憶装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6208542B1 (en) * | 1998-06-30 | 2001-03-27 | Sandisk Corporation | Techniques for storing digital data in an analog or multilevel memory |

| JP3802239B2 (ja) * | 1998-08-17 | 2006-07-26 | 株式会社東芝 | 半導体集積回路 |

| KR100394757B1 (ko) * | 2000-09-21 | 2003-08-14 | 가부시끼가이샤 도시바 | 반도체 장치 |

| JP4284247B2 (ja) * | 2004-08-13 | 2009-06-24 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7660161B2 (en) * | 2007-01-19 | 2010-02-09 | Silicon Storage Technology, Inc. | Integrated flash memory systems and methods for load compensation |

-

2008

- 2008-07-25 JP JP2008192470A patent/JP5086929B2/ja active Active

-

2009

- 2009-03-20 US US12/407,938 patent/US7848170B2/en active Active

- 2009-07-24 KR KR1020090067628A patent/KR101022127B1/ko active IP Right Grant

Patent Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09167217A (ja) * | 1995-12-14 | 1997-06-24 | Hitachi Ltd | マルチチップicカード及びそれを用いたicカードシステム |

| JPH11120075A (ja) * | 1997-10-20 | 1999-04-30 | Toshiba Corp | 半導体記憶装置及び半導体記憶システム |

| JPH11150452A (ja) * | 1997-11-17 | 1999-06-02 | Toshiba Microelectronics Corp | レベル変換回路および液晶表示装置 |

| US20030218479A1 (en) * | 2000-09-02 | 2003-11-27 | Actel Corporation, A California Corporation | Tileable field-programmable gate array architecture |

| JP2002100974A (ja) * | 2000-09-21 | 2002-04-05 | Toshiba Corp | 半導体装置 |

| JP2002150788A (ja) * | 2000-11-06 | 2002-05-24 | Fujitsu Ltd | 半導体装置及び半導体装置初期設定方法 |

| JP2002329791A (ja) * | 2001-04-27 | 2002-11-15 | Toshiba Corp | 電圧発生回路 |

| JP2004152405A (ja) * | 2002-10-30 | 2004-05-27 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2008077779A (ja) * | 2006-09-22 | 2008-04-03 | Toshiba Corp | 半導体記憶装置 |

| JP2008077834A (ja) * | 2007-12-10 | 2008-04-03 | Toshiba Corp | 不揮発性半導体記憶装置 |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10672433B2 (en) | 2017-03-24 | 2020-06-02 | Toshiba Memory Corporation | Semiconductor memory device |

| US10783933B2 (en) | 2017-03-24 | 2020-09-22 | Toshiba Memory Corporation | Semiconductor memory device |

| KR20190111430A (ko) * | 2018-03-22 | 2019-10-02 | 에스케이하이닉스 주식회사 | 리셋동작을 수행하는 반도체패키지 및 반도체시스템 |

| KR102504180B1 (ko) | 2018-03-22 | 2023-02-28 | 에스케이하이닉스 주식회사 | 리셋동작을 수행하는 반도체패키지 및 반도체시스템 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101022127B1 (ko) | 2011-03-17 |

| US20100020628A1 (en) | 2010-01-28 |

| JP5086929B2 (ja) | 2012-11-28 |

| KR20100011942A (ko) | 2010-02-03 |

| US7848170B2 (en) | 2010-12-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10410686B2 (en) | Memory modules storing a trimming control code associated with a minimum level of a power supply voltage, methods of operating the memory modules, and test systems of the memory modules | |

| KR100912561B1 (ko) | 반도체 기억 장치 | |

| JP5086929B2 (ja) | 不揮発性半導体記憶装置 | |

| US7760553B2 (en) | Fuse circuit and flash memory device having the same | |

| KR102496506B1 (ko) | 복수의 퓨즈 비트들을 독출하는 오티피 메모리 장치 | |

| US10031792B2 (en) | Flash memory | |

| CN108182962B (zh) | 包括虚拟故障产生器的存储器装置及其存储单元修复方法 | |

| KR102515463B1 (ko) | 비휘발성 메모리 장치와, 이의 리드 및 라이트 방법 | |

| KR102520496B1 (ko) | 오티피 메모리 장치 및 오피 메모리 장치의 테스트 방법 | |

| KR101391358B1 (ko) | 반도체 집적회로 및 그것의 초기화 정보 읽기 방법 | |

| US9424914B2 (en) | Resistive memory apparatus and memory cell thereof | |

| JP2008011446A (ja) | 半導体集積回路 | |

| JP2007035115A (ja) | 半導体記憶装置 | |

| JP5361685B2 (ja) | 半導体集積回路 | |

| US10629249B2 (en) | Semiconductor device and semiconductor system | |

| CN115413357A (zh) | 供电电压选择电路 | |

| JP6026270B2 (ja) | 半導体装置 | |

| JP2012069565A (ja) | 半導体集積回路及び制御方法 | |

| JP2008004196A (ja) | 半導体メモリ装置 | |

| US9716493B2 (en) | Input circuit and semiconductor apparatus including the input circuit | |

| US9368229B2 (en) | Semiconductor integrated circuit device including fuse block | |

| JP2009129472A (ja) | 半導体記憶装置 | |

| JP6103815B2 (ja) | 不揮発性メモリ回路、及び半導体装置 | |

| JP2009134828A (ja) | 半導体装置 | |

| JP2013186920A (ja) | 不揮発性半導体記憶装置及びメモリシステム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100915 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120801 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120810 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120907 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5086929 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |