JP2010028352A - インバータ回路 - Google Patents

インバータ回路 Download PDFInfo

- Publication number

- JP2010028352A JP2010028352A JP2008185956A JP2008185956A JP2010028352A JP 2010028352 A JP2010028352 A JP 2010028352A JP 2008185956 A JP2008185956 A JP 2008185956A JP 2008185956 A JP2008185956 A JP 2008185956A JP 2010028352 A JP2010028352 A JP 2010028352A

- Authority

- JP

- Japan

- Prior art keywords

- nmos transistor

- voltage

- inverter circuit

- input

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/20—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits characterised by logic function, e.g. AND, OR, NOR, NOT circuits

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

Abstract

【解決手段】入力端子INとNMOSトランジスタN1のサブストレートゲートを、高抵抗R1を用いてDC結合したことから、簡単な回路で、NMOSトランジスタN1のしきい値電圧の変更が、入力信号Sinの立ち上がり及び立ち下り速度に依存することがなく、しかも、インバータ回路の入力インピーダンスの低下を抑えることができ、更にNMOSトランジスタN1のリーク電流の増加も抑えることができ、NMOSトランジスタN1のスイッチング時にしきい値電圧を下げることができ、更にチップ面積の増加を抑えることができるようにした。

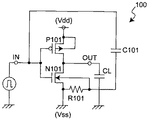

【選択図】図1

Description

図6のインバータ回路100は、PMOSトランジスタP101、NMOSトランジスタN101、抵抗R101、コンデンサC101で構成され、出力端子OUTには負荷CLが接続されている。

図6において、入力端子INに入力された入力電圧がローレベル、すなわち接地電圧Vssである場合、PMOSトランジスタP101がオンすると共にNMOSトランジスタN101がオフしているため、出力端子OUTはハイレベルになる。

このとき、コンデンサC101の入力端子INに接続された端部はハイレベルに引き上げられるため、コンデンサC101は入力電圧によって充電される。このときの充電電流が抵抗R101に流れるため、抵抗R101には電圧降下が発生し、NMOSトランジスタN101のサブストレートゲートの電圧を上昇させる。該サブストレートゲートの電圧が上昇すると、基板バイアス効果の影響でNMOSトランジスタN101のしきい値電圧が低下するため、入力電圧がより小さい電圧でもNMOSトランジスタN101はオンし、高速動作が可能になる。

入力電圧がハイレベルからローレベルに変化すると、PMOSトランジスタP101がオンすると共にNMOSトランジスタN101がオフし、出力端子OUTはハイレベルに変化する。

このように、図6のインバータ回路は、入力端子INの電圧がローレベルからハイレベルに変化する場合に、NMOSトランジスタN101のしきい値電圧を下げることで、高速動作を可能にしており、NMOSトランジスタN101のオフ時はサブストレートゲートを接地電圧Vssに保つため、リーク電流の増加も抑えることができる。

更に、コンデンサC101を追加しなければならず、チップ面積が大きくなるという問題もあった。

ゲートが前記入力端子に接続されたソース接地のMOSトランジスタと、

該MOSトランジスタに直列に接続された負荷抵抗と、

該MOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えるものである。

ゲートが前記入力端子に接続され、ソースが正側電源電圧に接続されたPMOSトランジスタと、

ゲートが前記入力端子に接続され、ソースが負側電源電圧に接続されたNMOSトランジスタと、

前記PMOSトランジスタと該NMOSトランジスタの各ドレインとの間に接続された負荷抵抗と、

前記NMOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えるものである。

ゲートが前記入力端子に接続され、ソースが正側電源電圧に接続されたPMOSトランジスタと、

ゲートが前記入力端子に接続され、ソースが負側電源電圧に接続されたNMOSトランジスタと、

前記PMOSトランジスタと該NMOSトランジスタの各ドレインとの間に接続された負荷抵抗と、

前記PMOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えるものである。

また、前記入力端子と前記MOSトランジスタのサブストレートゲートとをDC結合させたことから、前記入力信号の電圧が徐々に変化するような場合においても、インバータ回路のしきい値電圧を低下させることができる。

更に、コンデンサを使用しないため、チップ面積の増加を抑制することができる。

第1の実施の形態.

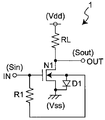

図1は、本発明の第1の実施の形態におけるインバータ回路の回路例を示した図である。

図1におけるインバータ回路1は、入力端子INに入力された入力信号Sinの信号レベルを反転させて出力端子OUTから出力信号Soutとして出力するものであり、NMOSトランジスタN1、負荷抵抗RL及び抵抗R1で構成されている。なお、図1では、NMOSトランジスタN1のサブストレートゲートとソースとの間に接続されているダイオードD1は、NMOSトランジスタN1を半導体チップ上に形成した際に形成される寄生ダイオードである。

また、入力信号Sinがハイレベルである状態では、NMOSトランジスタN1のしきい値電圧は小さいままであるが、NMOSトランジスタN1がオン状態であることから、リーク電流は問題にならない。

入力信号Sinがハイレベルからローレベルに変化すると、NMOSトランジスタN1はオフし、出力端子OUTはハイレベルになる。NMOSトランジスタN1のサブストレートゲートもローレベルに戻るため、前記のようにNMOSトランジスタN1のしきい値電圧が大きくなり、リーク電流の増加を抑えることができる。

図2において、NMOSトランジスタN1は、Psub基板上にNウエル領域NWが作られ、更にNウエル領域NW内に作られたPウエル領域PWに形成されている。Pウエル領域PWには2つのN領域と1つのP領域が形成されている。一方の該N領域がソースSを、他方の該N領域がドレインDをそれぞれなし、該P領域がサブストレートゲートSGをなしている。また、ソースSとドレインDの各N領域間のチップ表面には絶縁層が形成され、該絶縁層の上にゲート電極Gが形成されている。

前記第1の実施の形態では、NMOSトランジスタを使用してインバータ回路を形成したが、該NMOSトランジスタの代わりにPMOSトランジスタを使用してもよく、このようにしたものを本発明の第2の実施の形態とする。

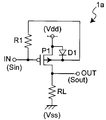

図3は、本発明の第2の実施の形態におけるインバータ回路の回路例を示した図である。なお、図3では、図1と同じもの又は同様のものは同じ符号で示している。

図3におけるインバータ回路1aは、入力端子INに入力された入力信号Sinの信号レベルを反転させて出力端子OUTから出力信号Soutとして出力するものであり、PMOSトランジスタP1、負荷抵抗RL及び抵抗R1で構成されている。なお、図3では、PMOSトランジスタP1のサブストレートゲートとソースとの間に接続されているダイオードD1は、PMOSトランジスタP1を半導体チップ上に形成した際に形成される寄生ダイオードである。

また、入力信号Sinがローレベルである状態では、PMOSトランジスタP1のしきい値電圧は小さいままであるが、PMOSトランジスタP1がオン状態であることから、リーク電流は問題にならない。

入力信号Sinがローレベルからハイレベルに変化すると、PMOSトランジスタP1はオフし、出力端子OUTはローレベルになる。PMOSトランジスタP1のサブストレートゲートの電圧もハイレベルに戻るため、前記のようにPMOSトランジスタP1のしきい値電圧が大きくなり、リーク電流の増加を抑えることができる。

前記第1の実施の形態ではNMOSトランジスタを使用してインバータ回路を形成するようにしたが、CMOS構成でインバータ回路を形成するようにしてもよく、このようにしたものを本発明の第3の実施の形態とする。

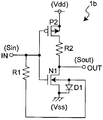

図4は、本発明の第3の実施の形態におけるインバータ回路の回路例を示した図である。なお、図4では、図1と同じもの又は同様のものは同じ符号で示している。

図4におけるインバータ回路1bは、入力端子INに入力された入力信号Sinの信号レベルを反転させて出力端子OUTから出力信号Soutとして出力するものであり、NMOSトランジスタN1、PMOSトランジスタP2及び抵抗R1,R2で構成されている。なお、図4では、ダイオードD1は、NMOSトランジスタN1を半導体チップ上に形成した際に形成される寄生ダイオードであり、抵抗R2は負荷抵抗をなしている。

なお、抵抗R2は、PMOSトランジスタP2とNMOSトランジスタN1が同時にオンしたときの貫通電流を低減させるためのものであり、インバータ回路1bの出力端子OUTは、抵抗R2の両端のいずれか一方に接続するようにすればよく、抵抗R2を2つの抵抗で構成し、該各抵抗の接続部を出力端子OUTに接続するようにしてもよい。

また、入力信号Sinがハイレベルである状態では、PMOSトランジスタP2がオフすると共にNMOSトランジスタN1がオンする。このとき、NMOSトランジスタN1のしきい値電圧は小さいままであるが、NMOSトランジスタN1はオン状態であることから、リーク電流は問題にならない。

入力信号Sinがハイレベルからローレベルに変化すると、PMOSトランジスタP2がオンすると共にNMOSトランジスタN1がオフし、出力端子OUTはハイレベルになる。NMOSトランジスタN1のサブストレートゲートもローレベルに戻るため、前記のようにNMOSトランジスタN1のしきい値電圧が大きくなり、リーク電流の増加を抑えることができる。

前記第2の実施の形態ではPMOSトランジスタを使用してインバータ回路を形成するようにしたが、CMOS構成でインバータ回路を形成するようにしてもよく、このようにしたものを本発明の第4の実施の形態とする。

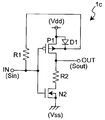

図5は、本発明の第4の実施の形態におけるインバータ回路の回路例を示した図である。なお、図5では、図3と同じもの又は同様のものは同じ符号で示している。

図5におけるインバータ回路1cは、入力端子INに入力された入力信号Sinの信号レベルを反転させて出力端子OUTから出力信号Soutとして出力するものであり、NMOSトランジスタN2、PMOSトランジスタP1、負荷抵抗RL及び抵抗R1,R2で構成されている。なお、図5では、ダイオードD1は、PMOSトランジスタP1を半導体チップ上に形成した際に形成される寄生ダイオードであり、抵抗R2は負荷抵抗をなしている。

なお、抵抗R2は、PMOSトランジスタP1とNMOSトランジスタN2が同時にオンしたときの貫通電流を低減させるためのものであり、インバータ回路1cの出力端子OUTは、抵抗R2の両端のいずれか一方に接続するようにすればよく、抵抗R2を2つの抵抗で構成し、該各抵抗の接続部を出力端子OUTに接続するようにしてもよい。

また、入力信号Sinがローレベルである状態では、NMOSトランジスタN2がオフすると共にPMOSトランジスタP1がオンする。このとき、PMOSトランジスタP1のしきい値電圧は小さいままであるが、PMOSトランジスタP1がオン状態であることから、リーク電流は問題にならない。

入力信号Sinがローレベルからハイレベルに変化すると、PMOSトランジスタP1はオフし、出力端子OUTはローレベルになる。PMOSトランジスタP1のサブストレートゲートの電圧もハイレベルに戻るため、前記のようにPMOSトランジスタP1のしきい値電圧が大きくなり、リーク電流の増加を抑えることができる。

N1,N2 NMOSトランジスタ

P1,P2 PMOSトランジスタ

RL 負荷抵抗

R1,R2 抵抗

D1 寄生ダイオード

Claims (4)

- 入力端子に入力された入力信号の信号レベルを反転させて出力端子から出力するインバータ回路において、

ゲートが前記入力端子に接続されたソース接地のMOSトランジスタと、

該MOSトランジスタに直列に接続された負荷抵抗と、

該MOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えることを特徴とするインバータ回路。 - 入力端子に入力された入力信号の信号レベルを反転させて出力端子から出力するCMOS構成のインバータ回路において、

ゲートが前記入力端子に接続され、ソースが正側電源電圧に接続されたPMOSトランジスタと、

ゲートが前記入力端子に接続され、ソースが負側電源電圧に接続されたNMOSトランジスタと、

前記PMOSトランジスタと該NMOSトランジスタの各ドレインとの間に接続された負荷抵抗と、

前記NMOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えることを特徴とするインバータ回路。 - 入力端子に入力された入力信号の信号レベルを反転させて出力端子から出力するCMOS構成のインバータ回路において、

ゲートが前記入力端子に接続され、ソースが正側電源電圧に接続されたPMOSトランジスタと、

ゲートが前記入力端子に接続され、ソースが負側電源電圧に接続されたNMOSトランジスタと、

前記PMOSトランジスタと該NMOSトランジスタの各ドレインとの間に接続された負荷抵抗と、

前記PMOSトランジスタのゲートとサブストレートゲートとの間に接続された抵抗と、

を備えることを特徴とするインバータ回路。 - 前記入力端子とサブストレートゲートとの間に前記抵抗が接続された前記MOSトランジスタは、サブストレートゲートの電極が、ドレインを形成する半導体領域側に配置された半導体領域に形成されることを特徴とする請求項1、2又は3記載のインバータ回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185956A JP5181893B2 (ja) | 2008-07-17 | 2008-07-17 | インバータ回路 |

| US12/492,873 US7755395B2 (en) | 2008-07-17 | 2009-06-26 | Inverter circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185956A JP5181893B2 (ja) | 2008-07-17 | 2008-07-17 | インバータ回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010028352A true JP2010028352A (ja) | 2010-02-04 |

| JP5181893B2 JP5181893B2 (ja) | 2013-04-10 |

Family

ID=41529776

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008185956A Expired - Fee Related JP5181893B2 (ja) | 2008-07-17 | 2008-07-17 | インバータ回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7755395B2 (ja) |

| JP (1) | JP5181893B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014138423A (ja) * | 2013-01-15 | 2014-07-28 | Triquint Semiconductor Inc | 抵抗分圧器を有するスイッチ装置 |

| JPWO2017057112A1 (ja) * | 2015-10-02 | 2018-05-17 | 国立研究開発法人産業技術総合研究所 | マルチプレクサ及びこれを用いた集積回路 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW201013925A (en) * | 2008-09-17 | 2010-04-01 | Grand Gem Semiconductor Co Ltd | MOS transistor having reverse current limiting and a voltage converter applied with the MOS transistor |

| US20100102872A1 (en) * | 2008-10-29 | 2010-04-29 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dynamic Substrate Bias for PMOS Transistors to Alleviate NBTI Degradation |

| KR101694877B1 (ko) | 2009-10-16 | 2017-01-11 | 삼성전자주식회사 | 그라핀 소자 및 그 제조 방법 |

| CZ303698B6 (cs) * | 2011-07-19 | 2013-03-20 | Vysoké ucení technické v Brne Fakulta elektrotechniky a komunikacních technologií | Zapojení FG MOS a QFG MOS tranzistoru pro analogové integrované obvody |

| CN102611417A (zh) * | 2011-12-21 | 2012-07-25 | 上海博泰悦臻电子设备制造有限公司 | 降低漏电流的电路 |

| TW201417496A (zh) * | 2012-10-24 | 2014-05-01 | Keystone Semiconductor Corp | 電源開啟重置電路 |

| US8803591B1 (en) * | 2013-11-06 | 2014-08-12 | Freescale Semiconductor, Inc. | MOS transistor with forward bulk-biasing circuit |

| CN104378102A (zh) * | 2014-11-21 | 2015-02-25 | 无锡中星微电子有限公司 | 低功耗逻辑电路 |

| US11705499B2 (en) * | 2021-06-11 | 2023-07-18 | Nanya Technology Corporation | Semiconductor device with inverter and method for fabricating the same |

| US20230368827A1 (en) * | 2022-05-13 | 2023-11-16 | Changxin Memory Technologies, Inc. | Drive circuit, method for driving drive circuit, and memory |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326890A (ja) * | 1992-05-07 | 1993-12-10 | Nec Corp | 出力バッファ回路 |

| JPH08251012A (ja) * | 1995-03-15 | 1996-09-27 | Mitsubishi Electric Corp | Cmos論理回路 |

| JPH08265123A (ja) * | 1995-03-22 | 1996-10-11 | Nec Corp | ドライバ回路 |

| JPH11346151A (ja) * | 1998-03-30 | 1999-12-14 | Nec Corp | 論理回路 |

| JPH11355123A (ja) * | 1998-06-11 | 1999-12-24 | Mitsubishi Electric Corp | 動的しきい値mosトランジスタを用いたバッファ |

| JP2004072709A (ja) * | 2002-06-10 | 2004-03-04 | Renesas Technology Corp | レベル変換回路 |

| JP2005311359A (ja) * | 2004-04-16 | 2005-11-04 | Zarlink Semiconductor Ab | トランジスタウェルへのバイアス印加方法、動作電圧低減方法、差動増幅器回路、回路、および集積回路 |

| JP2006237760A (ja) * | 2005-02-23 | 2006-09-07 | Renesas Technology Corp | 半導体集積回路装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4418292A (en) * | 1980-05-28 | 1983-11-29 | Raytheon Company | Logic gate having a noise immunity circuit |

| JPS59121939A (ja) | 1982-12-28 | 1984-07-14 | Fujitsu Ltd | ウエ−ハのブラツシング方法 |

| JPH0199317A (ja) | 1987-10-12 | 1989-04-18 | Ricoh Co Ltd | 温度補償付レベルシフト回路 |

| JPH01276920A (ja) | 1988-04-28 | 1989-11-07 | Ricoh Co Ltd | アナログ・スイッチ |

| JPH01300616A (ja) | 1988-05-27 | 1989-12-05 | Ricoh Co Ltd | シュミット回路の反転レベル制御回路 |

| JPH04273716A (ja) | 1991-02-28 | 1992-09-29 | Ricoh Co Ltd | アナログスイッチ |

| US6229405B1 (en) * | 1997-11-14 | 2001-05-08 | Seiko Epson Corporation | Low-voltage oscillation amplifying circuit |

| JP2003101403A (ja) | 2001-09-26 | 2003-04-04 | Ricoh Co Ltd | 入力回路 |

| JP3986391B2 (ja) | 2002-08-08 | 2007-10-03 | 株式会社リコー | 定電圧電源回路 |

| JP3923397B2 (ja) | 2002-09-17 | 2007-05-30 | 株式会社リコー | レベルトランスレータ回路 |

| JP2006147845A (ja) | 2004-11-19 | 2006-06-08 | Techno Network Shikoku Co Ltd | 半導体装置 |

| JP2006148515A (ja) | 2004-11-19 | 2006-06-08 | Ricoh Co Ltd | 遅延回路及び発振回路 |

-

2008

- 2008-07-17 JP JP2008185956A patent/JP5181893B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-26 US US12/492,873 patent/US7755395B2/en not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326890A (ja) * | 1992-05-07 | 1993-12-10 | Nec Corp | 出力バッファ回路 |

| JPH08251012A (ja) * | 1995-03-15 | 1996-09-27 | Mitsubishi Electric Corp | Cmos論理回路 |

| JPH08265123A (ja) * | 1995-03-22 | 1996-10-11 | Nec Corp | ドライバ回路 |

| JPH11346151A (ja) * | 1998-03-30 | 1999-12-14 | Nec Corp | 論理回路 |

| JPH11355123A (ja) * | 1998-06-11 | 1999-12-24 | Mitsubishi Electric Corp | 動的しきい値mosトランジスタを用いたバッファ |

| JP2004072709A (ja) * | 2002-06-10 | 2004-03-04 | Renesas Technology Corp | レベル変換回路 |

| JP2005311359A (ja) * | 2004-04-16 | 2005-11-04 | Zarlink Semiconductor Ab | トランジスタウェルへのバイアス印加方法、動作電圧低減方法、差動増幅器回路、回路、および集積回路 |

| JP2006237760A (ja) * | 2005-02-23 | 2006-09-07 | Renesas Technology Corp | 半導体集積回路装置 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014138423A (ja) * | 2013-01-15 | 2014-07-28 | Triquint Semiconductor Inc | 抵抗分圧器を有するスイッチ装置 |

| JPWO2017057112A1 (ja) * | 2015-10-02 | 2018-05-17 | 国立研究開発法人産業技術総合研究所 | マルチプレクサ及びこれを用いた集積回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7755395B2 (en) | 2010-07-13 |

| JP5181893B2 (ja) | 2013-04-10 |

| US20100013519A1 (en) | 2010-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5181893B2 (ja) | インバータ回路 | |

| JP5955924B2 (ja) | 静電放電保護回路 | |

| JP3865689B2 (ja) | レベルシフト回路 | |

| JP4597044B2 (ja) | 逆流防止回路 | |

| US7336101B2 (en) | Control circuit and method | |

| JP5211889B2 (ja) | 半導体集積回路 | |

| JP2008085571A (ja) | 半導体集積回路 | |

| US7759986B2 (en) | Gate oxide protected I/O circuit | |

| JP2006217540A (ja) | 半導体集積回路および半導体集積回路の制御方法 | |

| JP2008131266A (ja) | 半導体装置 | |

| JP2012203528A (ja) | ボルテージ・レギュレータ | |

| JP2011103607A (ja) | 入力回路 | |

| KR20090104362A (ko) | 인버터 회로 | |

| JP5005970B2 (ja) | 電圧制御回路及び電圧制御回路を有する半導体集積回路 | |

| US20100295593A1 (en) | Delay circuit | |

| US8405428B2 (en) | Semiconductor integrated circuit | |

| TWI479803B (zh) | 輸出級電路 | |

| US20070236253A1 (en) | Semiconductor integrated circuit | |

| JP3429213B2 (ja) | 集積回路 | |

| KR101622827B1 (ko) | 슈미트 트리거 회로를 이용한 논리 게이트 | |

| US20090284287A1 (en) | Output buffer circuit and integrated circuit | |

| JP2005184573A (ja) | インバータ回路 | |

| JP2020174323A (ja) | 半導体装置 | |

| US8902554B1 (en) | Over-voltage tolerant circuit and method | |

| TWI555334B (zh) | 具調節功能之緩衝器電路及其調節電路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110324 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120928 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121002 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121128 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121231 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5181893 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160125 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |