JP2010004082A - 半導体素子の製造方法 - Google Patents

半導体素子の製造方法 Download PDFInfo

- Publication number

- JP2010004082A JP2010004082A JP2009231557A JP2009231557A JP2010004082A JP 2010004082 A JP2010004082 A JP 2010004082A JP 2009231557 A JP2009231557 A JP 2009231557A JP 2009231557 A JP2009231557 A JP 2009231557A JP 2010004082 A JP2010004082 A JP 2010004082A

- Authority

- JP

- Japan

- Prior art keywords

- film

- layer

- adhesive layer

- contact hole

- plug

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B53/00—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors

- H10B53/30—Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory capacitors characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

-

- H10W20/0698—

Landscapes

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

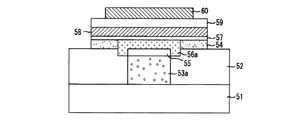

【解決手段】基礎導電膜51と、層間膜コンタクトホールを有し、基礎導電膜51上面に形成された、層間絶縁膜52と、層間膜コンタクトホールと連続した接着層コンタクトホールを有し、層間絶縁膜上面に形成された接着層54と、層間膜コンタクトホール及び接着層コンタクトホールからなる複合コンタクトホール内に、基礎導電膜51に接続され、接着層54の上面に合わせて平坦化されて形成された接続部200と、接続部200及び接着層54の上面に形成された第1電極57、58、誘電体膜59、及び第2電極60を備えたキャパシタとを装備する半導体素子を製造する。

【選択図】図5

Description

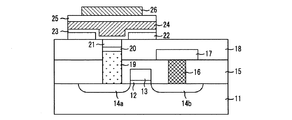

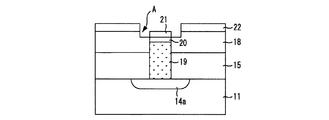

32、52 層間絶縁膜

33、53 プラグ埋込層

33a、53a ポリシリコンプラグ

34、54 接着層

35、55 チタニウムシリサイド

36a、56a チタニウムナイトライド

37、57 拡散バリヤ膜

38、58 下部電極

39、59 誘電体膜

40、60 上部電極

Claims (6)

- トランジスタが形成された半導体基板上面に層間絶縁膜を成長させる層間絶縁膜成長工程と、

前記層間絶縁膜をパターニングして、前記半導体基板の所定領域の表面を露出させる層間膜コンタクトホールを形成する層間膜コンタクトホール形成工程と、

前記層間膜コンタクトホール内、及び前記層間絶縁膜の上面に、シリコン含有物質からなるプラグ埋込層を成長させ、前記層間膜コンタクトホール内にプラグを形成するプラグ形成工程と、

前記プラグ及び前記層間絶縁膜の上面に形成された前記プラグ埋込層をエッチバック法で平坦化するプラグ埋込層平坦化工程と、

前記プラグ及び前記層間絶縁膜の上面に所定の厚さを有する反応予備膜を形成する反応予備膜形成工程と、

前記反応予備膜の上面にイリジウム含有物質を含むイリジウム反応層を成長させ、前記反応予備膜のシリコンと前記イリジウム反応層のイリジウムとを反応させて、前記プラグ及び前記層間絶縁膜の上面に、シリコン及びイリジウムを含有する接着層を成長させる接着層成長工程と、

前記接着層をパターニングして、前記プラグの上面を露出させる接着層コンタクトホールを形成する接着層コンタクトホール形成工程と、

前記接着層コンタクトホール内、及び前記接着層上面に導電性のバリヤ埋込層を成長させるバリヤ埋込層成長工程と、

前記接着層の表面が露出するまで、前記バリヤ埋込層を平坦化して、前記バリヤ層を形成するバリヤ埋込層平坦化工程と、

前記バリヤ層及び前記接着層の上面に第1電極と、誘電体膜と、第2電極とを含んで構成されるキャパシタを形成するキャパシタ形成工程とを含むことを特徴とする半導体素子の製造方法。 - 前記接着層形成工程を、約500℃〜約800℃の温度範囲で前記イリジウム反応層を成長させる条件で行うことを特徴とする請求項1記載の半導体素子の製造方法。

- 前記プラグ形成工程が、

前記プラグ埋込層としてポリシリコン層を成長させることを特徴とする請求項1記載の半導体素子の製造方法。 - 前記反応予備膜を、約10Å〜約1000Åの範囲内の厚さに形成することを特徴とする請求項1記載の半導体素子の製造方法。

- 前記バリヤ埋込層平坦化工程を、CMP法により、前記バリヤ層と前記接着層との研磨選択比が約50:1〜80:1の範囲内となる条件で行うことを特徴とする請求項1記載の半導体素子の製造方法。

- 前記キャパシタ形成工程が、前記第1電極を形成する第1電極形成工程と、前記第2電極を形成する第2電極形成工程とを含み、前記第1電極形成工程または前記第2電極形成工程が、TiN、RuTiN、IrTiN、Ir、IrOx、Ru、RuOx、Rh、RhOx、Pt及びこれらを組み合わせたもののうち、いずれかの物質を成長させる処理を含むことを特徴とする請求項1記載の半導体素子の製造方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR2001-056143 | 2001-09-12 | ||

| KR1020010056143A KR20030023142A (ko) | 2001-09-12 | 2001-09-12 | 반도체 소자 제조 방법 |

| KR2001-057368 | 2001-09-17 | ||

| KR10-2001-0057368A KR100415539B1 (ko) | 2001-09-17 | 2001-09-17 | 반도체 소자의 제조 방법 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002265456A Division JP4467229B2 (ja) | 2001-09-12 | 2002-09-11 | 半導体素子の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010004082A true JP2010004082A (ja) | 2010-01-07 |

| JP5047250B2 JP5047250B2 (ja) | 2012-10-10 |

Family

ID=26639338

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002265456A Expired - Fee Related JP4467229B2 (ja) | 2001-09-12 | 2002-09-11 | 半導体素子の製造方法 |

| JP2009231557A Expired - Fee Related JP5047250B2 (ja) | 2001-09-12 | 2009-10-05 | 半導体素子の製造方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002265456A Expired - Fee Related JP4467229B2 (ja) | 2001-09-12 | 2002-09-11 | 半導体素子の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6818935B2 (ja) |

| JP (2) | JP4467229B2 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7146007B1 (en) * | 2000-03-29 | 2006-12-05 | Sony Corporation | Secure conditional access port interface |

| AR028948A1 (es) * | 2000-06-20 | 2003-05-28 | Astrazeneca Ab | Compuestos novedosos |

| US6908639B2 (en) * | 2001-04-02 | 2005-06-21 | Micron Technology, Inc. | Mixed composition interface layer and method of forming |

| KR100561839B1 (ko) * | 2001-11-10 | 2006-03-16 | 삼성전자주식회사 | 강유전체 커패시터 및 그 제조방법 |

| KR100440072B1 (ko) * | 2001-12-10 | 2004-07-14 | 주식회사 하이닉스반도체 | 반도체소자의 캐패시터 형성방법 |

| KR100988082B1 (ko) * | 2003-05-21 | 2010-10-18 | 삼성전자주식회사 | 스택형 커패시터, 그를 구비한 반도체 메모리 소자 및 그제조방법 |

| US20050070097A1 (en) * | 2003-09-29 | 2005-03-31 | International Business Machines Corporation | Atomic laminates for diffusion barrier applications |

| CN100377357C (zh) * | 2003-10-22 | 2008-03-26 | 松下电器产业株式会社 | 半导体装置及其制造方法 |

| US20060046378A1 (en) * | 2004-08-26 | 2006-03-02 | Samsung Electronics Co., Ltd. | Methods of fabricating MIM capacitor employing metal nitride layer as lower electrode |

| US7151314B2 (en) * | 2004-11-17 | 2006-12-19 | Oki Electric Industry Co., Ltd. | Semiconductor device with superimposed poly-silicon plugs |

| JP4375561B2 (ja) * | 2004-12-28 | 2009-12-02 | セイコーエプソン株式会社 | 半導体記憶装置及びその製造方法 |

| JP2006324363A (ja) * | 2005-05-17 | 2006-11-30 | Elpida Memory Inc | キャパシタおよびその製造方法 |

| JP2006352082A (ja) * | 2005-05-19 | 2006-12-28 | Renesas Technology Corp | 半導体記憶装置及びその製造方法 |

| KR100705397B1 (ko) * | 2005-07-13 | 2007-04-10 | 삼성전자주식회사 | 저 저항의 텅스텐막 형성 방법 |

| JP5125510B2 (ja) * | 2005-08-31 | 2013-01-23 | 富士通セミコンダクター株式会社 | 半導体装置 |

| KR100647468B1 (ko) * | 2005-11-04 | 2006-11-23 | 삼성전자주식회사 | 반도체 장치의 배선 구조물 및 그 제조 방법. |

| JP4954614B2 (ja) * | 2006-05-30 | 2012-06-20 | セイコーエプソン株式会社 | 強誘電体メモリ装置の製造方法 |

| JP4884104B2 (ja) * | 2006-06-29 | 2012-02-29 | 富士通セミコンダクター株式会社 | キャパシタを含む半導体装置及びその製造方法 |

| US7582549B2 (en) | 2006-08-25 | 2009-09-01 | Micron Technology, Inc. | Atomic layer deposited barium strontium titanium oxide films |

| DE102007045074B4 (de) | 2006-12-27 | 2009-06-18 | Hynix Semiconductor Inc., Ichon | Halbleiterbauelement mit Gatestapelstruktur |

| KR100960934B1 (ko) * | 2008-05-16 | 2010-06-04 | 주식회사 하이닉스반도체 | 반도체 소자의 금속배선 및 그 형성방법 |

| JP2014053557A (ja) | 2012-09-10 | 2014-03-20 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2015046623A (ja) * | 2014-11-04 | 2015-03-12 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| KR102796863B1 (ko) | 2019-10-21 | 2025-04-17 | 삼성전자주식회사 | 금속 질화막 제조방법 및 금속 질화막을 포함하는 전자 소자 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0917972A (ja) * | 1995-06-30 | 1997-01-17 | Mitsubishi Electric Corp | 半導体記憶装置及びその製造方法 |

| JP2000040800A (ja) * | 1998-07-24 | 2000-02-08 | Sharp Corp | 強誘電体記憶素子及びその製造方法 |

| WO2000038247A1 (en) * | 1998-12-18 | 2000-06-29 | Infineon Technologies Ag | Reduced diffusion of a mobile specie from a metal oxide ceramic |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5382817A (en) * | 1992-02-20 | 1995-01-17 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device having a ferroelectric capacitor with a planarized lower electrode |

| ATE193335T1 (de) | 1994-11-30 | 2000-06-15 | Micron Technology Inc | Verfahren zum auftragen von wolframnitrid unter verwendung eines silicium enthaltenden gases |

| KR100273689B1 (ko) | 1997-06-30 | 2000-12-15 | 김영환 | 반도체메모리장치및그제조방법 |

| TW333684B (en) | 1997-09-24 | 1998-06-11 | Nanya Technology Co Ltd | The producing method for semiconductor capacitor electrode plate |

| JPH11195768A (ja) | 1997-10-22 | 1999-07-21 | Fujitsu Ltd | ペロブスカイト型酸化物膜を含む電子装置とその製造方法及び強誘電体キャパシタ |

| CN1181512C (zh) | 1998-05-01 | 2004-12-22 | 东洋锡钣株式会社 | 电解电容器壳体及其制造方法 |

| CN1155092C (zh) * | 1998-07-03 | 2004-06-23 | 松下电器产业株式会社 | 半导体装置及其制造方法 |

| JP2000091539A (ja) | 1998-07-16 | 2000-03-31 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| KR100324601B1 (ko) | 1998-12-30 | 2002-04-17 | 박종섭 | 계면의 특성 향상을 위한 강유전체 캐패시터 제조 방법 |

| JP3177973B2 (ja) | 1999-01-28 | 2001-06-18 | 日本電気株式会社 | 半導体装置の製造方法 |

| US6171899B1 (en) | 1999-03-12 | 2001-01-09 | United Microelectronics Corp. | Method for fabricating a capacitor |

| US6190963B1 (en) | 1999-05-21 | 2001-02-20 | Sharp Laboratories Of America, Inc. | Composite iridium-metal-oxygen barrier structure with refractory metal companion barrier and method for same |

| JP2001044073A (ja) | 1999-07-30 | 2001-02-16 | Sony Corp | 薄膜コンデンサとその製造方法 |

| JP2001053249A (ja) | 1999-08-05 | 2001-02-23 | Tokyo Electron Ltd | 半導体装置およびその製造方法 |

| KR100612561B1 (ko) * | 2000-06-19 | 2006-08-11 | 주식회사 하이닉스반도체 | 반도체 소자의 캐패시터 제조 방법 |

| KR100338780B1 (ko) * | 2000-09-15 | 2002-06-01 | 윤종용 | 층간절연막의 손상을 방지할 수 있는 반도체 메모리 소자및 그 제조방법 |

-

2002

- 2002-09-11 US US10/238,710 patent/US6818935B2/en not_active Expired - Lifetime

- 2002-09-11 JP JP2002265456A patent/JP4467229B2/ja not_active Expired - Fee Related

-

2009

- 2009-10-05 JP JP2009231557A patent/JP5047250B2/ja not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0917972A (ja) * | 1995-06-30 | 1997-01-17 | Mitsubishi Electric Corp | 半導体記憶装置及びその製造方法 |

| JP2000040800A (ja) * | 1998-07-24 | 2000-02-08 | Sharp Corp | 強誘電体記憶素子及びその製造方法 |

| WO2000038247A1 (en) * | 1998-12-18 | 2000-06-29 | Infineon Technologies Ag | Reduced diffusion of a mobile specie from a metal oxide ceramic |

Also Published As

| Publication number | Publication date |

|---|---|

| US6818935B2 (en) | 2004-11-16 |

| JP2003179164A (ja) | 2003-06-27 |

| JP5047250B2 (ja) | 2012-10-10 |

| US20030057445A1 (en) | 2003-03-27 |

| JP4467229B2 (ja) | 2010-05-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5047250B2 (ja) | 半導体素子の製造方法 | |

| US6825082B2 (en) | Ferroelectric memory device and method of forming the same | |

| US6599806B2 (en) | Method for manufacturing a capacitor of a semiconductor device | |

| US6380579B1 (en) | Capacitor of semiconductor device | |

| KR100449949B1 (ko) | 강유전체 메모리 소자의 캐패시터 제조방법 | |

| US6798010B2 (en) | Ferroelectric memory devices | |

| US20030075753A1 (en) | Stacked capacitor and method for fabricating the same | |

| KR100718267B1 (ko) | 강유전체 구조물, 이의 제조 방법, 이를 포함하는 반도체장치 및 그 제조 방법 | |

| KR20000048374A (ko) | 반도체기억장치의 제조방법 | |

| JP2003133534A (ja) | 半導体素子及びその製造方法 | |

| KR100725451B1 (ko) | 강유전체 캐패시터의 제조 방법 및 이를 이용한 반도체장치의 제조 방법 | |

| US6180970B1 (en) | Microelectronic devices including ferroelectric capacitors with lower electrodes extending into contact holes | |

| US6917114B2 (en) | Semiconductor device and method of fabricating the same | |

| US7042034B2 (en) | Capacitor | |

| US7573120B2 (en) | Semiconductor device and method of manufacturing the same | |

| KR100633330B1 (ko) | 반도체 장치의 캐패시터 제조방법 | |

| KR100415539B1 (ko) | 반도체 소자의 제조 방법 | |

| JP2002373975A (ja) | 強誘電体メモリ素子の製造方法および強誘電体メモリ素子 | |

| JP2008135543A (ja) | 不揮発性記憶装置およびその製造方法 | |

| KR100652354B1 (ko) | 하부전극과 콘택 플러그 사이에 낮은 접촉 저항을 갖는 반도체장치의 커패시터 및 그 제조방법 | |

| KR100418587B1 (ko) | 전기도금법을 이용한 반도체 메모리 소자의 형성방법 | |

| KR19990080412A (ko) | 이중 유전막을 가지는 고유전율 커패시터 및 그제조방법 | |

| KR20030023142A (ko) | 반도체 소자 제조 방법 | |

| KR20020002613A (ko) | 접촉 저항 증가 및 막의 들림을 효과적으로 방지할 수있는 반도체 메모리 소자 및 그 제조 방법 | |

| KR20030039236A (ko) | 강유전체 메모리 소자의 콘캐이브형 캐패시터 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091016 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120313 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120315 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120611 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120626 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120717 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150727 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |