JP2009529784A - 集積回路の限界寸法を制御するトリム工程 - Google Patents

集積回路の限界寸法を制御するトリム工程 Download PDFInfo

- Publication number

- JP2009529784A JP2009529784A JP2008558345A JP2008558345A JP2009529784A JP 2009529784 A JP2009529784 A JP 2009529784A JP 2008558345 A JP2008558345 A JP 2008558345A JP 2008558345 A JP2008558345 A JP 2008558345A JP 2009529784 A JP2009529784 A JP 2009529784A

- Authority

- JP

- Japan

- Prior art keywords

- hard mask

- mask layer

- layer

- trimming

- etching

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0337—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/033—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers

- H01L21/0334—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising inorganic layers characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/0338—Process specially adapted to improve the resolution of the mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3086—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

- H01L21/3088—Process specially adapted to improve the resolution of the mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31144—Etching the insulating layers by chemical or physical means using masks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32139—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer using masks

Abstract

(150) を設けるステップと、フォトレジスト層 (150) にパターンを形成するステップと、このパターンを第二のハードマスク層 (140) へと転写するステップと、第二のハードマスク層 (140) をその上面にフォトレジスト層 (150) を載せたままトリムするステップと、が含まれる。トリム蝕刻の間は、第二のハードマスク層(140) の上面はフォトレジスト (150) で保護され、対象層 (120) はその上に在るハードマスク層 (130) で保護されるので、強作用なトリム蝕刻が可能である。

【選択図】図1D

Description

けるステップと、フォトレジスト層にパターンを形成するステップと、パターンを第二のハードマスク層へと転写するステップと、フォトレジスト層を上面に載せたまま第二のハードマスク層をトリムするステップと、が含まれる。

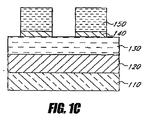

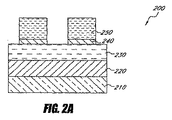

図1Aから図1Fには、本発明の或る実施形態にかかる、集積回路のための蝕刻方法を図解してある。図1Aでは、対象層 120 を基板 110 の上に設けている。その後、第一のハードマスク層 130 を対象層 120 の上に設ける。第二のハードマスク層 140 を、第一のハードマスク層 130 の上に設ける。第二のハードマスク層 140 は、第一のハードマスク層 130 よりも薄いのが好ましい。加えて、第二のハードマスク層 140 をつくる材料は、第一のハードマスク層 130 の材料とは異なる。最後にフォトレジスト層 150 を第二のハードマスク層 140 の上に設ける。

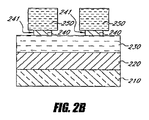

ト層 150 に形成している。その後にこのパターンを、蝕刻工程を用いて第二のハードマスク層 140 へと転写する(図1C参照)。そうしてから等方性蝕刻工程を施して、第二のハードマスク層 140 の上面にフォトレジスト層 150 を載せたまま、第二のハードマスク層 140 をトリムする言い換えれば縮める(図1D参照)。

図1Aには、或る実施形態に応じて、これから作成する集積回路(IC)の部分 100 を示してある。基板 110 は部分 100 の底に置かれる。示した実施形態では、基板 110 は珪素(シリコン)基板である。他の実施形態群では、基板 110 を別の種類の半導体材料からつくってもよい。

は、処理(蝕刻など)にかけようとする構造体の上に在る。第一のハードマスク層 130 によりパターンがつくられ、このパターンを対象層 120 へと転写することになる。第一のハードマスク層 130 は、有機材料からつくることができる。示した実施形態では、第一のハードマスク層 130 を非晶質炭素からつくる。好ましい非晶質炭素の種類は、下地層への光配向が容易な無色透明な炭素である。第一のハードマスク層 130 は厚いほうが好ましいので、不透明な膜では光配向を妨げてしまうと考えられる。

図1Aに話を戻して、フォトレジスト層 150 を第二のハードマスク層 140 の上につくる。示した実施形態においては、光刻法に通常使われる光の波長(248nm、193nm、157nm、および13.5nmなど)に対して感受性を持つようなフォトレジストから、フォトレジスト層 150 をつくることができる。フォトレジスト層 150 の厚さは、約500Åから約3,000Åの範囲であるのが好ましく、約1,000Åから約2,000Åの範囲であるのがより好ましい。図1Bでは、任意の適切なフォトレジスト処理法を使って、フォトレジスト層 150 をパターン化してある。

フォトレジスト 150 につくったパターンを第二のハードマスク 140 へと転写するに際しては、プラズマ蝕刻工程を使うのが好ましく、高密度プラズマ蝕刻工程を使うのがもっとも好ましい。プラズマ蝕刻工程は、異方性蝕刻工程であるのが好ましい。

写してある。この転写を行うにあたっては、処理室内で弗化炭素プラズマ乾式蝕刻法を施すのが好ましい。乾式蝕刻法(好ましくは高密度プラズマを用いる)を使うと、レジスト要素の寸法に忠実に、第二のハードマスク層 140 のパターン化が可能である。電力レベルと流量は、択んだ処理室に応じて変更できる。好ましい処理室としては、Lam Research Corp. (Fremont, CA) のTCP9400 poly etch chamberおよびTCP2300 poly etch chamber や、Applied Materials Corp. (Santa Clara, CA) のDPS2 poly etch chamberなどがある。パターンをフォトレジスト層 150 から第二のハードマスク層 140 へと転写するために使える蝕刻法が何種類もあるということを、当業者は正しく理解できる。

図1Dと図4では、フォトレジスト層 150 を上面に載せたまま、第二のハードマスク層 140 を縮めて(トリムして)いる。トリム工程では、横方向に蝕刻を起こして、限界寸法を縮める。このトリム工程ではまた、特徴的構造の縁部の粗を均している。第二のハードマスク層の縁部の平均粗さ(Ra)は、約10Årmsから約100Årmsの範囲であるのが好ましい。こうしたトリム工程を行うにあたっては、等方性蝕刻法を使うのが好ましい。

SiOxNyもしくは SiN を含んだ第二のハードマスク層 140 を縮めるには、等方性プラズマ乾式蝕刻法が使える。トリム工程で使われる蝕刻剤には、第二のハードマスク層 140 を選択的に蝕刻できて、しかも第一のハードマスク層 130 は最小限しか蝕刻しないようなものを選択することで、基板を保護する。或る実施形態群では、第二のハードマスク層

140 の蝕刻速度を、第一のハードマスク層 130 のそれと同程度だが低速にはならないようにできる。第二のハードマスク層 140 の蝕刻速度を、第一のハードマスク層 130 の蝕刻速度の約一倍から千倍までの範囲とするのが好ましく、約二倍から百倍までの範囲とするのがより好ましく、約十倍から百倍までの範囲とするのがもっとも好ましい。

第二のハードマスク層を縮めるにあたっては、等方性湿式蝕刻法を用いることができる。第二のハードマスク層 140 が SiO2からできているような実施形態においては、緩衝酸化物蝕刻法をこうした湿式蝕刻法に使ってもよい。こうした緩衝酸化物蝕刻溶液には、 HF 、 NH4F 、および H2O が含有されている。或る実施形態では、使う溶液の HF 濃度を約0.5 wt.%から20 wt.%の範囲とし、約2 wt.%から10 wt.%の範囲とするのがより好ましい。基板温度は、約15℃から80℃の範囲にするのが好ましく、約20℃から25℃の範囲にするのがより好ましい。

図1Eでは、縮めた(トリムした)パターンを、第二のハードマスク層 140 から第一のハードマスク層 130 へと転写している。図1Eでは、第二のハードマスク層 140 に在るパターンを、第一のハードマスク層 130 へと転写している。第一のハードマスク層 130 を、有機材料からつくるのが好ましく、非晶質炭素からつくるのがより好ましい。蝕刻工程は、乾式現像蝕刻(DDE)工程であるのが好ましい。蝕刻剤には硫黄と酸素を含めるのが好ましく、また蝕刻剤はプラズマであるのが好ましい。示した実施形態では、二酸化硫黄(SO2)を用いたプラズマを蝕刻剤として工程に使う。この工程のことを、DDE炭素蝕刻工程と呼ぶ。プラズマ工程では、不活性ガスをプラズマの補助として使うのが好ましい。

など)に較べて高くなるようにする。第一のハードマスク層 130 の蝕刻速度を、第二のハードマスク層 140 の蝕刻速度の約五倍以上とするのが好ましく、約十倍から五十倍までとするのがより好ましい。

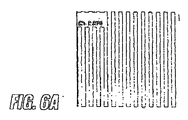

図1Fでは、第一のハードマスク層 130 をパターン化すれば、対象層120 の処理(蝕刻など)に使える、ということを示してある。集積回路製造過程でマスクを介して選択的に処理(蝕刻など)をする必要があるような、珪素、酸化珪素、窒化珪素、金属、もしくは他の任意の材料などから、対象層 120 を作成できる。好ましい実施形態では、対象層 120 を同一処理室内で処理する。しかし、ウェハを後続の工程にかけるために別の処理室へ移送してもかまわない。対象層 120 の蝕刻にあたっては、択んだ対象層に対して適切な蝕刻剤を使うのが好ましい。

い。対象層 120 の組成によっては、蝕刻停止層を、第二のハードマスク層 130 に使う材料と類似の材料からつくってもよい。そうした材料としては、DARCおよび窒化珪素がある。この蝕刻停止層により、第一のハードマスク層 130 の蝕刻中(すなわち、第一のハードマスク層 130 へのパターン転写中や、第一のハードマスク層 130 の除去中)に、対象層 120 が損傷しないようにできる。対象層 120 が金属である場合(金属配線層であるような場合など)には、このことは特に重要となる。金属をDDE処理室内で蝕刻すると、処理室が汚染されて処理が遅緩してしまう可能性がある。なので、対象層 120 に露出した金属層が有る場合には、ウェハを金属蝕刻室へと移送してから、さらなる処理にかけるのが好ましい。対象層の処理(蝕刻など)が完了したら、既知の蝕刻法(湿式蝕刻工程など)を使って、残っているハードマスク材料をすべて除去してよい。示した実施形態では、対象層の蝕刻中に、第二のハードマスク層 140 が第一のハードマスク層 130 の上面に残っている。他の実施形態群では、対象層 120 をパターン化された第一のハードマスク層 130 を介して処理する前に、第二のハードマスク層 140 を除去してもかまわない。上述した対象層の蝕刻工程の後に、付加的な工程(金属配線化など)を施して、集積回路を仕上げる。

示した実施形態では、トリム工程を光刻法と組み合わせて使っていた。他の実施形態群では、トリム工程を、他の種類のリソグラフィ法(インプリントリソグラフィなど)と組み合わせることができる。インプリントリソグラフィとは、剛体の機械的な鋳型を使って、パターンを基板へと転写する手法のことである。インプリントリソグラフィ工程では、光硬化性材料を第二のハードマスク層の上に配置する。そうしてから、剛体の透明な(水晶などでできた)鋳型を上から光硬化性材料に押しつけて、軟らかいレジストを圧印(成形)する。そしてパターンを使って光硬化性材料に光をあてて固めると、鋳型によって硬化した材料が成形される。こうして、パターンが第二のハードマスク層に転写されるわけである。続いて、硬化した材料を第二のハードマスク層の上面に載せたまま、第二のハードマスク層を縮める。このとき、下地である第一のハードマスク層が、下地である半導体基板を保護している。

本発明の別の特徴として、集積回路を処理するための保護構造体(マスキング構造体)が提供される。こうしたマスキング構造体は、添加法、酸化法、窒化法、および選択的堆積法などの種々の工程に使用可能である。図1Dでは、マスキング構造体が、対象層 120

の上につくった第一のハードマスク層 130 と、第一のハードマスク層 130 の上につくった第二のハードマスク層 140 と、第二のハードマスク層 140 の上につくったレジスト層 150 と、を含んでいてもよい。いくつかの実施形態群では、対象層 120 というものが、そこに溝を形成できる珪素ウェハ自体のことを表す、という旨を理解されたい。第二のハードマスク層 140 には、第一のハードマスク層130 を蔽うよう構築したマスキング部位を具えたパターンが含まれる。第二のハードマスク層 140 のマスキング部位に対応したマスキング部位を具えたパターンを有するように、レジスト層 150 を構築する。第二のハードマスク層140 のマスキング部位の露出した側面 141 の各々は、等方性蝕刻されている。

Claims (43)

- 集積回路のための蝕刻方法であって、

対象層の上に、第一のハードマスク層を設けるステップと、

前記第一のハードマスク層の上に、第二のハードマスク層を設けるステップと、

前記第二のハードマスク層の上に、レジスト層を設けるステップと、

前記レジスト層にパターンを形成するステップと、

前記パターンを、前記第二のハードマスク層へと転写するステップと、

前記第二のハードマスク層を、前記第二のハードマスク層の上面に前記レジスト層を載せたままトリムするステップと

を含む、方法。 - 前記対象層が、

絶縁体、半導体、および金属からなる群から選択される材料

を含む、請求項1記載の方法。 - 前記第一のハードマスク層が、非晶質炭素層を含む、請求項1記載の方法。

- 前記第一のハードマスク層が、有機下地層を含む、請求項1記載の方法。

- 前記第一のハードマスク層の厚さが、約200Åから約20,000Åの範囲である、請求項1記載の方法。

- 前記第一のハードマスク層のアスペクト比が、約20:1未満である、請求項1記載の方法。

- 前記第二のハードマスク層が、無機層を含む、請求項1記載の方法。

- 前記無機層が、反射防止絶縁膜(DARC)を含む、請求項7記載の方法。

- 前記無機層が、

酸窒化珪素、酸化珪素、もしくは窒化珪素からなる群から選択される材料

を含む、請求項7記載の方法。 - 前記第二のハードマスク層が、珪素含有有機層を含む、請求項1記載の方法。

- 前記第二のハードマスク層の厚さが、約50Åから約1,000Åの範囲である、請求項1記載の方法。

- 前記レジストが、

157nmフォトレジスト、193nmフォトレジスト、および248nmフォトレジストからなる群から選択されるフォトレジスト

を含む、請求項1記載の方法。 - 前記パターンを前記第二のハードマスク層へと転写するステップが、

異方性蝕刻工程を用いるステップ

を含む、請求項1記載の方法。 - 前記異方性蝕刻工程を用いるステップが、

弗化炭素を用いたプラズマを使うステップ

を含む、請求項13記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層の特徴的構造の巾を、約10Å以上縮めるステップ

を含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層を、前記レジスト層および前記第一のハードマスク層に対して選択的に蝕刻するステップ

を含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層を、前記第一のハードマスク層の蝕刻速度の約一倍から千倍までの速度で蝕刻するステップ

を含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層を、秒あたり約1Åから10Åまでの速度で蝕刻するステップ

を含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層を等方性蝕刻するステップ

を含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

前記第二のハードマスク層をプラズマで蝕刻するステップ

を含む、請求項1記載の方法。 - 前記プラズマが、弗素含有プラズマを含む、請求項20記載の方法。

- 前記プラズマが、

NF3 を用いたプラズマ、および SF6 を用いたプラズマからなる群から選択されるプラズマ

を含む、請求項21記載の方法。 - 前記第二のハードマスク層をトリムするステップが、

湿式蝕刻工程を使うステップ

を含む、請求項1記載の方法。 - 前記湿式蝕刻工程を使うステップが、

緩衝酸化物蝕刻工程を使うステップ

を含む、請求項23記載の方法。 - 前記緩衝酸化物蝕刻工程が、

HF 、 NH4F 、および H2O を含む蝕刻剤を使うステップ

を含む、請求項24記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを、前記第一のハードマスク層へと転写するステップ

をさらに含む、請求項1記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

高密度プラズマ蝕刻工程を用いるステップ

を含む、請求項26記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

前記第一のハードマスク層を、前記第二のハードマスク層の蝕刻速度の約五倍以上の速度で蝕刻するステップ

を含む、請求項27記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

前記第一のハードマスク層を、硫黄および酸素を用いたプラズマを使って蝕刻するステップ

を含む、請求項26記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

流量10sccmから75sccmの範囲で二酸化硫黄を処理室に流し入れるステップ

を含む、請求項29記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

流量20sccmから60sccmの範囲で二酸化硫黄を処理室に流し入れるステップ

を含む、請求項30記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

流量10sccmから100sccmの範囲で酸素を前記処理室に流し入れるステップ

をさらに含む、請求項30記載の方法。 - 前記第二のハードマスク層をトリムすることで得られるパターンを前記第一のハードマスク層へと転写するステップが、

アルゴンを前記処理室に流し入れるステップ

をさらに含む、請求項30記載の方法。 - 底部反射防止膜(BARC)層を、前記第二のハードマスク層の上に設けるステップ

をさらに含む、請求項1記載の方法。 - 前記底部反射防止膜層の厚さが、約200Åから約500Åの範囲である、請求項34記載の方法。

- 前記集積回路の装置が、メモリを含む、請求項1記載の方法。

- 前記集積回路の装置が、マイクロプロセッサを含む、請求項1記載の方法。

- 前記レジスト層が、インプリントリソグラフィレジストを含む、請求項1記載の方法。

- 集積回路用のマスキング構造体であって、

対象層の上につくられた、第一のハードマスク層と、

前記第一のハードマスク層の上につくられ、且つ前記第一のハードマスク層を蔽うように構築されたマスキング部位を具えたパターンを有する、第二のハードマスク層と、

前記第二のハードマスク層の上につくられ、且つ前記第二のハードマスク層の前記マスキング部位に対応したマスキング部位を具えたパターンを有する、レジスト層と

を含み、ここで、

前記第二のハードマスク層の前記マスキング部位の露出した側面の各々の平均粗さが、50Årms未満である

ことを特徴とする、マスキング構造体。 - 前記第二のハードマスク層の前記マスキング部位の露出した側面の各々の平均粗さが、約10Årmsから約50Årmsの範囲である、請求項39記載のマスキング構造体。

- 前記第二のハードマスク層の前記マスキング部位の巾が、前記レジスト層の前記対応するマスキング部位の巾とほぼ等しい、請求項39記載のマスキング構造体。

- 前記第二のハードマスク層の前記マスキング部位の巾が、前記レジスト層の前記対応するマスキング部位の巾よりも狭い、請求項39記載のマスキング構造体。

- 前記第二のハードマスク層の前記マスキング部位の前記露出した側面の各々が、前記レジスト層の下に5Å以上奥まっている、請求項42記載のマスキング構造体。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/372,825 US7662718B2 (en) | 2006-03-09 | 2006-03-09 | Trim process for critical dimension control for integrated circuits |

| PCT/US2007/005639 WO2007103343A1 (en) | 2006-03-09 | 2007-03-05 | Trim process for critical dimension control for integrated circuits |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009529784A true JP2009529784A (ja) | 2009-08-20 |

| JP2009529784A5 JP2009529784A5 (ja) | 2010-04-15 |

Family

ID=38219014

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008558345A Pending JP2009529784A (ja) | 2006-03-09 | 2007-03-05 | 集積回路の限界寸法を制御するトリム工程 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US7662718B2 (ja) |

| EP (1) | EP2002465A1 (ja) |

| JP (1) | JP2009529784A (ja) |

| KR (1) | KR20080112281A (ja) |

| CN (1) | CN101421824B (ja) |

| WO (1) | WO2007103343A1 (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010003757A (ja) * | 2008-06-18 | 2010-01-07 | Fujitsu Microelectronics Ltd | 半導体装置の製造方法 |

| CN102478764A (zh) * | 2010-11-30 | 2012-05-30 | 中芯国际集成电路制造(北京)有限公司 | 双重图形化方法 |

| JP2013089827A (ja) * | 2011-10-20 | 2013-05-13 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| JP2014507795A (ja) * | 2010-12-27 | 2014-03-27 | ブルーワー サイエンス アイ エヌ シー. | 高度なパターン形成に必要な小型フィーチャのパターン形成プロセス |

| JP2014157956A (ja) * | 2013-02-18 | 2014-08-28 | Mitsubishi Electric Corp | 炭化珪素半導体装置の製造方法 |

| US9177809B2 (en) | 2013-07-03 | 2015-11-03 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| KR20160030378A (ko) * | 2014-09-09 | 2016-03-17 | 도쿄엘렉트론가부시키가이샤 | 서브-해상도 스케일들로 상이한 임계 치수들을 패터닝하기 위한 방법 |

| US9779952B2 (en) | 2013-08-27 | 2017-10-03 | Tokyo Electron Limited | Method for laterally trimming a hardmask |

Families Citing this family (66)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7533068B2 (en) | 2004-12-23 | 2009-05-12 | D-Wave Systems, Inc. | Analog processor comprising quantum devices |

| JP2007081383A (ja) * | 2005-08-15 | 2007-03-29 | Fujitsu Ltd | 微細構造の製造方法 |

| US7662718B2 (en) * | 2006-03-09 | 2010-02-16 | Micron Technology, Inc. | Trim process for critical dimension control for integrated circuits |

| US20080102643A1 (en) * | 2006-10-31 | 2008-05-01 | United Microelectronics Corp. | Patterning method |

| KR100777927B1 (ko) * | 2006-12-05 | 2007-11-21 | 동부일렉트로닉스 주식회사 | 반도체 소자의 미세패턴 형성방법 |

| KR100838394B1 (ko) * | 2007-01-03 | 2008-06-13 | 주식회사 하이닉스반도체 | 하드마스크층을 이용한 반도체소자의 식각 방법 |

| JP5108489B2 (ja) * | 2007-01-16 | 2012-12-26 | 株式会社日立ハイテクノロジーズ | プラズマ処理方法 |

| KR20080086686A (ko) * | 2007-03-23 | 2008-09-26 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| WO2008122127A1 (en) | 2007-04-05 | 2008-10-16 | D-Wave Systems Inc. | Systems, methods and apparatus for anti-symmetric qubit-coupling |

| JP5236983B2 (ja) * | 2007-09-28 | 2013-07-17 | 東京エレクトロン株式会社 | 半導体装置の製造方法、半導体装置の製造装置、制御プログラム及びプログラム記憶媒体 |

| US7759201B2 (en) * | 2007-12-17 | 2010-07-20 | Sandisk 3D Llc | Method for fabricating pitch-doubling pillar structures |

| US7927782B2 (en) * | 2007-12-28 | 2011-04-19 | Texas Instruments Incorporated | Simplified double mask patterning system |

| US7981592B2 (en) * | 2008-04-11 | 2011-07-19 | Sandisk 3D Llc | Double patterning method |

| US7713818B2 (en) * | 2008-04-11 | 2010-05-11 | Sandisk 3D, Llc | Double patterning method |

| US8084366B2 (en) | 2008-04-11 | 2011-12-27 | Sandisk 3D Llc | Modified DARC stack for resist patterning |

| US7786015B2 (en) * | 2008-04-28 | 2010-08-31 | Sandisk 3D Llc | Method for fabricating self-aligned complementary pillar structures and wiring |

| US8293460B2 (en) * | 2008-06-16 | 2012-10-23 | Applied Materials, Inc. | Double exposure patterning with carbonaceous hardmask |

| US7781269B2 (en) | 2008-06-30 | 2010-08-24 | Sandisk 3D Llc | Triangle two dimensional complementary patterning of pillars |

| US8076056B2 (en) * | 2008-10-06 | 2011-12-13 | Sandisk 3D Llc | Method of making sub-resolution pillar structures using undercutting technique |

| JP2010226022A (ja) * | 2009-03-25 | 2010-10-07 | Elpida Memory Inc | 半導体装置の製造方法 |

| US7923305B1 (en) | 2010-01-12 | 2011-04-12 | Sandisk 3D Llc | Patterning method for high density pillar structures |

| US8026178B2 (en) * | 2010-01-12 | 2011-09-27 | Sandisk 3D Llc | Patterning method for high density pillar structures |

| WO2011105282A1 (ja) * | 2010-02-25 | 2011-09-01 | シャープ株式会社 | 配線形成方法、および、半導体基板の製造方法 |

| US20110244398A1 (en) * | 2010-03-30 | 2011-10-06 | United Microelectronics Corp | Patterning method |

| WO2012057967A2 (en) * | 2010-10-27 | 2012-05-03 | Applied Materials, Inc. | Methods and apparatus for controlling photoresist line width roughness |

| US8691697B2 (en) | 2010-11-11 | 2014-04-08 | International Business Machines Corporation | Self-aligned devices and methods of manufacture |

| CN102064096B (zh) * | 2010-12-03 | 2012-07-25 | 北京大学 | 一种细线条的制备方法 |

| USRE46464E1 (en) | 2010-12-14 | 2017-07-04 | Lam Research Corporation | Method for forming stair-step structures |

| US8329051B2 (en) | 2010-12-14 | 2012-12-11 | Lam Research Corporation | Method for forming stair-step structures |

| US8535549B2 (en) * | 2010-12-14 | 2013-09-17 | Lam Research Corporation | Method for forming stair-step structures |

| CN102129982A (zh) * | 2010-12-29 | 2011-07-20 | 北京大学深圳研究生院 | 半导体精细图形及鳍形场效应管的fin体的制作方法 |

| JP5485185B2 (ja) * | 2011-01-05 | 2014-05-07 | 信越化学工業株式会社 | レジスト下層膜材料及びこれを用いたパターン形成方法 |

| US8871102B2 (en) * | 2011-05-25 | 2014-10-28 | Western Digital (Fremont), Llc | Method and system for fabricating a narrow line structure in a magnetic recording head |

| US8541296B2 (en) * | 2011-09-01 | 2013-09-24 | The Institute of Microelectronics Chinese Academy of Science | Method of manufacturing dummy gates in gate last process |

| CN102983073B (zh) * | 2011-09-05 | 2015-12-09 | 中国科学院微电子研究所 | 小尺寸鳍形结构的制造方法 |

| JP2013075984A (ja) * | 2011-09-30 | 2013-04-25 | Toshiba Corp | 微細構造体の製造方法 |

| US20130130503A1 (en) * | 2011-11-23 | 2013-05-23 | Peking University | Method for fabricating ultra-fine nanowire |

| US8722541B2 (en) * | 2012-03-15 | 2014-05-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Double patterning method for semiconductor devices |

| CN104508558B (zh) * | 2012-08-10 | 2016-07-06 | 日产化学工业株式会社 | 抗蚀剂下层膜形成用组合物 |

| US8802565B2 (en) | 2012-09-10 | 2014-08-12 | International Business Machines Corporation | Semiconductor plural gate lengths |

| US9105587B2 (en) | 2012-11-08 | 2015-08-11 | Micron Technology, Inc. | Methods of forming semiconductor structures with sulfur dioxide etch chemistries |

| CN103928388A (zh) * | 2013-01-10 | 2014-07-16 | 中芯国际集成电路制造(上海)有限公司 | 互连结构及其制造方法 |

| US8999777B2 (en) * | 2013-03-14 | 2015-04-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method of conducting a direction-specific trimming process for contact patterning |

| TWI639179B (zh) | 2014-01-31 | 2018-10-21 | 美商蘭姆研究公司 | 真空整合硬遮罩製程及設備 |

| US10002107B2 (en) | 2014-03-12 | 2018-06-19 | D-Wave Systems Inc. | Systems and methods for removing unwanted interactions in quantum devices |

| KR102265271B1 (ko) | 2015-01-14 | 2021-06-17 | 삼성전자주식회사 | 반도체 소자 및 그 제조방법 |

| CN104716033A (zh) * | 2015-03-20 | 2015-06-17 | 上海华力微电子有限公司 | 改善刻蚀腔体养护后多晶硅栅极关键尺寸稳定性的方法 |

| US9673057B2 (en) | 2015-03-23 | 2017-06-06 | Lam Research Corporation | Method for forming stair-step structures |

| US10008384B2 (en) * | 2015-06-25 | 2018-06-26 | Varian Semiconductor Equipment Associates, Inc. | Techniques to engineer nanoscale patterned features using ions |

| US9711359B2 (en) * | 2015-08-13 | 2017-07-18 | Lam Research Corporation | Shadow trim line edge roughness reduction |

| US9741563B2 (en) | 2016-01-27 | 2017-08-22 | Lam Research Corporation | Hybrid stair-step etch |

| US9899219B2 (en) * | 2016-02-19 | 2018-02-20 | Tokyo Electron Limited | Trimming inorganic resists with selected etchant gas mixture and modulation of operating variables |

| KR20180113585A (ko) * | 2016-03-04 | 2018-10-16 | 도쿄엘렉트론가부시키가이샤 | 통합 계획의 다양한 스테이지 동안의 패터닝을 위한 트림 방법 |

| US10566212B2 (en) | 2016-12-19 | 2020-02-18 | Lam Research Corporation | Designer atomic layer etching |

| WO2018156794A1 (en) * | 2017-02-22 | 2018-08-30 | Tokyo Electron Limited | Method for reducing lithography defects and pattern transfer |

| US10276379B2 (en) | 2017-04-07 | 2019-04-30 | Applied Materials, Inc. | Treatment approach to improve film roughness by improving nucleation/adhesion of silicon oxide |

| US10832909B2 (en) | 2017-04-24 | 2020-11-10 | Lam Research Corporation | Atomic layer etch, reactive precursors and energetic sources for patterning applications |

| US10796912B2 (en) * | 2017-05-16 | 2020-10-06 | Lam Research Corporation | Eliminating yield impact of stochastics in lithography |

| US10312089B1 (en) * | 2017-11-29 | 2019-06-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Methods for controlling an end-to-end distance in semiconductor device |

| CN111788588A (zh) | 2017-12-20 | 2020-10-16 | D-波系统公司 | 量子处理器中耦合量子位的系统和方法 |

| US10522751B2 (en) | 2018-05-22 | 2019-12-31 | Taiwan Semiconductor Manufacturing Company, Ltd. | MTJ CD variation by HM trimming |

| WO2020102085A1 (en) | 2018-11-14 | 2020-05-22 | Lam Research Corporation | Methods for making hard masks useful in next-generation lithography |

| CN109950140B (zh) * | 2019-04-18 | 2021-11-05 | 上海华力微电子有限公司 | 一种自对准双层图形的形成方法 |

| CN109950141A (zh) * | 2019-04-18 | 2019-06-28 | 上海华力微电子有限公司 | 一种半导体结构的形成方法 |

| US11521846B2 (en) * | 2019-12-16 | 2022-12-06 | Taiwan Semiconductor Manufacturing Company Limited | Methods for patterning a silicon oxide-silicon nitride-silicon oxide stack and structures formed by the same |

| WO2023173217A1 (en) * | 2022-03-17 | 2023-09-21 | Photonic Inc. | Systems and methods for trimming photonic integrated circuits |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003031557A (ja) * | 2001-07-16 | 2003-01-31 | Toshiba Corp | 半導体装置の製造方法 |

| JP2003249485A (ja) * | 2001-11-12 | 2003-09-05 | Chartered Semiconductor Mfg Ltd | 有機底部反射防止コーティング及びフォトレジストのトリミングプロセスのための方法 |

| JP2005045053A (ja) * | 2003-07-23 | 2005-02-17 | Elpida Memory Inc | 半導体装置の製造方法 |

| JP2005129906A (ja) * | 2003-10-21 | 2005-05-19 | Applied Materials Inc | エッチングプロセスの精度及び反復性を制御する装置及び方法 |

| US20060006136A1 (en) * | 2004-07-06 | 2006-01-12 | Tokyo Electron Limited | Processing system and method for chemically treating a tera layer |

| JP2006505141A (ja) * | 2002-10-31 | 2006-02-09 | アプライド マテリアルズ インコーポレイテッド | シリコン含有誘電物質をエッチングする方法 |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4431477A (en) * | 1983-07-05 | 1984-02-14 | Matheson Gas Products, Inc. | Plasma etching with nitrous oxide and fluoro compound gas mixture |

| EP0394597A1 (en) | 1989-04-28 | 1990-10-31 | International Business Machines Corporation | Follow-up System for Monitoring the Etching Process in an RIE Equipment and its Application to Producing High-resolution and Reproducible Patterns |

| US5153691A (en) | 1989-06-21 | 1992-10-06 | Xicor, Inc. | Apparatus for a dual thickness floating gate memory cell |

| US5431770A (en) | 1993-10-13 | 1995-07-11 | At&T Corp. | Transistor gate formation |

| US5804088A (en) | 1996-07-12 | 1998-09-08 | Texas Instruments Incorporated | Intermediate layer lithography |

| US5885887A (en) | 1997-04-21 | 1999-03-23 | Advanced Micro Devices, Inc. | Method of making an igfet with selectively doped multilevel polysilicon gate |

| US5930634A (en) | 1997-04-21 | 1999-07-27 | Advanced Micro Devices, Inc. | Method of making an IGFET with a multilevel gate |

| US5965461A (en) | 1997-08-01 | 1999-10-12 | Advanced Micro Devices, Inc. | Controlled linewidth reduction during gate pattern formation using a spin-on barc |

| JPH1168095A (ja) | 1997-08-11 | 1999-03-09 | Fujitsu Ltd | 半導体装置の製造方法 |

| US6121123A (en) | 1997-09-05 | 2000-09-19 | Advanced Micro Devices, Inc. | Gate pattern formation using a BARC as a hardmask |

| CN1273646A (zh) | 1998-07-10 | 2000-11-15 | 克拉瑞特国际有限公司 | 底部抗反射涂层组合物和用于该组合物的新型聚合物染料 |

| US6156629A (en) * | 1998-10-01 | 2000-12-05 | Taiwan Semiconductor Manufacturing Company | Method for patterning a polysilicon gate in deep submicron technology |

| US6194323B1 (en) | 1998-12-16 | 2001-02-27 | Lucent Technologies Inc. | Deep sub-micron metal etch with in-situ hard mask etch |

| US6156485A (en) | 1999-01-19 | 2000-12-05 | Taiwan Semiconductor Manufacturing Company Ltd. | Film scheme to solve high aspect ratio metal etch masking layer selectivity and improve photo I-line PR resolution capability in quarter-micron technology |

| US6890448B2 (en) | 1999-06-11 | 2005-05-10 | Shipley Company, L.L.C. | Antireflective hard mask compositions |

| US6248635B1 (en) | 1999-10-25 | 2001-06-19 | Advanced Micro Devices, Inc. | Process for fabricating a bit-line in a monos device using a dual layer hard mask |

| US6174818B1 (en) | 1999-11-19 | 2001-01-16 | Taiwan Semiconductor Manufacturing Company | Method of patterning narrow gate electrode |

| US6420097B1 (en) | 2000-05-02 | 2002-07-16 | Advanced Micro Devices, Inc. | Hardmask trim process |

| US6281130B1 (en) | 2000-06-16 | 2001-08-28 | Advanced Micro Devices, Inc. | Method for developing ultra-thin resist films |

| US6429067B1 (en) | 2001-01-17 | 2002-08-06 | International Business Machines Corporation | Dual mask process for semiconductor devices |

| US6828205B2 (en) * | 2002-02-07 | 2004-12-07 | Taiwan Semiconductor Manufacturing Co., Ltd | Method using wet etching to trim a critical dimension |

| US6921723B1 (en) * | 2002-04-23 | 2005-07-26 | Applied Materials, Inc. | Etching method having high silicon-to-photoresist selectivity |

| US6762130B2 (en) | 2002-05-31 | 2004-07-13 | Texas Instruments Incorporated | Method of photolithographically forming extremely narrow transistor gate elements |

| US6794230B2 (en) | 2002-10-31 | 2004-09-21 | Taiwan Semiconductor Manufacturing Company, Ltd. | Approach to improve line end shortening |

| US6900002B1 (en) | 2002-11-19 | 2005-05-31 | Advanced Micro Devices, Inc. | Antireflective bi-layer hardmask including a densified amorphous carbon layer |

| US6913958B1 (en) | 2003-02-14 | 2005-07-05 | Advanced Micro Devices | Method for patterning a feature using a trimmed hardmask |

| US6764903B1 (en) * | 2003-04-30 | 2004-07-20 | Taiwan Semiconductor Manufacturing Co., Ltd | Dual hard mask layer patterning method |

| US7077903B2 (en) | 2003-11-10 | 2006-07-18 | International Business Machines Corporation | Etch selectivity enhancement for tunable etch resistant anti-reflective layer |

| DE10356668B4 (de) | 2003-12-04 | 2005-11-03 | Infineon Technologies Ag | Herstellungsverfahren für eine Hartmaske auf einer Halbleiterstruktur |

| US7354847B2 (en) * | 2004-01-26 | 2008-04-08 | Taiwan Semiconductor Manufacturing Company | Method of trimming technology |

| KR100704470B1 (ko) * | 2004-07-29 | 2007-04-10 | 주식회사 하이닉스반도체 | 비결정성 탄소막을 희생 하드마스크로 이용하는반도체소자 제조 방법 |

| US7271106B2 (en) | 2004-08-31 | 2007-09-18 | Micron Technology, Inc. | Critical dimension control for integrated circuits |

| US20070037101A1 (en) * | 2005-08-15 | 2007-02-15 | Fujitsu Limited | Manufacture method for micro structure |

| US7662718B2 (en) * | 2006-03-09 | 2010-02-16 | Micron Technology, Inc. | Trim process for critical dimension control for integrated circuits |

-

2006

- 2006-03-09 US US11/372,825 patent/US7662718B2/en not_active Expired - Fee Related

-

2007

- 2007-03-05 CN CN2007800136527A patent/CN101421824B/zh not_active Expired - Fee Related

- 2007-03-05 WO PCT/US2007/005639 patent/WO2007103343A1/en active Application Filing

- 2007-03-05 KR KR1020087024655A patent/KR20080112281A/ko not_active Application Discontinuation

- 2007-03-05 JP JP2008558345A patent/JP2009529784A/ja active Pending

- 2007-03-05 EP EP07752349A patent/EP2002465A1/en not_active Withdrawn

-

2010

- 2010-02-02 US US12/698,407 patent/US7910483B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003031557A (ja) * | 2001-07-16 | 2003-01-31 | Toshiba Corp | 半導体装置の製造方法 |

| JP2003249485A (ja) * | 2001-11-12 | 2003-09-05 | Chartered Semiconductor Mfg Ltd | 有機底部反射防止コーティング及びフォトレジストのトリミングプロセスのための方法 |

| JP2006505141A (ja) * | 2002-10-31 | 2006-02-09 | アプライド マテリアルズ インコーポレイテッド | シリコン含有誘電物質をエッチングする方法 |

| JP2005045053A (ja) * | 2003-07-23 | 2005-02-17 | Elpida Memory Inc | 半導体装置の製造方法 |

| JP2005129906A (ja) * | 2003-10-21 | 2005-05-19 | Applied Materials Inc | エッチングプロセスの精度及び反復性を制御する装置及び方法 |

| US20060006136A1 (en) * | 2004-07-06 | 2006-01-12 | Tokyo Electron Limited | Processing system and method for chemically treating a tera layer |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010003757A (ja) * | 2008-06-18 | 2010-01-07 | Fujitsu Microelectronics Ltd | 半導体装置の製造方法 |

| CN102478764A (zh) * | 2010-11-30 | 2012-05-30 | 中芯国际集成电路制造(北京)有限公司 | 双重图形化方法 |

| CN102478764B (zh) * | 2010-11-30 | 2013-08-07 | 中芯国际集成电路制造(北京)有限公司 | 双重图形化方法 |

| JP2014507795A (ja) * | 2010-12-27 | 2014-03-27 | ブルーワー サイエンス アイ エヌ シー. | 高度なパターン形成に必要な小型フィーチャのパターン形成プロセス |

| US9960038B2 (en) | 2010-12-27 | 2018-05-01 | Brewer Science, Inc. | Processes to pattern small features for advanced patterning needs |

| JP2013089827A (ja) * | 2011-10-20 | 2013-05-13 | Fujitsu Semiconductor Ltd | 半導体装置の製造方法 |

| JP2014157956A (ja) * | 2013-02-18 | 2014-08-28 | Mitsubishi Electric Corp | 炭化珪素半導体装置の製造方法 |

| US9177809B2 (en) | 2013-07-03 | 2015-11-03 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| US9305936B2 (en) | 2013-07-03 | 2016-04-05 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device and method of manufacturing the same |

| US9779952B2 (en) | 2013-08-27 | 2017-10-03 | Tokyo Electron Limited | Method for laterally trimming a hardmask |

| KR20160030378A (ko) * | 2014-09-09 | 2016-03-17 | 도쿄엘렉트론가부시키가이샤 | 서브-해상도 스케일들로 상이한 임계 치수들을 패터닝하기 위한 방법 |

| KR102328025B1 (ko) | 2014-09-09 | 2021-11-17 | 도쿄엘렉트론가부시키가이샤 | 서브-해상도 스케일들로 상이한 임계 치수들을 패터닝하기 위한 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101421824B (zh) | 2012-04-11 |

| CN101421824A (zh) | 2009-04-29 |

| US20070212889A1 (en) | 2007-09-13 |

| WO2007103343A1 (en) | 2007-09-13 |

| US7662718B2 (en) | 2010-02-16 |

| US20100173498A1 (en) | 2010-07-08 |

| US7910483B2 (en) | 2011-03-22 |

| KR20080112281A (ko) | 2008-12-24 |

| EP2002465A1 (en) | 2008-12-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2009529784A (ja) | 集積回路の限界寸法を制御するトリム工程 | |

| US7563723B2 (en) | Critical dimension control for integrated circuits | |

| US20060205223A1 (en) | Line edge roughness reduction compatible with trimming | |

| KR100990064B1 (ko) | 식각 공정에서 포토레지스트를 경화하는 방법 및 조성물 | |

| US20020045331A1 (en) | Method of producing a semiconductor device using feature trimming | |

| JP5100198B2 (ja) | 半導体素子の微細パターンの形成方法 | |

| KR100388591B1 (ko) | 미세 패턴 형성 방법 및 이것을 이용한 반도체 장치 또는액정 장치의 제조 방법 | |

| KR100849190B1 (ko) | 반도체 소자의 미세 패턴 형성 방법 | |

| KR100727439B1 (ko) | 금속 배선 형성 방법 | |

| JP3906037B2 (ja) | 半導体装置の製造方法 | |

| KR100875653B1 (ko) | 반도체 소자의 미세 패턴 형성 방법 | |

| KR100571629B1 (ko) | 반도체 소자 제조 방법 | |

| KR100816210B1 (ko) | 반도체 장치 형성 방법 | |

| KR100881397B1 (ko) | 비정질 카본막의 형성방법 및 이를 이용한 반도체 소자의패턴 형성방법 | |

| TWI794548B (zh) | 改善光阻粗糙度及移除光阻浮渣的電漿處理方法 | |

| KR100912958B1 (ko) | 반도체 소자의 미세 패턴 제조 방법 | |

| KR100549583B1 (ko) | 반도체소자의 게이트 제조방법 | |

| KR100699678B1 (ko) | 하드 마스크를 이용한 패턴 형성 방법 | |

| CN114975104A (zh) | 形成半导体器件的方法 | |

| KR20080094403A (ko) | 반도체 소자의 하드마스크 형성 방법 및 이를 이용한 패턴형성 방법 | |

| KR20020052842A (ko) | 플라즈마 애싱을 이용한 포토레지스트패턴 형성방법 | |

| KR20080088988A (ko) | 반도체 소자의 제조방법 | |

| KR20050067491A (ko) | 스페이서를 이용한 나칭 게이트 형성 방법 | |

| KR19990057899A (ko) | 반도체 소자 제조 방법 | |

| JPH06244158A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100218 Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100615 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120619 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120914 Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20120914 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20121211 |