JP2009105390A - 半導体装置およびその作製方法 - Google Patents

半導体装置およびその作製方法 Download PDFInfo

- Publication number

- JP2009105390A JP2009105390A JP2008251237A JP2008251237A JP2009105390A JP 2009105390 A JP2009105390 A JP 2009105390A JP 2008251237 A JP2008251237 A JP 2008251237A JP 2008251237 A JP2008251237 A JP 2008251237A JP 2009105390 A JP2009105390 A JP 2009105390A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- film

- layer

- amorphous semiconductor

- type amorphous

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 200

- 238000000034 method Methods 0.000 title claims description 52

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 229910021417 amorphous silicon Inorganic materials 0.000 claims abstract description 115

- 239000000758 substrate Substances 0.000 claims abstract description 76

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims abstract description 68

- 239000011574 phosphorus Substances 0.000 claims abstract description 68

- 229910052698 phosphorus Inorganic materials 0.000 claims abstract description 68

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 claims abstract description 51

- 229910000073 phosphorus hydride Inorganic materials 0.000 claims abstract description 25

- 239000007789 gas Substances 0.000 claims description 51

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 30

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 19

- 239000001301 oxygen Substances 0.000 claims description 19

- 229910052760 oxygen Inorganic materials 0.000 claims description 19

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 claims description 17

- 239000001257 hydrogen Substances 0.000 claims description 15

- 229910052739 hydrogen Inorganic materials 0.000 claims description 15

- 229910052757 nitrogen Inorganic materials 0.000 claims description 15

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 14

- 229910000077 silane Inorganic materials 0.000 claims description 14

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical group N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 5

- 229910052799 carbon Inorganic materials 0.000 claims description 5

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 3

- 229910052796 boron Inorganic materials 0.000 claims description 3

- 230000005669 field effect Effects 0.000 abstract description 15

- 230000015572 biosynthetic process Effects 0.000 abstract description 8

- 239000010408 film Substances 0.000 description 341

- 239000010410 layer Substances 0.000 description 267

- 239000004973 liquid crystal related substance Substances 0.000 description 42

- 239000010409 thin film Substances 0.000 description 40

- 239000012535 impurity Substances 0.000 description 35

- 230000008569 process Effects 0.000 description 19

- 229910052782 aluminium Inorganic materials 0.000 description 18

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 18

- 239000000463 material Substances 0.000 description 16

- 238000004364 calculation method Methods 0.000 description 15

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 14

- 229910052750 molybdenum Inorganic materials 0.000 description 14

- 239000011733 molybdenum Substances 0.000 description 14

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 13

- 238000005530 etching Methods 0.000 description 12

- 230000006870 function Effects 0.000 description 10

- 238000002834 transmittance Methods 0.000 description 9

- 239000003990 capacitor Substances 0.000 description 8

- 238000006243 chemical reaction Methods 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 8

- 239000000370 acceptor Substances 0.000 description 7

- 239000004020 conductor Substances 0.000 description 7

- 208000028659 discharge Diseases 0.000 description 7

- 230000005684 electric field Effects 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 238000004544 sputter deposition Methods 0.000 description 7

- 230000007423 decrease Effects 0.000 description 6

- 238000009826 distribution Methods 0.000 description 6

- 239000011521 glass Substances 0.000 description 6

- 239000011159 matrix material Substances 0.000 description 6

- 238000005192 partition Methods 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 229910000838 Al alloy Inorganic materials 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 239000002772 conduction electron Substances 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 239000010936 titanium Substances 0.000 description 5

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 238000004458 analytical method Methods 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- 125000004429 atom Chemical group 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 229910052990 silicon hydride Inorganic materials 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 229910001316 Ag alloy Inorganic materials 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 2

- JFBZPFYRPYOZCQ-UHFFFAOYSA-N [Li].[Al] Chemical compound [Li].[Al] JFBZPFYRPYOZCQ-UHFFFAOYSA-N 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 229910052791 calcium Inorganic materials 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- WUKWITHWXAAZEY-UHFFFAOYSA-L calcium difluoride Chemical compound [F-].[F-].[Ca+2] WUKWITHWXAAZEY-UHFFFAOYSA-L 0.000 description 2

- 229910001634 calcium fluoride Inorganic materials 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910000423 chromium oxide Inorganic materials 0.000 description 2

- 238000004040 coloring Methods 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 238000007865 diluting Methods 0.000 description 2

- 238000010891 electric arc Methods 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 125000004437 phosphorous atom Chemical group 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- -1 polysiloxane Polymers 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910019974 CrSi Inorganic materials 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 238000006124 Pilkington process Methods 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000005407 aluminoborosilicate glass Substances 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 230000001143 conditioned effect Effects 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 239000002274 desiccant Substances 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 208000037265 diseases, disorders, signs and symptoms Diseases 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 208000035475 disorder Diseases 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005538 encapsulation Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000003779 heat-resistant material Substances 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 150000002500 ions Chemical group 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 239000005001 laminate film Substances 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 239000013081 microcrystal Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 238000007500 overflow downdraw method Methods 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/4908—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET for thin film semiconductor, e.g. gate of TFT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

Abstract

【解決手段】逆スタガ型のTFTにおいて、ゲート絶縁膜と非晶質半導体層の間にn型化させた非晶質半導体層を薄く形成する。ホスフィンガスを微量に含む雰囲気下に、ゲート絶縁膜まで形成した基板を曝した後、非晶質半導体層を成膜することで、非晶質半導体層の成膜初期にリンを含む非晶質半導体層を形成する。こうして得られる非晶質半導体層は、ゲート絶縁膜表面近傍にリンの濃度ピークが位置する。

【選択図】図1

Description

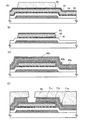

本実施の形態では、液晶表示装置に用いられる薄膜トランジスタの作製工程について、図1乃至図4を用いて説明する。図1乃至図3は、薄膜トランジスタの作製工程を示す断面図であり、図4は、一画素における薄膜トランジスタ及び画素電極の接続領域の上面図である。

実施の形態1は、シランガス及び微量のホスフィンガスに曝した後、非晶質シリコン膜を成膜することによってn型化された非晶質シリコン膜と、i型の非晶質シリコン膜との積層を形成する例を示したが、特に限定されず、ゲート絶縁膜を積層構造として下層にリンを含ませることによって、その上方にi型の非晶質シリコン膜を成膜し、ゲート絶縁膜の界面付近にn型化された非晶質シリコン膜が形成される方法を用いてもよい。その例を図5を用いて説明する。

実施の形態1は、シランガス及び微量のホスフィンガスに曝した後、非晶質シリコン膜を成膜することによってn型化された非晶質シリコン膜と、i型の非晶質シリコン膜との積層を形成する例を示したが、特に限定されず、ゲート絶縁膜を形成する前にチャンバー内壁にリンを含む非晶質シリコン膜を成膜しておくことで、n型化された非晶質シリコン膜と、i型の非晶質シリコン膜との積層を形成してもよい。

実施の形態1とは異なる薄膜トランジスタの作製方法について、図8乃至図12を用いて説明する。ここでは、上記実施の形態1よりフォトマスク数を削減することが可能なプロセスを用いて薄膜トランジスタを作製する工程について示す。

実施の形態1とは一部工程が異なる薄膜トランジスタの作製方法について、図13を用いて説明する。ここでは、多階調マスクを用いて保持容量を形成する工程と薄膜トランジスタと画素電極のコンタクトを形成する工程について示す。なお、図13において、実施の形態1と同一の箇所は、実施の形態1と同じ符号を用いる。

12:ゲート電極

13:ゲート絶縁膜

14:n−層

15:i型の非晶質半導体層

16:ソース領域

17:ドレイン領域

18:ソース電極

19:ドレイン電極

20:n−層

21a:第1のi層

21b:第2のi層

21c:第3のi層

50:基板

51a:第1の導電層

51b:第2の導電層

52:ゲート絶縁膜

53:n型化された非晶質シリコン膜

54:i型の非晶質シリコン膜

55:一導電型を付与する不純物が添加された半導体膜

56:レジストマスク

59:多階調マスク

61:n型化された非晶質シリコン膜

62:i型の非晶質シリコン膜

63:一導電型を付与する不純物が添加された半導体膜

65a、65b、65c:導電膜

66:レジストマスク

67:第1のゲート絶縁膜

68:第2のゲート絶縁膜

71a、71b、71c:ソース電極またはドレイン電極

72:ソース領域及びドレイン領域

73:i型の非晶質シリコン膜

74:薄膜トランジスタ

75:保持容量

76:絶縁膜

77:画素電極

78a:第1の導電層

78b:第2の導電層

79:薄膜トランジスタ

80:レジストマスク

81:レジストマスク

82:平坦化膜

83:薄膜トランジスタ

84a:第1の層間絶縁膜

84b:第2の層間絶縁膜

85a〜85c導電膜

86:レジストマスク

87:i型の非晶質シリコン膜

88:ソース領域及びドレイン領域

89a、89b、89c:導電膜

90:n型化された非晶質シリコン膜

92a、92b、92c:ソース電極及びドレイン電極

Claims (10)

- 絶縁表面を有する基板上にゲート電極を形成し、

前記ゲート電極上に絶縁層を形成し、

ホスフィンガスを含む雰囲気下に前記絶縁層の表面を曝し、

前記絶縁層上にn型非晶質半導体層を形成し、

前記n型非晶質半導体層上に前記n型非晶質半導体層よりも膜厚の厚い非晶質半導体層を形成し、

前記非晶質半導体層上に前記n型非晶質半導体層に含まれるリンの濃度よりも高濃度のリンを含むn型半導体層を形成し、

前記n型半導体層上にソース電極またはドレイン電極を形成する半導体装置の作製方法。 - 請求項1において、前記ホスフィンガスを含む雰囲気は、シランガス及び水素を含む半導体装置の作製方法。

- 絶縁表面を有する基板上にゲート電極を形成し、

前記ゲート電極上にリンを含む絶縁層を形成し、

前記リンを含む絶縁層上にn型非晶質半導体層と、前記n型非晶質半導体層上に前記n型非晶質半導体層よりも膜厚の厚い非晶質半導体層を形成し、

前記非晶質半導体層上に前記n型非晶質半導体層に含まれるリンの濃度よりも高濃度のリンを含むn型半導体層を形成し、

前記n型半導体層上にソース電極またはドレイン電極を形成する半導体装置の作製方法。 - 請求項1乃至3のいずれか一において、前記非晶質半導体層は、水素を含むアモルファスシリコンである半導体装置の作製方法。

- 絶縁表面を有する基板上にゲート電極と、

前記ゲート電極上に絶縁層と、

前記絶縁層上にn型非晶質半導体層と、

前記n型非晶質半導体層上に前記n型非晶質半導体層よりも膜厚の厚い非晶質半導体層と、

前記非晶質半導体層上に前記n型非晶質半導体層に含まれるリンの濃度よりも高濃度のリンを含むn型半導体層と、

前記n型半導体層上にソース電極またはドレイン電極とを有し、

前記n型非晶質半導体層において、窒素及び酸素の濃度が前記n型非晶質半導体層に含まれるリン濃度の10倍を超えない濃度であり、且つ、ボロン濃度は前記n型非晶質半導体層に含まれるリン濃度の10分の1未満である半導体装置。 - 請求項5において、前記n型非晶質半導体層は、窒素及び酸素の濃度が5×1018cm−3以下であり、且つ、リンの濃度が6×1015cm−3以上3×1018cm−3以下である半導体装置。

- 請求項5または請求項6において、リンの濃度ピークは、前記絶縁層と前記n型非晶質半導体層との界面に位置する半導体装置。

- 請求項5乃至7のいずれか一において、さらに、前記n型非晶質半導体層において、炭素の濃度が5×1018cm−3以下である半導体装置。

- 請求項5乃至7のいずれか一において、前記非晶質半導体層は、水素を含むアモルファスシリコンである半導体装置。

- 請求項5乃至9のいずれか一において、前記絶縁層は窒化シリコン膜である半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008251237A JP2009105390A (ja) | 2007-10-05 | 2008-09-29 | 半導体装置およびその作製方法 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007262603 | 2007-10-05 | ||

| JP2008251237A JP2009105390A (ja) | 2007-10-05 | 2008-09-29 | 半導体装置およびその作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014152565A Division JP2014212346A (ja) | 2007-10-05 | 2014-07-28 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009105390A true JP2009105390A (ja) | 2009-05-14 |

| JP2009105390A5 JP2009105390A5 (ja) | 2011-08-18 |

Family

ID=40522484

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008251237A Withdrawn JP2009105390A (ja) | 2007-10-05 | 2008-09-29 | 半導体装置およびその作製方法 |

| JP2014152565A Withdrawn JP2014212346A (ja) | 2007-10-05 | 2014-07-28 | 半導体装置の作製方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014152565A Withdrawn JP2014212346A (ja) | 2007-10-05 | 2014-07-28 | 半導体装置の作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8183102B2 (ja) |

| JP (2) | JP2009105390A (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101771268B1 (ko) | 2009-10-09 | 2017-08-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제조 방법 |

| US9865742B2 (en) | 2009-10-09 | 2018-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP2019033288A (ja) * | 2009-11-27 | 2019-02-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI521712B (zh) * | 2007-12-03 | 2016-02-11 | 半導體能源研究所股份有限公司 | 薄膜電晶體,包括該薄膜電晶體的顯示裝置,和其製造方法 |

| TWI437697B (zh) * | 2009-07-27 | 2014-05-11 | Kobe Steel Ltd | Wiring structure and a display device having a wiring structure |

| KR102148664B1 (ko) * | 2009-11-06 | 2020-08-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| JP6199583B2 (ja) | 2012-04-27 | 2017-09-20 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9882058B2 (en) * | 2013-05-03 | 2018-01-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| CN105116653B (zh) * | 2015-09-14 | 2019-02-15 | 深超光电(深圳)有限公司 | 显示面板 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01125867A (ja) * | 1987-11-10 | 1989-05-18 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ製造方法 |

| JPH04196132A (ja) * | 1990-11-26 | 1992-07-15 | Seiko Epson Corp | 表示装置の製造方法 |

| JPH11177094A (ja) * | 1997-12-08 | 1999-07-02 | Advanced Display Inc | 半導体薄膜トランジスタおよび該半導体薄膜トランジスタを含む半導体薄膜トランジスタアレイ基板 |

| JP2003297850A (ja) * | 2002-04-02 | 2003-10-17 | Advanced Display Inc | 薄膜トランジスタアレイ及びその製造方法並びにこれを用いた液晶表示装置 |

| JP2004274050A (ja) * | 2003-03-04 | 2004-09-30 | Samsung Electronics Co Ltd | 非晶質−シリコン薄膜トランジスタとこれを有するシフトレジスタ。 |

| JP2006091866A (ja) * | 2004-08-27 | 2006-04-06 | Semiconductor Energy Lab Co Ltd | 表示装置及び電子機器 |

| JP2007011351A (ja) * | 2005-06-27 | 2007-01-18 | Lg Phillips Lcd Co Ltd | 漏洩電流を減少させる液晶表示素子及びその製造方法 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5886776A (ja) | 1981-11-19 | 1983-05-24 | Matsushita Electric Ind Co Ltd | Mos型トランジスタの製造方法 |

| JPS59172774A (ja) | 1983-03-22 | 1984-09-29 | Nec Corp | アモルファスシリコン薄膜トランジスタ |

| JPS60160170A (ja) | 1984-01-31 | 1985-08-21 | Seiko Instr & Electronics Ltd | 薄膜トランジスタ |

| JPS63258072A (ja) | 1987-04-15 | 1988-10-25 | Nec Corp | 電界効果トランジスタ |

| US5173753A (en) * | 1989-08-10 | 1992-12-22 | Industrial Technology Research Institute | Inverted coplanar amorphous silicon thin film transistor which provides small contact capacitance and resistance |

| US5521107A (en) * | 1991-02-16 | 1996-05-28 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming a field-effect transistor including anodic oxidation of the gate |

| JP3156878B2 (ja) * | 1992-04-30 | 2001-04-16 | 株式会社東芝 | 半導体装置およびその製造方法 |

| US5470768A (en) * | 1992-08-07 | 1995-11-28 | Fujitsu Limited | Method for fabricating a thin-film transistor |

| JPH06104283A (ja) | 1992-09-22 | 1994-04-15 | Sharp Corp | 薄膜トランジスタ |

| JP3637069B2 (ja) * | 1993-03-12 | 2005-04-06 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3256084B2 (ja) * | 1994-05-26 | 2002-02-12 | 株式会社半導体エネルギー研究所 | 半導体集積回路およびその作製方法 |

| JP2762968B2 (ja) * | 1995-09-28 | 1998-06-11 | 日本電気株式会社 | 電界効果型薄膜トランジスタの製造方法 |

| KR970077745A (ko) * | 1996-05-28 | 1997-12-12 | 장진 | 염소가 함유된 비정질 실리콘/비정질 실리콘 다층을 활성층으로 이용한 박막 트랜지스터의 구조 및 제조 방법 |

| JPH10270701A (ja) * | 1997-03-27 | 1998-10-09 | Advanced Display:Kk | 薄膜トランジスタおよびその製法 |

| JP2001168092A (ja) * | 1999-01-08 | 2001-06-22 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP2002110973A (ja) * | 2000-09-29 | 2002-04-12 | Seiko Instruments Inc | 半導体装置の製造方法 |

| US20050176188A1 (en) * | 2004-02-11 | 2005-08-11 | Fang-Chen Luo | Thin film transistor and manufacturing method thereof |

| US7205171B2 (en) * | 2004-02-11 | 2007-04-17 | Au Optronics Corporation | Thin film transistor and manufacturing method thereof including a lightly doped channel |

| TWI234288B (en) * | 2004-07-27 | 2005-06-11 | Au Optronics Corp | Method for fabricating a thin film transistor and related circuits |

| US20060088976A1 (en) * | 2004-10-22 | 2006-04-27 | Applied Materials, Inc. | Methods and compositions for chemical mechanical polishing substrates |

| KR101158896B1 (ko) * | 2005-10-28 | 2012-06-25 | 삼성전자주식회사 | 박막트랜지스터 기판 및 이의 제조방법과,박막트랜지스터를 갖는 액정표시패널 및 전계발광 표시패널 |

| KR100671824B1 (ko) * | 2005-12-14 | 2007-01-19 | 진 장 | 역 스태거드 박막 트랜지스터 제조 방법 |

| TW200915573A (en) * | 2007-09-29 | 2009-04-01 | Chunghwa Picture Tubes Ltd | Thin film transistor, pixel structure and fabricating methods thereof |

| US8344378B2 (en) * | 2009-06-26 | 2013-01-01 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and method for manufacturing the same |

-

2008

- 2008-09-29 JP JP2008251237A patent/JP2009105390A/ja not_active Withdrawn

- 2008-10-01 US US12/243,085 patent/US8183102B2/en not_active Expired - Fee Related

-

2014

- 2014-07-28 JP JP2014152565A patent/JP2014212346A/ja not_active Withdrawn

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01125867A (ja) * | 1987-11-10 | 1989-05-18 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ製造方法 |

| JPH04196132A (ja) * | 1990-11-26 | 1992-07-15 | Seiko Epson Corp | 表示装置の製造方法 |

| JPH11177094A (ja) * | 1997-12-08 | 1999-07-02 | Advanced Display Inc | 半導体薄膜トランジスタおよび該半導体薄膜トランジスタを含む半導体薄膜トランジスタアレイ基板 |

| JP2003297850A (ja) * | 2002-04-02 | 2003-10-17 | Advanced Display Inc | 薄膜トランジスタアレイ及びその製造方法並びにこれを用いた液晶表示装置 |

| JP2004274050A (ja) * | 2003-03-04 | 2004-09-30 | Samsung Electronics Co Ltd | 非晶質−シリコン薄膜トランジスタとこれを有するシフトレジスタ。 |

| JP2006091866A (ja) * | 2004-08-27 | 2006-04-06 | Semiconductor Energy Lab Co Ltd | 表示装置及び電子機器 |

| JP2007011351A (ja) * | 2005-06-27 | 2007-01-18 | Lg Phillips Lcd Co Ltd | 漏洩電流を減少させる液晶表示素子及びその製造方法 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101771268B1 (ko) | 2009-10-09 | 2017-08-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제조 방법 |

| US9865742B2 (en) | 2009-10-09 | 2018-01-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US10290742B2 (en) | 2009-10-09 | 2019-05-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including oxide semiconductor layer |

| JP2019033288A (ja) * | 2009-11-27 | 2019-02-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2019036752A (ja) * | 2009-11-27 | 2019-03-07 | 株式会社半導体エネルギー研究所 | 半導体装置及びその作製方法 |

| US20190109259A1 (en) | 2009-11-27 | 2019-04-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US10396236B2 (en) | 2009-11-27 | 2019-08-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device |

| JP2020014015A (ja) * | 2009-11-27 | 2020-01-23 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US11894486B2 (en) | 2009-11-27 | 2024-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2014212346A (ja) | 2014-11-13 |

| US8183102B2 (en) | 2012-05-22 |

| US20090090909A1 (en) | 2009-04-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7289021B1 (ja) | 半導体装置 | |

| JP6640823B2 (ja) | 半導体装置 | |

| US8030147B2 (en) | Method for manufacturing thin film transistor and display device including the thin film transistor | |

| US8951849B2 (en) | Method for manufacturing semiconductor device including layer containing yttria-stabilized zirconia | |

| US7824939B2 (en) | Method for manufacturing display device comprising separated and electrically connected source wiring layers | |

| US8183102B2 (en) | Semiconductor device and manufacturing method thereof | |

| KR101399608B1 (ko) | 반도체 장치의 제작방법 | |

| JP5496500B2 (ja) | 半導体装置の作製方法 | |

| JP4825181B2 (ja) | 薄膜トランジスタの作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110704 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110704 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130604 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130606 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130704 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140204 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140214 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140722 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20140729 |