JP2007294488A - 半導体装置、電子部品、及び半導体装置の製造方法 - Google Patents

半導体装置、電子部品、及び半導体装置の製造方法 Download PDFInfo

- Publication number

- JP2007294488A JP2007294488A JP2006117074A JP2006117074A JP2007294488A JP 2007294488 A JP2007294488 A JP 2007294488A JP 2006117074 A JP2006117074 A JP 2006117074A JP 2006117074 A JP2006117074 A JP 2006117074A JP 2007294488 A JP2007294488 A JP 2007294488A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor chip

- semiconductor device

- external connection

- semiconductor

- connection terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

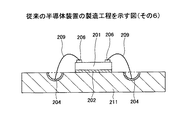

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/568—Temporary substrate used as encapsulation process aid

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00

- H01L25/0652—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00 the devices being arranged next and on each other, i.e. mixed assemblies

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H10D89/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

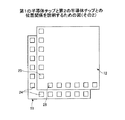

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85001—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector involving a temporary auxiliary member not forming part of the bonding apparatus, e.g. removable or sacrificial coating, film or substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/922—Connecting different surfaces of the semiconductor or solid-state body with connectors of different types

- H01L2224/9222—Sequential connecting processes

- H01L2224/92242—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92247—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0651—Wire or wire-like electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes

- H01L2225/04—All the devices being of a type provided for in the same main group of the same subclass of class H10, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same main group of the same subclass of class H10

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06555—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking

- H01L2225/06562—Geometry of the stack, e.g. form of the devices, geometry to facilitate stacking at least one device in the stack being rotated or offset

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of semiconductor or other solid state devices

- H01L25/03—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes

- H01L25/10—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices having separate containers

- H01L25/105—Assemblies consisting of a plurality of semiconductor or other solid state devices all the devices being of a type provided for in a single subclass of subclasses H10B, H10D, H10F, H10H, H10K or H10N, e.g. assemblies of rectifier diodes the devices having separate containers the devices being integrated devices of class H10

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

- H01L2924/1815—Shape

- H01L2924/1816—Exposing the passive side of the semiconductor or solid-state body

- H01L2924/18165—Exposing the passive side of the semiconductor or solid-state body of a wire bonded chip

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006117074A JP2007294488A (ja) | 2006-04-20 | 2006-04-20 | 半導体装置、電子部品、及び半導体装置の製造方法 |

| KR1020070037328A KR20070104236A (ko) | 2006-04-20 | 2007-04-17 | 반도체 장치, 전자 장치, 및 반도체 장치의 제조 방법 |

| US11/736,926 US8525355B2 (en) | 2006-04-20 | 2007-04-18 | Semiconductor device, electronic apparatus and semiconductor device fabricating method |

| US13/368,900 US20120133056A1 (en) | 2006-04-20 | 2012-02-08 | Semiconductor device, electronic apparatus and semiconductor device fabricating method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006117074A JP2007294488A (ja) | 2006-04-20 | 2006-04-20 | 半導体装置、電子部品、及び半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007294488A true JP2007294488A (ja) | 2007-11-08 |

| JP2007294488A5 JP2007294488A5 (enExample) | 2009-04-09 |

Family

ID=38618728

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006117074A Pending JP2007294488A (ja) | 2006-04-20 | 2006-04-20 | 半導体装置、電子部品、及び半導体装置の製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US8525355B2 (enExample) |

| JP (1) | JP2007294488A (enExample) |

| KR (1) | KR20070104236A (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8664757B2 (en) | 2010-07-12 | 2014-03-04 | Samsung Electronics Co., Ltd. | High density chip stacked package, package-on-package and method of fabricating the same |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100886717B1 (ko) | 2007-10-16 | 2009-03-04 | 주식회사 하이닉스반도체 | 적층 반도체 패키지 및 이의 제조 방법 |

| US8014166B2 (en) * | 2008-09-06 | 2011-09-06 | Broadpak Corporation | Stacking integrated circuits containing serializer and deserializer blocks using through silicon via |

| JP5918664B2 (ja) * | 2012-09-10 | 2016-05-18 | 株式会社東芝 | 積層型半導体装置の製造方法 |

| US9368422B2 (en) * | 2012-12-20 | 2016-06-14 | Nvidia Corporation | Absorbing excess under-fill flow with a solder trench |

| JP2018101699A (ja) * | 2016-12-20 | 2018-06-28 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置、固体撮像装置の製造方法および電子機器 |

| US20200118991A1 (en) * | 2018-10-15 | 2020-04-16 | Intel Corporation | Pre-patterned fine-pitch bond pad interposer |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001196526A (ja) * | 2000-01-06 | 2001-07-19 | Seiko Epson Corp | マルチベアチップ実装体、マルチチップパッケージ、半導体装置、ならびに電子機器 |

| JP2003303919A (ja) * | 2002-04-10 | 2003-10-24 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2004031946A (ja) * | 2003-06-05 | 2004-01-29 | Nec Electronics Corp | 半導体装置及びその製造方法 |

| WO2004034433A2 (en) * | 2002-10-08 | 2004-04-22 | Chippac, Inc. | Semiconductor stacked multi-package module having inverted second package |

| JP2004179622A (ja) * | 2002-11-15 | 2004-06-24 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2005268533A (ja) * | 2004-03-18 | 2005-09-29 | Shinko Electric Ind Co Ltd | 積層型半導体装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2439478A1 (fr) * | 1978-10-19 | 1980-05-16 | Cii Honeywell Bull | Boitier plat pour dispositifs a circuits integres |

| JP3007833B2 (ja) | 1995-12-12 | 2000-02-07 | 富士通株式会社 | 半導体装置及びその製造方法及びリードフレーム及びその製造方法 |

| US6404049B1 (en) * | 1995-11-28 | 2002-06-11 | Hitachi, Ltd. | Semiconductor device, manufacturing method thereof and mounting board |

| US6001671A (en) * | 1996-04-18 | 1999-12-14 | Tessera, Inc. | Methods for manufacturing a semiconductor package having a sacrificial layer |

| JP3638771B2 (ja) * | 1997-12-22 | 2005-04-13 | 沖電気工業株式会社 | 半導体装置 |

| DE60025720T2 (de) * | 1999-06-18 | 2006-11-09 | Hitachi Chemical Co., Ltd. | Klebstoff, klebstoffgegenstand, schaltungssubstrat für halbleitermontage mit einem klebstoff und eine halbleiteranordnung die diesen enthält |

| US6605875B2 (en) * | 1999-12-30 | 2003-08-12 | Intel Corporation | Integrated circuit die having bond pads near adjacent sides to allow stacking of dice without regard to dice size |

| US20020125568A1 (en) * | 2000-01-14 | 2002-09-12 | Tongbi Jiang | Method Of Fabricating Chip-Scale Packages And Resulting Structures |

| JP3752949B2 (ja) * | 2000-02-28 | 2006-03-08 | 日立化成工業株式会社 | 配線基板及び半導体装置 |

| JP2002040095A (ja) * | 2000-07-26 | 2002-02-06 | Nec Corp | 半導体装置及びその実装方法 |

| US6468471B1 (en) * | 2000-11-10 | 2002-10-22 | Gary K. Loda | System for, and method of, irradiating opposite sides of articles with optimal amounts of cumulative irradiation |

| US6753613B2 (en) * | 2002-03-13 | 2004-06-22 | Intel Corporation | Stacked dice standoffs |

| US7560821B2 (en) * | 2005-03-24 | 2009-07-14 | Sumitomo Bakelite Company, Ltd | Area mount type semiconductor device, and die bonding resin composition and encapsulating resin composition used for the same |

-

2006

- 2006-04-20 JP JP2006117074A patent/JP2007294488A/ja active Pending

-

2007

- 2007-04-17 KR KR1020070037328A patent/KR20070104236A/ko not_active Withdrawn

- 2007-04-18 US US11/736,926 patent/US8525355B2/en active Active

-

2012

- 2012-02-08 US US13/368,900 patent/US20120133056A1/en not_active Abandoned

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001196526A (ja) * | 2000-01-06 | 2001-07-19 | Seiko Epson Corp | マルチベアチップ実装体、マルチチップパッケージ、半導体装置、ならびに電子機器 |

| JP2003303919A (ja) * | 2002-04-10 | 2003-10-24 | Hitachi Ltd | 半導体装置及びその製造方法 |

| WO2004034433A2 (en) * | 2002-10-08 | 2004-04-22 | Chippac, Inc. | Semiconductor stacked multi-package module having inverted second package |

| JP2004179622A (ja) * | 2002-11-15 | 2004-06-24 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2004031946A (ja) * | 2003-06-05 | 2004-01-29 | Nec Electronics Corp | 半導体装置及びその製造方法 |

| JP2005268533A (ja) * | 2004-03-18 | 2005-09-29 | Shinko Electric Ind Co Ltd | 積層型半導体装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8664757B2 (en) | 2010-07-12 | 2014-03-04 | Samsung Electronics Co., Ltd. | High density chip stacked package, package-on-package and method of fabricating the same |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070246842A1 (en) | 2007-10-25 |

| KR20070104236A (ko) | 2007-10-25 |

| US20120133056A1 (en) | 2012-05-31 |

| US8525355B2 (en) | 2013-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5193898B2 (ja) | 半導体装置及び電子装置 | |

| TWI394503B (zh) | 佈線板及其製造方法 | |

| JP4058642B2 (ja) | 半導体装置 | |

| JP4361826B2 (ja) | 半導体装置 | |

| JP5106460B2 (ja) | 半導体装置及びその製造方法、並びに電子装置 | |

| JP5535494B2 (ja) | 半導体装置 | |

| US8169072B2 (en) | Semiconductor device, manufacturing method thereof, and electronic device | |

| JP4602208B2 (ja) | 電子部品実装構造体及びその製造方法 | |

| JP4070470B2 (ja) | 半導体装置用多層回路基板及びその製造方法並びに半導体装置 | |

| CN1239589A (zh) | 集成电路封装用的芯片级球形格栅阵列 | |

| JP2013069807A (ja) | 半導体パッケージ及びその製造方法 | |

| JP5025399B2 (ja) | 配線基板及びその製造方法 | |

| JP5357239B2 (ja) | 配線基板、半導体装置、及び配線基板の製造方法 | |

| WO2011024939A1 (ja) | 半導体装置およびその製造方法 | |

| KR20070104236A (ko) | 반도체 장치, 전자 장치, 및 반도체 장치의 제조 방법 | |

| CN110402492A (zh) | 柔性导电粘合 | |

| JP4110189B2 (ja) | 半導体パッケージ | |

| JP4403821B2 (ja) | パッケージ基板とその製造方法、及び半導体装置とその製造方法、ならびに積層構造体 | |

| JP2008091719A (ja) | 半導体装置 | |

| JP4647673B2 (ja) | 放熱型多穿孔半導体パッケージ | |

| JP5000877B2 (ja) | 半導体装置 | |

| JP4955259B2 (ja) | 配線基板、半導体装置、及び配線基板の製造方法 | |

| WO2000008685A1 (en) | Wiring substrate, method of manufacture thereof, and semiconductor device | |

| JP5772134B2 (ja) | 回路基板、その製造方法および半導体装置 | |

| JP3745705B2 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090223 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090223 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090929 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120131 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120807 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130312 |