JP2007019188A - 半導体集積回路装置およびその製造方法 - Google Patents

半導体集積回路装置およびその製造方法 Download PDFInfo

- Publication number

- JP2007019188A JP2007019188A JP2005197939A JP2005197939A JP2007019188A JP 2007019188 A JP2007019188 A JP 2007019188A JP 2005197939 A JP2005197939 A JP 2005197939A JP 2005197939 A JP2005197939 A JP 2005197939A JP 2007019188 A JP2007019188 A JP 2007019188A

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- wiring

- interlayer insulating

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 104

- 238000004519 manufacturing process Methods 0.000 title claims description 47

- 239000011229 interlayer Substances 0.000 claims abstract description 122

- 230000004888 barrier function Effects 0.000 claims abstract description 87

- 238000000034 method Methods 0.000 claims abstract description 79

- 239000010410 layer Substances 0.000 claims description 91

- 239000000758 substrate Substances 0.000 claims description 45

- 229910052751 metal Inorganic materials 0.000 claims description 40

- 239000002184 metal Substances 0.000 claims description 40

- 239000010949 copper Substances 0.000 claims description 31

- 229920001721 polyimide Polymers 0.000 claims description 19

- 239000009719 polyimide resin Substances 0.000 claims description 18

- 230000001681 protective effect Effects 0.000 claims description 18

- 238000005498 polishing Methods 0.000 claims description 12

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 10

- 229910052802 copper Inorganic materials 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 10

- 229910052782 aluminium Inorganic materials 0.000 claims description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 3

- 239000004642 Polyimide Substances 0.000 claims 1

- 239000011347 resin Substances 0.000 claims 1

- 229920005989 resin Polymers 0.000 claims 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 abstract description 8

- 238000009792 diffusion process Methods 0.000 abstract description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 51

- 238000005530 etching Methods 0.000 description 26

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 21

- 229910052814 silicon oxide Inorganic materials 0.000 description 21

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 16

- 239000000945 filler Substances 0.000 description 16

- 230000006870 function Effects 0.000 description 10

- 230000015654 memory Effects 0.000 description 10

- 238000004544 sputter deposition Methods 0.000 description 10

- 230000002950 deficient Effects 0.000 description 9

- 239000000463 material Substances 0.000 description 9

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 239000000523 sample Substances 0.000 description 7

- 239000003795 chemical substances by application Substances 0.000 description 6

- 238000005520 cutting process Methods 0.000 description 6

- 238000007747 plating Methods 0.000 description 6

- -1 tungsten nitride Chemical class 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 238000001312 dry etching Methods 0.000 description 5

- 239000010931 gold Substances 0.000 description 5

- 239000012535 impurity Substances 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 239000011810 insulating material Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 238000007689 inspection Methods 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 229910000679 solder Inorganic materials 0.000 description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 230000001678 irradiating effect Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000003870 refractory metal Substances 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 239000006117 anti-reflective coating Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000001579 optical reflectometry Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76832—Multiple layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76834—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers formation of thin insulating films on the sidewalls or on top of conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/525—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections

- H01L23/5256—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive

- H01L23/5258—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive the change of state resulting from the use of an external beam, e.g. laser beam or ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H01L23/53295—Stacked insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

- H10B99/10—Memory cells having a cross-point geometry

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Abstract

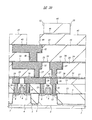

【解決手段】 第4層配線54およびヒューズ55の上層にバリア絶縁膜56と層間絶縁膜57とを堆積する。バリア絶縁膜56は、Cuの拡散を防ぐための絶縁膜であり、下層のバリア絶縁膜44と同じく、プラズマCVD法で堆積したSiCN膜で構成する。ヒューズ55を覆うバリア絶縁膜56の膜厚は、下層のバリア絶縁膜44よりも大きく、ヒューズ55の耐湿性が向上するようになっている。

【選択図】 図22

Description

本実施の形態は、例えば、4層Cu配線とヒューズとを有する半導体集積回路装置であり、その製造方法を図1〜図26を用いて工程順に説明する。

前記実施の形態1では、層間絶縁膜にビアホールを形成した後、配線溝を形成する場合について説明したが、本実施の形態では、層間絶縁膜に配線溝を形成した後、ビアホールを形成する場合について説明する。

2 素子分離溝

3 酸化シリコン膜

4 p型ウエル

5 n型ウエル

6 ゲート絶縁膜

7 ゲート電極

8 サイドウォールスペーサ

9 Coシリサイド膜

11 n型半導体領域(ソース、ドレイン)

12 p型半導体領域(ソース、ドレイン)

13 エッチングストッパ膜

14 絶縁膜

15 コンタクトホール

16 プラグ

17 絶縁膜(SiOC膜)

18 絶縁膜

19 第1層配線

20 配線溝

21、22 バリア絶縁膜

23 層間絶縁膜

24 絶縁膜

25 反射防止膜

26 フォトレジスト膜

27 ビアホール

28 埋め込み剤

30 反射防止膜

31 フォトレジスト膜

32 配線溝

33 第2層配線

34 バリア絶縁膜

35 層間絶縁膜

36 反射防止膜

37 フォトレジスト膜

38 ビアホール

39 埋め込み剤

40 反射防止膜

41 フォトレジスト膜

42 配線溝

43 第3層配線

44 バリア絶縁膜

45 層間絶縁膜

46 ストッパ膜

47 反射防止膜

48 フォトレジスト膜

49 ビアホール

50 埋め込み剤

51 フォトレジスト膜

52、53 配線溝

54 第4層配線

55 ヒューズ

56 バリア絶縁膜

57 層間絶縁膜

58 スルーホール

59 プラグ

60 最上層配線(第5層配線)

60B ボンディングパッド

61 表面保護膜

62 開口

63 ポリイミド樹脂膜

64 引き出し配線

65 ポリイミド樹脂膜

66 Au膜

67 半田バンプ

Qn:nチャネル型MISFET

Qp:pチャネル型MISFET

Claims (10)

- 半導体基板の主面上に形成された第1層間絶縁膜と、

前記第1層間絶縁膜に形成された第1配線溝の内部に埋め込まれた第1配線と、

前記第1配線上を覆う第1バリア絶縁膜を介して前記第1層間絶縁膜上に形成された第2層間絶縁膜と、

前記第2層間絶縁膜に形成された第2配線溝の内部に埋め込まれたヒューズと、

前記第2層間絶縁膜に形成された第3配線溝の内部に埋め込まれた第2配線と、

前記ヒューズ上および前記第2配線上を覆う第2バリア絶縁膜と、

前記第2バリア絶縁膜上に第1絶縁膜を介して形成された最上層配線と、

前記最上層配線上を覆う表面保護膜とを有し、

前記第2バリア絶縁膜の膜厚は、前記第1バリア絶縁膜の膜厚よりも大きく、

前記ヒューズの上部の前記第1絶縁膜および前記表面保護膜には、前記第2バリア絶縁膜の表面に達する第1開口が設けられていることを特徴とする半導体集積回路装置。 - 前記第1および第2配線と前記ヒューズとは、銅を主体とする金属膜で構成され、前記第1および第2バリア絶縁膜は、SiCN膜で構成されていることを特徴とする請求項1記載の半導体集積回路装置。

- 前記最上層配線は、アルミニウムを主体とする金属膜で構成されていることを特徴とする請求項1記載の半導体集積回路装置。

- 前記表面保護膜上に形成された第1ポリイミド樹脂膜と、前記第1ポリイミド樹脂膜上に形成され、前記最上層配線に電気的に接続された引き出し配線と、前記引き出し配線を覆う第2ポリイミド樹脂膜と、前記第2ポリイミド樹脂膜の一部から露出する前記引き出し配線上に形成された外部接続端子とをさらに有することを特徴とする請求項1記載の半導体集積回路装置。

- 前記引き出し配線は、銅を主体とする金属膜で構成されていることを特徴とする請求項4記載の半導体集積回路装置。

- 以下の工程を含む半導体集積回路装置の製造方法:

(a)半導体基板の主面上に第1層間絶縁膜に形成し、前記第1層間絶縁膜に第1配線溝を形成する工程、

(b)前記第1配線溝の内部を含む前記第1層間絶縁膜上に第1金属膜を形成した後、前記第1配線溝の外部の前記第1金属膜を化学的機械研磨法で除去することにより、前記第1配線溝の内部に前記第1金属膜からなる第1配線を形成する工程、

(c)前記第1配線の上部を含む前記第1層間絶縁膜上に第1バリア絶縁膜を形成する工程、

(d)前記第1バリア絶縁膜上に第2層間絶縁膜を形成し、前記第2層間絶縁膜に第2および第3配線溝を形成する工程、

(e)前記第2および第3配線溝の内部を含む前記第2層間絶縁膜上に第2金属膜を形成した後、前記第2および第3配線溝の外部の前記第2金属膜を化学的機械研磨法で除去することにより、前記第2配線溝の内部に前記第2金属膜からなるヒューズを形成し、前記第3配線溝の内部に前記第2金属膜からなる第2配線を形成する工程、

(f)前記第2配線および前記ヒューズの上部を含む前記第2層間絶縁膜上に、前記第1バリア絶縁膜よりも厚い膜厚を有する第2バリア絶縁膜を形成する工程、

(g)前記第2バリア絶縁膜上に第1絶縁膜を形成し、前記第1絶縁膜上に最上層配線を形成する工程、

(h)前記ヒューズの上部の前記第1絶縁膜および前記表面保護膜に、前記第2バリア絶縁膜の表面に達する第1開口を形成し、前記最上層配線の上部の前記第1絶縁膜および前記表面保護膜に、前記最上層配線に達する第2開口を形成する工程。 - 前記第1および第2配線と前記ヒューズとを銅を主体とする金属膜で構成し、前記第1および第2バリア絶縁膜をSiCN膜で構成することを特徴とする請求項6記載の半導体集積回路装置の製造方法。

- 前記最上層配線をアルミニウムを主体とする金属膜で構成することを特徴とする請求項6記載の半導体集積回路装置の製造方法。

- 前記工程(h)の後、さらに、

(i)前記最上層配線の上部を含む前記表面保護膜上に第1ポリイミド樹脂膜を形成した後、前記第1ポリイミド樹脂膜上に引き出し配線を形成し、前記引き出し配線と前記最上層配線とを電気的に接続する工程、

(j)前記引き出し配線の上部を含む前記第1ポリイミド樹脂膜上に第2ポリイミド樹脂膜を形成した後、前記第2ポリイミド樹脂膜の一部から露出する前記引き出し配線上に外部接続端子を形成する工程、

を含むことを特徴とする請求項6記載の半導体集積回路装置の製造方法。 - 前記引き出し配線を銅を主体とする金属膜で構成することを特徴とする請求項9記載の半導体集積回路装置の製造方法。

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005197939A JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

| US11/453,897 US7419901B2 (en) | 2005-07-06 | 2006-06-16 | Semiconductor device and a method of manufacturing the same |

| TW095122398A TW200707646A (en) | 2005-07-06 | 2006-06-22 | Semiconductor device and a method of manufacturing the same |

| CNB2006100957511A CN100573871C (zh) | 2005-07-06 | 2006-07-04 | 半导体器件及其制造方法 |

| US12/102,532 US7602040B2 (en) | 2005-07-06 | 2008-04-14 | Semiconductor device and a method of manufacturing the same |

| US12/564,043 US7968966B2 (en) | 2005-07-06 | 2009-09-21 | Semiconductor device with fuse and a method of manufacturing the same |

| US13/071,546 US8269309B2 (en) | 2005-07-06 | 2011-03-25 | Semiconductor device with a fuse formed by a damascene technique and a method of manufacturing the same |

| US13/597,129 US8686538B2 (en) | 2005-07-06 | 2012-08-28 | Semiconductor device with a fuse formed by a damascene technique and a method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005197939A JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007019188A true JP2007019188A (ja) | 2007-01-25 |

| JP2007019188A5 JP2007019188A5 (ja) | 2008-08-14 |

Family

ID=37597735

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005197939A Pending JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (5) | US7419901B2 (ja) |

| JP (1) | JP2007019188A (ja) |

| CN (1) | CN100573871C (ja) |

| TW (1) | TW200707646A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111446230A (zh) * | 2019-01-17 | 2020-07-24 | 三菱电机株式会社 | 半导体装置 |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007019188A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体集積回路装置およびその製造方法 |

| US7586132B2 (en) * | 2007-06-06 | 2009-09-08 | Micrel, Inc. | Power FET with low on-resistance using merged metal layers |

| US7956466B2 (en) | 2008-05-09 | 2011-06-07 | International Business Machines Corporation | Structure for interconnect structure containing various capping materials for electrical fuse and other related applications |

| US8772156B2 (en) * | 2008-05-09 | 2014-07-08 | International Business Machines Corporation | Methods of fabricating interconnect structures containing various capping materials for electrical fuse and other related applications |

| US7893520B2 (en) * | 2008-05-12 | 2011-02-22 | International Business Machines Corporation | Efficient interconnect structure for electrical fuse applications |

| KR101198758B1 (ko) * | 2009-11-25 | 2012-11-12 | 엘지이노텍 주식회사 | 수직구조 반도체 발광소자 및 그 제조방법 |

| US8530320B2 (en) * | 2011-06-08 | 2013-09-10 | International Business Machines Corporation | High-nitrogen content metal resistor and method of forming same |

| TWI555122B (zh) * | 2012-05-11 | 2016-10-21 | 聯華電子股份有限公司 | 半導體元件之內連線結構其製備方法 |

| US20130299993A1 (en) * | 2012-05-11 | 2013-11-14 | Hsin-Yu Chen | Interconnection of semiconductor device and fabrication method thereof |

| US9087841B2 (en) * | 2013-10-29 | 2015-07-21 | International Business Machines Corporation | Self-correcting power grid for semiconductor structures method |

| JP6448424B2 (ja) * | 2015-03-17 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US9455261B1 (en) * | 2015-07-10 | 2016-09-27 | Micron Technology, Inc. | Integrated structures |

| TWI590350B (zh) * | 2016-06-30 | 2017-07-01 | 欣興電子股份有限公司 | 線路重分佈結構的製造方法與線路重分佈結構單元 |

| KR102616489B1 (ko) | 2016-10-11 | 2023-12-20 | 삼성전자주식회사 | 반도체 장치 제조 방법 |

| US20190169841A1 (en) * | 2017-12-02 | 2019-06-06 | M-Fire Suppression, Inc. | Wild-fire protected shed for storage and protection of personal property during wild-fires |

| US20190169837A1 (en) * | 2017-12-02 | 2019-06-06 | M-Fire Suppression, Inc. | Wild-fire protected shed for storage and protection of personal property during wild-fires |

| CN110047799A (zh) * | 2019-04-28 | 2019-07-23 | 上海华虹宏力半导体制造有限公司 | 半导体器件的制造方法及半导体器件 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001085526A (ja) * | 1999-09-10 | 2001-03-30 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP2001274247A (ja) * | 2000-03-27 | 2001-10-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003017570A (ja) * | 2001-07-02 | 2003-01-17 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004221275A (ja) * | 2003-01-14 | 2004-08-05 | Nec Electronics Corp | 有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法。 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6291891B1 (en) * | 1998-01-13 | 2001-09-18 | Kabushiki Kaisha Toshiba | Semiconductor device manufacturing method and semiconductor device |

| US6111301A (en) * | 1998-04-24 | 2000-08-29 | International Business Machines Corporation | Interconnection with integrated corrosion stop |

| US6440833B1 (en) * | 2000-07-19 | 2002-08-27 | Taiwan Semiconductor Manufacturing Company | Method of protecting a copper pad structure during a fuse opening procedure |

| JP2002164428A (ja) * | 2000-11-29 | 2002-06-07 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP4523194B2 (ja) * | 2001-04-13 | 2010-08-11 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

| JP2003124307A (ja) | 2001-10-15 | 2003-04-25 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2003142485A (ja) * | 2001-11-01 | 2003-05-16 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP3588612B2 (ja) | 2002-02-19 | 2004-11-17 | 株式会社東芝 | 半導体装置 |

| US7067897B2 (en) * | 2002-02-19 | 2006-06-27 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US7042095B2 (en) * | 2002-03-29 | 2006-05-09 | Renesas Technology Corp. | Semiconductor device including an interconnect having copper as a main component |

| JP4250006B2 (ja) * | 2002-06-06 | 2009-04-08 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP3779243B2 (ja) * | 2002-07-31 | 2006-05-24 | 富士通株式会社 | 半導体装置及びその製造方法 |

| US7094683B2 (en) * | 2003-08-04 | 2006-08-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dual damascene method for ultra low K dielectrics |

| US7018917B2 (en) * | 2003-11-20 | 2006-03-28 | Asm International N.V. | Multilayer metallization |

| JP4673557B2 (ja) * | 2004-01-19 | 2011-04-20 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2007019188A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体集積回路装置およびその製造方法 |

-

2005

- 2005-07-06 JP JP2005197939A patent/JP2007019188A/ja active Pending

-

2006

- 2006-06-16 US US11/453,897 patent/US7419901B2/en active Active

- 2006-06-22 TW TW095122398A patent/TW200707646A/zh not_active IP Right Cessation

- 2006-07-04 CN CNB2006100957511A patent/CN100573871C/zh active Active

-

2008

- 2008-04-14 US US12/102,532 patent/US7602040B2/en active Active

-

2009

- 2009-09-21 US US12/564,043 patent/US7968966B2/en active Active

-

2011

- 2011-03-25 US US13/071,546 patent/US8269309B2/en not_active Expired - Fee Related

-

2012

- 2012-08-28 US US13/597,129 patent/US8686538B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001085526A (ja) * | 1999-09-10 | 2001-03-30 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP2001274247A (ja) * | 2000-03-27 | 2001-10-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003017570A (ja) * | 2001-07-02 | 2003-01-17 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004221275A (ja) * | 2003-01-14 | 2004-08-05 | Nec Electronics Corp | 有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法。 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111446230A (zh) * | 2019-01-17 | 2020-07-24 | 三菱电机株式会社 | 半导体装置 |

| CN111446230B (zh) * | 2019-01-17 | 2023-05-05 | 三菱电机株式会社 | 半导体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8269309B2 (en) | 2012-09-18 |

| TW200707646A (en) | 2007-02-16 |

| US20100013046A1 (en) | 2010-01-21 |

| US7968966B2 (en) | 2011-06-28 |

| US7419901B2 (en) | 2008-09-02 |

| US7602040B2 (en) | 2009-10-13 |

| TWI380404B (ja) | 2012-12-21 |

| CN1893076A (zh) | 2007-01-10 |

| US8686538B2 (en) | 2014-04-01 |

| CN100573871C (zh) | 2009-12-23 |

| US20110169128A1 (en) | 2011-07-14 |

| US20120319235A1 (en) | 2012-12-20 |

| US20080211103A1 (en) | 2008-09-04 |

| US20070026664A1 (en) | 2007-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11600522B2 (en) | Semiconductor device and a method of manufacturing the same | |

| US7602040B2 (en) | Semiconductor device and a method of manufacturing the same | |

| JP4891296B2 (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080627 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080627 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110804 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111122 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20111130 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20111222 |