JP2007019188A - 半導体集積回路装置およびその製造方法 - Google Patents

半導体集積回路装置およびその製造方法 Download PDFInfo

- Publication number

- JP2007019188A JP2007019188A JP2005197939A JP2005197939A JP2007019188A JP 2007019188 A JP2007019188 A JP 2007019188A JP 2005197939 A JP2005197939 A JP 2005197939A JP 2005197939 A JP2005197939 A JP 2005197939A JP 2007019188 A JP2007019188 A JP 2007019188A

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- wiring

- interlayer insulating

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

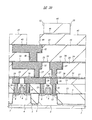

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76832—Multiple layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76834—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers formation of thin insulating films on the sidewalls or on top of conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/525—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections

- H01L23/5256—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive

- H01L23/5258—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body with adaptable interconnections comprising fuses, i.e. connections having their state changed from conductive to non-conductive the change of state resulting from the use of an external beam, e.g. laser beam or ion beam

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

- H01L23/53295—Stacked insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B99/00—Subject matter not provided for in other groups of this subclass

- H10B99/10—Memory cells having a cross-point geometry

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

Priority Applications (8)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005197939A JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

| US11/453,897 US7419901B2 (en) | 2005-07-06 | 2006-06-16 | Semiconductor device and a method of manufacturing the same |

| TW095122398A TW200707646A (en) | 2005-07-06 | 2006-06-22 | Semiconductor device and a method of manufacturing the same |

| CNB2006100957511A CN100573871C (zh) | 2005-07-06 | 2006-07-04 | 半导体器件及其制造方法 |

| US12/102,532 US7602040B2 (en) | 2005-07-06 | 2008-04-14 | Semiconductor device and a method of manufacturing the same |

| US12/564,043 US7968966B2 (en) | 2005-07-06 | 2009-09-21 | Semiconductor device with fuse and a method of manufacturing the same |

| US13/071,546 US8269309B2 (en) | 2005-07-06 | 2011-03-25 | Semiconductor device with a fuse formed by a damascene technique and a method of manufacturing the same |

| US13/597,129 US8686538B2 (en) | 2005-07-06 | 2012-08-28 | Semiconductor device with a fuse formed by a damascene technique and a method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005197939A JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007019188A true JP2007019188A (ja) | 2007-01-25 |

| JP2007019188A5 JP2007019188A5 (cg-RX-API-DMAC7.html) | 2008-08-14 |

Family

ID=37597735

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005197939A Pending JP2007019188A (ja) | 2005-07-06 | 2005-07-06 | 半導体集積回路装置およびその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (5) | US7419901B2 (cg-RX-API-DMAC7.html) |

| JP (1) | JP2007019188A (cg-RX-API-DMAC7.html) |

| CN (1) | CN100573871C (cg-RX-API-DMAC7.html) |

| TW (1) | TW200707646A (cg-RX-API-DMAC7.html) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111446230A (zh) * | 2019-01-17 | 2020-07-24 | 三菱电机株式会社 | 半导体装置 |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007019188A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体集積回路装置およびその製造方法 |

| US7586132B2 (en) * | 2007-06-06 | 2009-09-08 | Micrel, Inc. | Power FET with low on-resistance using merged metal layers |

| US7956466B2 (en) | 2008-05-09 | 2011-06-07 | International Business Machines Corporation | Structure for interconnect structure containing various capping materials for electrical fuse and other related applications |

| US8772156B2 (en) * | 2008-05-09 | 2014-07-08 | International Business Machines Corporation | Methods of fabricating interconnect structures containing various capping materials for electrical fuse and other related applications |

| US7893520B2 (en) * | 2008-05-12 | 2011-02-22 | International Business Machines Corporation | Efficient interconnect structure for electrical fuse applications |

| KR101198758B1 (ko) * | 2009-11-25 | 2012-11-12 | 엘지이노텍 주식회사 | 수직구조 반도체 발광소자 및 그 제조방법 |

| US8530320B2 (en) * | 2011-06-08 | 2013-09-10 | International Business Machines Corporation | High-nitrogen content metal resistor and method of forming same |

| TWI555122B (zh) * | 2012-05-11 | 2016-10-21 | 聯華電子股份有限公司 | 半導體元件之內連線結構其製備方法 |

| US20130299993A1 (en) * | 2012-05-11 | 2013-11-14 | Hsin-Yu Chen | Interconnection of semiconductor device and fabrication method thereof |

| US9087841B2 (en) * | 2013-10-29 | 2015-07-21 | International Business Machines Corporation | Self-correcting power grid for semiconductor structures method |

| JP6448424B2 (ja) * | 2015-03-17 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US9455261B1 (en) | 2015-07-10 | 2016-09-27 | Micron Technology, Inc. | Integrated structures |

| TWI590350B (zh) * | 2016-06-30 | 2017-07-01 | 欣興電子股份有限公司 | 線路重分佈結構的製造方法與線路重分佈結構單元 |

| KR102616489B1 (ko) | 2016-10-11 | 2023-12-20 | 삼성전자주식회사 | 반도체 장치 제조 방법 |

| US20190169841A1 (en) * | 2017-12-02 | 2019-06-06 | M-Fire Suppression, Inc. | Wild-fire protected shed for storage and protection of personal property during wild-fires |

| US20190169837A1 (en) * | 2017-12-02 | 2019-06-06 | M-Fire Suppression, Inc. | Wild-fire protected shed for storage and protection of personal property during wild-fires |

| CN110047799A (zh) * | 2019-04-28 | 2019-07-23 | 上海华虹宏力半导体制造有限公司 | 半导体器件的制造方法及半导体器件 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001085526A (ja) * | 1999-09-10 | 2001-03-30 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP2001274247A (ja) * | 2000-03-27 | 2001-10-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003017570A (ja) * | 2001-07-02 | 2003-01-17 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004221275A (ja) * | 2003-01-14 | 2004-08-05 | Nec Electronics Corp | 有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法。 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6291891B1 (en) * | 1998-01-13 | 2001-09-18 | Kabushiki Kaisha Toshiba | Semiconductor device manufacturing method and semiconductor device |

| US6111301A (en) * | 1998-04-24 | 2000-08-29 | International Business Machines Corporation | Interconnection with integrated corrosion stop |

| US6440833B1 (en) * | 2000-07-19 | 2002-08-27 | Taiwan Semiconductor Manufacturing Company | Method of protecting a copper pad structure during a fuse opening procedure |

| JP2002164428A (ja) * | 2000-11-29 | 2002-06-07 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP4523194B2 (ja) * | 2001-04-13 | 2010-08-11 | 富士通セミコンダクター株式会社 | 半導体装置とその製造方法 |

| JP2003124307A (ja) | 2001-10-15 | 2003-04-25 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2003142485A (ja) * | 2001-11-01 | 2003-05-16 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP3588612B2 (ja) | 2002-02-19 | 2004-11-17 | 株式会社東芝 | 半導体装置 |

| US7067897B2 (en) * | 2002-02-19 | 2006-06-27 | Kabushiki Kaisha Toshiba | Semiconductor device |

| US7042095B2 (en) * | 2002-03-29 | 2006-05-09 | Renesas Technology Corp. | Semiconductor device including an interconnect having copper as a main component |

| JP4250006B2 (ja) * | 2002-06-06 | 2009-04-08 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP3779243B2 (ja) * | 2002-07-31 | 2006-05-24 | 富士通株式会社 | 半導体装置及びその製造方法 |

| US7094683B2 (en) * | 2003-08-04 | 2006-08-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Dual damascene method for ultra low K dielectrics |

| US7018917B2 (en) * | 2003-11-20 | 2006-03-28 | Asm International N.V. | Multilayer metallization |

| JP4673557B2 (ja) * | 2004-01-19 | 2011-04-20 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2007019188A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体集積回路装置およびその製造方法 |

-

2005

- 2005-07-06 JP JP2005197939A patent/JP2007019188A/ja active Pending

-

2006

- 2006-06-16 US US11/453,897 patent/US7419901B2/en active Active

- 2006-06-22 TW TW095122398A patent/TW200707646A/zh not_active IP Right Cessation

- 2006-07-04 CN CNB2006100957511A patent/CN100573871C/zh active Active

-

2008

- 2008-04-14 US US12/102,532 patent/US7602040B2/en active Active

-

2009

- 2009-09-21 US US12/564,043 patent/US7968966B2/en active Active

-

2011

- 2011-03-25 US US13/071,546 patent/US8269309B2/en not_active Expired - Fee Related

-

2012

- 2012-08-28 US US13/597,129 patent/US8686538B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001085526A (ja) * | 1999-09-10 | 2001-03-30 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP2001274247A (ja) * | 2000-03-27 | 2001-10-05 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2003017570A (ja) * | 2001-07-02 | 2003-01-17 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2004221275A (ja) * | 2003-01-14 | 2004-08-05 | Nec Electronics Corp | 有機絶縁膜及びその製造方法及び有機絶縁膜を用いた半導体装置及びその製造方法。 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111446230A (zh) * | 2019-01-17 | 2020-07-24 | 三菱电机株式会社 | 半导体装置 |

| CN111446230B (zh) * | 2019-01-17 | 2023-05-05 | 三菱电机株式会社 | 半导体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20120319235A1 (en) | 2012-12-20 |

| TW200707646A (en) | 2007-02-16 |

| TWI380404B (cg-RX-API-DMAC7.html) | 2012-12-21 |

| US20110169128A1 (en) | 2011-07-14 |

| US7968966B2 (en) | 2011-06-28 |

| US20080211103A1 (en) | 2008-09-04 |

| US8686538B2 (en) | 2014-04-01 |

| US20070026664A1 (en) | 2007-02-01 |

| US20100013046A1 (en) | 2010-01-21 |

| CN100573871C (zh) | 2009-12-23 |

| US8269309B2 (en) | 2012-09-18 |

| US7419901B2 (en) | 2008-09-02 |

| CN1893076A (zh) | 2007-01-10 |

| US7602040B2 (en) | 2009-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11600522B2 (en) | Semiconductor device and a method of manufacturing the same | |

| US7602040B2 (en) | Semiconductor device and a method of manufacturing the same | |

| JP4891296B2 (ja) | 半導体集積回路装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080627 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080627 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110804 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111122 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20111130 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20111222 |