JP2006503439A - キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法 - Google Patents

キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法 Download PDFInfo

- Publication number

- JP2006503439A JP2006503439A JP2004545696A JP2004545696A JP2006503439A JP 2006503439 A JP2006503439 A JP 2006503439A JP 2004545696 A JP2004545696 A JP 2004545696A JP 2004545696 A JP2004545696 A JP 2004545696A JP 2006503439 A JP2006503439 A JP 2006503439A

- Authority

- JP

- Japan

- Prior art keywords

- region

- insulating

- electrode

- transistor

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 title claims abstract description 113

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 46

- 239000000758 substrate Substances 0.000 claims abstract description 18

- 238000000034 method Methods 0.000 claims description 44

- 239000004065 semiconductor Substances 0.000 claims description 44

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 42

- 230000005669 field effect Effects 0.000 claims description 28

- 239000000463 material Substances 0.000 claims description 28

- 125000006850 spacer group Chemical group 0.000 claims description 26

- 235000012239 silicon dioxide Nutrition 0.000 claims description 21

- 239000000377 silicon dioxide Substances 0.000 claims description 21

- 229910021332 silicide Inorganic materials 0.000 claims description 17

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims description 17

- 229910052751 metal Inorganic materials 0.000 claims description 14

- 239000002184 metal Substances 0.000 claims description 14

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 12

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 12

- 229910052710 silicon Inorganic materials 0.000 claims description 11

- 239000010703 silicon Substances 0.000 claims description 11

- 238000000059 patterning Methods 0.000 claims description 10

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 10

- 238000000407 epitaxy Methods 0.000 claims description 7

- 238000009413 insulation Methods 0.000 claims description 7

- 239000013078 crystal Substances 0.000 claims description 6

- 239000012777 electrically insulating material Substances 0.000 claims description 6

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 claims description 5

- 239000002019 doping agent Substances 0.000 claims description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 4

- 230000015572 biosynthetic process Effects 0.000 claims description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims 1

- 229910052701 rubidium Inorganic materials 0.000 claims 1

- IGLNJRXAVVLDKE-UHFFFAOYSA-N rubidium atom Chemical compound [Rb] IGLNJRXAVVLDKE-UHFFFAOYSA-N 0.000 claims 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims 1

- 229920002120 photoresistant polymer Polymers 0.000 description 17

- 238000011161 development Methods 0.000 description 16

- 230000018109 developmental process Effects 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 230000008569 process Effects 0.000 description 7

- 238000005530 etching Methods 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- 229920005591 polysilicon Polymers 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 5

- 238000005468 ion implantation Methods 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229910052454 barium strontium titanate Inorganic materials 0.000 description 3

- 239000003989 dielectric material Substances 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000000609 electron-beam lithography Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 125000004437 phosphorous atom Chemical group 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Abstract

Description

COX=εr ε0/tphys=34.5fF/μm2

である。ただし、tphysは、実施例では1nmになる酸化物厚みである。その結果、メモリ容量が必要とする面AMEM、すなわち:

AMEM=CMEM/COX=0.29μm2

が生じる。

COX=3.9ε0/tox=19fF/μm2

の面につき、1容量が生じる。ただし、1.8nmに等しいtoxは、電気的に有効な酸化物厚みを表しており、ε0は、自由空間での誘電率を表している。金属ゲートを使用する場合は、電気的に有効な酸化物厚みは、ゲート空乏が存在しなくなるので、約0.4nmだけ少なくなる。その結果、1面毎の容量は、

COX=3.9ε0/tox=24fF/μm2

に上昇する。

Ceff=Cs+CGS(M2)

ただし、Csは、キャパシタCsの容量であり、CGSは、トランジスタM2のゲート−ソース容量である。この製造方法によると、ゲート酸化物およびキャパシタ誘電体を同じ誘電性層に生成し、この層がどこでも同じ厚みであるならば、メモリキャパシタCsとトランジスタM2との1面毎の容量は、例えば同じ大きさである。

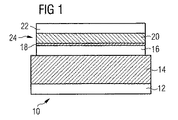

10 SOI基板

12 担体基板

14 絶縁層

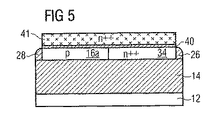

16 半導体層

16a トランジスタ部

16b キャパシタ部

18 二酸化シリコン層

20 窒化シリコン層

22 フォトレジスト層

24 積層

26,28 酸化物角取り部

30,32 フォトレジスト層

33 埋め込み

34 下部電極領域

40 二酸化シリコン層

41 ポリシリコン層

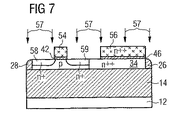

42 ゲート酸化物

46 誘電体

50a、50b フォトレジスト層領域

54 ゲート電極

56 被覆電極

57 埋め込み

58,59 LDD領域

60〜66 スペーサ

70〜76 エピタキシャル領域

78 埋め込み

80,82 ソース/ドレイン領域

84 チャネル領域

90〜96 ケイ化物領域

100 パッシベーション層

102〜136 接続部

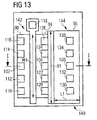

140 トランジスタ−キャパシタ構造

142 電界効果トランジスタ

144 キャパシタ

W1,W2 トランジスタ幅

L1,L2 長さ

B1,B2 幅

A 面

F 最小形状

150 メモリセル

152 電界効果トランジスタ

154 キャパシタ

200 メモリセル

M1〜M3 トランジスタ

Cs キャパシタ

BL1 書き込みビット線

BL2 読み出しビット線

RWL 読み出しワード線

WWL 書き込みワード線

X メモリ節点

VDD 操作電位

VSS 接地電位

Claims (15)

- 電気的に絶縁性の絶縁領域と、少なくとも1つの連続した領域とを有する集積回路構造(140)であって、

上記連続した領域は、キャパシタ(144)を形成しているとともに、上記絶縁領域に近接した電極領域(34)と、

誘電体領域(46)と、

絶縁領域から離れた電極領域(56)とをこの順で有しており、

上記絶縁領域が、平面に配置された絶縁層(14)の一部であり、

上記集積回路構造(140)の上記キャパシタ(144)と、少なくとも1つの能動素子(142)とが、上記絶縁層(14)に対して同じ側に配置されており、

上記絶縁領域に近接した電極領域(34)と、上記素子(142)の活性領域(84)とが、絶縁層(14)の配置されている平面と平行な平面に配置されている、集積回路構造(140)。 - 少なくとも1つの電界効果トランジスタ(142)にて特徴付けされており、

この電界効果トランジスタ(142)のチャネル領域(84)が、活性領域であり、上記チャネル領域(84)が、ドープまたは非ドープされていることが好ましく、

および/または、電界効果トランジスタ(142)の制御電極(54)が、絶縁領域から離れた電極領域(56)と同じ材料および/または同じドーパント濃度の材料を含み、

および/または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)と同じ材料および/または同じ厚みを有する材料を含み、

および/または、電界効果トランジスタ(142)の制御電極絶縁領域(42)が、誘電体領域(46)とは異なる材料および/または異なる厚みを有する材料を含む請求項1に記載の回路構造(140)。 - 上記電界効果トランジスタ(122)が、プレーナ型の電界効果トランジスタであり、

および/または、上記トランジスタが、補助端子領域(58,59)を含み、

これらの補助端子領域は、端子領域(80,82)と同じ導電型ではあるが少なくとも1桁だけ小さいドーパント濃度にドーピングされており、

および/または、上記トランジスタが、補助ドーピング領域を備え、これらの補助ドーピング領域は、端子領域(80,82)および/または補助端子領域(58,59)に近接して配置されており、端子領域(80,82)および/または補助端子領域(58,59)とは異なる導電性型のドーピングを有し、

および/または、上記制御電極(54)が、金属半導体組成物、特に、ケイ化物領域(92)を含む領域に隣接している、請求項2に記載の回路構造(140)。 - トランジスタ(142)の1つの端子領域(80,82)またはトランジスタ(142)の両方の端子領域(80,82)が、絶縁層(14)に隣接し、

および/または、少なくとも1つの端子領域(80,82)が、金属半導体組成物を含む領域、好ましくはケイ化物領域(90,96)と隣接し、

および/または、少なくとも1つの端子領域(80,82)の絶縁領域から離れた境界面が、活性領域(84)よりも、絶縁層(14)から離れており、または、

および/または、絶縁領域から離れた少なくとも一つの端子領域(80,82)の境界面が、活性領域(84)よりも、絶縁層(14)から離れており、

または、絶縁領域から離れた少なくとも一つの端子領域(80,82)の境界面が、活性領域(84)が絶縁領域から離れた活性領域(84)の境界面よりも絶縁層(14)に近接して配置されている、請求項2または3に記載の回路構造(140)。

少なくとも1つの端子領域(80,82)の絶縁領域から離れた境界面が、活性領域(84)の絶縁領域から離れた境界面よりも、絶縁層(14)の近くに配置されている、請求項2または3に記載の回路構造(140)。 - スペーサ(60,62)が、制御電極(54)の両側に配置されており、これらのスペーサは、制御電極(54)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、これらのスペーサは、制御電極(54)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、

および/または、スペーサ(64,66)が、絶縁領域から離れた電極領域(56)の少なくとも一方側に配置されており、このスペーサは、上記絶縁領域から離れた上記電極領域(56)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンを含み、または、このスペーサは、上記絶縁領域から離れた上記電極領域(56)とは異なる材料、好ましくは二酸化シリコンまたは窒化シリコンからなり、

および/または、制御電極(54)に配置されたスペーサ(62a)と、絶縁領域から離れた電極領域(56)に配置されたスペーサ(64a)とが相互に接触する、請求項2から4のいずれか1項に記載の回路構造(140)。 - 上記電界効果トランジスタ(142)の端子領域(82)と、キャパシタ(144)の絶縁領域に近接した電極領域(34)とが、相互に隣接し、境界で導電性接続されており、

および/または、絶縁領域に近接した電極領域(34)に隣接する上記トランジスタ(152)の端子領域(59a)が、金属半導体組成物を含む領域、特に、ケイ化物領域に隣接せず、

および/または、他の端子領域(80a)が、金属半導体組成物を含む領域(70a)に隣接する、請求項2から5のいずれか1項に記載の回路構造(140)。 - 端子領域(82)に隣接する、絶縁領域に近接した電極領域(34)の側面が、上記側面を横断するように配置されている、絶縁領域に近接した電極領域(34)の側面よりも長く、好ましくは少なくとも2倍または少なくとも5倍は長く、

トランジスタ(142)が、好ましくはトランジスタ幅(W1)を有し、このトランジスタ幅は、最小形状(F)の倍数であり、好ましくは3倍または5倍を上回り、

または、端子領域(82)に隣接する、絶縁領域に近接した電極領域(34)の側面を横断するように配置されている、絶縁領域に近接した電極領域(34)の側面が、端子領域(82)に隣接している側面よりも長く、好ましくは少なくとも2倍または少なくとも5倍は長く、

トランジスタ(152)が、好ましくはトランジスタ幅(W2)を有しており、

このトランジスタ幅は、最小形状(F)の3倍未満であり、好ましくは最小形状(F)の2倍未満である、請求項6に記載の回路構造(140)。 - 上記絶縁領域に近接した上記電極領域(34)が、単結晶領域、好ましくはドープされた半導体領域であり、

および/または、上記絶縁領域に近接した上記電極領域(34)および/または活性領域(84)が、100nm未満、または、50nm未満の厚みを有しており、

および/または、上記活性領域(84)が、単結晶領域、好ましくはドープまたは非ドープされた半導体領域であり、

および/または、上記絶縁層(14)が、一方の側面で、担体基板(12)、好ましくは担体基板に隣接し、この担体基板は、半導体材料を含むんでいるか、または、半導体材料、特にシリコンまたは単結晶シリコンからなり、

および/または、上記絶縁層(14)が、他方の側面で、上記絶縁領域に近接した上記電極領域(34)に隣接し、

および/または、境界面が、好ましくは2つの相互に平行な面に完全に含まれており、

および/または、絶縁層(14)が、電気的に絶縁性のある材料、好ましくは酸化物、特に二酸化シリコンを含み、

または、電気的に絶縁性のある材料、好ましくは酸化物、特に二酸化シリコンからなり、

および/または、能動素子(142)が、トランジスタ、好ましくは電界効果トランジスタ、特にプレーナ型の電界効果トランジスタである、請求項1〜7のいずれか1項に記載の回路構造(140)。 - 上記誘電性領域(46)が、二酸化シリコンを含み、または、二酸化シリコンからなり、

および/または、上記誘電性領域(46)が、4以上または10以上または50以上の誘電定数を有する材料からなり、

および/または、上記絶縁領域から離れた上記電極領域(56)が、シリコン、好ましくは多結晶シリコンを含み、または、シリコン、好ましくは多結晶シリコンからなり、

および/または、上記絶縁領域から離れた上記電極領域(56)が、金属を含み、または、金属からなり、

および/または、上記絶縁領域から離れた上記電極領域(56)が、低インピーダンス材料、好ましくは窒化チタン、窒化タンタル、ルビジウムまたは高ドープしたシリコンゲルマニウムを含み、

および/または、上記絶縁領域から離れた上記電極領域(56)が、金属半導体組成物を含む領域、特にケイ化物領域(96)に隣接する、上記請求項1〜8のいずれか1項に記載の回路構造(140)。 - 上記回路構造が、少なくとも1つの処理器、好ましくはマイクロ処理器を含み、

および/または、上記キャパシタ(154)と能動素子(152)とが、メモリセル(150)を、特に、ダイナミックRAMメモリユニットに形成し、

および/または、メモリセルが、キャパシタ(152)およびただ1つのトランジスタ(152)、または、キャパシタ(Cs)および複数のトランジスタ(M1〜M3)、好ましくは3つのトランジスタ(M1〜M3)のどちらかを含む、請求項1〜9のいずれかに記載の回路構造(140)。 - キャパシタ(144)を有する集積回路構造(140)、特に上記請求項1から10のいずれか1項に記載の回路構造(140)の製造方法において、

規定の順序に制限されることなく、

電気的に絶縁性の材料から成る絶縁層(14)と、半導体層(16)とを含む基板(10)を用意し、

キャパシタ用の少なくとも1つの電極領域(34)を形成するため、および、トランジスタ(142)用の少なくとも1つの活性領域(84)を形成するために、半導体層(16)をパターン化し、

半導体層(16)をパターン化した後、少なくとも1つの誘電性層(42、46)を生成し、

誘電性層(42,46)を生成した後、電極層(41)を生成し、

上記電極層(41)の絶縁領域から離してキャパシタ(144)の電極(56)を形成する方法工程を実施する方法。 - パターン化の前に半導体層(16)に少なくとも1つの補助層(18,20)、好ましくは窒化シリコン層(20)および/または酸化物層(18)を形成する工程であって、補助層(20)が、半導体層(16)のパターン化中に、好ましくはハードマスクの機能を果たすようになっており、

および/または、好ましくは誘電性層(42,46)の生成前に、トランジスタ(142)のチャネル領域(84)をドーピングし、

角取り酸化物(26,28)を形成するために、好ましくは電極層(41)を形成する前に、熱酸化し、

および/または、好ましくは誘電性層(42,44,46)を生成する前に、上記絶縁領域に近接した電極(34)をドーピングし、

および/または、トランジスタ(122)の活性領域(84)に、誘電性層と同時に誘電性層(42,46)を生成し、

および/または、上記絶縁領域から離れた電極領域(56)の形成と同時にトランジスタ(142)の制御電極(54)を形成することを特徴とする、請求項11に記載の方法。 - 好ましくはトランジスタ(142)の制御電極(54)をパターン化した後に、トランジスタ(142)の端子領域(80,82)よりも低いドーパント濃度を有する補助端子領域(58,59)を形成し、

および/または、好ましくは制御電極(54)をパターン化する前に、補助ドーピング領域を形成し、

トランジスタ(142)の制御電極(54)をパターン化した後に、更なる補助層(60から66)、好ましくは窒化シリコン層または二酸化シリコン層、特にTEOS層を形成し、

および/または、更なる補助層(60〜66)を異方性エッチングすることを特徴とする、請求項11または12に記載の方法。 - 上記絶縁領域から離れた電極領域(56)を形成した後、および/または、トランジスタ(142)の制御電極(54)をパターン化した後、半導体材料(16)からなる露出領域に、選択的エピタキシーを行い、

および/または、上記絶縁領域から離れた電極領域(56)を形成した後、および/または制御電極(54)をパターン化した後、および、好ましくはエピタキシーの後、トランジスタ(122)の端子領域(70、72)をドーピングすることを特徴とする、請求項11から13のいずれか1項に記載の方法。 - 電極層(54)、および/または、露出半導体領域(16)に、金属半導体組成物、特に、ケイ化物を選択的に形成することを特徴とする、請求項11から14のいずれか1項に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE10248723A DE10248723A1 (de) | 2002-10-18 | 2002-10-18 | Integrierte Schaltungsanordnung mit Kondensatoren und mit vorzugsweise planaren Transistoren und Herstellungsverfahren |

| PCT/DE2003/003354 WO2004038802A2 (de) | 2002-10-18 | 2003-10-10 | Integrierte schaltungsanordnung mit kondensatoren und mit vorzugsweise planaren transistoren und herstellungsverfahren |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006503439A true JP2006503439A (ja) | 2006-01-26 |

| JP2006503439A5 JP2006503439A5 (ja) | 2009-12-24 |

Family

ID=32087020

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004545696A Pending JP2006503439A (ja) | 2002-10-18 | 2003-10-10 | キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7173302B2 (ja) |

| EP (1) | EP1552561B1 (ja) |

| JP (1) | JP2006503439A (ja) |

| KR (1) | KR100757531B1 (ja) |

| CN (1) | CN100557803C (ja) |

| DE (2) | DE10248723A1 (ja) |

| TW (1) | TWI274417B (ja) |

| WO (1) | WO2004038802A2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010129980A (ja) * | 2008-12-01 | 2010-06-10 | Fujitsu Microelectronics Ltd | 半導体装置の製造方法 |

| JP2012015499A (ja) * | 2010-06-04 | 2012-01-19 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2021503717A (ja) * | 2017-11-16 | 2021-02-12 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | テクスチャ形成されたイリジウム底部電極を有する酸化ハフニウムおよび酸化ジルコニウムベースの強誘電性デバイス |

| WO2023058594A1 (ja) * | 2021-10-08 | 2023-04-13 | 株式会社村田製作所 | 電子素子、および回路装置 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040097027A1 (en) * | 2002-11-14 | 2004-05-20 | Won-Kyu Park | Method for manufacturing semiconductor device |

| FR2872958B1 (fr) | 2004-07-12 | 2008-05-02 | Commissariat Energie Atomique | Procede de fabrication d'un film mince structure et film mince obtenu par un tel procede |

| FR2879020B1 (fr) * | 2004-12-08 | 2007-05-04 | Commissariat Energie Atomique | Procede d'isolation de motifs formes dans un film mince en materiau semi-conducteur oxydable |

| US7915681B2 (en) * | 2007-06-18 | 2011-03-29 | Infineon Technologies Ag | Transistor with reduced charge carrier mobility |

| KR101017809B1 (ko) | 2008-03-13 | 2011-02-28 | 주식회사 하이닉스반도체 | 반도체 소자 및 그 제조 방법 |

| US8659066B2 (en) | 2012-01-06 | 2014-02-25 | International Business Machines Corporation | Integrated circuit with a thin body field effect transistor and capacitor |

| WO2015015700A1 (ja) * | 2013-08-02 | 2015-02-05 | シャープ株式会社 | 放射線検出用半導体装置 |

| US10418364B2 (en) * | 2016-08-31 | 2019-09-17 | Globalfoundries Inc. | Semiconductor device structure with self-aligned capacitor device |

| US9792958B1 (en) * | 2017-02-16 | 2017-10-17 | Micron Technology, Inc. | Active boundary quilt architecture memory |

| US10600778B2 (en) | 2017-11-16 | 2020-03-24 | International Business Machines Corporation | Method and apparatus of forming high voltage varactor and vertical transistor on a substrate |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326556A (ja) * | 1992-05-18 | 1993-12-10 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JPH08125034A (ja) * | 1993-12-03 | 1996-05-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH08335702A (ja) * | 1995-06-06 | 1996-12-17 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2000501237A (ja) * | 1995-11-30 | 2000-02-02 | シーメンス アクチエンゲゼルシヤフト | 少なくとも1個のmosトランジスタを有する集積回路装置の製造方法 |

| JP2002134755A (ja) * | 2000-10-25 | 2002-05-10 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57176757A (en) * | 1981-04-22 | 1982-10-30 | Nec Corp | Semiconductor device |

| JPS61113271A (ja) * | 1984-11-08 | 1986-05-31 | Matsushita Electronics Corp | 半導体記憶素子 |

| JPS62259466A (ja) * | 1986-05-02 | 1987-11-11 | Sony Corp | メモリ装置 |

| US4753896A (en) | 1986-11-21 | 1988-06-28 | Texas Instruments Incorporated | Sidewall channel stop process |

| JPH07335904A (ja) * | 1994-06-14 | 1995-12-22 | Semiconductor Energy Lab Co Ltd | 薄膜半導体集積回路 |

| JP3107691B2 (ja) * | 1993-12-03 | 2000-11-13 | 株式会社東芝 | 半導体記憶装置及びその製造方法 |

| JP3312083B2 (ja) | 1994-06-13 | 2002-08-05 | 株式会社半導体エネルギー研究所 | 表示装置 |

| DE59707274D1 (de) * | 1996-09-27 | 2002-06-20 | Infineon Technologies Ag | Integrierte CMOS-Schaltungsanordnung und Verfahren zu deren Herstellung |

| JP4147594B2 (ja) * | 1997-01-29 | 2008-09-10 | セイコーエプソン株式会社 | アクティブマトリクス基板、液晶表示装置および電子機器 |

| US6294420B1 (en) * | 1997-01-31 | 2001-09-25 | Texas Instruments Incorporated | Integrated circuit capacitor |

| US6133075A (en) * | 1997-04-25 | 2000-10-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of fabricating the same |

| JP2001051292A (ja) | 1998-06-12 | 2001-02-23 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体表示装置 |

| US6140162A (en) * | 1998-06-19 | 2000-10-31 | Lg Electronics Inc. | Reduction of masking and doping steps in a method of fabricating a liquid crystal display |

| JP2000022160A (ja) | 1998-07-06 | 2000-01-21 | Hitachi Ltd | 半導体集積回路及びその製造方法 |

| JP3399432B2 (ja) * | 1999-02-26 | 2003-04-21 | セイコーエプソン株式会社 | 電気光学装置の製造方法及び電気光学装置 |

| JP4963750B2 (ja) * | 2000-08-10 | 2012-06-27 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

-

2002

- 2002-10-18 DE DE10248723A patent/DE10248723A1/de not_active Ceased

-

2003

- 2003-09-22 TW TW092126126A patent/TWI274417B/zh not_active IP Right Cessation

- 2003-10-10 DE DE50312210T patent/DE50312210D1/de not_active Expired - Lifetime

- 2003-10-10 EP EP03757707A patent/EP1552561B1/de not_active Expired - Lifetime

- 2003-10-10 US US10/531,493 patent/US7173302B2/en not_active Expired - Lifetime

- 2003-10-10 KR KR1020057006707A patent/KR100757531B1/ko not_active IP Right Cessation

- 2003-10-10 JP JP2004545696A patent/JP2006503439A/ja active Pending

- 2003-10-10 WO PCT/DE2003/003354 patent/WO2004038802A2/de active Application Filing

- 2003-10-10 CN CNB2003801016685A patent/CN100557803C/zh not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05326556A (ja) * | 1992-05-18 | 1993-12-10 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JPH08125034A (ja) * | 1993-12-03 | 1996-05-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JPH08335702A (ja) * | 1995-06-06 | 1996-12-17 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2000501237A (ja) * | 1995-11-30 | 2000-02-02 | シーメンス アクチエンゲゼルシヤフト | 少なくとも1個のmosトランジスタを有する集積回路装置の製造方法 |

| JP2002134755A (ja) * | 2000-10-25 | 2002-05-10 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010129980A (ja) * | 2008-12-01 | 2010-06-10 | Fujitsu Microelectronics Ltd | 半導体装置の製造方法 |

| JP2012015499A (ja) * | 2010-06-04 | 2012-01-19 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2021503717A (ja) * | 2017-11-16 | 2021-02-12 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | テクスチャ形成されたイリジウム底部電極を有する酸化ハフニウムおよび酸化ジルコニウムベースの強誘電性デバイス |

| JP7177574B2 (ja) | 2017-11-16 | 2022-11-24 | インターナショナル・ビジネス・マシーンズ・コーポレーション | テクスチャ形成されたイリジウム底部電極を有する酸化ハフニウムおよび酸化ジルコニウムベースの強誘電性デバイス |

| WO2023058594A1 (ja) * | 2021-10-08 | 2023-04-13 | 株式会社村田製作所 | 電子素子、および回路装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI274417B (en) | 2007-02-21 |

| DE50312210D1 (de) | 2010-01-21 |

| WO2004038802A2 (de) | 2004-05-06 |

| EP1552561B1 (de) | 2009-12-09 |

| WO2004038802A3 (de) | 2004-09-10 |

| CN1706045A (zh) | 2005-12-07 |

| US20060022302A1 (en) | 2006-02-02 |

| KR20050053780A (ko) | 2005-06-08 |

| EP1552561A2 (de) | 2005-07-13 |

| US7173302B2 (en) | 2007-02-06 |

| TW200408114A (en) | 2004-05-16 |

| CN100557803C (zh) | 2009-11-04 |

| KR100757531B1 (ko) | 2007-09-11 |

| DE10248723A1 (de) | 2004-05-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7682896B2 (en) | Trench metal-insulator-metal (MIM) capacitors integrated with middle-of-line metal contacts, and method of fabricating same | |

| JP4598531B2 (ja) | キャパシタを含んだ集積回路構造およびその製造方法 | |

| US5780338A (en) | Method for manufacturing crown-shaped capacitors for dynamic random access memory integrated circuits | |

| KR100547227B1 (ko) | 신규한 디램 액세스 트랜지스터 | |

| US6534807B2 (en) | Local interconnect junction on insulator (JOI) structure | |

| US6022781A (en) | Method for fabricating a MOSFET with raised STI isolation self-aligned to the gate stack | |

| US6365452B1 (en) | DRAM cell having a vertical transistor and a capacitor formed on the sidewalls of a trench isolation | |

| US7193262B2 (en) | Low-cost deep trench decoupling capacitor device and process of manufacture | |

| EP0562207B1 (en) | Method of forming thin film pseudo-planar PFET devices and structures resulting therefrom | |

| US6235574B1 (en) | High performance DRAM and method of manufacture | |

| US7915691B2 (en) | High density SRAM cell with hybrid devices | |

| US6251726B1 (en) | Method for making an enlarged DRAM capacitor using an additional polysilicon plug as a center pillar | |

| JPH06151772A (ja) | 二重垂直チャネルを有するsram及びその製造方法 | |

| US20070241335A1 (en) | Methods of fabricating semiconductor integrated circuits using selective epitaxial growth and partial planarization techniques and semiconductor integrated circuits fabricated thereby | |

| US6605838B1 (en) | Process flow for thick isolation collar with reduced length | |

| US7560382B2 (en) | Embedded interconnects, and methods for forming same | |

| JP2006503439A (ja) | キャパシタと好ましくはプレーナ型のトランジスタとを有する集積回路構造およびその製造方法 | |

| US6436744B1 (en) | Method and structure for creating high density buried contact for use with SOI processes for high performance logic | |

| US6441456B1 (en) | Semiconductor device and a process for manufacturing the same | |

| KR100360786B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| TWI774102B (zh) | 整合組件及形成整合組件之方法 | |

| KR100190017B1 (ko) | 스태틱 랜덤 억세스 메모리 소자 및 그 제조방법 | |

| JP4031777B2 (ja) | 半導体装置 | |

| US20090278185A1 (en) | Device structures for a memory cell of a non-volatile random access memory and design structures for a non-volatile random access memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090217 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090513 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090630 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20091028 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20091110 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20091204 |