JP2005257366A - 半導体回路装置及び半導体回路に関するスキャンテスト方法 - Google Patents

半導体回路装置及び半導体回路に関するスキャンテスト方法 Download PDFInfo

- Publication number

- JP2005257366A JP2005257366A JP2004066997A JP2004066997A JP2005257366A JP 2005257366 A JP2005257366 A JP 2005257366A JP 2004066997 A JP2004066997 A JP 2004066997A JP 2004066997 A JP2004066997 A JP 2004066997A JP 2005257366 A JP2005257366 A JP 2005257366A

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- flip

- macro cell

- scan

- circuit unit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 26

- 238000010998 test method Methods 0.000 title claims description 8

- 238000012360 testing method Methods 0.000 claims abstract description 87

- 238000012545 processing Methods 0.000 claims description 17

- 230000007547 defect Effects 0.000 claims description 2

- 238000013461 design Methods 0.000 abstract description 16

- 238000010586 diagram Methods 0.000 description 8

- 238000001514 detection method Methods 0.000 description 5

- 230000007704 transition Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 3

- 238000011990 functional testing Methods 0.000 description 2

- 238000005352 clarification Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000015654 memory Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/18—Address generation devices; Devices for accessing memories, e.g. details of addressing circuits

- G11C29/30—Accessing single arrays

- G11C29/32—Serial access; Scan testing

-

- E—FIXED CONSTRUCTIONS

- E01—CONSTRUCTION OF ROADS, RAILWAYS, OR BRIDGES

- E01D—CONSTRUCTION OF BRIDGES, ELEVATED ROADWAYS OR VIADUCTS; ASSEMBLY OF BRIDGES

- E01D19/00—Structural or constructional details of bridges

- E01D19/06—Arrangement, construction or bridging of expansion joints

- E01D19/062—Joints having intermediate beams

-

- E—FIXED CONSTRUCTIONS

- E01—CONSTRUCTION OF ROADS, RAILWAYS, OR BRIDGES

- E01D—CONSTRUCTION OF BRIDGES, ELEVATED ROADWAYS OR VIADUCTS; ASSEMBLY OF BRIDGES

- E01D19/00—Structural or constructional details of bridges

- E01D19/08—Damp-proof or other insulating layers; Drainage arrangements or devices ; Bridge deck surfacings

- E01D19/086—Drainage arrangements or devices

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318533—Reconfiguring for testing, e.g. LSSD, partitioning using scanning techniques, e.g. LSSD, Boundary Scan, JTAG

- G01R31/318536—Scan chain arrangements, e.g. connections, test bus, analog signals

- G01R31/318538—Topological or mechanical aspects

Landscapes

- Engineering & Computer Science (AREA)

- Architecture (AREA)

- Civil Engineering (AREA)

- Structural Engineering (AREA)

- General Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Tests Of Electronic Circuits (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

スキャンテストに関する効率的な設計を可能とした半導体回路装置を提供すること

【解決手段】

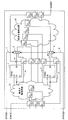

本発明にかかる半導体回路装置の第一の態様は、複数の回路部を備え、スキャンテストを実行可能な半導体回路装置であって、テストデータを伝送するフリップフロップ111乃至119を有するスキャンチェインと、スキャンチェインのフリップフロップ間の経路に配置されているマクロセル1と、マクロセル1をバイパスするバイパス経路14と、マクロセル1もしくはバイパス経路14を選択するセレクタ3と、同様にスキャンチェインのフリップフロップ間の経路に配置されるマクロセル2と、マクロセル2をバイパスするバイパス経路15と、マクロセル2もしくはバイパス経路15を選択するセレクタ4を有する。セレクタ3とセレクタ4はそれぞれ独立して動作する。

【選択図】 図1

Description

発明の実施の形態1.

本実施の形態にかかるLSIの主要部を示したブロック図を図3に示す。発明の実施の形態1ではセレクタ3、4の制御信号線7、8をチップに設けた外部入力端子BYPASS1、BYPASS2と接続して外部から制御するよう構成していたが、本実施の形態では、スキャンチェイン上に設けたフリップフロップ9、10の出力をセレクタ3、4の制御端子に接続している。これにより、セレクタ3、4の制御は、フリップフロップ9、10にスキャンシフト動作によって値を設定することによって行うことができる。また、フリップフロップ9、10は、マクロセル1、2のCS信号を取得する。これによって、フリップフロップ9、10を論理ゲートの故障検出用のフリップフロップと兼用させることが可能であり、マクロセル1、2のCS端子に繋がる論理ゲートの故障検出を行う際に、新たにフリップフロップを追加する必要がなくなるという利点がある。

3、4 セレクタ

5、6、9、10、111−119 フリップフロップ

12、13 組み合わせ論理回路

16、17 バイパス路

Claims (8)

- 複数の回路部を備え、スキャンテストを実行可能な半導体回路装置であって、

テストデータを伝送する複数のフリップフロップを有するスキャンチェインと、

前記スキャンチェインのフリップフロップ間の経路に配置されている第1の回路部と、

前記第1の回路部をバイパスする第1のバイパス経路と、

前記第1の回路部もしくは前記第1のバイパス経路を選択する第1の選択回路部と、

前記スキャンチェインのフリップフロップ間の経路に配置され、前記第1の回路部と異なる第2の回路部と、

前記第2の回路部をバイパスする第2のバイパス経路と、

前記第1の選択回路部と独立して動作し、前記第2の回路部もしくは前記第2のバイパス経路を選択する第2の選択回路部と、

を有する、半導体回路装置。 - 前記第1及び第2の回路部は、複数クロック動作によって、入力データに従うデータを出力する、請求項1に記載の半導体回路装置。

- 前記第1及び第2の回路部はマクロセルである、請求項1に記載の半導体回路装置。

- 前記第1の選択回路部は、前記第1の回路部の出力、もしくは、前記第1のバイパス経路上にあり前記スキャンチェインに含まれるフリップフロップの出力、を選択する、請求項1から3のいずれかに記載の半導体回路装置。

- 前記第2の選択回路部は、前記第2の回路部の出力、もしくは、前記第2のバイパス経路上にあり前記スキャンチェインに含まれるフリップフロップの出力、を選択する、請求項4に記載の半導体回路装置。

- 前記第1の選択回路部は、前記スキャンチェインに含まれるフリップフロップの出力に制御されて選択動作を行う、請求項1から5のいずれかに記載の半導体回路装置。

- 前記第1の選択回路部に出力するフリップフロップに、前記第1の回路部の動作状態を制御する信号が入力される、請求項6に記載の半導体回路装置。

- 複数の回路部を備える半導体回路に関するスキャンテスト方法であって、

スキャンシフトによってテストデータを入力する第1のステップと、

第1の回路部によるテストデータの処理もしくは前記第1の回路部のバイパスを選択する第2のステップと、

前記第2のステップとは独立に、第2の回路部によるテストデータの処理もしくは前記第2の回路部のバイパスを選択する第3のステップと、

前記入力されたテストデータの前記半導体回路による処理結果を取得するステップと、

前記処理結果に従って、前記半導体回路の欠陥を決定するステップと、

を有する、スキャンテスト方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004066997A JP4549701B2 (ja) | 2004-03-10 | 2004-03-10 | 半導体回路装置及び半導体回路に関するスキャンテスト方法 |

| US11/073,864 US7380183B2 (en) | 2004-03-10 | 2005-03-08 | Semiconductor circuit apparatus and scan test method for semiconductor circuit |

| KR1020050020297A KR100735585B1 (ko) | 2004-03-10 | 2005-03-10 | 반도체 회로 장치 및 반도체 회로에 관한 스캔 테스트 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004066997A JP4549701B2 (ja) | 2004-03-10 | 2004-03-10 | 半導体回路装置及び半導体回路に関するスキャンテスト方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005257366A true JP2005257366A (ja) | 2005-09-22 |

| JP2005257366A5 JP2005257366A5 (ja) | 2006-11-09 |

| JP4549701B2 JP4549701B2 (ja) | 2010-09-22 |

Family

ID=34918370

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004066997A Expired - Fee Related JP4549701B2 (ja) | 2004-03-10 | 2004-03-10 | 半導体回路装置及び半導体回路に関するスキャンテスト方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7380183B2 (ja) |

| JP (1) | JP4549701B2 (ja) |

| KR (1) | KR100735585B1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7427875B2 (en) | 2005-09-29 | 2008-09-23 | Hynix Semiconductor Inc. | Flip-flop circuit |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7555687B2 (en) * | 2005-07-20 | 2009-06-30 | Texas Instruments Incorporated | Sequential scan technique for testing integrated circuits with reduced power, time and/or cost |

| JP2011099835A (ja) * | 2009-11-09 | 2011-05-19 | Renesas Electronics Corp | スキャンテスト回路及びスキャンテスト方法 |

| JP2011149775A (ja) * | 2010-01-20 | 2011-08-04 | Renesas Electronics Corp | 半導体集積回路及びコアテスト回路 |

| US8645778B2 (en) * | 2011-12-31 | 2014-02-04 | Lsi Corporation | Scan test circuitry with delay defect bypass functionality |

| US8826087B2 (en) * | 2012-11-21 | 2014-09-02 | Lsi Corporation | Scan circuitry for testing input and output functional paths of an integrated circuit |

| US10317464B2 (en) * | 2017-05-08 | 2019-06-11 | Xilinx, Inc. | Dynamic scan chain reconfiguration in an integrated circuit |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60231187A (ja) * | 1984-05-01 | 1985-11-16 | Nippon Telegr & Teleph Corp <Ntt> | テスト容易化回路構成法 |

| JPH04170065A (ja) * | 1990-11-02 | 1992-06-17 | Nec Ic Microcomput Syst Ltd | 半導体集積回路 |

| JPH05119123A (ja) * | 1991-10-25 | 1993-05-18 | Nec Corp | シフトパス回路 |

| JPH08254570A (ja) * | 1995-03-16 | 1996-10-01 | Fujitsu Ltd | 半導体集積回路 |

| JPH1019983A (ja) * | 1996-07-02 | 1998-01-23 | Matsushita Electric Ind Co Ltd | バウンダリスキャンテスト方法 |

| JPH1183958A (ja) * | 1997-09-02 | 1999-03-26 | Sharp Corp | テストパタン生成装置並びにテストパタン生成プログラムを記録した記録媒体 |

| JP2000131389A (ja) * | 1998-10-28 | 2000-05-12 | Hitachi Ltd | Icチップ内モジュールテスト制御方式 |

| JP2001042008A (ja) * | 1999-07-30 | 2001-02-16 | Sanyo Electric Co Ltd | 半導体集積回路 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5477545A (en) * | 1993-02-09 | 1995-12-19 | Lsi Logic Corporation | Method and apparatus for testing of core-cell based integrated circuits |

| GB9802091D0 (en) * | 1998-01-30 | 1998-03-25 | Sgs Thomson Microelectronics | Device scan testing |

| KR20030027989A (ko) | 2001-09-27 | 2003-04-08 | 삼성전자주식회사 | 칩 테스트 장치 |

| US7441164B2 (en) * | 2002-12-26 | 2008-10-21 | Broadcom Corporation | Memory bypass with support for path delay test |

-

2004

- 2004-03-10 JP JP2004066997A patent/JP4549701B2/ja not_active Expired - Fee Related

-

2005

- 2005-03-08 US US11/073,864 patent/US7380183B2/en not_active Expired - Fee Related

- 2005-03-10 KR KR1020050020297A patent/KR100735585B1/ko not_active IP Right Cessation

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60231187A (ja) * | 1984-05-01 | 1985-11-16 | Nippon Telegr & Teleph Corp <Ntt> | テスト容易化回路構成法 |

| JPH04170065A (ja) * | 1990-11-02 | 1992-06-17 | Nec Ic Microcomput Syst Ltd | 半導体集積回路 |

| JPH05119123A (ja) * | 1991-10-25 | 1993-05-18 | Nec Corp | シフトパス回路 |

| JPH08254570A (ja) * | 1995-03-16 | 1996-10-01 | Fujitsu Ltd | 半導体集積回路 |

| JPH1019983A (ja) * | 1996-07-02 | 1998-01-23 | Matsushita Electric Ind Co Ltd | バウンダリスキャンテスト方法 |

| JPH1183958A (ja) * | 1997-09-02 | 1999-03-26 | Sharp Corp | テストパタン生成装置並びにテストパタン生成プログラムを記録した記録媒体 |

| JP2000131389A (ja) * | 1998-10-28 | 2000-05-12 | Hitachi Ltd | Icチップ内モジュールテスト制御方式 |

| JP2001042008A (ja) * | 1999-07-30 | 2001-02-16 | Sanyo Electric Co Ltd | 半導体集積回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7427875B2 (en) | 2005-09-29 | 2008-09-23 | Hynix Semiconductor Inc. | Flip-flop circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| US7380183B2 (en) | 2008-05-27 |

| KR100735585B1 (ko) | 2007-07-04 |

| JP4549701B2 (ja) | 2010-09-22 |

| US20050204227A1 (en) | 2005-09-15 |

| KR20060043851A (ko) | 2006-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6054597B2 (ja) | 半導体集積回路 | |

| JP2003332443A (ja) | 半導体集積回路とその設計支援装置およびテスト方法 | |

| JP3996055B2 (ja) | 内部中間スキャンテスト故障をデバッグするテストアクセスポート(tap)コントローラシステムおよび方法 | |

| US7380183B2 (en) | Semiconductor circuit apparatus and scan test method for semiconductor circuit | |

| JP2007205933A (ja) | 半導体集積回路 | |

| US7712001B2 (en) | Semiconductor integrated circuit and method of testing semiconductor integrated circuit | |

| CN114667455A (zh) | 用于测试电路的通用压缩器架构 | |

| JP2008164470A (ja) | 集積回路の内部ラッチをスキャンする方法及び装置並びに集積回路 | |

| JP2006292646A (ja) | Lsiのテスト方法 | |

| JP4187728B2 (ja) | テスト構成の半導体集積回路およびそのテスト方法 | |

| JP2006038831A (ja) | スキャン試験回路を備えた半導体集積回路 | |

| JP4610919B2 (ja) | 半導体集積回路装置 | |

| JP5237148B2 (ja) | 半導体集積回路 | |

| KR100769041B1 (ko) | 테스트를 위한 집적회로 장치 | |

| JP4666468B2 (ja) | 半導体集積回路 | |

| JP6782134B2 (ja) | スキャン回路、集合スキャン回路、半導体装置、および半導体装置の検査方法 | |

| JP4272898B2 (ja) | 半導体テスト回路及びそのテスト方法 | |

| JP2009042017A (ja) | スキャンパス回路及び半導体集積回路 | |

| JP2004258791A (ja) | 半導体集積回路のスキャンパス設計方法 | |

| KR20050060865A (ko) | 신호 단자 단락과 정상 동작 검출을 위하여 에스오씨아이피 코아를 스캔 시험할 수 있는 집적회로 장치 및 그방법 | |

| JP4777399B2 (ja) | テスト構成の半導体集積回路 | |

| JP2010025703A (ja) | 半導体装置およびそのテスト方法 | |

| JP2002189060A (ja) | 半導体集積回路装置およびその検査方法 | |

| JP2010122009A (ja) | 半導体集積回路 | |

| JPH0389178A (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060922 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070206 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090910 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090915 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100415 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100706 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100707 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4549701 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |