CN1264225C - 具有含氮栅绝缘膜的半导体器件及其制造方法 - Google Patents

具有含氮栅绝缘膜的半导体器件及其制造方法 Download PDFInfo

- Publication number

- CN1264225C CN1264225C CN00122716.5A CN00122716A CN1264225C CN 1264225 C CN1264225 C CN 1264225C CN 00122716 A CN00122716 A CN 00122716A CN 1264225 C CN1264225 C CN 1264225C

- Authority

- CN

- China

- Prior art keywords

- insulating film

- gate electrode

- film

- semiconductor substrate

- gate insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 115

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 title claims abstract description 76

- 229910052757 nitrogen Inorganic materials 0.000 title claims abstract description 41

- 238000004519 manufacturing process Methods 0.000 title claims description 31

- 239000000758 substrate Substances 0.000 claims abstract description 77

- 230000003647 oxidation Effects 0.000 claims description 40

- 238000007254 oxidation reaction Methods 0.000 claims description 40

- 238000000034 method Methods 0.000 claims description 17

- 229920002120 photoresistant polymer Polymers 0.000 description 23

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 16

- 229910052814 silicon oxide Inorganic materials 0.000 description 14

- 238000009792 diffusion process Methods 0.000 description 13

- 239000012535 impurity Substances 0.000 description 11

- 150000002500 ions Chemical class 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 6

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 238000006731 degradation reaction Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000002955 isolation Methods 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000007850 degeneration Effects 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000001465 metallisation Methods 0.000 description 1

- 239000003595 mist Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28202—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation in a nitrogen-containing ambient, e.g. nitride deposition, growth, oxynitridation, NH3 nitridation, N2O oxidation, thermal nitridation, RTN, plasma nitridation, RPN

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28185—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation with a treatment, e.g. annealing, after the formation of the gate insulator and before the formation of the definitive gate conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823462—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate insulating layers, e.g. different gate insulating layer thicknesses, particular gate insulator materials or particular gate insulator implants

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/518—Insulating materials associated therewith the insulating material containing nitrogen, e.g. nitride, oxynitride, nitrogen-doped material

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

MOS半导体器件包括:形成在半导体衬底上含氮的栅绝缘膜;栅电极选择性地形成在栅绝缘膜上;以及形成在栅电极和半导体衬底表面上的氧化膜,其中第二部分中的位于第一平行线和衬底之间的那一部分的厚度为第二部分中位于第二平行线和栅极之间的另外一部分的厚度的三分之一以下。由于栅绝缘膜含氮,可以抑制栅绝缘膜厚度的增加超出需要的厚度,也可以防止栅电压降低,同时可以提高MOS晶体管的控制能力。

Description

技术领域

本发明涉及在栅电极和半导体衬底的表面上形成柱(post)状氧化膜的MOS半导体器件。

背景技术

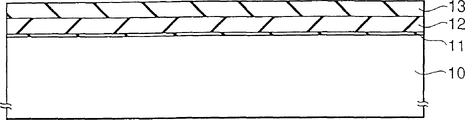

作为防止硅MOSFET的栅绝缘膜耐压退化的方法,到目前为止存在一种称做柱状氧化的技术。柱状氧化膜是指形成在栅电极和半导体衬底的表面上的氧化膜,以保护栅电极角部中的栅绝缘膜。其中形成有柱状氧化膜的MOS半导体器件的简图显示在图1-A中。柱状氧化膜128形成在栅电极127、n型扩散层135以及p型扩散层136上。

图1-B示出了在MOS半导体器件的制造步骤中进行柱状氧化之后的结构剖面图,示出了栅电极127的角部。如图1-B所示,栅绝缘膜125形成在硅衬底110上,由多晶硅形成的栅电极(多晶硅栅电极)127选择性地形成在栅绝缘膜125上。此后,进行柱状氧化,之后栅柱状氧化膜128形成在栅电极127和半导体衬底110上。

在形成所述栅氧化膜的柱状氧化步骤中,栅电极127与硅衬底110也一起被氧化,因此栅电极127角部的厚度增加。因此,栅电极127角部的曲率半径变大,从而可以避免MOS晶体管栅电极角部的电场集中。

此外,可以防止在MOS晶体管的制造步骤中栅电极角部的栅绝缘膜退化。

然而,在形成栅柱状氧化膜128的步骤中,硅衬底110也和形成栅电极127的多晶硅一起氧化,比要求厚度大的氧化膜125形成在栅电极127的角部中。由此,由于栅电极氧化膜125的视在厚度很大,因此施加到栅氧化膜125的电压变弱,栅电压降低,导致MOS晶体管控制能力退化。当MOS晶体管工作在该状态中时,微观制造的沟道区处的阈值电压的绝对值基本上降低了。为此,在关断的MOS晶体管中流动的关断漏电流会增加。

要形成源/漏电极的延伸扩散层132,在离子注入中使用柱状氧化膜128作为保护氧化膜。此时,杂质离子进入柱状氧化膜128内,因此注入到硅衬底110内的杂质剂量减少。此外,由于以上原因,进行离子注入时必须考虑棚柱状氧化膜的厚度,并且注入的离子形成宽杂质分布。因此,不可能形成精确的杂质浓度分布。

发明内容

本发明的一个目的是提供一种半导体器件及其制造方法,能够抑制在栅电极角部发生漏电流,并且可以抑制离子注入形成源/漏扩散层时注入到衬底内杂质剂量的减少。

本发明的半导体器件具有以下结构以达到以上和其它目的。

本发明的半导体器件包括:半导体衬底;形成在半导体衬底上的栅绝缘膜,栅绝缘膜含有氮;栅电极选择性地形成在栅绝缘膜上;以及形成在栅电极和半导体衬底表面上的氧化膜,其中靠近半导体衬底的那部分栅绝缘膜的厚度为靠近栅电极角部的栅绝缘膜厚度的三分之一以下。

栅绝缘膜允许含有氮,以便可以控制栅电极角部的栅绝缘膜的厚度。由此,可以防止栅电压降低。

此外,在本发明的半导体器件中,形成在栅电极下的栅绝缘膜为含有浓度范围为约2%到10%氮的氧化膜。

通过将氮浓度设置在以上范围,可以降低栅绝缘膜的介质常数,因此可以防止源-漏电流降低。

此外,在本发明的半导体器件中,栅绝缘膜的氮浓度峰值设置在半导体衬底的表面附近。

由于氮浓度的峰值位置设置在半导体衬底的表面内,不对半导体衬底进行氧化,同时对栅电极的侧面进行氧化。

本发明的制造方法包括以下步骤:在半导体衬底上形成栅绝缘膜,栅绝缘膜含有氮;在栅绝缘膜上选择性地形成栅电极;以及形成栅电极以在栅电极和半导体衬底表面上形成氧化膜之后,进行柱状氧化。

通过使栅绝缘膜含氮,可以抑制栅绝缘膜厚度的增加超出需要的厚度,也可以防止栅电压降低,同时可以提高MOS晶体管的控制能力。

此外,在本发明的制造方法中,靠近半导体衬底的那部分栅绝缘膜的厚度为靠近栅电极角部的栅绝缘膜厚度的三分之一以下。

而且,在本发明的制造方法中,在栅电极下的栅绝缘膜为含有浓度范围为约2%到10%氮的氧化膜。

此外,在本发明的制造方法中,栅绝缘膜的氮浓度峰值设置在半导体衬底的表面附近。

由于氮浓度的峰值位置设置在半导体衬底的表面内,不对半导体衬底进行氧化,同时对栅电极的侧面进行氧化。

从下面的详细说明中,本发明的其它目的、特点及优点将变得很显然。然而,应该理解仅为了说明的目的给出了详细的说明和具体的例子,同时表示本发明的优选实施例。对于本领域的技术人员来说很显然可以在本发明的精神和范围内对所述详细的说明进行各种修改和变形。

通过下面参考附图的详细说明将容易得到本发明更完整的理解和许多附带优点,其中:

附图说明

图1-A示出了具有栅柱状氧化膜的常规MOS半导体器件的剖面图;

图1-B为图1-A中示出的MOS半导体器件的栅电极角部的局部放大剖面图;

图2-A示出了根据本发明具有栅柱状氧化膜的MOS半导体器件的剖面图;

图2-B为图2-A中示出的MOS半导体器件的栅电极角部的局部放大剖面图;

图3示出了根据本发明半导体器件的制造步骤剖面图;

图4示出了图3之后的半导体器件的制造步骤剖面图;

图5示出了图4之后的半导体器件的制造步骤剖面图;

图6示出了图5之后的半导体器件的制造步骤剖面图;

图7示出了图6之后的半导体器件的制造步骤剖面图;

图8示出了图7之后的半导体器件的制造步骤剖面图;

图9示出了图8之后的半导体器件的制造步骤剖面图;

图10示出了图9之后的半导体器件的制造步骤剖面图;

图11示出了图10之后的半导体器件的制造步骤剖面图;

图12示出了图11之后的半导体器件的制造步骤剖面图;

图13示出了图12之后的半导体器件的制造步骤剖面图;

图14示出了图13之后的半导体器件的制造步骤剖面图;以及

图15示出了图14之后的半导体器件的制造步骤剖面图;

图16示出了根据本发明的半导体器件的栅角部的剖面图;

图17示出了氮浓度和从栅氧化膜延伸到半导体衬底内的深度之间的关系图;

图18示出了根据本发明的半导体器件的栅角部的剖面图;

图19示出了含在根据本发明的半导体器件的栅氧化膜中的氮浓度和MOS晶体管性能之间的相关图。

具体实施方式

下面参考附图介绍本发明的半导体器件及其制造方法的实施例。

作为防止MOS半导体器件的栅绝缘膜的耐压退化的方法,现在已有一种称做柱状氧化的技术。柱状氧化膜为形成在栅电极表面和半导体衬底上的氧化膜,以保护位于栅电极角部的栅绝缘膜。其内形成有栅柱状氧化膜(下文称做柱状氧化膜28)的MOS半导体器件的剖面显示在图2-A中。

n型扩散层35和p型扩散层36形成在半导体衬底10中,栅氧化膜25和栅电极27形成在半导体衬底的表面上。栅氧化膜25含有浓度范围从约2%到10%的氮。柱状氧化膜28形成在栅电极27、n型扩散层35以及p型扩散层36的表面上。

图2-B示出了在MOS晶体管的制造步骤中进行柱状氧化之后的结构,其中详细地示出了栅电极27的角部。如图2-B所示,栅绝缘膜25形成在半导体(硅)衬底10上,由多晶硅制成的栅电极(多晶硅栅电极27)选择性地形成在栅绝缘膜25上。此后,氧化栅电极27和半导体衬底10的表面,由此在栅电极27和半导体衬底10上形成氧化膜28。

在形成柱状氧化膜28的柱状氧化步骤中,由多晶硅形成的栅电极27和半导体衬底10也一起被氧化,靠近栅电极27角部的氧化膜厚度增加,导致靠近栅电极27角部的氧化膜翘曲。因此,栅电极27角部的曲率半径变大,因此可以防止MOS晶体管栅电极角部的电场集中。

下面根据具体的制造步骤顺序介绍本发明的半导体器件的制造方法。图3到6示出了形成本发明的元件隔离区的制造步骤的剖面图。

如图3所示,氧化硅膜11首先形成在半导体衬底10上,氮化硅膜12形成在氧化硅膜11上。氧化硅膜13形成在氮化硅膜12上。

接下来,如图4所示,构图的光刻胶膜14形成在氧化硅膜13上。使用光刻胶膜14做为掩模选择性地除去氧化硅膜11和13以及氮化硅膜12。此后,除去光刻胶膜14。

接下来,如图5所示,使用氧化硅膜11和13以及氮化硅膜12做为掩模通过反应离子腐蚀(RIE)除去对应于元件隔离区的部分半导体衬底10,由此在半导体衬底10中形成沟槽15。

随后,如图6所示,氧化硅膜16形成在所得结构的整个表面上,由此用氧化硅膜16填充沟槽15。

接下来,如图7所示,通过化学机械抛光(CMP)法平坦氧化硅膜16,抛光直到露出氮化硅膜12的表面。

之后,通过湿腐蚀除去氧化硅膜11和16以及氮化硅膜12,由此露出半导体衬底10的表面。

通过这种处理,如图8所示,元件隔离区17形成在半导体衬底10中,此后,氧化硅膜18形成在所得结构的整个表面上。

图9到15示出了栅电极形成步骤的剖面图。

如图9所示,首先构图的光刻胶膜(未示出)形成在半导体衬底10上。使用光刻胶膜作为掩模进行离子注入和扩散,在半导体衬底10的表面内形成p型阱21。此后,除去光刻胶膜。以与上面介绍的相同方式,在p型阱21上形成构图的光刻胶膜(未示出)。使用光刻胶膜作为掩模进行离子注入和扩散,在半导体衬底10的表面内形成n型阱22。此后,除去光刻胶膜。随后,在半导体衬底10中P和N型阱21和22的表面内分别形成n沟道区23和p沟道区24。然后除去氧化膜18。接下来,在半导体衬底10上形成栅绝缘膜25。形成栅绝缘膜25时,使用单一气体或由氧和含有NO、N2O以及NH3中任何一种氮作成的混合气体进行氧化/氮化反应。因此,形成由含氮浓度为约2%到10%的氧化硅膜形成的栅绝缘膜25。注意形成栅氧化膜25和高浓度区的方法不限于以上方法。例如,以形成氧化硅膜作为基底材料然后通过含有以上NO、N2O以及NH3中任何一种气体氮化氧化硅膜的方式形成栅绝缘膜25。

随后,在栅绝缘膜25上形成多晶硅膜26。

接下来,在多晶硅膜26上形成光刻胶膜(未示出)。此后,如图10所示,使用光刻胶膜作为掩模通过RIE选择性地除去多晶硅膜26和栅绝缘膜25。由此,形成多晶硅栅电极27。

随后,如图11所示,多晶硅栅电极27和半导体衬底10的表面被气氛柱状氧化,由此在所得结构的整个表面上形成栅柱状氧化膜28。

栅绝缘膜25含有氮气,与半导体衬底10接触的栅绝缘膜25表面处的氮浓度显示出浓度最高。由此氮气的分子键比氧气的分子键稳固,因此抑制了硅的氧化。

因此,由于氧化了栅电极27,抑制了半导体衬底10表面附近的氧化,因此控制了半导体衬底10上栅柱状氧化膜28的生长。相反,对多晶硅栅电极27的表面和扩散层32表面的氧化多于栅电极27下半导体衬底10的氧化。

例如,当在800℃的温度下和30分钟的处理时间的条件下通过退火进行氧化,当栅氧化膜不含氮时半导体衬底10被氧化约6nm。另一方面,在具有3.5nm厚含有浓度约2%氮的栅绝缘膜的半导体器件中,半导体衬底10仅氧化约1nm。

接下来,如图12所示,在P阱21上形成构图的光刻胶膜29。使用光刻胶膜29作掩模在半导体衬底10的表面引入杂质,由此在对应于N阱22的半导体衬底10的表面中形成P型延伸区30。此后,除去光刻胶膜29。

随后,如图13所示,在N阱22上选择性地形成构图的光刻胶膜31。使用光刻胶膜31作掩模在半导体衬底10的表面引入杂质,由此在对应于P阱21的半导体衬底10的表面中形成N型延伸区32。此后,除去光刻胶膜31。

在图14所示的所得结构的整个表面上形成氮化硅膜33。

通过RIE选择性地除去氮化硅膜33,在栅电极侧壁上形成栅侧壁(间隔层34)。接下来,在N阱22上选择性地形成构图的光刻胶膜(未示出)。使用光刻胶膜作掩模在半导体衬底10的表面引入杂质,由此在对应于P阱21的半导体衬底10的表面中形成N型扩散区35。此后,除去光刻胶膜。接下来,在P阱21上选择性地形成构图的光刻胶膜(未示出)。使用光刻胶膜作掩模在半导体衬底10的表面引入杂质,由此在对应于N阱22的半导体衬底10的表面中形成P型扩散区36。此后,除去光刻胶膜。

以上面介绍的方式形成CMOS FET,此后进行公知的硅化步骤和金属化步骤之后完成了LSI的形成。

下面参考图16和17介绍本发明的半导体器件中氮的浓度分布。在本发明中,栅绝缘膜25中的高浓度氮区接触半导体衬底10的表面。这是由于在半导体衬底10的表面中存在少量的氮,因此可以抑制半导体衬底10的氧化。此外,氮化硅通常显示出比氧化硅高的介电常数。当氮的含量太多时,栅氧化膜的介电常数变大,直通电流增加。实验表明如果氮的浓度约10%,那么可以抑制MOS晶体管的直通电流。

在本实施例中,如图16所示,氮的高浓度区形成在靠近半导体衬底10的栅绝缘膜25的表面上。如图17所示,半导体衬底10的表面和栅绝缘膜25之间的边界部分显示出氮浓度最高。

根据本发明的半导体器件的剖面图详细地显示在图18中。首先,厚度为2.5nm的氧化膜28a形成在半导体器件的部分表面上,不与多晶硅栅电极27垂直地重叠,厚度为1nm以下的氧化膜28b形成在半导体衬底10的部分表面上,与多晶硅栅电极27垂直地重叠。厚度为12nm的氧化膜28c形成在多晶硅栅电极27的侧面,厚度为3nm以上的氧化膜28d形成在多晶硅栅电极27的角部,与栅绝缘膜25垂直地重叠。如上所述,参考形成在栅电极27角部的栅绝缘膜25,氧化膜28b的厚度为氧化膜28d厚度的三分之一以下。当栅氧化膜不含氮时,氧化膜28b的厚度增加。

图19示出了本发明的半导体器件中含在栅绝缘膜中的氮浓度和MOS晶体管的性能的关系图。在图19中,横坐标示出了含在栅绝缘膜中的氮浓度(%),纵坐标示出了由○表示的栅极漏电流和由■表示的漏电流退化率。漏电流退化率为当氮浓度为0%时漏电流设置为1的比例。

随着氮浓度的增加,泄露电流减少。然而,漏电流也减少。由于漏电流与驱动力成正比,因此MOS晶体管的驱动力减小。虽然泄露电流应该小,但氮浓度增加太多会使MOS晶体管不能工作。假设漏电流退化的极限为10%时,含在栅氧化膜中的氮浓度应为约2%到10%。

根据本发明,如图2B所示,虽然形成柱状氧化膜时进行栅电极27侧壁的氧化,但由于在半导体衬底10的表面中存在含氮的高浓度区40,所以可以控制对半导体衬底10的氧化。因此,可以将栅电极27角部氧化膜厚度的增加控制到约为现有技术的一半。换句话说,可以控制由于栅电极27角部氧化膜的厚度增加造成的电力线的泄露。因此,可以防止栅电极的降低,并可以提高晶体管的控制能力。此外,当形成源/漏电极的延伸扩散层时,栅绝缘膜可以用做离子注入时的保护氧化膜。由于可以控制栅绝缘膜厚度的增加,因此可以防止注入到半导体衬底内杂质剂量的减少。因此,与现有技术相比,离子的飞行距离缩短。由于可以控制注入的离子广泛的扩散。由此,可以形成精确的杂质浓度剖面。

在栅电极27的角部,由于氧化栅电极27角部的半径曲率变大,因此可以缓和栅电极27角部中的电场集中。注意氧化栅电极的方法不限于退火,也可以在例如1053℃的温度下例如50秒的处理时间的条件下通过RTO(快速热氧化)对栅电极进行氧化。

如上所述,根据本发明,提供了一种半导体器件及其制造方法,能够控制在栅电极角部产生泄露电流,并可以减少形成源/漏扩散层时离子注入期间注入到半导体衬底内的杂质剂量的减少。

虽然示出和介绍了目前被认为是本发明的优选实施例,但是本领域的技术人员应该理解可以进行各种变化和修改,可以用等效物替代本发明的器件,而不脱离本发明的实际范围。此外,可以根据本发明的教导进行许多修改以适合特定的情况或材料,而不脱离本发明的主要范围。因此,本发明并不局限于作为实施本发明的最佳方式公开的特定实施例,实际上本发明包括落入附带权利要求书的范围内的所有实施例。

Claims (4)

1.一种半导体器件,包括:

半导体衬底;

形成在所述半导体衬底上的栅绝缘膜,所述栅绝缘膜的氮浓度峰值设置在所述半导体衬底的表面附近;

形成在所述栅绝缘膜上的栅电极;以及

形成在所述栅电极表面和所述半导体衬底上的氧化膜,

其中所述栅绝缘膜有位于所述栅电极的中心部分下的第一部分,以及位于所述栅电极边缘下面的第二部分,所述第二部分厚于所述第一部分,所述第一部分的第一表面和第二表面限定了与所述第二部分交叉的第一和第二平行线,所述第一平行线位于所述第一部分和所述衬底之间,所述第二平行线位于所述第一部分和所述栅电极之间,所述第二部分中的位于所述第一平行线和所述衬底之间的那一部分厚度为所述第二部分中的位于所述第二平行线和所述栅电极之间的另一部分厚度的三分之一以下。

2.根据权利要求1的半导体器件,其中所述栅绝缘膜为含有浓度范围为2%到10%氮的氧化膜。

3.一种半导体器件的制造方法,包括以下步骤:

在半导体衬底上形成栅绝缘膜,所述栅绝缘膜的氮浓度峰值设置在半导体衬底的表面附近;

在所述栅绝缘膜上选择性地形成栅电极;以及

氧化所述栅电极和所述半导体衬底的表面,由此在所述栅电极表面和所述半导体衬底的表面上形成氧化膜,以使得在所述栅电极的角部的栅绝缘膜上,所述半导体衬底一侧的膜厚是所述栅电极一侧的膜厚的1/3以下。

4.根据权利要求3的半导体器件的制造方法,其中正位于所述栅电极下的所述栅绝缘膜含有浓度范围为2%到10%氮的氧化膜。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP11187970A JP2001015748A (ja) | 1999-07-01 | 1999-07-01 | 半導体装置及びその製造方法 |

| JP187970/1999 | 1999-07-01 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1284748A CN1284748A (zh) | 2001-02-21 |

| CN1264225C true CN1264225C (zh) | 2006-07-12 |

Family

ID=16215344

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN00122716.5A Expired - Fee Related CN1264225C (zh) | 1999-07-01 | 2000-06-30 | 具有含氮栅绝缘膜的半导体器件及其制造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6498374B1 (zh) |

| JP (1) | JP2001015748A (zh) |

| CN (1) | CN1264225C (zh) |

| TW (1) | TW535191B (zh) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001291861A (ja) * | 2000-04-05 | 2001-10-19 | Nec Corp | Mosトランジスタ、トランジスタ製造方法 |

| JP2002026139A (ja) | 2000-06-30 | 2002-01-25 | Toshiba Corp | 半導体装置及び半導体装置の製造方法 |

| JP2002270833A (ja) * | 2001-03-14 | 2002-09-20 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| US6921743B2 (en) * | 2001-04-02 | 2005-07-26 | The Procter & Gamble Company | Automatic dishwashing compositions containing a halogen dioxide salt and methods for use with electrochemical cells and/or electrolytic devices |

| KR100464535B1 (ko) * | 2002-05-20 | 2005-01-03 | 주식회사 하이닉스반도체 | 반도체소자의 트랜지스터 형성 방법 |

| JP2004221246A (ja) * | 2003-01-14 | 2004-08-05 | Seiko Epson Corp | 半導体装置及びその製造方法 |

| JP2005064317A (ja) * | 2003-08-18 | 2005-03-10 | Semiconductor Leading Edge Technologies Inc | 半導体装置 |

| US7005333B2 (en) * | 2003-12-30 | 2006-02-28 | Infineon Technologies Ag | Transistor with silicon and carbon layer in the channel region |

| US7002224B2 (en) * | 2004-02-03 | 2006-02-21 | Infineon Technologies Ag | Transistor with doped gate dielectric |

| US7094671B2 (en) * | 2004-03-22 | 2006-08-22 | Infineon Technologies Ag | Transistor with shallow germanium implantation region in channel |

| JP2006253311A (ja) * | 2005-03-09 | 2006-09-21 | Toshiba Corp | 半導体装置及びその製造方法 |

| JP2013125826A (ja) * | 2011-12-14 | 2013-06-24 | Renesas Electronics Corp | 半導体装置及び半導体装置の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0730113A (ja) * | 1993-07-09 | 1995-01-31 | Sony Corp | Mos型トランジスタの製造方法 |

| JPH09312393A (ja) * | 1996-05-22 | 1997-12-02 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP3312102B2 (ja) * | 1996-11-27 | 2002-08-05 | シャープ株式会社 | 不揮発性半導体記憶装置の製造方法 |

| JP3754234B2 (ja) * | 1998-04-28 | 2006-03-08 | インターナショナル・ビジネス・マシーンズ・コーポレーション | ゲート構造側壁の酸化膜の形成方法 |

-

1999

- 1999-07-01 JP JP11187970A patent/JP2001015748A/ja active Pending

-

2000

- 2000-06-29 TW TW089112854A patent/TW535191B/zh not_active IP Right Cessation

- 2000-06-30 US US09/609,314 patent/US6498374B1/en not_active Expired - Fee Related

- 2000-06-30 CN CN00122716.5A patent/CN1264225C/zh not_active Expired - Fee Related

-

2002

- 2002-12-02 US US10/307,405 patent/US20030119235A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| CN1284748A (zh) | 2001-02-21 |

| JP2001015748A (ja) | 2001-01-19 |

| US20030119235A1 (en) | 2003-06-26 |

| TW535191B (en) | 2003-06-01 |

| US6498374B1 (en) | 2002-12-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1215554C (zh) | 互补型金属氧化物半导体器件及其制造方法 | |

| CN1293637C (zh) | 具有应变沟道的互补式金属氧化物半导体及其制作方法 | |

| US7541246B2 (en) | Method of manufacturing semiconductor device | |

| CN1271682C (zh) | 具有不同厚度栅极绝缘膜的半导体器件的制造方法 | |

| CN1264225C (zh) | 具有含氮栅绝缘膜的半导体器件及其制造方法 | |

| CN1282230C (zh) | 半导体装置的制造方法及半导体装置 | |

| CN1505114A (zh) | 半导体器件的制造方法 | |

| CN1841772A (zh) | 半导体器件及其制造方法 | |

| CN1195199A (zh) | 场效应晶体管及其制造方法 | |

| CN1619817A (zh) | 具有不同栅极介质的半导体器件及其制造方法 | |

| CN1663051A (zh) | 半导体器件及其制造方法 | |

| KR100839359B1 (ko) | 피모스 트랜지스터 제조 방법 및 상보형 모스 트랜지스터제조 방법 | |

| CN1744318A (zh) | 半导体装置及其制造方法 | |

| CN1571166A (zh) | 半导体器件及其制造方法 | |

| CN1812103A (zh) | 在栅极电极上具有硅层的半导体器件 | |

| CN1421908A (zh) | 具有浅源极/漏极结区的mos晶体管的制造方法 | |

| CN1906768A (zh) | 半导体器件及其制造方法 | |

| CN1612347A (zh) | 半导体集成电路器件 | |

| CN1542947A (zh) | 半导体装置制造方法 | |

| JPH10125906A (ja) | 半導体装置及びその製造方法 | |

| JP3681525B2 (ja) | 半導体装置の製造方法 | |

| KR100281135B1 (ko) | 반도체 소자의 게이트 산화막 형성 방법 | |

| US7056816B2 (en) | Method for manufacturing semiconductor device | |

| CN1291455C (zh) | 半导体装置的制造方法 | |

| CN1873955A (zh) | 半导体元件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20060712 Termination date: 20130630 |