CN1075242C - Soi基片及其制造方法 - Google Patents

Soi基片及其制造方法 Download PDFInfo

- Publication number

- CN1075242C CN1075242C CN96123935A CN96123935A CN1075242C CN 1075242 C CN1075242 C CN 1075242C CN 96123935 A CN96123935 A CN 96123935A CN 96123935 A CN96123935 A CN 96123935A CN 1075242 C CN1075242 C CN 1075242C

- Authority

- CN

- China

- Prior art keywords

- film

- soi substrate

- manufacture method

- silicon chip

- oxide

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

Abstract

本发明提供了一种硅器件层无损伤的SOI基片的制造方法,在硅基片上形成槽,在硅基片上面及槽内侧壁上形成氧化阻挡膜。之后,以氧化阻挡膜为掩模,对硅基片进行各向同性腐蚀,在槽底面形成沟,对硅基片氧化,形成氧化膜和由所述氧化膜分离的硅器件层。然后,除去氧化阻挡膜,使硅基片表面平坦化。

Description

本发明涉及SOI的制造方法,特别是涉及同时形成埋置绝缘膜和元件分离膜的SOI基片的制造方法。

通常,在CMOS晶体管的制造工序中,为了在大面积上确保避免元件间的分离和CMOS晶体管的闭锁现象,需要形成元件分离。此时,增加分离面积就要减少基片面积,从而成为阻碍高集成度的因素。

为了解决这种问题,提出了SOI(绝缘体上生长硅)技术。

在硅支撑基片和器件用硅基片之间夹置预定厚度的埋置绝缘层的SOI基片,是完全的元件分隔,因而可防止CMOS晶体管的闭锁现象,使元件的高速动作成为可能。

作为SOI基片形成方法,有SIMOX(由注入的氧形成分离)技术及接合技术。

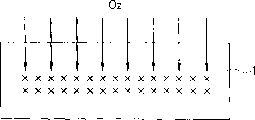

如图4A所示,已有的SIMOX技术中,制备掺杂杂质的硅基片1。在硅基片1内的预定厚度注入氧离子。参看图4B,对硅基片1退火,在硅基片内形成预定厚度的埋置氧化膜2和硅器件层1A。由此,如图4C所示,利用公知的选择的氧化方式,在硅器件层1A的预定的部分形成场氧化膜3。

但是,这种SIMOX技术的缺点是,注入氧离子的步骤中,器件形成面容易发生位错,难以正确地调节器件形成层的厚度,因而产生大量的泄漏电流。

如图5A所示,在已有的其它方式中,制备器件用硅基片10和支承基片11。通过对支承基片11的一表面进行热氧化,形成埋置绝缘层12。如图5B所示,器件用硅基片10和支承基片11在埋置绝缘层12之间接合。之后,通过研磨及抛光除去大部分的器件硅基片10,然后通过高精度的化学机械研磨,形成硅器件层10A。之后,如图5C所示,在用于限定硅器件10A的有源区的硅器件层10A的预定部分形成场氧化膜13。

由此,形成具有硅器件层10A的SOI基片100。

但是,如上所述,为形成硅器件层10A所做的化学机械研磨时,出现难以正确控制研磨阻挡点、硅器件层10A的厚度不均匀的问题。

而且,上述接合方式存在制造工序复杂、制造成本过大的问题。

如上所述,SIMOX方式及接合方式,存在为了限定有源层,必须在硅器件层形成另外的元件分离膜的缺点。

因此,本发明的主要目的在于提供一种硅器件层无损伤的SOI基片的制造方法。

而且,本发明的又一目的在于提供一种制造工序简单的SOI基片的制造方法。

而且,本发明的另一目的在于提供一种能同时形成埋置氧化膜和元件分离膜的SOI基片的制造方法。

为实现上述目的,根据本发明的SOI制造方法,包括以下步骤:

在硅基片上形成槽;

在所述硅基片上面及槽内侧壁上形成氧化阻挡膜;

以所述氧化阻挡膜为掩模,对硅基片做各向同性腐蚀,在槽底面形成沟;

对所述硅基片进行氧化,形成氧化膜和由所述氧化膜分离的硅器件层;

除去所述氧化阻挡膜;

使所述硅基片表面平坦化。

图1A-1F是说明根据本发明的实施例的SOI基片制造方法的剖面图;

图2是本发明另一实施例的硅基片的剖面图;

图3是说明本发明另一实施例的硅基片的剖面图;

图4A-4C是说明根据已有的SIMOX方式的SOI基片的制造方法的剖面图;

图5A-5C是说明根据已有的接合方式的SOI基片的制造方法的剖面图。

以下,参考附图详细说明本发明的优选实施例。

参看图1,对掺杂杂质的硅基片20的元件分离预定区域做各向异性腐蚀,形成槽T。

接着,如图1B所示,在形成有槽T的硅基片20表面淀积预定厚度的氮化硅膜21。由已知的光刻法形成光刻胶图形22以露出槽T底面上部的氮化硅膜21。这里,为了减少由硅基片20与氮化硅膜21的热膨胀系数差引起的应力,在硅基片20与氧化硅膜21之间形成衬底氧化膜(未图示)。

对氮化硅膜21进行腐蚀,由于光刻胶图形22的存在,氮化硅膜21仅存留于硅基片20的上部及槽T的两侧壁,然后除去光刻胶图形22,如图1C所示,露出槽T底面的硅基片20。

如图1D所示,以氧化膜21为掩模,对露出的硅基片20做各向同性腐蚀,形成沟H。其中,由于露出的硅基片20与相邻的槽的间隔狭小,基于各向同性而向侧面腐蚀。

之后,参看图1E,对硅基片20热氧化,形成氧化膜23和由氧化膜23所隔离的硅器件层20A。

如图1F所示,对露出的基片20进行化学机械研磨或者腐蚀,使氧化膜23A表面露出,形成平坦化的SOI基片300。

由此,形成由氧化膜23A和23B所分离的硅器件层20A。此时,氧化膜23之中,在槽区域形成的部分23A,亦即相邻的硅器件层之间的部分23A用作元件分离用的场氧化膜,在硅基片20内部形成的部分23B,亦即硅器件层20A下部的氧化膜23B用作埋置氧化膜。由此,同时形成场氧化膜和埋置氧化膜。

图2中,作为促进场氧化的另一实施例,在热氧化工序之前,在槽T底面的沟H内形成多晶硅层30。此时,多晶硅层30在热氧化工序中作为硅提供层使用,氧化膜23具有到达硅基片表面的充足厚度。

而且,如图3所示,作为本发明的又一实施例,在热氧化工序之前,在槽底面的沟H内进行氧离子的离子注入,从而促进热氧化工序。

如以上的详细说明,在硅基片的预定部分形成槽后,通过热氧化工序同时形成场氧化膜和埋置氧化膜,通过化学机械研磨或者腐蚀,使硅基片表面平坦化,形成SOI基片。

虽然以上对本发明的特定实施例做了说明,但在不脱离本申请的权利要求书的范围的条件下,显然本领域的技术人员可以做出各种变化。

根据本发明,通过离子注入可使SOI基片的表面不发生损伤,并使制造工序简单。

Claims (11)

1、一种SOI基片的制造方法,其特征在于包括以下步骤:

在硅基片上形成槽;

在所述硅基片上面和槽内侧壁上形成氧化阻挡膜;

以所述氧化阻挡膜为掩模,对硅基片进行各向同性腐蚀,在槽底面形成沟;

对所述硅基片氧化,形成氧化膜和由所述氧化膜分离的硅器件层;

除去所述氧化阻挡膜;

使所述硅基片表面平坦化。

2、根据权利要求1的SOI基片制造方法,其特征在于所述氧化阻挡膜是氮化硅膜。

3、根据权利要求2的SOI基片制造方法,其特征在于所述硅基片上面和槽内侧壁上形成氧化阻挡膜的步骤包括:

在形成有槽的硅基片上部淀积所述氮化硅膜;

在所述氮化硅膜上部形成光刻胶图形,以使所述槽下部的氮化硅膜露出;

利用所述光刻胶图形,对氮化硅膜构图;

除去光刻胶图形。

4、根据权利要求3的SOI基片制造方法,其特征在于还包括淀积所述氮化硅之前形成衬底氮化膜的步骤。

5、根据权利要求1的SOI基片制造方法,其特征在于还包括在所述沟的形成步骤与氧化步骤之间,在沟内部形成多晶硅层的步骤。

6、根据权利要求1的SOI基片制造方法,其特征在于在所述沟的形成步骤与热氧化步骤之间,还包括在沟内部注入氧离子的步骤。

7、根据权利要求1的SOI基片制造方法,其特征在于通过所述硅基片表面平坦化步骤,使所述氧化膜表面露出,从而实现平坦化。

8、根据权利要求1的SOI基片制造方法,其特征在于通过化学的机械的研磨方式使所述硅基片平坦化。

9、根据权利要求1的SOI基片制造方法,其特征在于通过腐蚀使所述硅基片平坦化。

10、根据权利要求1的SOI基片制造方法,其特征在于所述氧化膜在所述槽内形成的部分起元件分离的作用。

11、根据权利要求1的SOI基片制造方法,其特征在于所述氧化膜中在所述硅器件层下部的硅基片内形成的部分起埋置氧化膜的作用。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR69459/1995 | 1995-12-30 | ||

| KR69459/95 | 1995-12-30 | ||

| KR19950069459 | 1995-12-30 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1162835A CN1162835A (zh) | 1997-10-22 |

| CN1075242C true CN1075242C (zh) | 2001-11-21 |

Family

ID=19448457

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN96123935A Expired - Fee Related CN1075242C (zh) | 1995-12-30 | 1996-12-30 | Soi基片及其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US5907783A (zh) |

| JP (1) | JP3120275B2 (zh) |

| CN (1) | CN1075242C (zh) |

| DE (1) | DE19654301B4 (zh) |

| GB (1) | GB2309585B (zh) |

| TW (1) | TW309647B (zh) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW358236B (en) * | 1997-12-19 | 1999-05-11 | Nanya Technology Corp | Improved local silicon oxidization method in the manufacture of semiconductor isolation |

| EP1049155A1 (en) * | 1999-04-29 | 2000-11-02 | STMicroelectronics S.r.l. | Process for manufacturing a SOI wafer with buried oxide regions without cusps |

| KR100356577B1 (ko) | 2000-03-30 | 2002-10-18 | 삼성전자 주식회사 | 에스오아이 기판과 그 제조방법 및 이를 이용한에스오아이 엠오에스에프이티 |

| US7294536B2 (en) * | 2000-07-25 | 2007-11-13 | Stmicroelectronics S.R.L. | Process for manufacturing an SOI wafer by annealing and oxidation of buried channels |

| CN100432721C (zh) * | 2001-02-02 | 2008-11-12 | 英特尔公司 | 提供光学质量硅表面的方法 |

| US6818559B2 (en) * | 2001-03-21 | 2004-11-16 | Intel Corporation | Method of fabrication to sharpen corners of Y-branches in integrated optical components and other micro-devices |

| US6551937B2 (en) * | 2001-08-23 | 2003-04-22 | Institute Of Microelectronics | Process for device using partial SOI |

| KR100545183B1 (ko) * | 2003-12-27 | 2006-01-24 | 동부아남반도체 주식회사 | 플래시 셀 내의 자기 정렬 소자 분리막 구조 및 그 형성방법 |

| US7115463B2 (en) * | 2004-08-20 | 2006-10-03 | International Business Machines Corporation | Patterning SOI with silicon mask to create box at different depths |

| US7666735B1 (en) * | 2005-02-10 | 2010-02-23 | Advanced Micro Devices, Inc. | Method for forming semiconductor devices with active silicon height variation |

| KR100849186B1 (ko) * | 2006-04-28 | 2008-07-30 | 주식회사 하이닉스반도체 | 엘에스오아이 공정을 이용한 반도체소자의 제조 방법 |

| IT1397603B1 (it) * | 2009-12-21 | 2013-01-16 | St Microelectronics Srl | Trincee di isolamento per strati semiconduttori. |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0562127A1 (en) * | 1991-10-14 | 1993-09-29 | Nippondenso Co., Ltd. | Method for fabrication of semiconductor device |

| US5434444A (en) * | 1987-02-26 | 1995-07-18 | Kabushiki Kaisha Toshiba | High breakdown voltage semiconductor device |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5940291B2 (ja) * | 1977-12-16 | 1984-09-29 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| JPS6028387B2 (ja) * | 1979-07-12 | 1985-07-04 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| US4361600A (en) * | 1981-11-12 | 1982-11-30 | General Electric Company | Method of making integrated circuits |

| US4502913A (en) * | 1982-06-30 | 1985-03-05 | International Business Machines Corporation | Total dielectric isolation for integrated circuits |

| JPS59188938A (ja) * | 1983-04-12 | 1984-10-26 | Matsushita Electric Ind Co Ltd | 半導体装置の製造方法 |

| US4604162A (en) * | 1983-06-13 | 1986-08-05 | Ncr Corporation | Formation and planarization of silicon-on-insulator structures |

| JPS6068628A (ja) * | 1983-09-26 | 1985-04-19 | Matsushita Electric Ind Co Ltd | 半導体装置の製造方法 |

| US4615746A (en) * | 1983-09-29 | 1986-10-07 | Kenji Kawakita | Method of forming isolated island regions in a semiconductor substrate by selective etching and oxidation and devices formed therefrom |

| FR2554638A1 (fr) * | 1983-11-04 | 1985-05-10 | Efcis | Procede de fabrication de structures integrees de silicium sur ilots isoles du substrat |

| JPS61125039A (ja) * | 1984-11-21 | 1986-06-12 | Nec Corp | 半導体装置の製造方法 |

| US4685198A (en) * | 1985-07-25 | 1987-08-11 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing isolated semiconductor devices |

| US4671851A (en) * | 1985-10-28 | 1987-06-09 | International Business Machines Corporation | Method for removing protuberances at the surface of a semiconductor wafer using a chem-mech polishing technique |

| US4700454A (en) * | 1985-11-04 | 1987-10-20 | Intel Corporation | Process for forming MOS transistor with buried oxide regions for insulation |

| JPH0779133B2 (ja) * | 1986-06-12 | 1995-08-23 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| JPH0239434A (ja) * | 1988-07-28 | 1990-02-08 | Sharp Corp | 半導体装置の製造方法 |

| US5212397A (en) * | 1990-08-13 | 1993-05-18 | Motorola, Inc. | BiCMOS device having an SOI substrate and process for making the same |

| JPH0775244B2 (ja) * | 1990-11-16 | 1995-08-09 | 信越半導体株式会社 | 誘電体分離基板及びその製造方法 |

| EP0525256A1 (en) * | 1991-07-25 | 1993-02-03 | Motorola, Inc. | Method of fabricating isolated device regions |

| JPH0536680A (ja) * | 1991-07-26 | 1993-02-12 | Ricoh Co Ltd | 半導体装置とその製造方法 |

| JPH05267661A (ja) * | 1992-03-23 | 1993-10-15 | Sharp Corp | 半導体装置及びその製造方法 |

| US5382541A (en) * | 1992-08-26 | 1995-01-17 | Harris Corporation | Method for forming recessed oxide isolation containing deep and shallow trenches |

| US5270265A (en) * | 1992-09-01 | 1993-12-14 | Harris Corporation | Stress relief technique of removing oxide from surface of trench-patterned semiconductor-on-insulator structure |

| EP0603106A2 (en) * | 1992-12-16 | 1994-06-22 | International Business Machines Corporation | Method to reduce stress from trench structure on SOI wafer |

| JPH06268054A (ja) * | 1993-03-10 | 1994-09-22 | Nippondenso Co Ltd | 半導体装置 |

| US5344524A (en) * | 1993-06-30 | 1994-09-06 | Honeywell Inc. | SOI substrate fabrication |

| KR100187678B1 (ko) * | 1993-11-23 | 1999-06-01 | 김영환 | 반도체 장치의 소자 분리막 형성방법 |

-

1996

- 1996-12-19 TW TW085115678A patent/TW309647B/zh not_active IP Right Cessation

- 1996-12-24 DE DE19654301A patent/DE19654301B4/de not_active Expired - Fee Related

- 1996-12-25 JP JP08356109A patent/JP3120275B2/ja not_active Expired - Fee Related

- 1996-12-26 US US08/773,163 patent/US5907783A/en not_active Expired - Lifetime

- 1996-12-27 GB GB9626976A patent/GB2309585B/en not_active Expired - Fee Related

- 1996-12-30 CN CN96123935A patent/CN1075242C/zh not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5434444A (en) * | 1987-02-26 | 1995-07-18 | Kabushiki Kaisha Toshiba | High breakdown voltage semiconductor device |

| EP0562127A1 (en) * | 1991-10-14 | 1993-09-29 | Nippondenso Co., Ltd. | Method for fabrication of semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| GB2309585A (en) | 1997-07-30 |

| DE19654301B4 (de) | 2005-03-03 |

| JPH1027894A (ja) | 1998-01-27 |

| GB2309585B (en) | 2000-10-25 |

| JP3120275B2 (ja) | 2000-12-25 |

| GB9626976D0 (en) | 1997-02-12 |

| CN1162835A (zh) | 1997-10-22 |

| US5907783A (en) | 1999-05-25 |

| DE19654301A1 (de) | 1997-07-03 |

| TW309647B (zh) | 1997-07-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5391911A (en) | Reach-through isolation silicon-on-insulator device | |

| US6319333B1 (en) | Silicon-on-insulator islands | |

| US6524929B1 (en) | Method for shallow trench isolation using passivation material for trench bottom liner | |

| JP3208575B2 (ja) | 半導体装置の製法 | |

| CN1075242C (zh) | Soi基片及其制造方法 | |

| CN1875482A (zh) | 制造鳍型场效应晶体管的方法 | |

| CN1577803A (zh) | 制造快闪存储装置的方法 | |

| JP2655469B2 (ja) | 半導体集積回路装置の製造方法 | |

| CN1199256C (zh) | 利用绝缘衬垫防止窄器件中的阈值电压的滚降 | |

| JPH10335441A (ja) | 半導体装置の製造方法 | |

| JP3362588B2 (ja) | 半導体装置の製造方法 | |

| CN1992194A (zh) | 增强的浅沟槽隔离结构及其制作方法 | |

| CN1078739C (zh) | Soi基片及其制造方法 | |

| JPS5898943A (ja) | 半導体装置の製造方法 | |

| JPH0621210A (ja) | 半導体装置の製造方法 | |

| CN1121064C (zh) | 制造半导体器件的方法 | |

| CN1229860C (zh) | 中空沟槽隔离物及其制造方法 | |

| KR100475050B1 (ko) | 스페이서로보호되는박막의질화막라이너를갖는트렌치소자분리방법및구조 | |

| US7297577B2 (en) | SOI SRAM device structure with increased W and full depletion | |

| JPS6255700B2 (zh) | ||

| CN1078737C (zh) | Soi基片的制造方法 | |

| KR100475049B1 (ko) | 박막의질화물라이너를갖는트렌치소자분리방법 | |

| KR100344765B1 (ko) | 반도체장치의 소자격리방법 | |

| JP2000031489A (ja) | 半導体装置の製造方法 | |

| KR970023991A (ko) | Y자형 트렌치를 이용한 반도체 소자의 분리 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20011121 Termination date: 20131230 |