CN100565698C - 具有多比特预取输出数据通路的装置及其操作方法 - Google Patents

具有多比特预取输出数据通路的装置及其操作方法 Download PDFInfo

- Publication number

- CN100565698C CN100565698C CNB028097483A CN02809748A CN100565698C CN 100565698 C CN100565698 C CN 100565698C CN B028097483 A CNB028097483 A CN B028097483A CN 02809748 A CN02809748 A CN 02809748A CN 100565698 C CN100565698 C CN 100565698C

- Authority

- CN

- China

- Prior art keywords

- data

- bit

- signal

- data bit

- output channel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

- G11C7/1066—Output synchronization

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/4076—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

- G11C7/1012—Data reordering during input/output, e.g. crossbars, layers of multiplexers, shifting or rotating

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1015—Read-write modes for single port memories, i.e. having either a random port or a serial port

- G11C7/1039—Read-write modes for single port memories, i.e. having either a random port or a serial port using pipelining techniques, i.e. using latches between functional memory parts, e.g. row/column decoders, I/O buffers, sense amplifiers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1051—Data output circuits, e.g. read-out amplifiers, data output buffers, data output registers, data output level conversion circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/222—Clock generating, synchronizing or distributing circuits within memory device

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2207/00—Indexing scheme relating to arrangements for writing information into, or reading information out from, a digital store

- G11C2207/22—Control and timing of internal memory operations

- G11C2207/2281—Timing of a read operation

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Databases & Information Systems (AREA)

- Dram (AREA)

- Transition And Organic Metals Composition Catalysts For Addition Polymerization (AREA)

- Prostheses (AREA)

Abstract

一种通过多条数据通路将多个数据比特从存储单元传送到数据缓冲区的方法。每条所述通路并行接收这些数据比特并从中选择一个比特。来自每条所述输出通路的所选比特传送到选定的输出端。根据两个使能信号的交替相位顺序地激活多个定时信号,以便将来自输出选择器的数据比特串行传送到数据缓冲区。

Description

技术领域

本发明一般地涉及集成电路,具体说涉及存储器件中的数据通路。

背景技术

半导体存储器件如同步动态随机访问存储器(SDRAM)器件广泛应用于计算机和电子产品中。SDRAM器件一般具有用于存储数据的大量存储单元。为了读取数据,执行存储器读操作。在读操作期间,访问存储单元的数据并将其输出到数据缓冲区以便处理。SDRAM的操作基于公用时钟信号。

SDRAM器件有几种类型。在一种类型中,在每个时钟周期访问存储单元的数据并将其中的一比特数据输出到数据缓冲区。在SDRAM的另一种类型中,在每个时钟周期中访问两个数据比特并将其输出到数据缓冲区;因此,这种类型的SDRAM器件通常称之为两倍数据率(DDR)SDRAM器件。

电子设备工程联合委员会(JEDEC)目前已经提出了一种新型SDRAM器件,该国际组织制订包括存储器件的集成电路器件的标准。JEDEC建议的这种类型的SDRAM器件的规范草案通过引用结合到本说明书中。在所建议的SDRAM器件或DDR II型SDRAM器件中,在读周期内访问存储器件中的四个数据比特并将其输出到数据缓冲区。因此,DDR II SDRAM器件输出数据的速度高于传统的DDR SDRAM器件。

操作DDR II SDRAM器件的难题之一是,要这样实现这种器件,使得存储单元的四个数据比特正确输出到数据缓冲区。在DDR IISDRAM器件中,由于每次访问一个两比特数据组,所以,在一个时钟周期中可以把一个组的两比特输出到数据缓冲区中。在下一个时钟周期中,下一个两比特组也可以采用同前面一组相同的方式输出到数据缓冲区。因此,在每两个时钟周期中,有四个比特输出到数据缓冲区;这四个比特来自两个不同的组。在DDR II SDRAM器件中,一次访问一个四比特组并在两个时钟周期内将其输出到数据缓冲区,这两个时钟周期中每个时钟周期内分别输出两个比特。但是,不像DDR SDRAM,由于四个比特来自同一组,故DDR II SDRAM器件必须区分在两个时钟周期中的哪一个时钟周期输出这四个比特中的哪两个比特。此外,必须确定正确的比特顺序以便这四个比特中的每个比特按照正确顺序输出到数据缓冲区。

故需要在DDR II SDRAM中实现:在读操作期间,将数据从存储单元正确地输出到数据缓冲区。

发明内容

本发明是一种DDR II SDRAM器件,它具有在存储器件的存储单元和数据缓冲区之间实现数据传送的输出电路。

按照本发明的第一方面,提供了一种集成电路,包括:多条输出通路,用于接收第一、第二、第三和第四数据比特构成的数据比特组,所述数据通路中每条数据通路并行接收所述数据比特;与所述输出通路相连的输出选择器,用于从所述输出通路接收所述数据比特;以及输出级,用于接收由所述输出选择器传送的数据比特,以便在2个时钟信号周期内以序列形式将所述数据比特输出到数据缓冲区,其中,所述序列中的第一和第三数据比特在第一使能信号的交替相位下输出,而所述序列中的第二和第四数据比特在第二使能信号的交替相位下输出,其中,所述第一和第二使能信号不是同步的。

按照本发明的第二方面,提供了一种集成电路,包括:多条输出通路,其中每条所述输出通路包括:多个输入节点,用于接收一组数据比特;输入选择器,用于提供从所述数据比特中选定的数据比特;与所述输入选择器相连的第一锁存器,用于接收所述选定的数据比特;和与所述第一锁存器相连的第二锁存器,用于从所述第一锁存器接收所述选定的数据比特,其中,来自每一条所述输出通路的所述选定的数据比特是不同的;与所述输出通路相连的输出选择器,用于从每一条所述输出通路接收所述选定的数据比特;以及与所述输出选择器相连的输出级,所述输出级从所述输出选择器串行接收选定的比特并在2个时钟周期内将所述选定的比特提供给数据缓冲区。

按照本发明的第三方面,提供了一种集成电路,包括:多个输入节点,用于并行接收M个数据比特构成的数据比特组;数据缓冲区;以及连在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中的每条输出通路传送所述M个数据比特构成的数据比特组中的不同比特,其中,通过激活多个定时信号将所述M个数据比特构成的数据比特组传送到所述数据缓冲区,第一和第二使能信号在不同时刻激活所述定时信号,其中,所述各使能信号不同步,以及M和N大于2。

按照本发明的第四方面,提供了一种存储器件,包括:多个存储单元,用于存储多个数据比特;多条输出通路,用于从所述存储单元接收由第一、第二、第三和第四数据比特构成的数据比特组,所述输出通路中每条输出通路并行接收所述数据比特;与所述输出通路相连的输出选择器,用于从所述输出通路接收所述数据比特;以及输出级,用于接收由所述输出选择器传送的数据比特以在2个时钟信号周期内将所述数据比特以串行序列形式输出到数据缓冲区,其中,在第一使能信号的交替相位下输出所述序列中的第一和第三数据比特,而在第二使能信号的交替相位下输出所述序列中的第二和第四数据比特,其中,所述第一使能信号和第二使能信号不同步。

按照本发明的第五方面,提供了一种存储器件,包括:多个存储单元,用于存储多个数据比特;多条数据通路,每条所述数据通路包括:多个输入节点,用于从所述存储单元接收数据比特组;输入选择器,用于提供从所述数据比特中选出的比特;与所述输入选择器相连的第一锁存器,用于接收所述选定的比特;以及与所述第一锁存器相连的第二锁存器,用于从所述第一锁存器接收所述选定的比特,其中,从每条所述输出通路接收的所述选定的比特是各不相同的;与所述输出通路相连的输出选择器,用于从所述输出通路中每条输出通路接收所述选定的比特;以及与所述输出选择器相连的输出级,所述输出级从所述输出选择器串行接收选定的比特并在2个时钟周期内将所述选定的比特提供给数据缓冲区。

按照本发明的第六方面,提供了一种存储器件,包括:多个存储单元,用于存储多个数据比特;多个输入节点,用于从所述存储单元并行接收M个数据比特构成的数据比特组;数据缓冲区;以及连接在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中每条输出通路传送所述M个数据比特构成的数据比特组,其中,通过激活多个定时信号将所述M个数据比特构成的数据比特组串行传送到所述数据缓冲区,由第一和第二使能信号在不同时刻激活所述各定时信号,其中,所述使能信号不同步,且M和N大于2。

按照本发明的第七方面,提供了一种系统,包括:处理器;以及与所述处理器相连的存储器件,所述存储器件包括:多个存储单元,用于存储多个数据比特;多个输入节点,用于从所述存储单元并行接收M个数据比特构成的数据比特组;数据缓冲区;以及连接在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中每条输出通路传送所述M个数据比特构成的数据比特组,其中,通过激活多个定时信号而将所述M个数据比特构成的数据比特组串行传送到所述数据缓冲区,由第一和第二使能信号在不同时刻激活所述各定时信号,其中,所述使能信号不同步,且M和N大于2。

按照本发明的第八方面,提供了一种操作存储器件的方法,所述方法包括:访问存储单元中的M个数据比特,其中M大于2;将所述M个数据比特并行传送到输出电路;以及在两个时钟信号周期内根据第一和第二使能信号,从所述输出电路将所述M个数据比特串行输出到数据缓冲区,其中,所述第一使能信号允许将偶数据比特输出到所述数据缓冲区,而所述第二使能信号允许将奇数据比特输出到所述数据缓冲区,其特征在于还包括:接收地址比特;根据所述地址比特中一些比特的逻辑值确定传送顺序;以及根据所述传送顺序将所述M个数据比特从所述输出电路传送到所述数据缓冲区。

按照本发明的第九方面,提供了一种传送数据的方法,所述方法包括:并行读取M个数据比特到多条输出通路,其中M大于2;将所述M个数据比特从所述输出通路传送到输出选择器,其中,所述输出通路中每条输出通路传送不同的数据比特;激活第一和第二使能信号;根据所述第一和第二使能信号顺序地激活多个定时信号;在所述各定时信号发生转换之后将所述M个数据比特顺序传送到输出级;以及在两个时钟信号周期内将所述M个数据比特输出到数据缓冲区。

附图说明

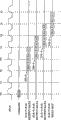

图1是根据本发明一个实施例的存储器件的框图;

图2是各种延迟设置下存储器操作期间图1所示存储器件的时序图;

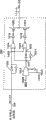

图3是图1的输出电路的框图;

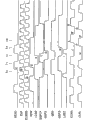

图4-7是图3所示输出电路在各种延迟设置下的工作时序图;

图8A-D是图3所示输入选择电路的原理图;

图9是图3的输出电路的锁存器的原理图;

图10是图3的输出级的原理图;

图11是图1的输出控制器的框图;

图12是图11的延迟输入电路的原理图;

图13是图11的输出定时使能电路的原理图;

图14是图11的输出定时发生器的原理图;

图15是图11的传播控制信号发生器的原理图;

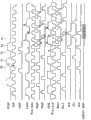

图16是图12-13所示电路的操作的时序图;

图17是图14-15所示电路的操作的时序图;

图18是根据本发明一个实施例的系统的框图。

具体实施方式

以下的详细说明涉及构成本说明书一部分的附图,并通过图解说明可实施本发明的具体实施例。对这些实施例作了足够详细的说明,以使本领域的技术人员能够实施本发明,还应理解,可以利用其它实施例,并且可以进行逻辑的、机械的和电气的变化而不会背离本发明的精神和范围。因此不应从限制意义上理解以下详细说明,本发明的范围仅由所述权利要求书来加以限定。

图1是根据本发明一个实施例的存储器件100的简化框图。在一个实施例中,存储器件100包括主存储器102。主存储器102一般包括动态随机访问存储(DRAM)器件,它包括一个或多个存储体,用存储体1-N表示。存储体1-N中每个存储体包括多个按照行和列的形式排列的存储单元。行译码器104和列译码器106响应地址总线或地址线1100-X上提供的地址而访问各存储单元。地址线1101-X接收多个地址信号A0-A2。多个输入电路1100-N和多个输出电路1120-N连接到数据总线即数据线1140-N,以便与主存储器102进行双向数据通信。数据线1140-N中每条数据线提供多个数据信号或多个数据比特D0-DN。输出控制器117控制从主存储器102到数据缓冲区1140-N的数据输出的定时。存储器控制器116响应通过控制线118提供的控制信号而控制存储器100。控制信号包括但不限于外时钟信号(CLK)、片选(CS*)、行访问脉冲(RAS*)、列访问脉冲(CAS*)和写使能(WE*)。存储器件100还包括模式寄存器119,可以对其编程以存储存储器件100的操作所用的各种设置。

本领域的技术人员应理解,图1所示的存储器件可以包括额外的电路和控制信号,并且图1所示的存储器件已经简化以有助于将重点集中到本发明上。应理解,以上对DRAM的说明旨在提供对存储器的一般性的理解,而不是对DRAM器件所有特征和要素的完整说明。

在此整个说明书中,诸如数据、比特、数据比特之类的比特可以互换用于描述同一主题,即从主存储器102读出或写入其中的信息或信号。而且,术语线或节点也可互换使用;它们的含义相同。

图2是在各种延迟设置下存储器操作期间图1所示电路的时序图。在图2中,CLK表示通过图1所示控制线118之一加到存储器件100的外时钟信号。在一个实施例中,存储器件100可以用频率范围在66MHZ到300MHZ之间的CLK信号来操作。COMMAND(指令)表示加到存储器件100上用于执行某些存储器件操作如读操作的指令。OUTPUT DATA(输出数据)2100-3表示在图1所示线1140-N之一上提供的输出数据。OUTPUT DATA 2100-3中每个数据表示在不同延迟设置下的输出数据。延迟设置通过对图1所示模式寄存器119编程来实现。当读指令发出之后第一数据比特在数据线1140-N之一上可用时,不同的延迟设置提供不同的定时。例如,如果延迟设为2,则READ(读)指令发出后隔两个时钟周期后,第一数据比特D1可用。在图2中,READ指令出现在T0时刻,则OUTPUT DATA 210-0的第一数据比特D1在T2时刻可用,T2在READ指令发出后隔两个时钟周期处。类似地,OUTPUT DATA指示如果延迟设置为3、4或5,则第一数据比特在T3、T4或T5时刻可用,这三个时刻分别在READ指令出现之后隔3个时钟周期、4个时钟周期或5个时钟周期处。延迟设置的选择取决于存储器件100外部的变量。

图1所示的存储器件100可用在读操作的每个读突发中输出4个数据比特的序列。在读操作中,存储器控制器116检查例如信号RAS*、CAS*和WE*指令的组合信号。如果对读操作而言该组合信号有效,则发出读指令。例如,在图2中时刻T0处,在读操作的指令组合有效后,就发出READ指令。读取主存储器102(见图1)中的4个数据比特并将其输出到输出电路112 0-N之一。读取主存储器102中的4个数据比特可以采用任何常规读方法完成。在4个数据比特被读到输出电路112 0-N之一后,将这些比特串行输出到数据线114 0-N之一。这4个数据比特输出到线114 0-N的定时由输出控制器117根据延迟设置来控制。如图2所示,OUTPUT DATA 210 0-3中每个输出数据的4个数据比特D0-D3基于不同的延迟设置在读指令出现之后隔不同的时钟周期输出。输出电路1120-N和输出控制器117及其操作在随后附图中予以更详细的说明。

图3是图1所示输出电路112 0-N之一的框图。图3显示输出电路112-0。其它输出电路的结构与图3所示输出电路112-0的相同。输出电路112-0具有多条输出通路310 0-3。输出选择器350通过线或节点342 0-3连接到输出通路310 0-3。输出级360通过线356连接到输出选择器350。输出级360连接到线114-0以提供多个数据比特D0-DN。

输出通路310 0-3包括多个输入选择器320 0-3。多个第一锁存器330 0-3通过线322 0-3连接到输入选择器320 0-3。多个第二锁存器340 0-3通过线332 0-3分别连接到第一锁存器330 0-3并且通过线342 0-3分别连接到输出选择器350。输出通路310 0-3的构造彼此相同,因此,输出通路310 0-3中每一个均具有相同元件。例如,输出通路310-0具有输入选择器320-0,它通过线322-0连接到第一锁存器330-0。第二锁存器340-0通过线332-0连接到第一锁存器330-0并且通过线342-0连接到输出选择器350。其它输出通路310 1-3与输出通路310-0的配置相同。

输入选择器320 0-3中每一个选择器连接到多个输入节点326以接收多个数据信号即数据比特D0-D3。这些数据比特是补码数据。换句话说,这些数据比特中每一个数据比特均是主存储器102的真实数据比特的逆。在节点326处并行接收数据比特D0-D3。换句话说,比特D0-D3在同一时刻从主存储器102到达节点326。输入选择器320 0-3中每一个输入选择器还连接到多条选择线328以接收多个选择信号CA0-CA3。第一锁存器330 0-3中每一个锁存器均连接到控制线334。第二锁存器340 0-3中每一个锁存器均连接到控制线344。控制线334和344接收多个传播控制信号Q0-Q2。所有第一锁存器的控制线334接收信号Q2。第二锁存器340 0-1的控制线344接收信号Q0。第二锁存器3402-3的控制线344接收信号Q1。

输出选择器350包括多个多路复用器352 0-3。多路复用器352 0-3中每一个多路复用器的输入端连接到节点342 0-3之一,而其输出端通过线356连接到输出级360。多路复用器352 0-3还连接到多条控制线354以接收多个定时信号DLL 0-3。

在图3中,输入选择器3200-3中每一个选择器通过线326选择上4个数据比特D0-D3之一并将所选比特传送给相应线3220-3之一。从比特D0-D3中选择一个数据比特是基于通过线1100-X(见图1)接收的两个地址信号或地址比特。通过线110-X接收的地址比特分别是A0、A1、A3、...,AX。比特A1和A0的逻辑值(逻辑1或逻辑0)通过输入选择器3200-3确定对数据比特的选择。如果A1和A0的逻辑值为0和0(二进制00),则通过输入选择器3200-3选出的数据比特分别是D0、D1、D2和D3。换句话说,如果A1A0的组合是00,则输入选择器320-0选择比特D0;输入选择器320-1选择比特D1;输入选择器320-2选择比特D2;以及输入选择器320-3选择比特D3。如果A1A0的组合是01,则输入选择器3200-3选择的数据的顺序分别为D1、D2和D3、D0。如果A1A0的组合是10,则输入选择器320 0-3选择的数据的顺序分别为D2、D3、D0和D1。如果A1A0的组合是11,则输入选择器320 0-3选择的数据的顺序分别为D3、D0、D1和D2。例如,如果A1A0的组合是00,则在图3中,则输入选择器320 0-3选择到线322 0-3的4个不同的数据比特分别是D0、D1、D2和D3。

锁存器330 0-3和340 0-3由信号QL0-QL2控制。当激活信号QL0-QL2时,锁存器330 0-3或340 0-3将数据信号或数据比特从一个节点传送给另一个节点。当激活信号QL2时,或者它从低信号电平(低电平)转换为高信号电平(高电平)时,第一锁存器330 0-3将数据从节点322 0-3传送给节点332 0-3。当激活信号QL0时,第二锁存器340 0-1将数据从节点332 0-1传送给节点342 0-1。当激活信号QL1时,第二锁存器340 2-3将数据从节点332 2-3传送给节点342 2-3。在以上示例中,在QL0-QL3被激活后,比特D0-D3从线322 0-3传送到节点332 0-3并最终到达节点342 0-3。

输出选择器350对节点342 0-3上的数据比特进行选择并将其顺序传送给输出级。顺序激活定时信号DLL0-DLL3以便将节点342 0-3上的数据比特经由线356传送给输出级360。因此,输出选择器350将数据比特顺序传送给输出级360。传送给输出级360的序列中的第一数据比特是输出通路310-0的线342-0上的数据比特。传送给输出级360的第二数据比特是输出通路310-2的线342-0上的数据比特。以这种模式,第三和第四比特分别从线342-2和342-3传送给输出级360。在以上示例中,传送给输出级360的第一比特是D0。传送给输出级360的第二比特、第三比特和第四比特分别是D1、D2和D3。

输出级360通过线356接收数据比特并将其串行输出到线114-0。利用以上示例,线114-0上的输出数据比特分别是D0、D1、D2和D3。输出级360通过线114-0输出原码形式的数据比特D0-D3。换句话说,线114-0上的输出数据的电位与线326上数据的相反。本示例中所用数据比特的顺序为D0、D1、D2和D3。但是,正如上述,根据地址比特A1和A0的逻辑值,数据比特的顺序可以是任何顺序。例如,如果线3420-3上的数据分别是D1、D2、D3和D0,则以相同顺序将这些数据传送给输出级360。在这种情况下,输出级360还将这些输出数据比特以同样的顺序输出到线114-0,即D1、D2、D3和D0。总之,如果地址比特A1A0的组合是00,则线114-0上数据的输出顺序分别为D0、D1、D2,和D3。如果A1A0为01,则输出数据为D1、D2、D3和D0。如果A1A0为10,则输出数据为D2、D3、D0和D1。如果A1A0为11则输出数据为D3、D0、D1和D2。

图4是延迟设置为2时图3所示输出电路112-0的操作的时序图。在图4中,CA信号表示通过线328接收的CA0-CA3信号之一。QL0、QL1和QL2信号表示在图3中第一锁存器330和第二锁存器340处接收的相同信号。DLL0、DLL1、DLL2和DLL3表示通过输出选择器350的线354接收的相同信号。输出数据D0、D1、D2和D3表示通过线114-0输出的数据D0-D3。

这里结合图4描述图3所示电路的操作。参照图4,READ指令在时刻T0发出。从存储单元102(图1)读取4个数据比特。4个数据比特顺序传送到图3输出电路112-0的数据通路3100-3。数据通路3100-3的输入选择器3200-3通过线326接收这4个数据比特D0-D3。在线326上,这4个数据比特以其补码形式表示。在图4中的TA时刻,信号CA切换为高电平,这允许输入选择器320 0-3中每一个选择器通过线326从4个比特D0-D3中选择一个数据比特。所选数据比特被传送到线322 0-3。为了说明本发明,假定A1A0是00。因此,传送给线322 0-3的这4个数据比特分别是D0、D1、D2和D3。换句话说,线322-0传送比特D0;线322-1传送比特D1;线322-2的传送比特D2;以及线322-3传送D3。

在延迟设置为2时,信号QL2总为高电平。如图4所示,从READ指令开始到其后所有时钟周期,QL2信号一直是高电平。因为QL2为高电平,故线3220-3上的D0-D3通过锁存器3300-3传送给节点3320-3。在时刻TA,QL0信号切换为高电平。这允许比特D0和D1从节点332 0-1通过第二锁存器340 0-1传送给节点342 0-1。在时刻TB,QL1切换为高电平。这允许比特D2和D3从节点322 2-3通过第二锁存器340 2-3传送给节点342 2-3。

在输出选择器350,多路复用器352 0-3由定时信号DLL0-DLL3控制。顺序激活DDL0-DLL3信号,使得节点3420-3上的比特D0-D3可以根据延迟设置正确地输出到线114-0上。因为延迟设置为2,故在读指令发出后隔2个时钟周期通过线114-0输出第一数据比特。在这种情况下,所述第一数据比特在时刻T2出现。为了传送节点342-0上的第一比特,激活DLL0信号。这允许比特D0从节点342-0传送到节点356,然后再传送到线114-0上。因为从节点342-0到节点114-0存在传播延迟,故恰好在时刻T2前激活信号DLL0,以便当比特D0出现在线114-0上时,信号DLL0与信号CLK的上升沿在时刻T2处对齐。在图4中,在时刻T2前激活DLL0或使其切换为高电平。这使比特D0(原码形式)能够在时刻T2与CLK信号的上升沿对齐。类似地,在时刻T3前激活DLL2(为高电平)以使比特D2在时刻T2与CLK信号的上升沿对齐。以相同方式,信号DLL1和DLL3分别在时刻T2.5和T3.5前被激活(为高电平)以便使比特D1和D3分别在时刻T2.5和T3.5与CLK信号的下降沿对齐。

图5是图3所示输出电路112-0在延迟设置为3时的工作时序图。在延迟设置为3时,在READ指令发出之后隔3个时钟周期输出数据的第一比特出现在线114-0上。在图5中,D0在时刻T3出现,T3在时刻T0发出READ指令之后隔3个时钟周期处。在延迟设置为3时,通过线326接收的数据比特D0-D3以与延迟设置为2时的相同方式输出到线114-0上。延迟设置为2与延迟设置为3之间的差异在于信号CA、QL0、QL1和DLL0-DLL3的定时。因为延迟设置为3时输出数据出现在线114-0上比延迟设置为2时输出数据的出现迟一个时钟周期,故信号CA几乎要迟一个时钟周期才被激活。在图5中,CA信号在时刻TA被激活(为高电平)时,此TA比图4所示TA迟几乎一个时钟周期。与延迟设置为2时的情况相同,QL2在整个读周期期间保持高电平。但是,其它信号比图5所示的要迟几乎一个时钟周期。

图6是图3所示输出电路112-0在延迟设置为4时的工作时序图。在延迟设置为4时,在READ指令发出之后隔4个时钟周期输出数据的第一比特出现在线114-0上。在图6中,D0在时刻T4出现,T4在时刻T0发出READ指令之后隔4个时钟周期处。在延迟设置为4时,通过线326接收的数据比特D0-D3以与延迟设置为2时的相同方式输出到线114-0上。但是,这里提供了不同的定时方案以确保还可以正确地输出一个4比特组中的最后一比特和下一个4比特组的第一比特。因此,与延迟设置为2和3的情况不同,QL2信号并不总是高电平。

在图6中,QL0和QL1的虚线部分表示来自前一个读周期的信号。在600和601处的虚线信号表示QL0和QL1信号以前的转换。在604和605处的信号表示当前读周期中QL0和QL1信号的当前转换。在602处的信号表示QL2信号的当前转换。在图3中,为确保当前读周期的当前比特D0-D3不与之前读周期中的在前比特D0-D3相混淆,节点3320-3上的在前比特D0-D3必须在当前比特D0-D3到达节点3320-3之前传送到节点3420-3。因此,QL2必须在QL0信号的转换和QL1信号的转换之间被激活。换句话说,QL2必须在前一读周期中QL0的转换之后和当前读周期中QL0的转换之前被激活。

如图6所示,QL2在602进行转换,即600处QL0的转换之后和604处QL0的转换之前。类似地,602处QL2也在601处QL1的转换之后和605处QL1的转换之前。因此,当QL2在602处进行转换时,当前比特D0-D3通过线3220-3传送到节点3320-3。到这时(602处),以前的比特D0-D3已不迟于600处QL0的转换和601处QL1的转换传送到节点3420-3。因此,在延迟设置为4时通过正确地激活各信号QL0-QL3,输出电路112-0可正确处理所有读周期中的比特D0-D3。

图7是图3所示输出电路112-0在延迟设置为5时的工作时序图。在延迟设置为5时,在READ指令发出之后隔5个时钟周期输出数据的第一比特出现在线114-0上。在图7中,D0在时刻T5出现,T5在时刻T0发出READ指令之后隔5个时钟周期处。在延迟设置为5时,通过线326接收的数据比特D0-D3以与延迟设置为2时的相同方式输出到线114-0上。延迟设置为5时输出通路112-0的操作定时与延迟设置为4时类似。类似于图6,图7中的虚线信号表示来自前一个读周期的信号。在图7中,信号QL2在702处被激活也即转换为高电平。该转换在704和705处QL0和QL1的转换之前以及700和701处QL0和QL1的转换之后。到那时(702处),以前的比特D0-D3已不迟于700处QL0的转换和701处QL1的转换传送到节点3420-3。因此,在延迟设置为5时通过正确地激活各信号QL0-QL3,输出电路112-0就可正确地处理所有读周期中的比特D0-D3。

图8A-D是图3所示输入选择器320 0-3的原理图。图8A-D所示输入选择器320 0-3中每一个输入选择器具有多个多路复用器8100-3。为简单起见,不同输入选择器320 0-3之间的多路复用器的标号是相同的。在图8A中,多路复用器810 0-3中每一个多路复用器具有连接到相应的输入线326之一的输入端,该输入接收数据比特D0-D3之一。多路复用器810 0-3还具有多个连接到节点812的输出端。存储单元814具有在节点812处与多路复用器810 0-3的输出端相连的第一存储节点和与节点322 0-3之一相连的第二存储节点。多路复用器810 0-3中每一个多路复用器由通过线328接收的信号CA0-CA3之一控制。

在图8B-D中,输入选择器310 1-3的配置与图8A所示输入选择器310-0的配置相同。但是,输入选择器310 1-3的输入端分别按不同顺序接收D0、D1、D2和D3。在图8B中,输入端326-0、326-1、326-2和326-3接收的D0-D3的顺序分别是D1、D2、D3和D0。在图8C中,输入326-0、326-1、326-2和326-3接收的信号D0-D3的顺序分别是D2、D3、D1和D0。在图8D中,输入326-0、326-1、326-2和326-3接收的信号D0-D3的顺序分别是D3、D0、D1和D2。

图8A-D所示输入选择器3200-3的工作机制是相同的。当CA 0-3信号之一被激活时,由该已激活的CA信号控制的相应多路复用器将比特D0-D3之一从节点326传送到节点812以及节点3220-3之一。例如,在图8A中,如果CA0被激活也即转换为高电平,则多路复用器810-0将比特D0从节点326传送到节点812和节点322-0。如果CA1被激活,则将比特D1传送到节点322-0。类似地,如果CA2或CA3被激活,则将比特D2或D3传送到节点322-0。

每次只有信号CA 0-3之一被激活。激活信号CA 0-3的顺序取决于地址比特A1和A0的逻辑值。如果AA0是00,则激活CA0;如果A1A0为01,则激活CA1。如果A1A0为10,则激活CA2;以及如果A1A0为11,则激活CA3。这些顺序与图3所示数据比特D0-D3的选择顺序一致。例如,如果A1A0为10,则激活CA2。在图8A中,由信号CA2控制的多路复用器810-2将D2传送到节点322-0。比特D2是序列中的第一比特。在图8B中,亦由信号CA2控制的多路复用器810-2将D3传送到节点322-1。比特D3是序列中的第二比特。类似地,图8C和8D中的多路复用器810-2将比特D0和D1分别传送到节点322-2和322-3。因此,当A1A0为10时,则激活信号CA2,使输入选择器3200-3选择比特D2、D3、D1和D0。这与图3所示输入选择器320 0-3的选择一致。

图9是图3所示输出通路310-0的第一锁存器330-0的原理图。锁存器330-0具有多路复用器912,它通过线916连接到存储单元914。多路复用器912包括与节点322-0相连的输入端D和与节点916相连的输出端。多路复用器912在其时钟端或CLK端与线334相连以接收QL2信号。多路复用器912还连接到线915,线915又连接到反相器917的输出端。反相器917还通过线334接收QL2信号并在线915上产生互补信号QL2*。存储单元914具有与节点916相连的第一存储节点Q和与线332-0相连的第二存储节点Q*。图9仅显示了输出通路310-0的第一锁存器330-0,然而,其它输出通路310 1-3的第一锁存器330 1-3和第二锁存器340 0-3均与图9所示的锁存器330-0相同。因此,图3所示其它第一和第二锁存器的工作机制与图9所示锁存器330-0的工作机制相同。

参照图9,当信号QL2未被激活时,多路复用器912禁止(closed),防止线322上的数据信或号通过多路复用器912。当信号QL2被激活时,多路复用器912工作(opened),允许线322上的数据信或号通过多路复用器912传送到线916和332-0。当信号从一种信号电平变换到另一种信号电平时信号被激活。在本示例中,当QL2从低信号电平转换为(或切换为)高电平信号时信号被激活。因此,在图9中,当QL2从低电平切换到高电平时,线322-0上的数据被传送到线332-0上。类似地,在图3中,当QL0和QL1被激活时,线3320-3上的数据经锁存器3400-3传送到线3420-3上。

图10是图3所示输出级360的原理图。输出级360包括连接到节点356的存储单元1002以便从输出选择器350接收数据比特D0-D3。存储单元1002还在节点1008处与“或非”门1004的第一输入端和“与非”门1006的第一输入端相连。“或非”门1004的第二输入端在节点1010处与存储单元1014相连。“与非”门的第二输入端在节点1012处与存储单元1014相连。“或非”门1004的输出端通过反相器1016与P沟道晶体管1020的栅极相连。“与非”门1006的输出端通过反相器1018与N沟道晶体管1022的栅极相连。晶体管1020还具有与电源相连的源极和与数据缓冲区114-0相连的漏级。晶体管1022还具有接地的漏级和与数据缓冲区114-0相连的源极。信号DLL0在节点1026处提供,节点1026与多路复用器1024相连。多路复用器1024具有用于接收节点1028处信号QED的输入端和与节点1010相连的输出端。

在工作时,存储单元1002顺序接收数据比特D0-D3,并将它们传送到节点1008,节点1008是“或非”门1004和“与非”门1006的第一输入端。在一定时刻,例如,在图4中所示时刻TB,DLL0转换为高电平。这使多路复用器1024将信号QED传送到节点1010和1012。“或非”门1004和“与非”门1006确定节点1010和1012处QED信号与节点1008处信号的组合信号,以便要么使晶体管1020导通要么使晶体管1022导通。如果晶体管1020导通,则节点114-0被拉高到电源电平(高电平)。如果晶体管1022导通,则节点114-0被拉低到地电平(低电平)。节点114-0处的高电平或低电平表示数据D0-D3之一,它是从线326上接收的相应的补码数据比特D0-D3之一的反相信号。

图11是图1所示输出控制器117的框图。输出控制器117包括延迟输入电路1110,该电路接收线1112-1115上的多个延迟信号LATE2-LATE5、线1116上的读信号RDW和线1118上的延迟锁定环时钟信号。延迟输入电路1110在线1120-1123上具有多个输出端,用于提供多个信号QED、QSP2、QSP3,和QSP1*。输出定时使能电路1130通过线1118和1123连接到输入延迟电路1110以接收CLKDQ和QSP1*信号。输出定时使能电路1130分别在线1132上和在线1334上产生第一使能信号CLKL和第二使能信号CLKH。输出定时发生器1150通过线1132和1134连接到输出定时使能电路1130以接收信号CLKL和CLKH。信号CLKL和CLKH使输出定时发生器1150能够在线1552-1155上产生定时信号DLL0-DLL3。DLL0-DLL3信号用于控制图3所示输出选择器350。传播控制信号发生器1170通过线1121-1123连接到延迟输入电路1110和通过线1152-1155连接到输出定时电路1150以接收信号QSP2、QSP3、QSP1*和DLL0-DLL3。传播控制信号发生器1170在线1172-1174上产生QL0-QL2信号。QL0-QL2用于启动图3所示第一锁存器3300-3和第二锁存器3400-3。

在以下说明中,“触发器”指本领域技术人员普遍理解的常用电子元件。以下说明中的触发器是正边沿触发器。虽然这有益于阅读本发明的公开,但本专业的任何普通技术人员可以容易地采用负边沿触发的触发器或其它类型的类似元件来取得相同结果。此外,在以下说明中,“锁存器”或“通过锁存器(pass through latch)”亦指普通的电路元件。锁存器用于将数据或信号从其输入端传送到输出端。以下说明中所描述的锁存器可以类似于图9所示的锁存器330-0。

图12是图11所示延迟输入电路1110的原理图。延迟输入电路1110具有通过锁存器(LAT)1210和多个触发器(FF)1212-1214。锁存器1210和触发器1212-1214通过线1118接收信号CLKDQ。锁存器1210和FF 1212通过线1116接收信号RDW。多个多路复用器1216-1219接收线1112-1115上的LATE2-LATE5以便将RDW信号传送给节点1230。触发器1232具有通过反相器1235连接到节点1230的输入端。触发器1232的输出端在节点1123与锁存器1234的输入端相连,节点1123提供信号QSP1*。锁存器1234具有在节点1122与锁存器1236的输入端相连的输出端,节点1122提供信号QSP2。节点1122还通过串联的反相器1242和1244提供QED信号。锁存器1236的输出端通过反相器1240连接到节点1121以提供信号QSP3。触发器1232、锁存器1234和锁存器1236的时钟输入端还接收信号CLKDQ。

RDW是当输入信号CS*、RAS*和WE*的组合信号有效时由存储器控制电路116产生的信号。LATE2-LATE5信号也是由控制电路116根据延迟产生的信号,所述延迟通过编程保存到存储器件100中。CLKDQ信号由存储器件100的延迟锁定环提供。未显示延迟锁定环,是因为它是常规电路,可以是本领域许多已知类型的延迟锁定环之

在图12中,信号RDW通过锁存器1210或触发器1212-1214之一传播从而产生了信号QSP1*、QSP2和QSP3。如果延迟设置为2,则RDW通过锁存器1216传送到节点1230。如果延迟设置为3或4或5,则RDW信号传送到触发器1212-1214中的一个触发器或两个触发器或三个触发器。信号LATE2-LATE5通过多路复用器1216-1219控制RDW信号到节点1230的传送。

这里结合图16所示时序图描述图12所示延迟输入电路1110的工作机制。为了说明本发明,假定通过对存储器件100编程或设置使其延迟设置为4,因此,只有信号LATE4被激活。在这种情况下,数据的第一比特将在读指令有效之后隔4个周期出现在数据缓冲区114-0。在图16中,预期进行读操作,CLKDQ和CLK信号分别在A和B处转换为高电平。在时刻T0,读指令READ(在C处)转换为高电平,指示新的读操作的开始。随后,在D处,信号RDW切换为高电平。在图12中,在信号RDW传播通过触发器1212和1213之后,LATE4信号启动多路复用器1218以便将信号RDW传送到图12的节点1230。因为RDW信号为高电平,故节点1230处的信号也为高电平。在图16中,节点1230在E处切换为高电平。节点1230处的高电平迫使反相器1235的输出变为低电平。反相器1235输出端处的信号也是触发器1232输入端处的信号。因为CLKDQ为高电平,故触发器1232使其输出信号在节点1123处为低电平,此信号代表QSP1*信号。在图16中,QSP1*在F处切换为低电平。随后,节点1123处的信号传播通过锁存器1234到达节点1122,然后再通过锁存器1236到达节点1121。节点1122处的信号用信号QSP2表示而节点1121处的信号用信号QSP3表示。在图16中,当节点1123处的信号QSP1*为低电平时,它使信号QSP2在G处切换为高电平以及使信号QSP3在H处切换为高电平。此外,节点1120处的信号QED还通过反相器1242和1244跟踪信号QSP2。如图11所示,信号QSP1*、QSP2和QSP3用作到其它电路的输入信号。如图10所示,信号QED用作用于输出数据的选通脉冲信号。

图13是图11所示输出定时使能电路1130的原理图。输出定时使能电路1130具有脉冲电路(PULSE)1315,它连接到线1123以接收信号QSP1*,从而在节点1317处产生锁存器复位信号LRST。触发器1320具有复位RS输入端、时钟CLK输入端、数据输入端D和互补输出端Q和Q*。RS输入端连接到节点1317以接收LRST信号。CLK输入端在节点1312处与延迟电路1314相连以接收延迟版本的CLKDQ信号。输入端D和输出端Q*连接在一起。输出端Q经由反相器1316和1318通过线1132提供信号CLKL。串联的锁存器1322和1324从线1312接收延迟版本的CLKDQ信号并在线1134上提供信号CLKH。节点1134经由包括反相器1332的反馈环连接到输入端D。晶体管1328具有连接到延迟电路1330的门电路,以接收LRST信号的延迟版本。晶体管1328还具有接地的源极和与锁存器1324的复位端RS相连的漏级。当LRST信号被激活(为高电平)时,就使晶体管1328导通并使锁存器1324复位。当锁存器1324复位时,它迫使信号CLKH节点1134为低电平。LRST信号还以同样方式使锁存器1320复位。当LRST信号被激活(为高电平)时,它迫使节点1132上的信号CLKL为低电平。

在图13中,根据信号CLKDQ产生CLKH和CLKL信号。使能信号CLKL和CLKH用于激活信号DLL0-DLL3,信号DLL0-DLL3又使数据能够在读操作期间传送到数据缓冲区114 0-N。为了确保在每次读操作期间正确传送数据,每次收到新的读命令时就激活LRST信号。LRST将信号CLKH和CLKL复位以确保正确传送数据。

再次参照图16,当QSP1*在F处切换为低电平时,由于RDW在D处为高电平表示新的读操作,故脉冲电路在I处产生脉冲LRST。当信号LRST被激活时,它将CLKH和CLKL信号复位到低电平,如J和K所示。在于J和K处复位为低电平之后,CLKH和CLKL信号仅受CLKDQ信号影响并一直到另一次复位。例如,CLKH在L、M和N处恢复其正常转换;CLKL在O、P和Q恢复其正常转换。如图16所示,CLKH和CLKL具有不同相位。换句话说,CLKH和CLKL不同步。CLKH和CLKL信号用于使能图14中的输出定时发生器1150。

图14是图11所示输出定时发生器1150的原理图。输出定时发生器1150具有第一定时电路1410和第二定时电路1420。电路1410和1420的构造相同并通过线1118接收相同的CLKDQ信号。电路1410具有脉冲发生器1416,它通过反相器1411接收CLKDQ的反相信号。脉冲发生器1416在节点1413产生输出信号。节点1413处的信号传送到线1153或1155,表示为信号DLL1或DLL3。从节点1413到线1153或1155的传送由多路复用器1415或1418控制。多路复用器1415和1418由节点1132处的信号CLKL控制。

电路1420具有脉冲发生器1426,它在节点1429其输入端处通过反相器1411接收CLKDQ。脉冲发生器1426在节点1423产生输出信号。节点1423处的信传送到线1153或1155,表示为信号DLL0或DLL2。从节点1423到线1154或1152的传送由多路复用器1425或1428来控制。多路复用器1425和1428由节点1134处的信号CLKH来控制。

一般而言,脉冲发生器1416和1426接收CLKDQ信号并分别在节点1413和1423上产生输出信号。节点1413上的信号通过多路复用器1415或1418变成信号DLL1或DLL3。因此,根据CLKL信号的具体相位,或产生DLL1或产生DLL3。换句话说,DLL1和DLL3在CLKL信号相位交替下被激活。类似地,节点1423上的信号通过多路复用器1425或1428成为信号DLL0或DLL2。因此,根据CLKH信号的具体相位,或产生DLL0或产生DLL2。换句话说,DLL 0和DLL2在CLKH信号相位交替下被激活。CLKH和CLKL信号不同相。这使得它们能够正确地激活各信号DLL0-DLL3,使得可以按正确顺序将数据比特D0-D3输出到数据缓冲区114-0。

图17是图14所示电路的工作时序图。在图17中,节点1423和1413处的信号表示图14所示脉冲发生器1416和1426在节点1423和1413的输出信号。信号CLK、READ、LRST、CLKH和CLKL与图16所示的信号相同。当CLKH信号在J处为低电平时,它启动多路复用器1428以允许节点1423处的信号通过反相器1429。节点1423处的信号这时为低电平,因此,反相器1429的输出信号即DLL0信号为高电平。在图17中,DLL0在S0处被激活,变为高电平。当信号CLKH在L处为高电平时,它启动多路复用器1425以允许将节点1423处的信号传送到反相器1427。节点1413处的信号这时为低电平,因此,反相器1427输出端处的信号即DLL2信号为高电平。在图17中,DLL2在S2被激活为高电平。总结一下,当信号CLKH进行转换时,它激活定时信号DLL0,当信号CLKH进行转换时,它激活定时信号信号DLL2。例如,在图17中,在使能信号CLKH的不同相位期间激活定时信号DLL0和DLL2。在信号CLKH的一个相位期间(当信号CLKH为低电平时)激活DLL0;而在信号CLKH的另一相位期间(当信号CLKH为高电平时)激活DLL2。换句话说,分别在使能信号CLKL的下降沿和上升沿之后激活定时信号DLL0和DLL2。

类似地,当CLKL信号在K处为低电平时,它启动多路复用器1418以允许节点1413处的信号传送到反相器1419。节点1413处的信号这时为低电平,因此,反相器输出端1419处的信号即DLL1信号为高电平。在图17中,DLL1在S1处被激活为高电平。当信号CLKL在O处为高电平时它启动多路复用器1415以允许节点1413处的信号传送到反相器1417。节点1413处的信号这时为低电平,因此,反相器1417的输出端处的信号即DLL3信号为高电平。在图17中,DLL3在S3处被激活为高电平。总结一下,当信号CLKL进行转换时,它激活定时信号DLL1,当信号CLKL进行另一次转换时,它激活定时信号DLL3。换句话说,在使能信号CLKL的不同相位期间激活定时信号DLL1和DLL3。例如,在图17中,在信号CLKL的一个相位期间(当信号CLKL为高电平时)激活DLL1;而在信号CLKL的另一个相位期间(当信号CLKL为低电平时)激活DLL3。换句话说,分别在使能信号CLKL的下降沿和上升沿之后激活定时信号DLL1和DLL3。

在图17中,OUTPUT DATA(输出数据)表示数据缓冲区114-0处输出的数据比特。在延迟为4时,第一数据比特在时刻T4出现。为了说明本发明,假定数据缓冲区114-0处的输出数据采取的传送顺序为D0、D1、D2和D3。因此,D0和D2称为偶数数据比特,而D1和D3称为奇数数据比特。一般而言,在数据缓冲区114-0处输出的数据的4比特序列中,偶数数据比特是第一和第三比特,而奇数数据比特是第二和第四数据比特。在这种情况下,在使能信号CLKH的不同相位使定时信号DLL0和DLL2激活即转换为高电平之后,输出偶数比特D0和D2。换句话说,在使能信号CLKH的交替相位下输出比特D0和D2。类似地,在使能信号CLKL的交替相位下使定时信号DLL1和DLL3激活即转换为高电平之后输出比特D1和D3。换句话说,在使能信号CLKL的交替相位下输出比特D1和D3。

图15是图11所示传播信号发生器1170的原理图。传播控制信号发生器1170具有“或非”门1502用于接收节点1155和1122上的DLL3和QSP2信号。“与非”门1502的输出连接到反相器1504,该反相器的输出连接到节点1172以提供QL0信号。在类似配置中,“与非”门1512分别接收节点1153和1121上的DLL1和QSP3。“与非”门1512的输出连接到反相器1514,该反相器的输出连接到节点1173以提供QL1信号。传播信号发生器1170还接收其他信号,例如LATE2、LATE3、QED、QSP1*、DLL0和DLL3,这些信号由前述其它电路产生。LATE2和LATE3信号在“或非”门1532处组合。DLL0和DLL2信号在“或非”门1534处组合。“或非”门1534的输出与是信号QED和QSP1*在“或非”门1536处相组合。“或非”门1532输出信号控制多路复用器1544和晶体管1546的栅极。晶体管1546被激活时将节点1174上拉到电源。多路复用器1544启动时将“或非”门1536的输出信号传送到节点1174。节点1174处的信号表示QL2信号。

在图15中,当DLL3和QSP2信号均为高电平时,QL0被激活为高电平。类似地,当DLL1和QSP3信号均为高电平时,仅仅QL1被激活为高电平。如前所述,当延迟设置为2或3时,QL2信号总是激活的,为高电平。在图15中,当节点1112处的LATE2信号或者节点1113处的LATE3信号为高电平时,表示延迟设置为2或3,迫使节点1540处“或非”门1532的输出为低电平。这使晶体管1546导通,从而将节点1174连接到电压源(高电平)。因此,当LATE2或LATE3为高电平时,节点1174处的信号QL2总是高电平。当LATE2和LATE3均为低电平时,表示延迟设置为4或5,迫使节点1540处“或非”门1532的输出为高电平。这使晶体管1546截止。因此,节点1174处的信号QL2取决于信号QED、QSP1*、DLL0和DLL2。

图17还显示了图15所示电路的操作定时。在图17中,在与图15所示其它信号有关的适当时刻使信号QL0-QL2激活或转换为高电平。信号QL2的转换介于信号QL0的转换之间。信号QL2的转换亦介于信号QL1的转换之间。如前图6和7中所述,信号QL2的转换定时允许正确地激活信号QL0和QL1。这使得能够在读操作期间精确处理数据。

图18显示根据本发明的系统。在该图中,系统1800包括与存储器件100相连的处理器1802。本发明的存储器件100在图1中描述。根据本发明,处理器1802通过控制线(CONTROL)向存储器件100提供控制信号。处理器和存储器之间的数据通信通过数据线或数据总线(DATA)进行,并通过地址线或地址总线(ADDRESS)向存储器提供地址。在一个实施例中,将处理器1802和存储器件100制作到单芯片上。

结论

尽管本说明书已对具体实施例作了图示和说明,本领域的技术人员应理解,任何适合于达到相同目的的装置可以代替所示具体实施例。本申请旨在涵盖本发明的任何一种修改或变化。因此,用意是,本发明仅由所附权利要求书及其等效来加以限定。

Claims (42)

1.一种集成电路,包括:

多条输出通路,用于接收第一、第二、第三和第四数据比特构成的数据比特组,所述数据通路中每条数据通路并行接收所述数据比特;

与所述输出通路相连的输出选择器,用于从所述输出通路接收所述数据比特;以及

输出级,用于接收由所述输出选择器传送的数据比特,以便在2个时钟信号周期内以序列形式将所述数据比特输出到数据缓冲区,其中,所述序列中的第一和第三数据比特在第一使能信号的交替相位下输出,而所述序列中的第二和第四数据比特在第二使能信号的交替相位下输出,其中,所述第一和第二使能信号不是同步的。

2.如权利要求1所述的集成电路,其特征在于,所述输出通路中的每条输出通路均包括:

多个输入节点,用于接收所述数据比特;

与所述输入节点相连的输入选择器,用于从所述数据比特中产生选定的数据比特;以及

与所述输入选择器相连的第一锁存器,用于接收所述选定的数据比特;以及

与所述第一锁存器相连的第二锁存器,用于从所述第一锁存器接收所述选定的数据比特,其中,来自一条输出通路的所述选定的数据比特不同于来自另一条输出通路的所述选定的数据比特。

3.如权利要求2所述的集成电路,其特征在于,所述输出通路的第一锁存器由第一传播控制信号控制,所述输出通路的一半的第二锁存器由第二传播控制信号控制,而所述输出通路的另一半的第二锁存器由第三传播控制信号控制,其中,激活所述传播控制信号以便将所述数据比特从所述锁存器传送到所述输出选择器。

4.如权利要求1所述的集成电路,其特征在于,从所述输出选择器传送给所述输出级的数据比特由多个定时信号控制,其中,按顺序激活所述各定时信号以便以串行方式将所述数据比特组从所述输出选择器传送到所述输出级。

5.如权利要求1所述的集成电路,其特征在于,所述时钟信号的频率范围在66兆赫兹到300兆赫兹之间。

6.一种集成电路,包括:

多条输出通路,其中每条所述输出通路包括:

多个输入节点,用于接收一组数据比特;

输入选择器,用于提供从所述数据比特中选定的数据比特;

与所述输入选择器相连的第一锁存器,用于接收所述选定的数据比特;和

与所述第一锁存器相连的第二锁存器,用于从所述第一锁存器接收所述选定的数据比特,其中,来自每一条所述输出通路的所述选定的数据比特是不同的;

与所述输出通路相连的输出选择器,用于从每一条所述输出通路接收所述选定的数据比特;以及

与所述输出选择器相连的输出级,所述输出级从所述输出选择器串行接收选定的比特并在2个时钟周期内将所述选定的比特提供给数据缓冲区。

7.如权利要求6所述的集成电路,其特征在于,所述输出通路的数目为4。

8.如权利要求6所述的集成电路,其特征在于,所有所述输出通路的第一锁存器由第一传播控制信号控制,所述输出通路的一半的第二锁存器由第二传播控制信号控制,而所述输出通路的另一半的第二锁存器由第三传播控制信号控制。

9.如权利要求6所述的集成电路,其特征在于,从所述输出选择器传送给所述输出级的数据比特由多个定时信号控制,其中,按顺序激活所述定时信号以便将所述数据比特组从所述输出选择器串行传送到所述输出级。

10.一种集成电路,包括:

多个输入节点,用于并行接收M个数据比特构成的数据比特组;

数据缓冲区;以及

连在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中的每条输出通路传送所述M个数据比特构成的数据比特组中的不同比特,其中,通过激活多个定时信号将所述M个数据比特构成的数据比特组传送到所述数据缓冲区,第一和第二使能信号在不同时刻激活所述定时信号,其中,所述各使能信号不同步,以及M和N大于2。

11.如权利要求10所述的集成电路,其特征在于M等于N。

12.如权利要求10所述的集成电路,其特征在于M为4而N也为4。

13.如权利要求10所述的集成电路,其特征在于,通过激活第一两个定时信号而在第一时钟周期内将所述M个数据比特中一半数据比特传送到所述数据缓冲区,而通过激活第二两个定时信号而在第二时钟周期内将所述M个数据比特中另一半数据比特传送到所述数据缓冲区,其中M大于2。

14.如权利要求13所述的集成电路,其特征在于,所述第一两个定时信号之一在所述第一使能信号的下降沿之后被激活,而所述第一两个定时信号中另一个信号在所述第二使能信号的上升沿之后被激活,以及,所述第二两个定时信号之一在所述第一使能信号的上升沿之后被激活,而所述第二两个定时信号中另一个信号在所述第二使能信号的下降沿之后被激活。

15.一种存储器件,包括:

多个存储单元,用于存储多个数据比特;

多条输出通路,用于从所述存储单元接收由第一、第二、第三和第四数据比特构成的数据比特组,所述输出通路中每条输出通路并行接收所述数据比特;

与所述输出通路相连的输出选择器,用于从所述输出通路接收所述数据比特;以及

输出级,用于接收由所述输出选择器传送的数据比特以在2个时钟信号周期内将所述数据比特以串行序列形式输出到数据缓冲区,其中,在第一使能信号的交替相位下输出所述序列中的第一和第三数据比特,而在第二使能信号的交替相位下输出所述序列中的第二和第四数据比特,其中,所述第一使能信号和第二使能信号不同步。

16.如权利要求15所述的存储器件,其特征在于,所述输出通路中每条输出通路从所述数据比特组中选择数据比特,其中从每条所述输出通路中选出的每个数据比特是不同的。

17.如权利要求15所述的存储器件,其特征在于,所述输出通路中每条输出通路根据所述存储器件的地址比特的逻辑值从所述数据比特中选择数据比特。

18.如权利要求15所述的存储器件,其特征在于,所述输出级根据所述存储器件的地址比特的逻辑值输出所述数据比特。

19.一种存储器件,包括:

多个存储单元,用于存储多个数据比特;

多条数据通路,每条所述数据通路包括:

多个输入节点,用于从所述存储单元接收数据比特组;

输入选择器,用于提供从所述数据比特中选出的比特;

与所述输入选择器相连的第一锁存器,用于接收所述选定的比特;以及

与所述第一锁存器相连的第二锁存器,用于从所述第一锁存器接收所述选定的比特,其中,从每条所述输出通路接收的所述选定的比特是各不相同的;

与所述输出通路相连的输出选择器,用于从所述输出通路中每条输出通路接收所述选定的比特;以及

与所述输出选择器相连的输出级,所述输出级从所述输出选择器串行接收选定的比特并在2个时钟周期内将所述选定的比特提供给数据缓冲区。

20.如权利要求19所述的存储器件,其特征在于,所述输出通路的所述第一锁存器由第一传播控制信号控制,所述输出通路的一半的所述第二锁存器由第二传播控制信号控制,而所述输出通路的另一半的所述第二锁存器由第三传播控制信号控制,其中,激活所述各传播控制信号以便将所述数据比特从所述锁存器传送到所述输出选择器。

21.如权利要求20所述的存储器件,其特征在于,当第一个输出数据比特在所述存储器件接收到读指令之后2个时钟周期内出现在所述数据缓冲区时,所述第一传播控制信号总是激活的。

22.如权利要求20所述的存储器件,其特征在于,当第一个输出数据比特在所述存储器件收到读指令之后3个时钟周期内出现在所述数据缓冲区时,所述第一传播控制信号总是被激活的。

23.如权利要求20所述的存储器件,其特征在于,当第一个输出数据比特在所述存储器件接收到读指令之后4个时钟周期内出现在所述数据缓冲区时,在所述第二传播控制信号的转换之间以及在所述第三传播控制信号的转换之间,激活所述第一传播控制信号。

24.如权利要求20所述的存储器件,其特征在于,当第一个输出数据比特在所述存储器件收到读指令之后5个时钟周期内出现在所述数据缓冲区时,在所述第二传播控制信号的转换之间以及在所述第三传播控制信号的转换之间,激活所述第一传播控制信号。

25.如权利要求20所述的存储器件,其特征在于,当第一个输出数据比特在所述存储器件收到读指令之后隔3个以上时钟周期出现在所述数据缓冲区时,在所述第二传播控制信号的转换之间以及在所述第三传播控制信号的转换之间,激活所述第一传播控制信号。

26.一种存储器件,包括:

多个存储单元,用于存储多个数据比特;

多个输入节点,用于从所述存储单元并行接收M个数据比特构成的数据比特组;

数据缓冲区;以及

连接在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中每条输出通路传送所述M个数据比特构成的数据比特组,其中,通过激活多个定时信号将所述M个数据比特构成的数据比特组串行传送到所述数据缓冲区,由第一和第二使能信号在不同时刻激活所述各定时信号,其中,所述使能信号不同步,且M和N大于2。

27.如权利要求26所述的存储器件,其特征在于输出通路的数目为4。

28.如权利要求26所述的存储器件,其特征在于M等于N。

29.如权利要求26所述的存储器件,其特征在于,M为4和N也为4。

30.如权利要求26所述的存储器件,其特征在于,通过激活第一两个定时信号而在第一时钟周期内将所述M个比特中一半比特传送到所述数据缓冲区,而通过激活第二两个定时信号而在第二时钟周期内将所述M个比特中另一半比特传送到所述数据缓冲区,其中M大于2。

31.一种用于处理器和存储器件之间数据通信的系统,包括:

处理器;以及

与所述处理器相连的存储器件,所述存储器件包括:

多个存储单元,用于存储多个数据比特;

多个输入节点,用于从所述存储单元并行接收M个数据比特构成的数据比特组;

数据缓冲区;以及

连接在所述输入节点和所述数据缓冲区之间的N条输出通路,所述输出通路中每条输出通路传送所述M个数据比特构成的数据比特组,其中,通过激活多个定时信号而将所述M个数据比特构成的数据比特组串行传送到所述数据缓冲区,由第一和第二使能信号在不同时刻激活所述各定时信号,其中,所述使能信号不同步,且M和N大于2。

32.如权利要求31所述的系统,其特征在于还包括:

用于所述处理器和所述存储器件之间数据通信的数据总线;以及

用于提供所述存储器件的存储单元地址位置的地址总线。

33.一种操作存储器件的方法,所述方法包括:

访问存储单元中的M个数据比特,其中M大于2;

将所述M个数据比特并行传送到输出电路;以及

在两个时钟信号周期内根据第一和第二使能信号,从所述输出电路将所述M个数据比特串行输出到数据缓冲区,其中,所述第一使能信号允许将偶数据比特输出到所述数据缓冲区,而所述第二使能信号允许将奇数据比特输出到所述数据缓冲区,

其特征在于还包括:

接收地址比特;

根据所述地址比特中一些比特的逻辑值确定传送顺序;以及

根据所述传送顺序将所述M个数据比特从所述输出电路传送到所述数据缓冲区。

34.如权利要求33所述的方法,其特征在于还包括根据所述第一和第二使能信号激活多个定时信号。

35.一种传送数据的方法,所述方法包括:

并行读取M个数据比特到多条输出通路,其中M大于2;

将所述M个数据比特从所述输出通路传送到输出选择器,其中,所述输出通路中每条输出通路传送不同的数据比特;

激活第一和第二使能信号;

根据所述第一和第二使能信号顺序地激活多个定时信号;

在所述各定时信号发生转换之后将所述M个数据比特顺序传送到输出级;以及

在两个时钟信号周期内将所述M个数据比特输出到数据缓冲区。

36.如权利要求35所述的方法,其特征在于,读M个数据比特包括访问多个存储单元。

37.如权利要求35所述的方法,其特征在于,传送来自所述输出通路的M个数据比特包括从每条所述输出通路上的所述M个数据比特中选择不同的比特。

38.如权利要求35所述的方法,其特征在于,激活所述第一和第二使能信号包括激活具有不同相位的信号。

39.如权利要求35所述的方法,其特征在于,激活多个定时信号包括:

根据所述第一使能信号的第一相位激活第一定时信号;

根据所述第二使能信号的第一相位激活使第二定时信号;

根据所述第一使能信号的第二相位激活第三定时信号;以及

根据所述第二使能信号的第二相位激活第四定时信号。

40.如权利要求35所述的方法,其特征在于,激活多个定时信号包括:

在所述第一使能信号的转换之后激活第一定时信号;

在所述第二使能信号的转换之后激活第二定时信号;

在所述第一使能信号的不同的转换之后激活第三定时信号;以及

在所述第二使能信号的不同的转换之后激活第四定时信号,其中,所述第一使能信号的转换在所述第二使能信号的转换之间。

41.如权利要求35所述的方法,其特征在于,激活多个定时信号包括:

在所述第一使能信号的下降沿之后激活第一定时信号;

在所述第二使能信号的下降沿之后激活第二定时信号;

在所述第一使能信号的上升沿之后激活第三定时信号;以及

在所述第二使能信号的上升沿之后激活第四定时信号,其中,所述第一使能信号的所述下降沿在所述第二使能信号的所述下降沿和所述上升沿之间。

42.如权利要求35所述的方法,其特征在于,输出所述M个数据比特包括:

在激活第一定时信号之后输出第一数据比特;

在激活第二定时信号之后输出第二数据比特;

在激活第三定时信号之后输出第三数据比特;

在激活第四定时信号之后输出第四数据比特。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/808,506 US6556494B2 (en) | 2001-03-14 | 2001-03-14 | High frequency range four bit prefetch output data path |

| US09/808,506 | 2001-03-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1543650A CN1543650A (zh) | 2004-11-03 |

| CN100565698C true CN100565698C (zh) | 2009-12-02 |

Family

ID=25198971

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028097483A Expired - Fee Related CN100565698C (zh) | 2001-03-14 | 2002-03-08 | 具有多比特预取输出数据通路的装置及其操作方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US6556494B2 (zh) |

| EP (1) | EP1377982B1 (zh) |

| JP (1) | JP4080892B2 (zh) |

| KR (1) | KR100568646B1 (zh) |

| CN (1) | CN100565698C (zh) |

| AT (1) | ATE341082T1 (zh) |

| DE (1) | DE60214992T2 (zh) |

| WO (1) | WO2002089141A1 (zh) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003044349A (ja) * | 2001-07-30 | 2003-02-14 | Elpida Memory Inc | レジスタ及び信号生成方法 |

| JP4812976B2 (ja) * | 2001-07-30 | 2011-11-09 | エルピーダメモリ株式会社 | レジスタ、メモリモジュール及びメモリシステム |

| US7549011B2 (en) * | 2001-08-30 | 2009-06-16 | Micron Technology, Inc. | Bit inversion in memory devices |

| US6785168B2 (en) * | 2002-12-27 | 2004-08-31 | Hynix Semiconductor Inc. | Semiconductor memory device having advanced prefetch block |

| KR100518564B1 (ko) * | 2003-04-03 | 2005-10-04 | 삼성전자주식회사 | 이중 데이터율 동기식 메모리장치의 출력 멀티플렉싱 회로및 방법 |

| KR100564596B1 (ko) * | 2003-12-18 | 2006-03-28 | 삼성전자주식회사 | 멀티비트 데이터의 지연 시간 보상이 가능한 반도체메모리 장치 |

| JP2005182939A (ja) * | 2003-12-22 | 2005-07-07 | Toshiba Corp | 半導体記憶装置 |

| US7016235B2 (en) * | 2004-03-03 | 2006-03-21 | Promos Technologies Pte. Ltd. | Data sorting in memories |

| US7054215B2 (en) * | 2004-04-02 | 2006-05-30 | Promos Technologies Pte. Ltd. | Multistage parallel-to-serial conversion of read data in memories, with the first serial bit skipping at least one stage |

| KR100562645B1 (ko) * | 2004-10-29 | 2006-03-20 | 주식회사 하이닉스반도체 | 반도체 기억 소자 |

| US7230858B2 (en) * | 2005-06-28 | 2007-06-12 | Infineon Technologies Ag | Dual frequency first-in-first-out structure |

| US7349289B2 (en) | 2005-07-08 | 2008-03-25 | Promos Technologies Inc. | Two-bit per I/O line write data bus for DDR1 and DDR2 operating modes in a DRAM |

| US7358872B2 (en) * | 2005-09-01 | 2008-04-15 | Micron Technology, Inc. | Method and apparatus for converting parallel data to serial data in high speed applications |

| US7567465B2 (en) * | 2007-08-30 | 2009-07-28 | Micron Technology, Inc. | Power saving sensing scheme for solid state memory |

| JP2011058847A (ja) * | 2009-09-07 | 2011-03-24 | Renesas Electronics Corp | 半導体集積回路装置 |

| KR20110088947A (ko) * | 2010-01-29 | 2011-08-04 | 주식회사 하이닉스반도체 | 반도체 메모리의 데이터 출력 회로 |

| TWI459401B (zh) * | 2011-03-09 | 2014-11-01 | Etron Technology Inc | 應用於一記憶體電路內複數個記憶區塊的栓鎖系統 |

| TWI490698B (zh) * | 2013-05-10 | 2015-07-01 | Integrated Circuit Solution Inc | 高速資料傳輸架構 |

| US9412294B2 (en) | 2013-08-22 | 2016-08-09 | Boe Technology Group Co., Ltd. | Data transmission device, data transmission method and display device |

| CN103413516B (zh) * | 2013-08-22 | 2016-03-30 | 京东方科技集团股份有限公司 | 数据传输装置、数据传输方法及显示装置 |

| KR102460281B1 (ko) * | 2017-11-24 | 2022-10-31 | 프라운호퍼 게젤샤프트 쭈르 푀르데룽 데어 안겐반텐 포르슝 에. 베. | 다중 입력 파이프 라인을 가진 데이터 버스 |

| CN111208867B (zh) * | 2019-12-27 | 2021-08-24 | 芯创智(北京)微电子有限公司 | 一种基于ddr读数据整数时钟周期的同步电路及同步方法 |

| CN116705132B (zh) * | 2022-02-24 | 2024-05-14 | 长鑫存储技术有限公司 | 数据传输电路、数据传输方法和存储器 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10255459A (ja) | 1997-03-10 | 1998-09-25 | Mitsubishi Electric Corp | ラインメモリ |

| JPH11176158A (ja) * | 1997-12-10 | 1999-07-02 | Fujitsu Ltd | ラッチ回路、データ出力回路及びこれを有する半導体装置 |

| TW430815B (en) * | 1998-06-03 | 2001-04-21 | Fujitsu Ltd | Semiconductor integrated circuit memory and, bus control method |

| JP2000076853A (ja) | 1998-06-17 | 2000-03-14 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

-

2001

- 2001-03-14 US US09/808,506 patent/US6556494B2/en not_active Expired - Fee Related

-

2002

- 2002-03-08 CN CNB028097483A patent/CN100565698C/zh not_active Expired - Fee Related

- 2002-03-08 WO PCT/US2002/007668 patent/WO2002089141A1/en active IP Right Grant

- 2002-03-08 DE DE60214992T patent/DE60214992T2/de not_active Expired - Lifetime

- 2002-03-08 JP JP2002586351A patent/JP4080892B2/ja not_active Expired - Fee Related

- 2002-03-08 KR KR1020037012038A patent/KR100568646B1/ko not_active IP Right Cessation

- 2002-03-08 AT AT02766728T patent/ATE341082T1/de not_active IP Right Cessation

- 2002-03-08 EP EP02766728A patent/EP1377982B1/en not_active Expired - Lifetime

- 2002-07-29 US US10/207,641 patent/US6600691B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP1377982B1 (en) | 2006-09-27 |

| DE60214992D1 (de) | 2006-11-09 |

| KR100568646B1 (ko) | 2006-04-07 |

| DE60214992T2 (de) | 2007-10-18 |

| JP2004523056A (ja) | 2004-07-29 |

| US6600691B2 (en) | 2003-07-29 |

| US6556494B2 (en) | 2003-04-29 |

| US20020186608A1 (en) | 2002-12-12 |

| EP1377982A1 (en) | 2004-01-07 |

| ATE341082T1 (de) | 2006-10-15 |

| KR20040041541A (ko) | 2004-05-17 |

| JP4080892B2 (ja) | 2008-04-23 |

| CN1543650A (zh) | 2004-11-03 |

| WO2002089141A1 (en) | 2002-11-07 |

| US20020131313A1 (en) | 2002-09-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100565698C (zh) | 具有多比特预取输出数据通路的装置及其操作方法 | |

| JP3410922B2 (ja) | クロック制御回路 | |

| CN1933028B (zh) | 具有突发读取等待功能的与非型快闪存储装置 | |

| CN100585735C (zh) | 同步型半导体存储装置 | |

| CN103460293B (zh) | 用于将命令提供到数据块的命令路径、设备及方法 | |

| CN102194510B (zh) | 半导体存储设备的数据输出电路 | |

| JP2000067577A5 (zh) | ||

| KR100322530B1 (ko) | 반도체 메모리 장치의 데이터 입력 회로 및 데이터 입력 방법 | |

| CN101149963B (zh) | 多端口存储设备 | |

| CN109643566A (zh) | 用于调整命令信号路径的延迟的设备及方法 | |

| JP3406790B2 (ja) | データ転送システム及びデータ転送方法 | |

| EP3590114A1 (en) | Apparatuses and methods for determining a phase relationship between an input clock signal and a multiphase clock signal | |

| CN100576140C (zh) | 产生数字信号处理器和存储器的时钟信号的电路和方法 | |

| KR20030009292A (ko) | 아날로그 정보 전송용 장치 | |

| KR100846386B1 (ko) | 멀티포트 메모리 장치 | |

| CN1945737B (zh) | 具有等待时间计数器的半导体器件 | |

| CN100407109C (zh) | 数据转换电路和半导体装置 | |

| KR100495917B1 (ko) | 고속 데이터 출력을 위한 파이프래치 회로 | |

| EP0273642B1 (en) | Apparatus for reading data from memory | |

| JPS6220632B2 (zh) | ||

| EP0660328B1 (en) | Method of controlling semiconductor storage circuit | |

| KR100190373B1 (ko) | 리드 패스를 위한 고속 동기식 메모리 장치 | |

| KR100673678B1 (ko) | 데이터 입력 도메인 크로싱 마진을 보장하는 반도체 메모리장치의 데이터 입력 회로 및 그 데이터 입력 동작 방법 | |

| KR20070036563A (ko) | 출력 제어장치 | |

| JPH0489687A (ja) | 同期式バーストアクセスメモリ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20091202 Termination date: 20110308 |