CN100394578C - 含有一组电路元件和一组隔离沟槽的集成电路的形成方法 - Google Patents

含有一组电路元件和一组隔离沟槽的集成电路的形成方法 Download PDFInfo

- Publication number

- CN100394578C CN100394578C CNB2004100473340A CN200410047334A CN100394578C CN 100394578 C CN100394578 C CN 100394578C CN B2004100473340 A CNB2004100473340 A CN B2004100473340A CN 200410047334 A CN200410047334 A CN 200410047334A CN 100394578 C CN100394578 C CN 100394578C

- Authority

- CN

- China

- Prior art keywords

- stress

- degrees centigrade

- environment

- annealing

- temperature

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

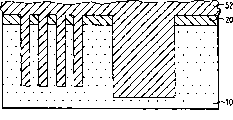

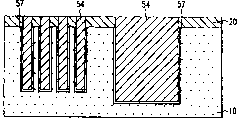

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

- H01L21/76229—Concurrent filling of a plurality of trenches having a different trench shape or dimension, e.g. rectangular and V-shaped trenches, wide and narrow trenches, shallow and deep trenches

-

- C—CHEMISTRY; METALLURGY

- C10—PETROLEUM, GAS OR COKE INDUSTRIES; TECHNICAL GASES CONTAINING CARBON MONOXIDE; FUELS; LUBRICANTS; PEAT

- C10L—FUELS NOT OTHERWISE PROVIDED FOR; NATURAL GAS; SYNTHETIC NATURAL GAS OBTAINED BY PROCESSES NOT COVERED BY SUBCLASSES C10G OR C10K; LIQUIFIED PETROLEUM GAS; USE OF ADDITIVES TO FUELS OR FIRES; FIRE-LIGHTERS

- C10L1/00—Liquid carbonaceous fuels

- C10L1/32—Liquid carbonaceous fuels consisting of coal-oil suspensions or aqueous emulsions or oil emulsions

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B01—PHYSICAL OR CHEMICAL PROCESSES OR APPARATUS IN GENERAL

- B01F—MIXING, e.g. DISSOLVING, EMULSIFYING OR DISPERSING

- B01F23/00—Mixing according to the phases to be mixed, e.g. dispersing or emulsifying

- B01F23/40—Mixing liquids with liquids; Emulsifying

- B01F23/41—Emulsifying

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B01—PHYSICAL OR CHEMICAL PROCESSES OR APPARATUS IN GENERAL

- B01F—MIXING, e.g. DISSOLVING, EMULSIFYING OR DISPERSING

- B01F25/00—Flow mixers; Mixers for falling materials, e.g. solid particles

- B01F25/40—Static mixers

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B01—PHYSICAL OR CHEMICAL PROCESSES OR APPARATUS IN GENERAL

- B01F—MIXING, e.g. DISSOLVING, EMULSIFYING OR DISPERSING

- B01F25/00—Flow mixers; Mixers for falling materials, e.g. solid particles

- B01F25/60—Pump mixers, i.e. mixing within a pump

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Oil, Petroleum & Natural Gas (AREA)

- General Chemical & Material Sciences (AREA)

- Organic Chemistry (AREA)

- Dispersion Chemistry (AREA)

- Element Separation (AREA)

- Semiconductor Memories (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/250,092 US6869860B2 (en) | 2003-06-03 | 2003-06-03 | Filling high aspect ratio isolation structures with polysilazane based material |

| US10/250,092 | 2003-06-03 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1574277A CN1574277A (zh) | 2005-02-02 |

| CN100394578C true CN100394578C (zh) | 2008-06-11 |

Family

ID=33489117

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2004100473340A Expired - Fee Related CN100394578C (zh) | 2003-06-03 | 2004-06-02 | 含有一组电路元件和一组隔离沟槽的集成电路的形成方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6869860B2 (enExample) |

| JP (1) | JP2004363595A (enExample) |

| KR (1) | KR100562236B1 (enExample) |

| CN (1) | CN100394578C (enExample) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100503527B1 (ko) * | 2003-02-12 | 2005-07-26 | 삼성전자주식회사 | 퍼하이드로 폴리실라잔을 포함하는 반도체 소자 제조용조성물 및 이를 이용한 반도체 소자의 제조방법 |

| JP2004273519A (ja) * | 2003-03-05 | 2004-09-30 | Clariant (Japan) Kk | トレンチ・アイソレーション構造の形成方法 |

| US7192891B2 (en) * | 2003-08-01 | 2007-03-20 | Samsung Electronics, Co., Ltd. | Method for forming a silicon oxide layer using spin-on glass |

| US7071075B2 (en) * | 2003-12-08 | 2006-07-04 | Nanya Technology Corporation | STI forming method for improving STI step uniformity |

| JP2005286256A (ja) * | 2004-03-31 | 2005-10-13 | Nec Electronics Corp | 半導体装置及びその製造方法 |

| US7521378B2 (en) * | 2004-07-01 | 2009-04-21 | Micron Technology, Inc. | Low temperature process for polysilazane oxidation/densification |

| US7067890B2 (en) * | 2004-09-29 | 2006-06-27 | Agere Systems Inc. | Thick oxide region in a semiconductor device |

| JP4607613B2 (ja) * | 2005-02-09 | 2011-01-05 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2007142311A (ja) * | 2005-11-22 | 2007-06-07 | Toshiba Corp | 半導体装置及びその製造方法 |

| US7682927B2 (en) | 2005-03-25 | 2010-03-23 | Kabushiki Kaisha Toshiba | Method of manufacturing semiconductor device |

| JP4515951B2 (ja) * | 2005-03-31 | 2010-08-04 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| JP2006286720A (ja) * | 2005-03-31 | 2006-10-19 | Toshiba Corp | 半導体装置およびその製造方法 |

| US8012847B2 (en) | 2005-04-01 | 2011-09-06 | Micron Technology, Inc. | Methods of forming trench isolation in the fabrication of integrated circuitry and methods of fabricating integrated circuitry |

| JP5116229B2 (ja) * | 2005-09-09 | 2013-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| KR100827314B1 (ko) * | 2005-10-10 | 2008-05-06 | 삼성전기주식회사 | 열처리에 의해 평탄면을 가지는 멤스 소자 및 광변조기제조 방법 |

| JP2007110005A (ja) * | 2005-10-17 | 2007-04-26 | Nec Electronics Corp | 半導体装置の製造方法 |

| US7371657B2 (en) * | 2005-10-19 | 2008-05-13 | Infineon Technologies Ag | Method for forming an isolating trench with a dielectric material |

| US20070132056A1 (en) * | 2005-12-09 | 2007-06-14 | Advanced Analogic Technologies, Inc. | Isolation structures for semiconductor integrated circuit substrates and methods of forming the same |

| US7276417B2 (en) * | 2005-12-28 | 2007-10-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | Hybrid STI stressor with selective re-oxidation anneal |

| US7626257B2 (en) * | 2006-01-18 | 2009-12-01 | Infineon Technologies Ag | Semiconductor devices and methods of manufacture thereof |

| CN101079391B (zh) * | 2006-05-26 | 2012-01-25 | 中芯国际集成电路制造(上海)有限公司 | 用于半导体器件的具有高间隙填充能力的方法 |

| JP5103804B2 (ja) * | 2006-06-27 | 2012-12-19 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| JP2008028357A (ja) * | 2006-07-24 | 2008-02-07 | Hynix Semiconductor Inc | 半導体素子及びその製造方法 |

| KR100810411B1 (ko) * | 2006-09-21 | 2008-03-04 | 주식회사 하이닉스반도체 | 반도체 소자의 소자 분리막 형성방법 |

| JP4965953B2 (ja) * | 2006-09-29 | 2012-07-04 | 株式会社東芝 | ポリシラザンまたはポリシラザン溶液の取り扱い方法、ポリシラザン溶液、半導体装置の製造方法 |

| US20080142897A1 (en) * | 2006-12-19 | 2008-06-19 | Chartered Semiconductor Manufacturing Ltd. | Integrated circuit system having strained transistor |

| KR100826776B1 (ko) * | 2006-12-28 | 2008-04-30 | 주식회사 하이닉스반도체 | 반도체 소자의 소자 분리막 형성 방법 |

| US20080179715A1 (en) * | 2007-01-30 | 2008-07-31 | Micron Technology, Inc. | Shallow trench isolation using atomic layer deposition during fabrication of a semiconductor device |

| KR100870322B1 (ko) * | 2007-02-09 | 2008-11-25 | 주식회사 하이닉스반도체 | 반도체 소자의 소자 분리막 형성 방법 |

| KR100855272B1 (ko) * | 2007-03-27 | 2008-09-01 | 주식회사 하이닉스반도체 | 반도체 소자의 소자분리막 형성방법 |

| KR100900232B1 (ko) * | 2007-05-22 | 2009-05-29 | 주식회사 하이닉스반도체 | 반도체 소자 및 그의 제조방법 |

| KR100861311B1 (ko) | 2007-09-10 | 2008-10-01 | 주식회사 하이닉스반도체 | 반도체 소자의 소자분리막 형성방법 |

| KR100909757B1 (ko) * | 2007-10-31 | 2009-07-29 | 주식회사 하이닉스반도체 | 반도체 소자의 층간절연막 형성 방법 |

| JP5329825B2 (ja) | 2008-02-25 | 2013-10-30 | 株式会社東芝 | 半導体装置の製造方法 |

| KR101003494B1 (ko) * | 2008-04-10 | 2010-12-30 | 주식회사 하이닉스반도체 | 메모리 소자의 소자분리 구조 및 형성 방법 |

| US7999355B2 (en) * | 2008-07-11 | 2011-08-16 | Air Products And Chemicals, Inc. | Aminosilanes for shallow trench isolation films |

| JP2010027904A (ja) * | 2008-07-22 | 2010-02-04 | Elpida Memory Inc | 半導体装置の製造方法 |

| US7655532B1 (en) * | 2008-07-25 | 2010-02-02 | Taiwan Semiconductor Manufacturing Company, Ltd. | STI film property using SOD post-treatment |

| KR101062293B1 (ko) | 2008-11-14 | 2011-09-05 | 주식회사 하이닉스반도체 | 반도체 소자 및 그의 제조방법 |

| JP5841306B2 (ja) | 2009-05-08 | 2016-01-13 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US8349985B2 (en) | 2009-07-28 | 2013-01-08 | Cheil Industries, Inc. | Boron-containing hydrogen silsesquioxane polymer, integrated circuit device formed using the same, and associated methods |

| TWI394230B (zh) * | 2009-07-30 | 2013-04-21 | Winbond Electronics Corp | 半導體元件之製作方法 |

| CN101989566B (zh) * | 2009-08-06 | 2012-07-25 | 华邦电子股份有限公司 | 半导体器件和闪存器件的制作方法 |

| US8466067B2 (en) * | 2009-10-05 | 2013-06-18 | Applied Materials, Inc. | Post-planarization densification |

| US8105956B2 (en) * | 2009-10-20 | 2012-01-31 | Micron Technology, Inc. | Methods of forming silicon oxides and methods of forming interlevel dielectrics |

| US8796105B2 (en) * | 2012-07-25 | 2014-08-05 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and apparatus for preparing polysilazane on a semiconductor wafer |

| CN103579116B (zh) * | 2012-08-10 | 2017-05-31 | 南亚科技股份有限公司 | 在基底中制作多个沟槽的方法 |

| CN103594412A (zh) * | 2012-08-13 | 2014-02-19 | 中芯国际集成电路制造(上海)有限公司 | 一种浅沟槽隔离结构的制作方法和浅沟槽隔离结构 |

| CN103943621B (zh) * | 2013-01-22 | 2019-08-13 | 联华电子股份有限公司 | 浅沟槽隔离结构及其形成方法 |

| US9018108B2 (en) | 2013-01-25 | 2015-04-28 | Applied Materials, Inc. | Low shrinkage dielectric films |

| US9786542B2 (en) * | 2014-01-13 | 2017-10-10 | Taiwan Semiconductor Manufacturing Co., Ltd. | Mechanisms for forming semiconductor device having isolation structure |

| KR102399338B1 (ko) | 2014-09-12 | 2022-05-19 | 삼성전자주식회사 | 이미지 센서의 제조 방법 |

| US20160225652A1 (en) | 2015-02-03 | 2016-08-04 | Applied Materials, Inc. | Low temperature chuck for plasma processing systems |

| CN108369896A (zh) * | 2015-12-10 | 2018-08-03 | 应用材料公司 | 利用空间原子层沉积的原位膜退火 |

| CN107359136B (zh) * | 2017-08-09 | 2018-10-02 | 睿力集成电路有限公司 | 隔离沟槽的填充方法、设备及隔离沟槽的填充结构 |

| US11776846B2 (en) | 2020-02-07 | 2023-10-03 | Asm Ip Holding B.V. | Methods for depositing gap filling fluids and related systems and devices |

| CN112768404A (zh) * | 2021-01-26 | 2021-05-07 | 上海华力微电子有限公司 | 半导体器件的制造方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08130199A (ja) * | 1994-09-06 | 1996-05-21 | Sony Corp | 段差基体の平坦化方法 |

| US5518950A (en) * | 1994-09-02 | 1996-05-21 | Advanced Micro Devices, Inc. | Spin-on-glass filled trench isolation method for semiconductor circuits |

| CN1234607A (zh) * | 1998-04-27 | 1999-11-10 | 日本电气株式会社 | 形成沟槽隔离结构的方法 |

| JP2001308090A (ja) * | 2000-04-25 | 2001-11-02 | Tonengeneral Sekiyu Kk | 微細溝をシリカ質材料で埋封する方法及びシリカ質膜付き基材 |

| US6489252B2 (en) * | 2000-12-27 | 2002-12-03 | Samsung Electronics Co., Ltd. | Method of forming a spin-on-glass insulation layer |

| US6566229B2 (en) * | 2001-03-05 | 2003-05-20 | Samsung Electronics Co., Ltd. | Method of forming an insulating layer in a trench isolation type semiconductor device |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6194283B1 (en) * | 1997-10-29 | 2001-02-27 | Advanced Micro Devices, Inc. | High density trench fill due to new spacer fill method including isotropically etching silicon nitride spacers |

| US6333274B2 (en) * | 1998-03-31 | 2001-12-25 | Kabushiki Kaisha Toshiba | Method of manufacturing a semiconductor device including a seamless shallow trench isolation step |

| US5932283A (en) * | 1998-05-01 | 1999-08-03 | Nec Corporation | Method for fabricating SiO2 film |

| US6146970A (en) * | 1998-05-26 | 2000-11-14 | Motorola Inc. | Capped shallow trench isolation and method of formation |

| US6235608B1 (en) * | 1999-04-14 | 2001-05-22 | Winbond Electronics Corp. | STI process by method of in-situ multilayer dielectric deposition |

| KR100362834B1 (ko) | 2000-05-02 | 2002-11-29 | 삼성전자 주식회사 | 반도체 장치의 산화막 형성 방법 및 이에 의하여 제조된 반도체 장치 |

| US7270886B2 (en) * | 2000-10-12 | 2007-09-18 | Samsung Electronics Co., Ltd. | Spin-on glass composition and method of forming silicon oxide layer in semiconductor manufacturing process using the same |

| KR100354439B1 (ko) * | 2000-12-08 | 2002-09-28 | 삼성전자 주식회사 | 트렌치 소자 분리막 형성 방법 |

| KR100354442B1 (ko) | 2000-12-11 | 2002-09-28 | 삼성전자 주식회사 | 반도체 장치의 스핀 온 글래스 절연막 형성 방법 |

| US6653718B2 (en) * | 2001-01-11 | 2003-11-25 | Honeywell International, Inc. | Dielectric films for narrow gap-fill applications |

| KR100364026B1 (ko) * | 2001-02-22 | 2002-12-11 | 삼성전자 주식회사 | 층간 절연막 형성방법 |

| KR100512167B1 (ko) * | 2001-03-12 | 2005-09-02 | 삼성전자주식회사 | 트렌치 소자 분리형 반도체 장치 및 트렌치형 소자 분리막형성방법 |

| US6737333B2 (en) * | 2001-07-03 | 2004-05-18 | Texas Instruments Incorporated | Semiconductor device isolation structure and method of forming |

| US6740955B1 (en) * | 2001-07-03 | 2004-05-25 | Samsung Electronics Co., Ltd. | Trench device isolation structure |

| KR100428806B1 (ko) * | 2001-07-03 | 2004-04-28 | 삼성전자주식회사 | 트렌치 소자분리 구조체 및 그 형성 방법 |

| TWI320214B (en) * | 2002-08-22 | 2010-02-01 | Method of forming a trench isolation structure | |

| US6960781B2 (en) * | 2003-03-07 | 2005-11-01 | Amberwave Systems Corporation | Shallow trench isolation process |

| US6890833B2 (en) * | 2003-03-26 | 2005-05-10 | Infineon Technologies Ag | Trench isolation employing a doped oxide trench fill |

| US6693050B1 (en) * | 2003-05-06 | 2004-02-17 | Applied Materials Inc. | Gapfill process using a combination of spin-on-glass deposition and chemical vapor deposition techniques |

-

2003

- 2003-06-03 US US10/250,092 patent/US6869860B2/en not_active Expired - Fee Related

-

2004

- 2004-05-24 KR KR1020040036786A patent/KR100562236B1/ko not_active Expired - Fee Related

- 2004-05-28 JP JP2004159279A patent/JP2004363595A/ja active Pending

- 2004-06-02 CN CNB2004100473340A patent/CN100394578C/zh not_active Expired - Fee Related

-

2005

- 2005-01-12 US US11/035,392 patent/US20050179112A1/en not_active Abandoned

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5518950A (en) * | 1994-09-02 | 1996-05-21 | Advanced Micro Devices, Inc. | Spin-on-glass filled trench isolation method for semiconductor circuits |

| JPH08130199A (ja) * | 1994-09-06 | 1996-05-21 | Sony Corp | 段差基体の平坦化方法 |

| CN1234607A (zh) * | 1998-04-27 | 1999-11-10 | 日本电气株式会社 | 形成沟槽隔离结构的方法 |

| JP2001308090A (ja) * | 2000-04-25 | 2001-11-02 | Tonengeneral Sekiyu Kk | 微細溝をシリカ質材料で埋封する方法及びシリカ質膜付き基材 |

| US6489252B2 (en) * | 2000-12-27 | 2002-12-03 | Samsung Electronics Co., Ltd. | Method of forming a spin-on-glass insulation layer |

| US6566229B2 (en) * | 2001-03-05 | 2003-05-20 | Samsung Electronics Co., Ltd. | Method of forming an insulating layer in a trench isolation type semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050179112A1 (en) | 2005-08-18 |

| CN1574277A (zh) | 2005-02-02 |

| KR100562236B1 (ko) | 2006-03-22 |

| US20040248374A1 (en) | 2004-12-09 |

| US6869860B2 (en) | 2005-03-22 |

| KR20040104398A (ko) | 2004-12-10 |

| JP2004363595A (ja) | 2004-12-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100394578C (zh) | 含有一组电路元件和一组隔离沟槽的集成电路的形成方法 | |

| JP2004363595A5 (enExample) | ||

| US7157327B2 (en) | Void free, silicon filled trenches in semiconductors | |

| US6531369B1 (en) | Heterojunction bipolar transistor (HBT) fabrication using a selectively deposited silicon germanium (SiGe) | |

| US4789560A (en) | Diffusion stop method for forming silicon oxide during the fabrication of IC devices | |

| US4666556A (en) | Trench sidewall isolation by polysilicon oxidation | |

| CN100334708C (zh) | 半导体器件的制造方法 | |

| US6150212A (en) | Shallow trench isolation method utilizing combination of spacer and fill | |

| US9190313B2 (en) | Shallow trench isolation structures | |

| US20090036629A1 (en) | Polysilazane perhydride solution and method of manufacturing a semiconductor device using the same | |

| US20010021595A1 (en) | Sub-atmospheric pressure thermal chemical vapor deposition (SACVD) trench isolation method with attenuated surface sensitivity | |

| CN1263358A (zh) | 用于垂直晶体管的可控制的槽顶部隔离层的形成 | |

| JPH11340313A (ja) | トレンチ隔離形成方法 | |

| JP2003273206A (ja) | 半導体装置とその製造方法 | |

| US6787409B2 (en) | Method of forming trench isolation without grooving | |

| US20040251513A1 (en) | Shallow trench isolation structure with low sidewall capacitance for high speed integrated circuits | |

| US5854121A (en) | Semiconductor fabrication employing barrier atoms incorporated at the edges of a trench isolation structure | |

| US6358785B1 (en) | Method for forming shallow trench isolation structures | |

| US10347626B2 (en) | High quality deep trench oxide | |

| US6436760B1 (en) | Method for reducing surface oxide in polysilicon processing | |

| US6344673B1 (en) | Multilayered quantum conducting barrier structures | |

| US20030211701A1 (en) | Semiconductor device including an isolation trench having a dopant barrier layer formed on a sidewall thereof and a method of manufacture therefor | |

| US6344390B1 (en) | Methods of forming the buried strap and its quantum barrier in deep trench cell capacitors | |

| US6936511B2 (en) | Inverted buried strap structure and method for vertical transistor DRAM | |

| US20010014513A1 (en) | Sti divot and seam elimination |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20080611 Termination date: 20110602 |