WO2015118721A1 - 半導体装置及び半導体装置の製造方法 - Google Patents

半導体装置及び半導体装置の製造方法 Download PDFInfo

- Publication number

- WO2015118721A1 WO2015118721A1 PCT/JP2014/076722 JP2014076722W WO2015118721A1 WO 2015118721 A1 WO2015118721 A1 WO 2015118721A1 JP 2014076722 W JP2014076722 W JP 2014076722W WO 2015118721 A1 WO2015118721 A1 WO 2015118721A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- region

- type

- outer peripheral

- exposed

- semiconductor device

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 103

- 238000004519 manufacturing process Methods 0.000 title claims description 13

- 230000002093 peripheral effect Effects 0.000 claims abstract description 112

- 239000000758 substrate Substances 0.000 claims abstract description 34

- 239000012535 impurity Substances 0.000 claims description 21

- 238000000034 method Methods 0.000 claims description 7

- 210000000746 body region Anatomy 0.000 description 25

- 230000015556 catabolic process Effects 0.000 description 15

- 238000002513 implantation Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 6

- 229910052796 boron Inorganic materials 0.000 description 5

- 238000009792 diffusion process Methods 0.000 description 5

- 238000009826 distribution Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 5

- 229910010271 silicon carbide Inorganic materials 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 238000005468 ion implantation Methods 0.000 description 4

- 239000008186 active pharmaceutical agent Substances 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7811—Vertical DMOS transistors, i.e. VDMOS transistors with an edge termination structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/761—PN junctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/0619—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE] with a supplementary region doped oppositely to or in rectifying contact with the semiconductor containing or contacting region, e.g. guard rings with PN or Schottky junction

- H01L29/0623—Buried supplementary region, e.g. buried guard ring

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0661—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body specially adapted for altering the breakdown voltage by removing semiconductor material at, or in the neighbourhood of, a reverse biased junction, e.g. by bevelling, moat etching, depletion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic Table

- H01L29/1608—Silicon carbide

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66674—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/66712—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/66734—Vertical DMOS transistors, i.e. VDMOS transistors with a step of recessing the gate electrode, e.g. to form a trench gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42364—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity

- H01L29/42368—Gate electrodes for field effect devices for field-effect transistors with insulated gate characterised by the insulating layer, e.g. thickness or uniformity the thickness being non-uniform

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

Definitions

- the technology disclosed in this specification relates to a semiconductor device.

- the semiconductor device disclosed in Japanese Patent Laid-Open No. 2008-135522 has a MOSFET and a plurality of termination trenches formed around the MOSFET. Each termination trench extends in an annular shape so as to surround a region where the MOSFET is formed. An insulating layer is disposed in each termination trench. A p-type floating region is formed in the semiconductor layer in the range in contact with the bottom surface of each termination trench. When the MOSFET is turned off, a depletion layer extends from the body region of the MOSFET toward the outer peripheral side (region where the termination trench is formed). When the depletion layer extends to the p-type floating region below the innermost termination trench, the depletion layer further extends from the p-type floating toward the outer peripheral side.

- the depletion layer when the depletion layer extends to the adjacent p-type floating region, the depletion layer extends further to the outer peripheral side from the p-type floating region. Thus, the depletion layer spreads widely around the region where the MOSFET is formed, passing through each p-type floating region. Thereby, the breakdown voltage of the semiconductor device is improved.

- the p-type floating region described above is formed by forming a termination trench, implanting p-type impurities into the bottom surface of the termination trench, and then diffusing the implanted p-type impurities into the semiconductor layer.

- the diffusion distance of the p-type impurity may be shortened, and the interval between the p-type floating regions may not be sufficiently narrowed. In such a case, it becomes difficult to sufficiently extend the depletion layer in the region of the interval.

- the semiconductor device has a semiconductor substrate.

- the semiconductor device includes an n-type first region exposed in the surface of the semiconductor substrate, a p-type second region disposed below the first region, and the second An n-type third region disposed below the region and separated from the first region by the second region, and formed on the surface and penetrating through the first region and the second region A plurality of gate trenches reaching the third region, a first insulating layer disposed in the gate trench, a second insulating layer disposed in the gate trench, and the second insulating layer interposed between the second insulating layer and the second insulating layer.

- the plurality of gate trenches are formed when the surface is viewed in plan. Termination trench that goes around the area A second insulating layer disposed in the termination trench, a p-type lower end p-type region in contact with the lower end of the termination trench, and an outer peripheral side of the termination trench, and is in contact with the termination trench A p-type outer peripheral p-type region exposed on the surface, and a plurality of p-type guard ring regions formed on the outer peripheral side of the outer peripheral p-type region and exposed on the surface; The outer peripheral p-type region is separated from the plurality of guard ring regions, and the plurality of guard ring regions are separated from each other. The n-type peripheral n-type region is separated.

- the outer peripheral side means a direction away from a region where a plurality of gate trenches are formed.

- region mentioned above may be connected with the outer periphery p-type area

- a switching element is formed by the first region, the second region, the third region, the fourth region, and the gate electrode.

- a depletion layer spreads from the second region to the third region.

- the depletion layer reaches the lower end of the gate trench.

- the depletion layer reaches the fourth region.

- a depletion layer also spreads from the fourth region into the third region.

- a breakdown voltage in the region where the switching element is formed is ensured.

- the depletion layer that extends from the second region to the third region reaches the lower end of the termination trench, the depletion layer reaches the lower end p-type region.

- the depletion layer extends from the lower end p-type region and the outer peripheral p-type region into the outer peripheral n-type region.

- the depletion layer extending from the outer peripheral p-type region reaches the guard ring region adjacent to the outer peripheral p-type region, the depletion layer further extends from the guard ring region toward the adjacent guard ring region.

- the depletion layer extends toward the outer peripheral side via each guard ring region.

- the depletion layer extends widely in the outer peripheral region, and a breakdown voltage is secured.

- extension of the depletion layer can be promoted by the guard ring exposed on the surface of the semiconductor substrate.

- the guard ring region is formed in a range exposed on the surface of the semiconductor substrate, it can be formed with high accuracy. For this reason, the space

- the surface may have a first surface and a second surface protruding from the first surface by forming a stepped portion on the surface.

- the termination trench may be formed in the second surface.

- the outer peripheral p-type region may be exposed in a range extending from the second surface to the first surface.

- the plurality of guard ring regions may be exposed on the first surface. In this case, an interval between the termination trench and the stepped portion may be 10 ⁇ m or more.

- the end of the outer peripheral p-type region on the outer peripheral side and exposed to the surface is an Al high concentration region in which the Al concentration is higher than the B concentration.

- the region adjacent to the Al high concentration region in the peripheral p-type region may be a B high concentration region in which the B concentration is higher than the Al concentration.

- the width of the Al high concentration region may be wider than the width of each guard ring region.

- variety means the dimension in the direction which goes to an outer peripheral side from an inner peripheral side.

- leakage current in the outer peripheral p-type region can be suppressed.

- a part of the lower end p-type region extends to the inner peripheral side from the termination trench, and the lower end p-type region extends to the inner peripheral side from the termination trench.

- the part may not extend above the lower end of the termination trench.

- the guard ring region may contain Al.

- the guard ring region can be formed with higher accuracy.

- the semiconductor device having the steps described above may be manufactured by the following method.

- This method includes growing a p-type layer on the n-type layer, removing a part of the p-type layer, exposing the surface of the n-type layer, and exposing the p-type layer.

- a step of forming a surface protruding from the surface where the n-type layer is exposed, and a range extending from the surface where the n-type layer is exposed to the surface where the p-type layer is exposed Forming the peripheral p-type region by implanting p-type impurities into the surface, and forming the guard ring region by implanting p-type impurities into the surface where the n-type layer is exposed. And forming a termination trench on the surface where the p-type layer is exposed.

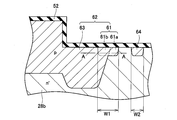

- FIG. 2 is a plan view of the semiconductor device 10.

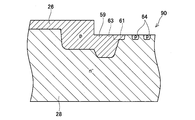

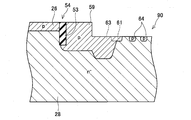

- FIG. 2 is a longitudinal sectional view taken along line II-II in FIG. The expanded sectional view of the outer periphery p-type area

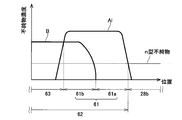

- FIG. 4 is a graph showing an impurity concentration distribution along the line AA in FIG. 3.

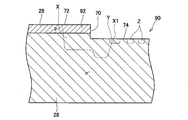

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

- FIG. 6 is an explanatory diagram of a manufacturing process of the semiconductor device 10.

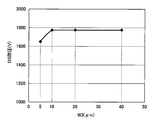

- the graph which shows the relationship between width W3 and DS pressure

- the semiconductor device 10 includes a semiconductor substrate 12 made of SiC (silicon carbide).

- the semiconductor substrate 12 has a MOSFET region 20 and an outer peripheral region 50.

- a MOSFET is formed in the MOSFET region 20.

- the outer peripheral region 50 is a region outside the MOSFET region 20.

- the outer peripheral region 50 is a region between the MOSFET region 20 and the end face 12 a of the semiconductor substrate 12.

- a breakdown voltage structure is formed in the outer peripheral region 50.

- FIG. 1 only the termination trench 54, the boundary p-type region 59, and the guard ring region 64 are shown in the outer peripheral region 50 in consideration of easy viewing.

- a source region 22, a body region 26, a drift region 28, a drain region 30, a p-type floating region 32, a gate trench 34, a source electrode 36, and a drain electrode 38 are formed in the MOSFET region 20. ing.

- a plurality of source regions 22 are formed in the MOSFET region 20.

- the source region 22 is an n-type region containing an n-type impurity at a high concentration.

- the source region 22 is formed in a range exposed on the upper surface of the semiconductor substrate 12.

- the body region 26 is formed on the side and the lower side of the source region 22 and is in contact with the source region 22.

- Body region 26 is a p-type region.

- the body region 26 is exposed on the upper surface of the semiconductor substrate 12 at a position where the source region 22 is not formed.

- the drift region 28 is an n-type region containing n-type impurities at a low concentration.

- the n-type impurity concentration of the drift region 28 is lower than the n-type impurity concentration of the source region 22.

- the drift region 28 is formed below the body region 26. The drift region 28 is in contact with the body region 26 and is separated from the source region 22 by the body region 26.

- the drain region 30 is an n-type region containing an n-type impurity at a high concentration.

- the n-type impurity concentration of the drain region 30 is higher than the n-type impurity concentration of the drift region 28.

- the drain region 30 is formed below the drift region 28. Drain region 30 is in contact with drift region 28 and is separated from body region 26 by drift region 28.

- the drain region 30 is formed in a range exposed on the lower surface of the semiconductor substrate 12.

- a plurality of gate trenches 34 are formed in the MOSFET region 20.

- the gate trench 34 is a groove formed on the upper surface of the semiconductor substrate 12.

- Each gate trench 34 is formed so as to penetrate the source region 22 and the body region 26 and reach the drift region 28.

- the plurality of gate trenches 34 extend in parallel to each other.

- a bottom insulating layer 34a, a gate insulating film 34b, and a gate electrode 34c are formed in each gate trench 34.

- the bottom insulating layer 34 a is a thick insulating layer formed at the bottom of the gate trench 34.

- a side surface of the gate trench 34 above the bottom insulating layer 34a is covered with a gate insulating film 34b.

- a gate electrode 34c is formed in the gate trench 34 above the bottom insulating layer 34a.

- the gate electrode 34c is opposed to the source region 22, the body region 26, and the drift region 28 through the gate insulating film 34b.

- the gate electrode 34c is insulated from the semiconductor substrate 12 by the gate insulating film 34b and the bottom insulating layer 34a.

- the upper surface of the gate electrode 34c is covered with an insulating layer 34d.

- the p-type floating region 32 is formed in the semiconductor substrate 12 in a range in contact with the bottom surface (that is, the lower end) of each gate trench 34.

- the periphery of the p-type floating region 32 is surrounded by the drift region 28.

- the p-type floating regions 32 are separated from each other by the drift region 28.

- Each p-type floating region 32 is separated from the body region 26 by the drift region 28.

- the source electrode 36 is formed on the upper surface of the semiconductor substrate 12 in the MOSFET region 20.

- the source electrode 36 is electrically connected to the source region 22 and the body region 26.

- the drain electrode 38 is formed on the lower surface of the semiconductor substrate 12.

- the drain electrode 38 is electrically connected to the drain region 30.

- drift region 28 and drain region 30 extend to the outer peripheral region 50.

- the drift region 28 and the drain region 30 extend to the end face 12 a of the semiconductor substrate 12.

- the drain electrode 38 is formed on the entire lower surface of the semiconductor substrate 12 including the outer peripheral region 50. Further, the upper surface of the semiconductor substrate 12 in the outer peripheral region 50 is covered with an insulating layer 52.

- the drift region 28 in the MOSFET region 20 may be referred to as an element portion drift region 28a

- the drift region 28 in the outer periphery region 50 may be referred to as an outer periphery drift region 28b.

- a stepped portion 70 is formed on the surface of the semiconductor substrate 12 in the outer peripheral region 50.

- the stepped portion 70 divides the surface of the semiconductor substrate 12 into a surface 72 on the central portion side and a surface 74 on the end surface 12a side.

- the surface 72 protrudes upward with respect to the surface 74.

- the thickness of the semiconductor substrate 12 is thicker at the portion corresponding to the surface 72 than at the portion corresponding to the surface 74.

- the MOSFET region 20 described above is formed in a portion corresponding to the surface 72 (a portion having a large thickness).

- the height of the stepped portion 70 is larger than the thickness of the body region 26. Therefore, the front surface 74 is located on the lower side (back surface side) than the lower end of the body region 26.

- a termination trench 54 is formed on the surface 72 of the semiconductor substrate 12 in the outer peripheral region 50.

- An insulating layer 53 is formed in the termination trench 54.

- the termination trench 54 is formed at a position adjacent to the body region 26.

- the termination trench 54 has substantially the same depth as the gate trench 34. Therefore, the insulating layer 53 is in contact with the element portion drift region 28 a at a position deeper than the body region 26.

- the termination trench 54 extends around the MOSFET region 20 when the surface of the semiconductor substrate 12 is viewed in plan. Therefore, body region 26 is separated from any p-type region in outer peripheral region 50 by insulating layer 53. That is, in this embodiment, the region surrounded by the termination trench 54 is the MOSFET region 20.

- a lower end p-type region 60 is formed at a position in contact with the lower end (that is, the bottom surface) of the termination trench 54.

- the lower end p-type region 60 is not formed in the MOSFET region 20.

- an outer peripheral p-type region 62 is formed in a region on the outer peripheral side of the termination trench 54 and in a position in contact with the termination trench 54.

- the outer peripheral p-type region 62 is formed from the position exposed at the surface 72 to the position exposed at the surface 74.

- the outer peripheral p-type region 62 is exposed on the surface 72, the stepped portion 70 and the surface 74.

- the outer peripheral p-type region 62 extends to a position deeper than the lower end of the termination trench 54. As shown in the drawing, in this embodiment, the lower end p-type region 60 and the outer peripheral p-type region 62 are connected. Since the lower end p-type region 60 and the outer peripheral p-type region 62 are one p-type region, hereinafter, these may be collectively referred to as a boundary portion p-type region 59. That is, the boundary p-type region 59 is a p-type region extending across the position exposed at the lower end of the termination trench 54, the position exposed at the surface 72, and the position exposed at the surface 74. As shown in FIG. 1, the boundary p-type region 59 is formed so as to go around the MOSFET region 20 along the termination trench 54. As shown in FIG. 2, an outer peripheral drift region 28 b is formed below the boundary p-type region 59.

- FIG. 3 shows an enlarged cross-sectional view of the vicinity of the outer peripheral edge of the outer peripheral p-type region 62.

- the outer peripheral p-type region 62 has an Al (aluminum) high concentration region 61 and a B (boron) high concentration region 63.

- the Al high concentration region 61 is a p-type region having a higher Al concentration than B

- the B high concentration region 63 is a p-type region having a higher B concentration than Al.

- the outer peripheral p-type region 62 does not contain p-type impurities other than B and Al except for an uncontrollable error level.

- the Al high concentration region 61 is formed at the outer peripheral end of the outer peripheral p-type region 62 in the range where the outer peripheral p-type region 62 is exposed on the surface 74.

- the B high concentration region 63 is formed in the outer peripheral p-type region 62 other than the Al high concentration region 61. Most of the outer peripheral p-type region 62 is constituted by the B high concentration region 63.

- FIG. 4 shows an impurity concentration distribution (impurity concentration distribution along the line AA in FIG. 3) in the vicinity of the outer peripheral edge of the outer peripheral p-type region 62. 3 and 4, a region 61 a is a region containing Al and not containing B.

- the region 61b contains Al and B, and the concentration of Al is higher than the concentration of B.

- the Al high concentration region 61 is composed of a region 61a and a region 61b.

- the width W1 (that is, the dimension in the direction from the inner circumference side to the outer circumference side) of the Al high concentration region 61 shown in FIG. 3 is wider than each width W2 of the guard ring region 64 described later.

- said width W1, W2 means the dimension in the direction which goes to an outer peripheral side from an inner peripheral side.

- each guard ring region 64 is a p-type region and is formed in a range exposed to the surface 74. Each guard ring region 64 is formed only in a shallow range. Therefore, the lower end of each guard ring region 64 is located on the upper side (surface side) than the lower end of the outer peripheral p-type region 62.

- An outer peripheral drift region 28 b is formed below each guard ring region 64. An outer peripheral drift region 28 b is formed between the guard ring region 64 on the innermost peripheral side (the MOSFET region 20 side) and the outer peripheral p-type region 62.

- the innermost guard ring region 64 is separated from the outer peripheral p-type region 62 by the outer peripheral drift region 28 b. Further, an outer peripheral drift region 28 b is formed between the guard ring regions 64. The guard ring regions 64 are separated from each other by the outer peripheral drift region 28b.

- Each guard ring region 64 contains Al as a p-type impurity. Each guard ring region 64 does not contain p-type impurities other than Al except for an uncontrollable error level.

- the operation of the semiconductor device 10 will be described.

- a voltage that makes the drain electrode 38 positive is applied between the drain electrode 38 and the source electrode 36.

- the gate-on voltage is applied to the gate electrode 34c, whereby the MOSFET in the MOSFET region 20 is turned on. That is, a channel is formed in the body region 26 at a position facing the gate electrode 34 c, and from the source electrode 36 to the drain electrode 38 via the source region 22, the channel, the drift region 28, and the drain region 30. Current flows.

- the application of the gate-on voltage to the gate electrode 34c is stopped, the channel disappears and the MOSFET is turned off.

- the depletion layer extending from the above-described pn junction reaches the boundary p-type region 59 below the termination trench 54 as indicated by an arrow 82 in FIG. Then, a depletion layer spreads from the boundary p-type region 59 into the drift region 28.

- the drift region 28 between the gate trench 34 and the termination trench 54 has a depletion layer extending from the p-type floating region 32 below the gate trench 34 and a boundary p-type region 59 below the termination trench 54 (that is, the lower end p). Depleted by the depletion layer extending from the mold region 60).

- the depth of the gate trench 34 and the depth of the termination trench 54 are substantially equal (that is, the position in the depth direction of the p-type floating region 32 and the position in the depth direction of the lower end p-type region 60).

- equipotential lines extend in the lateral direction (direction parallel to the surface 72). Thereby, electric field concentration in the vicinity of the termination trench 54 is suppressed.

- the boundary p-type region 59 extends from a range in contact with the lower end of the termination trench 54 to a position in contact with the surface 74 of the semiconductor substrate 12. For this reason, in the vicinity of the surface 74, the depletion layer spreads from the boundary p-type region 59 toward the innermost guard ring region 64. When the depletion layer reaches the innermost guard ring region 64, the depletion layer extends from the guard ring region 64 to the adjacent guard ring region 64. In this way, the depletion layer spreads to the outer peripheral side via each guard ring region 64 sequentially. For this reason, the depletion layer extends widely in the outer peripheral region 50. Thereby, a high breakdown voltage in the outer peripheral region 50 is realized.

- the lower boundary p-type region 59 of the termination trench 54 is provided at a deep position like the p-type floating region 32, so that the electric field in the vicinity of the outer peripheral end of the MOSFET region 20 is obtained. Concentration is suppressed. Further, since the boundary p-type region 59 extends from the bottom surface of the termination trench 54 to the surface 74 of the semiconductor substrate 12 on the outer peripheral side of the termination trench 54, the guard ring formed only in a shallow range near the surface 74. A depletion layer can reach the region 64. As a result, extension of the depletion layer in the outer peripheral region 50 is promoted by the plurality of guard ring regions 64. Further, since the guard ring regions 64 are separated from each other, the potential can be distributed relatively evenly in the outer peripheral region 50. For this reason, a high breakdown voltage in the outer peripheral region 50 is realized.

- the Al high concentration region 61 is formed in the outer peripheral end of the outer peripheral p-type region 62 and in the range exposed to the surface 74.

- a method for manufacturing the semiconductor device 10 will be described.

- a semiconductor wafer 90 consisting only of the n-type layer 28 is prepared.

- the n-type layer 28 is a region that becomes the drift region 28.

- a p-type layer 26 is formed on the surface of the n-type layer 28 by epitaxial growth.

- the p-type layer 26 is a region that becomes the body region 26.

- the surface of the semiconductor wafer 90 within a predetermined range is partially etched.

- etching is performed so that the p-type layer 26 is removed and the n-type layer 28 is exposed as shown in FIG.

- a stepped portion 70 is formed on the surface of the semiconductor wafer 90.

- the stepped portion 70 partitions the surface of the semiconductor wafer 90 into a surface 72 and a surface 74.

- B is implanted into a range including the stepped portion 70 on the surface of the semiconductor wafer 90 (that is, a range extending from the surface 72 to the surface 74).

- B is implanted so that B is distributed from a shallow position to a relatively deep position.

- Al is implanted into the range including the outer peripheral end X1 of the implantation range X in the surface 74 of the semiconductor wafer 90 (that is, the implantation range Y in FIG. 8).

- Al is implanted so that Al is implanted only in the vicinity of the surface 74 of the semiconductor wafer 90 by setting the Al implantation energy low.

- ion implantation into the guard ring region 64 is performed. That is, Al is injected into the outer peripheral side (injection range Z corresponding to each guard ring region 64) of the surface 74 of the semiconductor wafer 90 from the injection range Y.

- Al is implanted so that Al is implanted only in the vicinity of the surface 74 of the semiconductor wafer 90 by setting the Al implantation energy low.

- the width of the injection range Z is narrower than the width of the injection range Y.

- the implanted Al and B are diffused and activated.

- a boundary p-type region 59 and a guard ring region 64 are formed.

- the distribution range of B is widened. That is, compared with the implantation range X, the range in which B after diffusion is distributed becomes considerably wide.

- the width of the Al implantation range Y is widened, the Al high concentration region 61 can be easily disposed at the outer peripheral edge of the boundary p-type region 59 even if the B distribution range is expanded. it can.

- the guard ring region 64 is formed at a shallow position near the surface 74 of the semiconductor wafer 90, the guard ring region 64 can be formed with high accuracy.

- Al implanted into the guard ring region 64 has a low diffusion coefficient in SiC, the guard ring region 64 can be formed with higher accuracy. Therefore, the interval between the guard ring regions 64 can be reduced. Furthermore, the interval between the outer peripheral p-type region 62 and the guard ring region 64 can also be reduced.

- the termination trench 54 is formed at the end of the outer peripheral p-type region 62 (the end opposite to the Al high concentration region 61), and the insulating layer 53 is formed in the termination trench 54. To do.

- the structure in the MOSFET region 20 is formed, and other necessary structures (diffusion layer, electrode, insulating layer, etc.) are formed, whereby the semiconductor device 10 of FIG. 1 is completed.

- the order of each process of the manufacturing method mentioned above can be changed suitably.

- the structure in the MOSFET region 20 may be formed before the structure in the outer peripheral region 50 or may be formed in parallel with the structure in the outer peripheral region 50.

- the interval between the guard ring regions 64 can be reduced. Further, the interval between the outer peripheral p-type region 62 and the guard ring region 64 can also be reduced. Therefore, in this semiconductor device 10, the depletion layer tends to extend in the outer peripheral region 50. For this reason, according to this method, the semiconductor device 10 having a high breakdown voltage in the outer peripheral region 50 can be manufactured.

- interval W3 shows the relationship between the interval W3 (see FIG. 2) between the termination trench 54 and the stepped portion 70 and the DS breakdown voltage (drain-source breakdown voltage) of the semiconductor device 10.

- interval W3 is 10 micrometers or more.

- the lower boundary p-type region 59 (that is, the lower end p-type region 60) of the termination trench 54 is not formed on the MOSFET region 20 side.

- a part of the lower end p-type region 60 may protrude to the MOSFET region 20 side from the termination trench 54.

- the drift region 28 between the gate trench 34 and the termination trench 54 is more easily depleted.

- the protruding portion does not protrude above the lower end of the termination trench 54 (on the body region 26 side).

- the lower end p-type region 60 when a part of the lower end p-type region 60 is located above the lower end depth D1 of the termination trench 54 in the MOSFET region 20 as shown in FIG.

- the distance L1 between them becomes shorter.

- the inter-DS breakdown voltage decreases.

- a part of the lower end p-type region 60 may be disposed above the depth D1, and the distance L1 may be optimized to ensure the withstand voltage between the DSs.

- the stepped portion 70 is formed on the surface of the semiconductor substrate 12, but the surface of the semiconductor substrate 12 may be flat as shown in FIG.

- the body region 26 of the semiconductor device of FIG. 14 is formed by ion implantation. Unlike the epitaxial growth, the ion implantation allows the body region 26 to be formed only in a necessary region on the surface of the semiconductor wafer. Therefore, in the manufacturing process of the semiconductor device of FIG. 14, it is necessary to perform the step of etching part of the p-type layer 26 (body region 26) described in the above-described embodiment (that is, the step of forming the stepped portion 70). There is no. Therefore, in the semiconductor device of FIG. 14, the surface of the semiconductor substrate 12 is flat.

- the lower end p-type region 60 is connected to the outer peripheral p-type region 62.

- the lower end p-type region 60 may be separated from the outer peripheral p-type region 62.

- the outer peripheral p-type region 62 is formed in a shallower range than the termination trench 54. For this reason, the lower end p-type region 60 is separated from the outer peripheral p-type region 62 by the drift region 28.

- the distance L2 between the lower end p-type region 60 and the outer peripheral p-type region 62 is set to a distance at which the depletion layer can extend from the lower end p-type region 60 to the outer peripheral p-type region 62,

- the breakdown voltage of the outer peripheral region 50 can be ensured as in the above-described embodiment.

- the distance L2 is preferably set so as to satisfy the formula of L2 ⁇ ⁇ 2 ⁇ (Vbi ⁇ V) / q ⁇ Nb ⁇ 1/2 .

- ⁇ is a dielectric constant of the drift region 28

- Vbi is a built-in potential between the lower end p-type region 60 and the drift region 28

- V is an applied voltage

- q is an elementary charge

- Nb is This is the n-type impurity concentration of the drift region 28.

- the semiconductor device having the MOSFET has been described.

- another element such as an IGBT may be formed instead of the MOSFET.

- the semiconductor substrate 12 is made of SiC.

- a semiconductor substrate made of another material such as Si may be used.

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、終端トレンチの下端に接するp型の下端p型領域と、外周側から終端トレンチに接しており、半導体基板の表面に露出しているp型の外周p型領域と、外周p型領域よりも外周側に形成されており、半導体基板の表面に露出しているp型の複数のガードリング領域と、外周p型領域を複数のガードリング領域から分離しており、複数のガードリング領域を互いから分離しているn型の外周n型領域を有する半導体装置。

Description

(関連出願の相互参照)

本出願は、2014年2月10日に出願された日本特許出願特願2014-023869の関連出願であり、この日本特許出願に基づく優先権を主張するものであり、この日本特許出願に記載された全ての内容を、本明細書を構成するものとして援用する。

本出願は、2014年2月10日に出願された日本特許出願特願2014-023869の関連出願であり、この日本特許出願に基づく優先権を主張するものであり、この日本特許出願に記載された全ての内容を、本明細書を構成するものとして援用する。

本明細書が開示する技術は、半導体装置に関する。

特開2008-135522号公報に開示の半導体装置は、MOSFETと、MOSFETの周囲に形成されている複数の終端トレンチを有する。各終端トレンチは、MOSFETが形成されている領域を囲むように環状に伸びている。各終端トレンチ内には、絶縁層が配置されている。また、各終端トレンチの底面に接する範囲の半導体層には、p型フローティング領域が形成されている。MOSFETがオフする際には、MOSFETのボディ領域から外周側(終端トレンチが形成されている領域)に向かって空乏層が伸びる。最も内側の終端トレンチの下側のp型フローティング領域まで空乏層が伸びると、そのp型フローティングから外周側に向かってさらに空乏層が伸びる。これによって、空乏層が隣のp型フローティング領域まで伸びると、そのp型フローティング領域からさらに外周側に空乏層が伸びる。このように、空乏層は、各p型フローティング領域を経由しながら、MOSFETが形成されている領域の周囲に広く広がる。これによって、半導体装置の耐圧が向上される。

近年、上述したタイプの半導体装置に対する耐圧の要求がますます高まっている。従来は、上述したp型フローティング領域は、終端トレンチを形成した後に終端トレンチの底面にp型不純物を注入し、その後、注入したp型不純物を半導体層内に拡散させることで形成される。しかしながら、半導体の材料や、その他の製造工程の各種条件によっては、p型不純物の拡散距離が短くなり、各p型フローティング領域の間の間隔を十分に狭めることができない場合がある。このような場合、当該間隔の領域に十分に空乏層を伸展させることが困難となる。各終端トレンチの間の間隔を狭くすることで各p型フローティング領域の間の間隔を狭めることも考え得るが、加工精度の問題等により各終端トレンチ間の間隔を狭くすることには限界がある。従来の終端トレンチの構造では、耐圧の向上に限界があった。したがって、本明細書では、より高耐圧を実現可能な半導体装置を開示する。

本明細書は、半導体基板を有する半導体装置を開示する。この半導体装置は、前記半導体基板内であってその表面に露出しているn型の第1領域と、前記第1領域の下側に配置されているp型の第2領域と、前記第2領域の下側に配置されており、前記第2領域によって第1領域から分離されているn型の第3領域と、前記表面に形成されており、前記第1領域及び前記第2領域を貫通して前記第3領域に達する複数のゲートトレンチと、前記ゲートトレンチ内に配置されている第1絶縁層と、前記ゲートトレンチ内に配置されており、前記第1絶縁層を介して前記第2領域に対向しているゲート電極と、前記ゲートトレンチの下端に接するp型の第4領域と、前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、前記終端トレンチ内に配置されている第2絶縁層と、前記終端トレンチの下端に接するp型の下端p型領域と、前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出しているp型の外周p型領域と、前記外周p型領域よりも外周側に形成されており、前記表面に露出しているp型の複数のガードリング領域と、前記終端トレンチよりも外周側に形成されており、前記第3領域と繋がっており、前記外周p型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離しているn型の外周n型領域を有する。

なお、本明細書において、外周側とは、複数のゲートトレンチが形成されている領域から遠ざかる方向を意味する。また、上述した下端p型領域は、上述した外周p型領域と繋がっていてもよいし、外周p型領域から分離されていてもよい。

この半導体装置では、第1領域、第2領域、第3領域、第4領域及びゲート電極によってスイッチング素子が形成されている。スイッチング素子がオフすると、第2領域から第3領域内に空乏層が広がる。空乏層がゲートトレンチの下端に達すると、空乏層が第4領域に到達する。すると、第4領域からも第3領域内に空乏層が広がる。これによって、スイッチング素子が形成されている領域における耐圧が確保される。また、空乏層が、第2領域から第3領域内に広がる空乏層が終端トレンチの下端に達すると、空乏層が下端p型領域に到達する。すると、空乏層が、下端p型領域及び外周p型領域から外周n型領域内に延びる。外周p型領域から伸びる空乏層が、外周p型領域の隣のガードリング領域に到達すると、そのガードリング領域から隣のガードリング領域に向かってさらに空乏層が伸びる。空乏層は、各ガードリング領域を経由して外周側に向かって広がる。これによって、外周側の領域に空乏層が広く伸展し、耐圧が確保される。このように、この半導体装置では、半導体基板の表面に露出するガードリングによって、空乏層の伸展を促進することができる。また、ガードリング領域は半導体基板の表面に露出する範囲に形成されているため、高精度に形成することができる。このため、ガードリング領域の間の間隔を容易に狭くすることができる。このため、この半導体装置では、ガードリング領域によって十分な耐圧を確保することができる。

上述した半導体装置においては、前記表面に段差部が形成されていることによって、前記表面が、第1表面と、第1表面から突出する第2表面を有していてもよい。前記終端トレンチが、前記第2表面に形成されていてもよい。前記外周p型領域が、前記第2表面から前記第1表面に跨る範囲に露出していてもよい。前記複数のガードリング領域が、前記第1表面に露出していてもよい。また、この場合、前記終端トレンチと前記段差部の間の間隔が、10μm以上であってもよい。

上述したいずれかの半導体装置においては、前記外周p型領域のうちの外周側の端部であって前記表面に露出する領域が、Alの濃度がBの濃度よりも高いAl高濃度領域であり、前記外周p型領域のうちの前記Al高濃度領域に隣接する領域が、Bの濃度がAlの濃度よりも高いB高濃度領域であってもよい。この場合、前記Al高濃度領域の幅が、前記各ガードリング領域の幅よりも広くてもよい。なお、上記の幅は、内周側から外周側に向かう方向における寸法を意味する。

このような構成によれば、外周p型領域における漏れ電流を抑制することができる。

上述したいずれかの半導体装置において、前記下端p型領域の一部が、前記終端トレンチよりも内周側に広がっており、前記終端トレンチよりも内周側に広がっている前記下端p型領域の前記一部が、前記終端トレンチの下端よりも上側に広がっていなくてもよい。

上述したいずれかの半導体装置において、前記ガードリング領域が、Alを含有していてもよい。

このような構成によれば、より高精度にガードリング領域を形成することができる。

上述した段差を有する半導体装置は、以下の方法によって製造してもよい。この方法は、n型層上にp型層を成長させる工程と、前記p型層の一部を除去することで、前記n型層が露出している表面と、前記p型層が露出しており、前記n型層が露出している表面よりも突出する表面を形成する工程と、前記n型層が露出している前記表面から前記p型層が露出している前記表面に跨る範囲にp型不純物を注入することによって、前記外周p型領域を形成する工程と、前記n型層が露出している前記表面にp型不純物を注入することによって、前記ガードリング領域を形成する工程と、前記p型層が露出している前記表面に終端トレンチを形成する工程を有する。

図1に示すように、実施例1に係る半導体装置10はSiC(シリコンカーバイド)からなる半導体基板12を有している。半導体基板12は、MOSFET領域20と、外周領域50を有している。MOSFET領域20には、MOSFETが形成されている。なお、図1では、図の見易さを考慮して、MOSFET領域20内にゲートトレンチ34のみを示している。外周領域50は、MOSFET領域20の外側の領域である。本実施例では、外周領域50は、MOSFET領域20と半導体基板12の端面12aとの間の領域である。外周領域50には、耐圧構造が形成されている。なお、図1では、図の見易さを考慮して、外周領域50内に終端トレンチ54と、境界部p型領域59と、ガードリング領域64のみを示している。

図2に示すように、MOSFET領域20内には、ソース領域22、ボディ領域26、ドリフト領域28、ドレイン領域30、p型フローティング領域32、ゲートトレンチ34、ソース電極36、ドレイン電極38が形成されている。

ソース領域22は、MOSFET領域20内に複数個形成されている。ソース領域22は、高濃度にn型不純物を含むn型領域である。ソース領域22は、半導体基板12の上面に露出する範囲に形成されている。

ボディ領域26は、ソース領域22の側方及び下側に形成されており、ソース領域22に接している。ボディ領域26は、p型領域である。ボディ領域26は、ソース領域22が形成されていない位置において半導体基板12の上面に露出している。

ドリフト領域28は、低濃度にn型不純物を含むn型領域である。ドリフト領域28のn型不純物濃度は、ソース領域22のn型不純物濃度よりも低い。ドリフト領域28は、ボディ領域26の下側に形成されている。ドリフト領域28は、ボディ領域26に接しており、ボディ領域26によってソース領域22から分離されている。

ドレイン領域30は、高濃度にn型不純物を含むn型領域である。ドレイン領域30のn型不純物濃度は、ドリフト領域28のn型不純物濃度よりも高い。ドレイン領域30は、ドリフト領域28の下側に形成されている。ドレイン領域30は、ドリフト領域28に接しており、ドリフト領域28によってボディ領域26から分離されている。ドレイン領域30は、半導体基板12の下面に露出する範囲に形成されている。

ゲートトレンチ34は、MOSFET領域20内に複数個形成されている。ゲートトレンチ34は、半導体基板12の上面に形成された溝である。各ゲートトレンチ34は、ソース領域22とボディ領域26を貫通し、ドリフト領域28に達するように形成されている。図1に示すように、複数のゲートトレンチ34は、互いに平行に伸びている。図2に示すように、各ゲートトレンチ34内には、ボトム絶縁層34aと、ゲート絶縁膜34bと、ゲート電極34cが形成されている。ボトム絶縁層34aは、ゲートトレンチ34の底部に形成された厚い絶縁層である。ボトム絶縁層34aの上側のゲートトレンチ34の側面は、ゲート絶縁膜34bによって覆われている。ボトム絶縁層34aの上側のゲートトレンチ34内には、ゲート電極34cが形成されている。ゲート電極34cは、ゲート絶縁膜34bを介して、ソース領域22、ボディ領域26及びドリフト領域28と対向している。ゲート電極34cは、ゲート絶縁膜34b及びボトム絶縁層34aによって、半導体基板12から絶縁されている。ゲート電極34cの上面は、絶縁層34dによって覆われている。

p型フローティング領域32は、半導体基板12内であって、各ゲートトレンチ34の底面(すなわち、下端)に接する範囲に形成されている。p型フローティング領域32の周囲は、ドリフト領域28に囲まれている。各p型フローティング領域32は、ドリフト領域28によって、互いに分離されている。また、各p型フローティング領域32は、ドリフト領域28によって、ボディ領域26から分離されている。

ソース電極36は、MOSFET領域20内の半導体基板12の上面に形成されている。ソース電極36は、ソース領域22及びボディ領域26と導通している。

ドレイン電極38は、半導体基板12の下面に形成されている。ドレイン電極38は、ドレイン領域30と導通している。

上述したドリフト領域28及びドレイン領域30は、外周領域50まで広がっている。ドリフト領域28とドレイン領域30は、半導体基板12の端面12aまで広がっている。また、ドレイン電極38は、外周領域50を含む半導体基板12の下面全体に形成されている。また、外周領域50内の半導体基板12の上面は、絶縁層52によって覆われている。以下では、MOSFET領域20内のドリフト領域28を、素子部ドリフト領域28aと呼び、外周領域50内のドリフト領域28を、外周部ドリフト領域28bと呼ぶ場合がある。

外周領域50内の半導体基板12の表面には、段差部70が形成されている。段差部70によって、半導体基板12の表面が、中央部側の表面72と、端面12a側の表面74に区画されている。表面72は、表面74に対して上側に突出している。このため、表面72に対応する部分では、表面74に対応する部分よりも、半導体基板12の厚みが厚い。上述したMOSFET領域20は、表面72に対応する部分(厚みが厚い部分)に形成されている。段差部70の高さは、ボディ領域26の厚みよりも大きい。したがって、ボディ領域26の下端よりも、表面74が下側(裏面側)に位置している。

外周領域50内の半導体基板12の表面72には、終端トレンチ54が形成されている。終端トレンチ54内には、絶縁層53が形成されている。終端トレンチ54は、ボディ領域26に隣接する位置に形成されている。終端トレンチ54は、ゲートトレンチ34と略同じ深さを有している。従って、絶縁層53は、ボディ領域26よりも深い位置では、素子部ドリフト領域28aに接している。図1に示すように、終端トレンチ54は、半導体基板12の表面を平面視したときに、MOSFET領域20の周囲を一巡するように伸びている。したがって、ボディ領域26は、絶縁層53によって、外周領域50内のいずれのp型領域からも分離されている。すなわち、本実施例では、終端トレンチ54に囲まれた領域がMOSFET領域20である。

図2に示すように、終端トレンチ54の下端(すなわち、底面)に接する位置に、下端p型領域60が形成されている。本実施例では、下端p型領域60は、MOSFET領域20内には形成されていない。また、終端トレンチ54よりも外周側の領域であって、終端トレンチ54に接する位置には、外周p型領域62が形成されている。外周p型領域62は、表面72に露出する位置から表面74に露出する位置に跨って形成されている。外周p型領域62は、表面72、段差部70及び表面74に露出している。また、外周p型領域62は、終端トレンチ54の下端よりも深い位置まで広がっている。図示するように、本実施例では、下端p型領域60と外周p型領域62が繋がっている。下端p型領域60と外周p型領域62は1つのp型領域であるので、以下ではこれらをまとめて境界部p型領域59と呼ぶ場合がある。すなわち、境界部p型領域59は、終端トレンチ54の下端に露出する位置、表面72に露出する位置及び表面74に露出する位置に跨って延びるp型領域である。図1に示すように、境界部p型領域59は、終端トレンチ54に沿って、MOSFET領域20の周囲を一巡するように形成されている。図2に示すように、境界部p型領域59の下側には、外周部ドリフト領域28bが形成されている。

図3は、外周p型領域62の外周端近傍の拡大断面図を示している。図示するように、外周p型領域62は、Al(アルミニウム)高濃度領域61と、B(ボロン)高濃度領域63を有している。Al高濃度領域61はBよりもAlの濃度が高いp型領域であり、B高濃度領域63はAlよりもBの濃度が高いp型領域である。外周p型領域62は、制御不能な誤差レベルを除いて、BとAl以外のp型不純物を含有していない。Al高濃度領域61は、外周p型領域62が表面74に露出する範囲のうち、外周p型領域62の外周端に形成されている。B高濃度領域63は、Al高濃度領域61以外の外周p型領域62内に形成されている。外周p型領域62の大部分は、B高濃度領域63によって構成されている。図4は、外周p型領域62の外周端近傍における不純物濃度分布(図3のA-A線に沿った不純物濃度分布)を示している。図3、4において、領域61aは、Alを含有するとともに、Bを含有しない領域である。領域61bは、AlとBを含有しており、Alの濃度がBの濃度よりも高い領域である。Al高濃度領域61は、領域61aと領域61bによって構成されている。図3に示すAl高濃度領域61の幅W1(すなわち、内周側から外周側に向かう方向における寸法)は、後述するガードリング領域64のそれぞれの幅W2よりも広い。なお、上記の幅W1、W2は、内周側から外周側に向かう方向における寸法を意味する。

図2に示すように、外周p型領域62の外周側には、複数のガードリング領域64が形成されている。各ガードリング領域64は、p型領域であり、表面74に露出する範囲に形成されている。各ガードリング領域64は、浅い範囲にのみ形成されている。したがって、各ガードリング領域64の下端は、外周p型領域62の下端よりも上側(表面側)に位置している。各ガードリング領域64の下側には、外周部ドリフト領域28bが形成されている。最も内周側(MOSFET領域20側)のガードリング領域64と外周p型領域62の間には、外周部ドリフト領域28bが形成されている。外周部ドリフト領域28bによって、最も内周側のガードリング領域64が外周p型領域62から分離されている。また、各ガードリング領域64の間には、外周部ドリフト領域28bが形成されている。外周部ドリフト領域28bによって、各ガードリング領域64が互いから分離されている。各ガードリング領域64は、p型不純物としてAlを含有している。各ガードリング領域64は、制御不可能な誤差レベルを除いて、Al以外のp型不純物を含有していない。

次に、半導体装置10の動作について説明する。半導体装置10を動作させる際には、ドレイン電極38とソース電極36の間にドレイン電極38がプラスとなる電圧が印加される。さらに、ゲート電極34cに対してゲートオン電圧が印加されることで、MOSFET領域20内のMOSFETがオンする。すなわち、ゲート電極34cに対向している位置のボディ領域26にチャネルが形成され、ソース電極36から、ソース領域22、チャネル、ドリフト領域28、ドレイン領域30を経由して、ドレイン電極38に向かって電流が流れる。ゲート電極34cへのゲートオン電圧の印加を停止すると、チャネルが消失し、MOSFETがオフする。MOSFETがオフすると、ボディ領域26とドリフト領域28の境界部のpn接合からドリフト領域28内に空乏層が広がる。空乏層がMOSFET領域20内のp型フローティング領域32に到達すると、p型フローティング領域32からもドリフト領域28内に空乏層が広がる。これによって、2つのp型フローティング領域32の間のドリフト領域28が効果的に空乏化される。このため、MOSFET領域20内における電界集中が抑制される。これによって、MOSFET領域20内における高い耐圧が実現される。

また、上述したpn接合から伸びる空乏層は、図2の矢印82に示すように、終端トレンチ54の下側の境界部p型領域59にも到達する。すると、境界部p型領域59からドリフト領域28内に空乏層が広がる。ゲートトレンチ34と終端トレンチ54の間のドリフト領域28は、ゲートトレンチ34の下側のp型フローティング領域32から広がる空乏層と終端トレンチ54の下側の境界部p型領域59(すなわち、下端p型領域60)から広がる空乏層によって空乏化される。このとき、ゲートトレンチ34の深さと終端トレンチ54の深さが略等しい(すなわち、p型フローティング領域32の深さ方向の位置と下端p型領域60の深さ方向の位置が略等しい)ため、ゲートトレンチ34と終端トレンチ54の間のドリフト領域28において等電位線が横方向(表面72と平行な方向)に伸びる。これによって、終端トレンチ54の近傍における電界集中が抑制される。

また、境界部p型領域59は、終端トレンチ54の下端に接する範囲から半導体基板12の表面74に接する位置まで広がっている。このため、表面74の近傍では、境界部p型領域59から最も内周側のガードリング領域64に向かって空乏層が広がる。空乏層が最も内周側のガードリング領域64に到達すると、そのガードリング領域64からその隣のガードリング領域64に空乏層が伸展する。このように、空乏層が、各ガードリング領域64を順次経由して外周側に広がる。このため、外周領域50内に空乏層が広く伸展する。これによって、外周領域50内における高い耐圧が実現される。

このように、この半導体装置では、終端トレンチ54の下側の境界部p型領域59がp型フローティング領域32と同様に深い位置に設けられていることによって、MOSFET領域20の外周端近傍における電界集中が抑制される。また、終端トレンチ54よりも外周側において境界部p型領域59が終端トレンチ54の底面から半導体基板12の表面74まで伸びていることで、表面74近傍の浅い範囲内にのみ形成されたガードリング領域64に空乏層が到達することが可能となっている。その結果、複数のガードリング領域64によって外周領域50における空乏層の伸展が促進される。また、各ガードリング領域64が互いから分離されているため、外周領域50内において電位が比較的均等に分布することができる。このため、外周領域50における高い耐圧が実現されている。

また、この半導体装置では、外周p型領域62の外周端であって、表面74に露出する範囲に、Al高濃度領域61が形成されている。このようにAl高濃度領域61が形成されていることによって、外周p型領域62の表面近傍を通る漏れ電流を抑制することができる。

次に、半導体装置10の製造方法について説明する。まず、図5に示すようにn型層28のみからなる半導体ウエハ90を準備する。n型層28は、ドリフト領域28となる領域である。次に、図6に示すように、n型層28の表面に、エピタキシャル成長によってp型層26を形成する。p型層26は、ボディ領域26となる領域である。次に、所定範囲内の半導体ウエハ90の表面を部分的にエッチングする。ここでは、エッチングした範囲において、図7に示すようにp型層26が除去され、n型層28が露出するようにエッチングを行う。これによって、半導体ウエハ90の表面に段差部70が形成される。段差部70によって、半導体ウエハ90の表面が、表面72と表面74に区画される。

次に、境界部p型領域59に対するイオン注入を行う。すなわち、まず、半導体ウエハ90の表面のうちの段差部70を含む範囲(すなわち、表面72から表面74に跨る範囲)にBを注入する。ここでは、Bの注入エネルギーを調節することによって、図8の注入範囲Xに示すように、浅い位置から比較的深い位置までBが分布するようにBを注入する。次に、半導体ウエハ90の表面74のうちの注入範囲Xの外周端X1の含む範囲(すなわち、図8の注入範囲Y)に、Alを注入する。ここでは、Alの注入エネルギーを低く設定することで、半導体ウエハ90の表面74近傍にのみAlが注入されるようにAlを注入する。

次に、ガードリング領域64に対するイオン注入を行う。すなわち、半導体ウエハ90の表面74のうちの注入範囲Yよりも外周側(各ガードリング領域64に対応する注入範囲Z)に、Alを注入する。ここでは、Alの注入エネルギーを低く設定することで、半導体ウエハ90の表面74近傍にのみAlが注入されるようにAlを注入する。なお、注入範囲Zの幅は、注入範囲Yの幅よりも狭い。

次に、半導体ウエハ90を熱処理することで、注入したAlとBを拡散させると共に活性化させる。これによって、図9に示すように、境界部p型領域59とガードリング領域64を形成する。このとき、BはAlよりもSiC中における拡散係数が大きいため、Bの分布範囲が広がる。すなわち、注入範囲Xに比べて、拡散後のBが分布する範囲はかなり広くなる。上述したようにAlの注入範囲Yの幅を広くしておくと、Bの分布範囲が拡大しても、境界部p型領域59の外周端にAl高濃度領域61を容易に配置することができる。また、ガードリング領域64は、半導体ウエハ90の表面74近傍の浅い位置に形成されるため、ガードリング領域64を高精度に形成することができる。特に、ガードリング領域64に注入されるAlはSiC中における拡散係数が低いので、ガードリング領域64をより高精度に形成することができる。したがって、各ガードリング領域64の間の間隔を狭小化することができる。さらに、外周p型領域62とガードリング領域64の間の間隔も狭小化することができる。

次に、図10に示すように、外周p型領域62の端部(Al高濃度領域61とは反対側の端部)に終端トレンチ54を形成し、終端トレンチ54内に絶縁層53を形成する。

その後、MOSFET領域20内の構造を形成し、その他の必要な構造(拡散層、電極、絶縁層等)を形成することで、図1の半導体装置10が完成する。なお、上述した製造方法の各工程の順序は、適宜変更することができる。また、MOSFET領域20内の構造を、外周領域50内の構造より先に形成してもよいし、外周領域50内の構造と並行して形成してもよい。

以上に説明したように、この製造方法によれば、各ガードリング領域64の間の間隔を狭小化することができる。また、外周p型領域62とガードリング領域64の間の間隔も狭小化することができる。したがって、この半導体装置10では、外周領域50に空乏層が伸びやすい。このため、この方法によれば、外周領域50の耐圧が高い半導体装置10を製造することができる。

なお、図11は、終端トレンチ54と段差部70の間の間隔W3(図2参照)と、半導体装置10のDS間耐圧(ドレイン‐ソース間の耐圧)との関係を示している。図示するように、間隔W3が10μm未満となると、DS間耐圧が急激に低下する。このため、間隔W3は10μm以上であることが好ましい。

また、上述した実施例の半導体装置10では、終端トレンチ54の下側の境界部p型領域59(すなわち、下端p型領域60)が、MOSFET領域20側に形成されていなかった。しかしながら、図12に示すように、下端p型領域60の一部が、終端トレンチ54よりもMOSFET領域20側に突出していてもよい。このような構成によれば、ゲートトレンチ34と終端トレンチ54の間のドリフト領域28をより空乏化し易くなる。なお、この場合、その突出している部分が、終端トレンチ54の下端よりも上側(ボディ領域26側)にはみ出していないことが好ましい。すなわち、図13のように下端p型領域60の一部がMOSFET領域20内において終端トレンチ54の下端の深さD1よりも上側に位置していると、下端p型領域60とボディ領域26の間の距離L1が短くなる。距離L1が短くなると、DS間耐圧が低下する。このため、MOSFET領域20内に位置する下端p型領域60は、終端トレンチ54の下端よりも下側にのみ存在することが好ましい。但し、場合によっては、下端p型領域60の一部を深さD1よりも上側に配置し、距離L1を最適化することで、DS間耐圧を確保してもよい。

また、上述した半導体装置10では、半導体基板12の表面に段差部70が形成されていたが、図14に示すように半導体基板12の表面がフラットであってもよい。なお、図14の半導体装置のボディ領域26は、イオン注入により形成される。エピタキシャル成長とは異なり、イオン注入によれば、ボディ領域26を半導体ウエハの表面の必要な領域内にのみ形成することができる。したがって、図14の半導体装置の製造工程では、上述した実施例で説明したp型層26(ボディ領域26)の一部をエッチングする工程(すなわち、段差部70を形成する工程)を実施する必要がない。したがって、図14の半導体装置では、半導体基板12の表面がフラットとなっている。

また、上述した実施例では、下端p型領域60が外周p型領域62と繋がっていた。しかしながら、図15に示すように、下端p型領域60が外周p型領域62から分離されていてもよい。図15では、外周p型領域62が終端トレンチ54よりも浅い範囲に形成されている。このため、ドリフト領域28によって、下端p型領域60が外周p型領域62から分離されている。このような構成でも、下端p型領域60と外周p型領域62の間の距離L2が、下端p型領域60から外周p型領域62まで空乏層が伸展可能な距離に設定されていれば、上述した実施例と同様に外周領域50の耐圧を確保することができる。なお、空乏層を伸展させるために、距離L2は、L2≦{2ε(Vbi-V)/q・Nb}1/2の数式を満たすように設定されていることが好ましい。ここで、εはドリフト領域28の誘電率であり、Vbiは下端p型領域60とドリフト領域28の間の内蔵電位であり、Vは印加電圧であり、qは電気素量であり、Nbはドリフト領域28のn型不純物濃度である。

また、上述した実施例では、MOSFETを有する半導体装置について説明したが、MOSFETに代えてIGBT等の他の素子が形成されていてもよい。また、上述した実施例では、半導体基板12がSiCにより構成されていたが、Si等の他の材質によって構成された半導体基板を使用してもよい。

以上、本発明の具体例を詳細に説明したが、これらは例示にすぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例をさまざまに変形、変更したものが含まれる。

本明細書または図面に説明した技術要素は、単独であるいは各種の組み合わせによって技術的有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

本明細書または図面に説明した技術要素は、単独であるいは各種の組み合わせによって技術的有用性を発揮するものであり、出願時請求項記載の組み合わせに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成するものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

Claims (8)

- 半導体基板を有する半導体装置であって、

前記半導体基板内であってその表面に露出しているn型の第1領域と、

前記第1領域の下側に配置されているp型の第2領域と、

前記第2領域の下側に配置されており、前記第2領域によって第1領域から分離されているn型の第3領域と、

前記表面に形成されており、前記第1領域及び前記第2領域を貫通して前記第3領域に達する複数のゲートトレンチと、

前記ゲートトレンチ内に配置されている第1絶縁層と、

前記ゲートトレンチ内に配置されており、前記第1絶縁層を介して前記第2領域に対向しているゲート電極と、

前記ゲートトレンチの下端に接するp型の第4領域と、

前記表面に形成されており、前記表面を平面視したときに前記複数のゲートトレンチが形成されている領域の周囲を一巡する終端トレンチと、

前記終端トレンチ内に配置されている第2絶縁層と、

前記終端トレンチの下端に接するp型の下端p型領域と、

前記終端トレンチよりも外周側に形成されており、前記終端トレンチに接しており、前記表面に露出しているp型の外周p型領域と、

前記外周p型領域よりも外周側に形成されており、前記表面に露出しているp型の複数のガードリング領域と、

前記終端トレンチよりも外周側に形成されており、前記第3領域と繋がっており、前記外周p型領域を前記複数のガードリング領域から分離しており、前記複数のガードリング領域を互いから分離しているn型の外周n型領域、

を有する半導体装置。 - 前記表面に段差部が形成されていることによって、前記表面が、第1表面と、第1表面から突出する第2表面を有しており、

前記終端トレンチが、前記第2表面に形成されており、

前記外周p型領域が、前記第2表面から前記第1表面に跨る範囲に露出しており、

前記複数のガードリング領域が、前記第1表面に露出している、

請求項1の半導体装置。 - 前記終端トレンチと前記段差部の間の間隔が、10μm以上である請求項2の半導体装置。

- 前記外周p型領域のうちの外周側の端部であって前記表面に露出する領域が、Alの濃度がBの濃度よりも高いAl高濃度領域であり、前記外周p型領域のうちの前記Al高濃度領域に隣接する領域が、Bの濃度がAlの濃度よりも高いB高濃度領域である請求項1~3のいずれか一項の半導体装置。

- 前記Al高濃度領域の幅が、前記各ガードリング領域の幅よりも広い請求項4の半導体装置。

- 前記下端p型領域の一部が、前記終端トレンチよりも内周側に広がっており、

前記終端トレンチよりも内周側に広がっている前記下端p型領域の前記一部が、前記終端トレンチの下端よりも上側に広がっていない、

請求項1~5のいずれか一項の半導体装置。 - 前記ガードリング領域が、Alを含有する請求項1~6のいずれか一項の半導体装置。

- 請求項2の半導体装置を製造する方法であって、

n型層上にp型層を成長させる工程と、

前記p型層の一部を除去することで、前記n型層が露出している表面と、前記p型層が露出しており、前記n型層が露出している表面よりも突出する表面を形成する工程と、

前記n型層が露出している前記表面から前記p型層が露出している前記表面に跨る範囲にp型不純物を注入することによって、前記外周p型領域を形成する工程と、

前記n型層が露出している前記表面にp型不純物を注入することによって、前記ガードリング領域を形成する工程と、

前記p型層が露出している前記表面に終端トレンチを形成する工程、

を有する方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE112014006350.9T DE112014006350B4 (de) | 2014-02-10 | 2014-10-06 | Halbleitereinrichtungen und Verfahren zum Herstellen einer Halbleitereinrichtung |

| CN201480075197.3A CN105981173B (zh) | 2014-02-10 | 2014-10-06 | 半导体装置以及半导体装置的制造方法 |