KR930007523B1 - 반도체 기억 장치 및 그 제조방법 - Google Patents

반도체 기억 장치 및 그 제조방법 Download PDFInfo

- Publication number

- KR930007523B1 KR930007523B1 KR1019900006855A KR900006855A KR930007523B1 KR 930007523 B1 KR930007523 B1 KR 930007523B1 KR 1019900006855 A KR1019900006855 A KR 1019900006855A KR 900006855 A KR900006855 A KR 900006855A KR 930007523 B1 KR930007523 B1 KR 930007523B1

- Authority

- KR

- South Korea

- Prior art keywords

- groove

- capacitor

- semiconductor substrate

- memory device

- insulating film

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/37—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the capacitor being at least partially in a trench in the substrate

- H10B12/377—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the capacitor being at least partially in a trench in the substrate having a storage electrode extension located over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

Landscapes

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

Abstract

내용 없음.

Description

제1도는 이 발명의 한 실시예에 관한 반도체 기억장치의 평면도.

제2도는 제1도에 있어서 Ⅱ-Ⅱ선을 따르는 단면도.

제3a도~제 3k도는 이 발명의 한 실시예에 관한 반도체 기억장치의 제조공정의 단면도.

제4도는 이발명의 다른 실시예에 관한 반도체 기억장치의 평면도.

제5도는 일반의 RAM의 구성의 한예를 표시하는 블록도.

제6도는 메모리 셀의 기록/판독 동작을 설명하기 위하여 표시된 다이나믹형 메모리 셀의 등가회로도.

제7도는 흠형 커패시터를 구비한 종래의 반도체 기억장치의 평면도.

제8도는 제7도에 있는 Ⅷ-Ⅷ선을 따르는 단면도.

제9a도~제9g도는 제8도에 표시하는 반도체 기억장치의 제조공정을 단면도로써표시한 것.

제10도는 흠형 커패시터와 스택트(stacked) 커패시터의 양쪽을 구비한 종래의 기억장치의 단면도.

* 도면의 주요부분에 대한 부호의 설명

11 : 반도체 기판 14 : 게이트 전극

15 : 홈 16 : 스토리지 노드

17,18 : 소스/드레인 영역 19 : 불순물 확산층

20 : 캐패시터 절연막 22 : 셀플레이트 (각도중 , 동일부호는 동일 또는 상당부분을 표시)

이 발명의 일반적인 반도체 기억장치에 관한 것이며, 구체적으로는 , 기억 용량을 증대할 수 있도록 개량된 반도체 기억장치에 관한다.

이 발명은 더우기 그 같은 반도체 기억 장치를 제조하는 방법에 관한다. IC메모리는, 다수의 기억소자로 이루어지는 메로리 셀 어레이와, 입출력에 필요한 주변회로로부터 구성되어 있고, 그들은 동일 기판상에 형성되어 있는 경우가 많다.

제5도는, 일반 RAM의 구성의 한 예를 표시하는 블록도이다. 도면을 참조하여, 메모리 셀 어레이(I)에는, 보수의 워드선 및 복수의 비트선이 서로 교차하도록 배치되어 있다. 이들의 워드선과 비트선과의 작 교점에는, 메로리 셀이 설치되어 있다.

메모리 셀의 선택은, X어드레스 버퍼 디코더(2)에 의하여 1개의 워드선과 Y어드레스 버퍼 디코더(3)에 의하여 선택된 1개의 비트선과의 교점을 기초로 하여 행하여진다. 선택된 셀에 데이타가 기록되거나, 혹은 그 메모리 셀에 축정되어 있던 데이타가 판독되거나 하지만, 이 데이타의 기록/판독의 지시는 R/W제어회로(4)에 의하여 부과되는 판독/기록 제어신호(R/W)에 의하여 행하여진다.

데이타의 기록시에는, 입력데이타(Din)가 R/W제어회로(4)사이에 두고 선택된 메로리 셀에 입력된다. 한편, 데이타의 판독시에는, 선택된 메로리 셀에 축적되어 있는 데이타가 센스 앰프(5)에 의하여 검출된후, 증폭되고, 데이타 출력 버퍼(6)를 사이에 두고 출력 데이타(Dout)로써 외부에 출력된다.

제6도는 메로리 셀의 기록/판독 동작을 설명하기 위하여 표시된 다이나믹형 메로리 셀의 등가 회로도이다. 도면을 참조하여, 다이나믹형 메모리 셀은 1조의 전계 효과형 트랜지스터(7)와 커패시터(8)로 이루어진다.

전계효과형 트랜지스터(7)의 게이트 전극은 워드선(9)에 접속된다. 커패시터(8)에 접속되는 전계효과형 트랜지스터(7)의 소스/트레인 전극은 비트선(10)에 접속된다. 데이타의 기록시에는 워드선(9)에 소정의 전위가 인가된다. 그것에 의하여, 전기효과형 트랜지스터(7)가 도통하고, 비트선(10)에 인가된 전하가 커패시터(8)에 축적된다. 한편, 데이타의 판독시에는 워드선(9)에 소정의 전위가 인가된다.

그것에 의하여, 전계효과형 트랜지스터(7)가 도통하고, 커패시터(8)에 축적되어 있던 전하가 비트선(10)을 사이에 두고 꺼내게 된다. 제7도는 홈형 커패시터 메로리 셀을 구비하는 종래의 바도체 기억 장치의 평면도이며, 제8도는 제7도에 있어서의 Ⅷ-Ⅷ선을 따르는 단면도이다.

이들의 도면을 참조하여, 반도체 기판(11)의 주 표면에는 , 활성영역(21)을 분리하기 위한 소자간 분리용 절연막(12)이 형성되어 있다. 더우기, 반도체 기판(11)의 주표면상에는 게이트 산화막(13)을 사이에 두고 게이트 전극(14)(워드선(9)에 대응)이 형성되어 있다.

게이트 전극(14)은 다결정 실리콘으로 형성된다. 반도체 기판(11)의 주표면상에 있으며, 또한 게이트 전극(14)의 양측에 위치하는 부분에는, 소스/드레인 영역(17,18)이 형성되어 있다. 반도체 기판(11)의 주 표면에는, 홈(15)이 형성되어 있다. 홈(15)의 내벽면에는, 스토리지 노드(16)가 형성되어 있다. 스토리지 노드(16)는, 불순물을 홈(15)의 내면벽에 주입하고, 이것을 확산시키는 것에 의하여 형성된 도전영역에 있다.

스토리지 노드(16)와 소스/드레인 영역(17)과는, 반도체 기판(11)의 주 표면상에 설치된 연결용의 불순물 확산층(19)에서 전기적으로 접속되어 있다. 홈(15)의 왜벽면을 덮도록 커패시터 절연막(20)이 설치되어 있다.

커패시티 절연막(20)의 한 끝단은, 소자간 분리용 절연막(12)의 위에 까지 뻗혀 있다. 커패시터 절연막(20)을 덮도록, 셀플레이트(22)가 설치되어 있다. 셀플레이트(22)의 일부는, 홈(15)내에 묻혀져있다. 게이트 전극(14)및 셀플레이트(22)를 포함하는 반도체 기판(11)의 표면 전면에 층간 절연막(23)이 설치되어 있다. 층간 절연막(23)에는 콘택트 홀(24)이 형성되어 있다. 이 코텍트 홀(24)을 사이에 두고, 비트선(25)이 소스/드레인 영역(18)에 접속되어 있다.

이상과 같이 구성되어 있는 반도체 기억 장치는, 워드선(9)이 선택되어, 게이트 전극(14)에 소정의 전위가 인가되는 것에 의하여, 소스/드레인 영역(17,18)간을 도통시켜, 판독/기록 동작을 행하는 것이다.

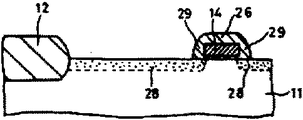

다음에, 상술한 것과 같은 홈형 커패시터를 구비하는 종래의 반도체 기억장치의 제조방법에 관하여 설명한다. 제9a도를 참조하여, 반도체 기판(11)의 주표면에 활성영역을 다른 활성 영역으로 부터 분리하기 위한 소자간 분리용 절연막(12)을 형성한다. 다음에 반도체 기판(11)상에, 전계효과형 트랜지스터의 게이트산화막(13), 게이트 전극(14), 및 산화막(26)을 형성한다.

이들은, 반도체 기판(11)상에 열산화막, 다결정실리콘막, CVDSiO2막을 순차 형성하고, 그후, 이들의 얇은 막을 포토리소그래피 법에서 드라이 에칭하는 것에 의하여 얻어진다.

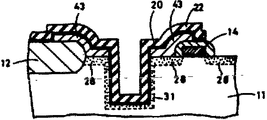

다음에, 제9b도를 참조하여, 반도체 기판(11)의 주표면을 향하여, N형 불순물이온(27)을 자기 정합적으로 주입한다. 그후, 열처리를 행하는 것에 의하여, 반도체 기판(11)의 주표면상에 있어서, 또한 게이트 전극(14)의 양측에 위치하는 부분에, 제1의 불순물 확산 영역(28)이 형성된다. 다음에, 제9c도를 참조하여, 게이트 선극(14)의 측벽에 사이드 월 스페이서(side wall spacer)(29)를 형성한다.

다음에 , 제9d도를 참조하여, 반도체 기판(11)의 표면 전면에, 에칭용의 포토레지스트(30)를 형성한다. 그후, 홈을 형성하여야 할 영역의 상부분에 소망의 형상의 개구부가 되도록, 포토레지스트(30)를 포토리소 그래피법에 의하여 패터닝한다.

그후, 이패터닝된 포토레지스트(30)를 마스크로 하여, 반도체 기판(11)의 주표면의 선택에칭을 행하면(예를 들면, 선택성이 있도록 그 조건이 선택된 반응성 이온에칭에서 행하여 진다.), 반도체 기판(11)의 주표면에 홈(15)이 형성된다.

그후, 포토 레지스트(30)가 제거된다. 그후, 제9e도를 참조하여, 회전 이온 주입법에 의하여, 홈(15)의 내벽면(측벽면 및 저변)에 N형 불순물 이온(27)을 이온 주입한다. 이온 주입후 열처리를 행하면, 홈(15)의 내벽면에, 제1의 불순물 확산 영역과 연이은 제2의 불순물 확산 영역(31)이 형성된다. 다음에, 제9f도를 참조하여, 홈(15)의 내벽면을 포함하는 반도체 기판(11)의 전면에 질화막(32)을 성막하고, 그후, 이 질화막(32)의 열산화를 행한다.

그후, 홈(15)의 내부를 포함하는 반도체 기판(11)의 전면에 다결정 실리콘막(33)을 형성한다. 그후, 이 다결정 실리콘막(339의 위에, 에칭용의 포토레지스트(34)를 형성한다. 그후, 포토 레지스트(34)를 소망의 형상으로 패터닝하고, 이 패터닝된 포토레지스트(34)를 마스크로 하여, 선택에칭법에 의하여, 질화막(32)및 다결정 실리콘막(33)을 패터닝한다. 이것에 의하여, 커패시터 절연막 및 셀플레이트 전극이 얻어진다.

다음에, 제9g도를 참조하여, 반도체 기판(11)의 전면에 층간절연막(23)을 CVD법에 의하여 퇴적한다. 그후, 층간절연막(23)에 콘택트홀(24)을 형성하고 이 콘택트 홀을 사이에 두고, 비트선(10)을 제1불순물 확산 영역(28)에 접속하면, 제8도에 표시하는 반도체 기억장치가 얻어진다. 그런데, 이와같은 홈형 커패시터를 구비하는 반도체 기억 장치에 있어서는, 그 기억용량의 증대는, 제8도를 참조하여, 홈(15)의 깊이를 깊게하는 것에 의하여 실현된다. 그럼, 반도체 기억장치의 기억용량을 증대시키는 다른 방법으로써, 흠형 커패시터와 스톡트 커패시터의 양자를 구비한 반도체 기억장치도 제안되고 있다.

제10도는 특개소 62-190868호 공보에 개시되어있는 , 흠형 켜패시터와 스톡트 커패시터의 양자를 구비한 반도체 기억 장치의 단면도이다. 제10도를 참조하여, 반도체 기판(11)의 주표면에 홈(15)이 형성되어 있다.

홈(15)의 내벽면에는 불순물 확산층(38)이 설치되어, 이 불순물 확산층(38)은 소스영역(35)에 접속되어 있다. 홈(15)의 내면을 덮도록 절연막(39)을 사이에 두고 제1도전층(40)이 형성되어 있다. 제1도전층(40)의 위에는, 절연막(41)을 사이에 두고, 제2의 도전층(42)이 형성되어 있다.

이 반도체 기억장치에서는, 소스영역(35)과 , 불순물 확산층(38)과, 셀플레이트인 제1도전층(40)과, 절연막(39)으로 부터 홈형 커패시터가 형성된다. 그리고 이홈형 커패시터의 위에, 제2도전층(42)과 절연막(41)과, 제1도전층(40)으로부터 구성되는 스톡트 커패시터가 형성된다.

홈형 커패시터와 스톡트 커패시터가 직렬로 접속되어 있고, 이것에 의하여, 메모리 셀 용량이 크게 되어 있다. 이와같은 홈형 커패시터 및 스톡트 커패시터의 양자를 구비한 반도체 기억장치는, 특개소 62-248248호 공보, 특개소 60-6559호 공보, 특개소 62-37962호 공보, 및 특개소 62-7153호 공보에도 개시되어 있다.

제8도에 표시하는 홈형 커패시터를 구비한 반도체 기억 장치에서는, 상술한 것과같이, 커패시터용량을 크게하기 위하여는, 홈(15)을 깊게 하지 않으면 안된다. 그러나, 홈(15)을 깊게하는 것은, 양산성에 있어서 문제점이 있다.

또, 제10도에 표시하는, 홈형 커패시터와 스톡트 커패시터의 양자를 구비한 반도체 기억장치에서는 홈형 커패시터를 형성한후, 더우기 그위에, 스톡트 커패시터를 형성하지 않으면 않되므로, 양자의 위치를 합하여, 고도의 정확성이 요구되고 , 제조공정상, 문제점이 있다. 그러므로, 이 발명의 목적은, 양산화가 용이하게 되도록 개량함과 동시에, 기억용량을 증대할 수 있도록 개량된, 홈형 커패시터를 포함하는 반도체 기억장치를 제공하는 것이다.

이 발명의 다른 목적은, 집적도를 감소시키는 일 없이, 기억용량이 높아진 홈형 커패시터를 포함하는 기억장치의 제조방법을 제공하는데 있다. 이 발명에 따른 반도체 기억 장치는, 홈형 커패시터에 축적된 전하의 유무에 의하여 정부를 기억하는 것이다. 당해 반도체 기억장치는, 주표면을 가지는 반도체 기판을 구비하고 있다.

반도체 기판의 위에는 트랜지스터가 형성되어 있다. 반도체 기판의 주표면에는 홈형이 형성되어 있다. 홈의 내벽면에는 제1도전영역이 형성되어 있다. 반도체 기판의 주표면에는, 상기 제1도전영역과 상기 트랜지스터와를 전기적으로 접속하는 제2도전영역이 설치되어 있다.

제2도전영역상에는, 해당 제2도전영역과 접촉하도록 도전성 부재가 설치되어 있다. 도전성 부재의 노출면 및 상기 홈의 내벽면을 덮도록, 커패시터 절연막이 연속적으로 설치되어 있다. 이 커패시터 절연막을 덮도록 셀플레이트 전극이 설치되어 있다.

이 발명의 다른 국면에 따르는, 반도체 기억장치의 제조방법에 있어서는, 우선, 반도체 기판의 주표면상에 상기 트랜지스터의 게이트 전극이 형성된다. 다음에 ,상기 반도체 기판의 주표면상에 있어서, 또한 상기 게이트 전극의 양측에 위치하는 부분에, 제1의 불순물 확산층이 형성된다.

그후 , 상기 제1의 불순물 확산층을 형성한 후, 상기 반도체 기판의 주표면상에 도전성 부재가 퇴적된다. 다음에, 적어도 상기 홈형 커패시터를 형성하여야 할 영역의 위부분에, 소망의 형상의 개구부가 되도록, 상기 도전성 부재가 패터닝 된다.

그후, 홈형 커패시터용의 홈을 형성하기 위하여, 상기 개구부가 형성되는 것에 의하여 노출한 상기 반도체 기판의 주표면의 일부가 선택적으로 에칭 제거된다. 그후, 홈의 적어도 측벽면에, 제2의 불순물 확산층이 형성된다.

다음에, 도전성 부재의 노출면 및 상기 홈의 내면을 덮도록, 상기 반도체 기판의 주표면에 커패시터 절연막이 형성되고, 이 커패시터 절연막의 위에 셀플레이트 전극이 형성된다.

이 발명에 관한 반도체 기억 장치는, 홈의 내벽에 형성된 제1도전영역, 커패시터 절연막 및 셀플레이트 전극으로 이루어지는 제1의 커패시터와 홈의 주변부상에 설치된 도전성 부재, 커패시터 절연막 및 셀플레이트 전극으로 이루어지는 제2의 커패시터를 구비한다. 그러므로, 이 반도체 기억장치에서는, 제2의 커패시터의 기억용량분만큼, 기억 용량이 증대한다.

또, 홈의 주변부상에 도전성 부재를 설치하므로써 집적도는 하등 감소하지 않는다. 이 발명에 관한 반도체 기억장치의 제조방법에 의하면, 반도체 기판의 위에 형성된 도전성 부재를 소망의 형상에 패터닝하고, 다음에 이패터닝된 도전성 부재를 마스크와 같이 사용하여 자기 정합적으로 반도체 기판의 주표면의 일부를 선택적으로 에칭 제거하고, 그것에 의하여, 반도체 기판의 주표면에 홈을 형성한다.

그로므로, 반도체 기판의 주표면에 홈을 형성하는데 있어서, 고정도의 마스크 맞춤은 요구되지 않는다. 그 결과, 양산성이 향상한다. 이하, 이 발명의 실시예를 도면에 의하영 설명한다.

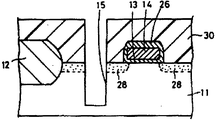

제1도는, 홈형 커패시터 메모리 셀을 구비한 본 발명의 한 실시예에 관한 반도체 기억장치의 평면도이며, 제2도는 제1도에 있어서 Ⅱ-Ⅱ선에 따른 단면도이다. 이들의 도면을 참조하여, 반도체 기판(11)의 주표면에는, 활성영역(21)을 분리하기 위한 소자간 분리용 절연막(12)이 형성되어 있다.

반도체 기판(11)의 주표상에는 게이트 산화막(13)을 사이에 두고 게이트 전극(14)(워드선(9)에 대응)이 형성되어 있다. 게이트 전극(14)은, 예를들면 다결정 실리콘으론 형성된다. 반도체 기판(11)의 주표면상에 있어서, 또한 게이트 전극(14)의 양측에 위치하는 부분에는, 소스/드레인영역(17,18)이 형성되어 있다.

반도체 기판(11)의 주표면에는 홈(15)이 형성되어 있다. 홈(15)의 내벽면에는, 스토리지 노드(16)가 형성되어 있다. 스트레이지 노드(16)와 소스/드레인 영역(17)과는, 반도체 기판(11)의 주표면에 설치된 연결용의 불순물확산층(19)에서 전기적으로 접속되어 있다.

홈(15)의 주변부상에는, 해당 홈(15)을 에워 싸도록 도전성 부재(43)가 설치되어 있다. 도전성 부재(43)는, 소스/드레인 영역(17) 및 연결용의 불순물 확산층(19)과 접촉하도록 설치되어 있다. 도전성 부재(43)의 외연(外緣)(43a)은 게이트 전극(14)의 상방 위치 및 분리 산화막(13)의 상방위치에 까지 뻗혀 있다.

도전성 부재(43)의 내방 단면(43b)과, 홈(15)의 내벽면과는, 동일평면상에 형성되어 있다. 이 도전성 부재(43)는, 예를들면 다결정 실리콘에서 형성된다. 도전성 부재(43)의 노출면 및 홈(15)의 내벽면을 덮도록 연속적으로 커패시터 절연막(20)이 서치되어 있다. 커패시터 절연막(20)을 덮도록 셀플레이트 전극(22)이 설치되어 있다.

반도체 기판(11)의 표면전면에 층간 절연막(23)이 형성되어 있다. 층간 절연막(23)에는 콘택트 홀(24)이 설치되어 있다. 이 코텍트 홀(24)을 사이에 두고, 비트선(25)이 소스/드레인 영역(18)에 접속되어 있다.

이 실시예에 관한 반도체 기억장치에 있어서는, 홈(15)의 내벽면에 형성된 스트레이지 노드(16)와 커패시터 절연막(20)과 셀플레이트 전극(22)으로 부터 홈형의 제1의 커패시터가 형성되고, 홈(15)의 주변부상에 설치된 도전성 부재(43)와 커패시터 절연막(20)과 셀플레이트 전극(22)으로 부터 제2의 커패시터가 형성되어 있다.

제1의 커패시터와 제2의 커패시터는, 커패시터 절연막(20)과 셀플레이트 전극(22)을 공유하고 있으므로, 제1의 커패시터와 제2의 커패시터는 병렬로 접속되어 있는 것이 된다. 실시예에 관한 반도체 기억장치는, 홈형 커패시터를 구비한 종래의 반도체 기억장치에 비하여, 제2의 커패시터의 용량분만큼 기억용량이 많게 되어 있다.

따라서, 반대로, 종래의 반도체 기억장치의 기억용량과 같은 것을 얻으려고 하려면, 홈(15)의 깊이를 얕게 할 수 있다. 홈(15)의 깊이를 얕게 하는 것은, 직접적으로, 양산성의 향상과 연결된다. 또, 제2의 커패시터는 홈(15)의 주변부상에 설치되어, 있으므로 집적도는 하등 감소하지 않는다.

다음에, 제2도에 표시하는 반도체 기억 장치의 제조방법에 관하여 설명한다. 제3a도를 참조하여, 반도체 기판(11)의 주표면에 활성 영역을 다른 활성 영역으로부터 분리하기 위한 소자간 분리용 절연막(12)을 형성한다. 다음에, 반도체 기판(11)상에, 전계효과 트랜지스터의 게이트 산화막(13), 게이트 전극(14)및 산화막(26)을 형성한다.

이들은, 반도체 기판(11)상에 열산화막, 다결정 실리콘 막, CVDSiO2막을 순차 형성하고, 그후, 이들을 포토리소그래피법에 의하여 드라이에칭하는 것에 의하여 얻어진다. 다음에 제3b도를 참조하여, 반도체 기판(11)의 주표면을 향하여, N형 불순물 이온(27)을 자기정합적으로 주입한다. 그후, 열처리를 행하는 것에 의하여, 반도체 기판(11)의 주표면상에 있어서, 또한 게이트 전극(14)의 양측에 위치하는 부분에, 제1의 불수물 확산영역(28)이 형성된다.

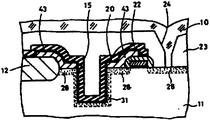

다음에, 제3c도를 참조하여, 게이트 전극(14)의 측벽에 사이드월 스페이서(side Wall spacer)(29)를 형성한다. 다음에 제3d도를 참조하여, 반도체 기판(11)의 주표면상에 다결정 실리콘을 퇴적시켜서, 도전성 부재(43)를 형성한다. 다음에, 제3e도를 참조하여, 전면에 에칭용의 포토레지스터(30)를 형성한다.

그후, 적어도 홈형 커패시터를 형성하여야 할 영역의 상부분에 개구부(44)가 되도록, 포토레지스트(30)를 소망의 형상에 패터닝한다. 다음에. 이 패터닝된 포토레지스트(30)를 마스크로 하여, 도전성 부재(43)를 선택 에칭(예를들면 선택성이 되도록 그 조건이 선택된 반응성 이온 에칭에서 행하여진다)하면, 도전성 부재(43)에 개구부(45)가 형성된다.

또, 이때, 도전성 부재(43)의 외방단연(外方端緣)도 소망의 형상에 패터닝된다. 그후, 포토레지스트(30)를 제거한다. 다음에 제3f도를 참조하여, 반도체 기판(11)의 표면 전면에 에칭용의 포토레지스트(46)를 형성한다. 그후, 홈형 커패시터를 형성하여야 할 영역의 윗부분에 소망에 형상의 개구부(47)가 되도록, 포토레지스트(46)를 패터닝한다.

포토레지스트(46)의 패터닝은 마스크를 사용하여 행하는 것이나, 이때의 마스크 맞추기는 정확하지 않아도 좋다. 도면과 같이, 개구부(47)의 단면이 개구부(46)의 단면과 일치하지 않아도 좋다. 이와같이, 마스크 맞추기를 여유를 갖고 행한 결과, 생산성이 현저하게 향상한다. 그후, 도전성 부재(43)보다도 반도체 기판(11)을 선택적으로 에칭하는 고 선택성 에칭 조건하에서, 반도체 기판(11)을 자기 정합적으로 에칭하고, 반도체 기판(11)의 주표면에 홈(15)을 형성한다.

이때, 에칭이 자기 정합적으로 행하여지므로써, 도전성 부재(43)의 개구부의 단면(43b)과 홈(15)의 내벽면과는 동일 평면상에 형성된다. 그후 포토 레지스트(46)를 제거한다. 그후 제3g도를 참조하여, 회전 이온 주입법에 의하여, 홈(15)의 측벽면 및 저면에 N형 불순물이온(27)을 이온 주입한다.

이온 주입후 열처리를 행하면, 홈(15)의 측벽면 및 저면에, 제1의 불순물 확산 영역(28)과 연이은 제2의 불순물 확산 영역(31)이 형성된다. 다음에,제3h도를 참조하여, 도전성 부재(43)의 노출면 및 홈(15)의 내면을 덮도록, 반도체 기판(11)의 주표면에 질화막(50)을 형성한다. 그후, 이 질화막(50)은 열산화된다.

다음에, 제3i도를 참조하여, 질화막(50)을 덮도록 반도체 기판(11)의 표면 전면에 다결정 실리콘막(49)을 형성한다. 다음에, 반도체 기판(11)의 표면 전면에 에칭 포토레지스트(48)를 형성한다. 그후, 에칭 포토 레지스트(48)를 소망의 형상에 패터닝한다.

다음에, 제3i도 및 제3j도를 참조하여, 다결정 실리콘막(49)과 질화막(50)을 패터닝하면, 소망의 형상의 커패시터 절연막(20)과 셀플레이트 전극(22)이 얻어진다. 다음에, 제3k도를 참조하여, 반도체 기판(11)의 표면 전면에, 층간 절연막(23)을 CVD법에 의하여 퇴적한다. 이때, 층간 절연막의 일부분은 홈(15)의 내부에 파묻힌다.

그후, 층간 절연막(23)에 콘택트 홀(24)을 형성하고, 이 콘택트 홀(24)을 사이에 두고, 비트선(10)을 제1의 불순물 확산 영역(28)에 접속하면, 제2도에 표시하는 반도체 기억장치가 얻어진다.

또한, 상기 실시예에서는, 커패시터 절연막(20)을 열산화한 질화막에서 형성하였으나, Ta2O5막과 같은 고유전율의 막, 혹은 질화막과 Ta2O5막과를 조합시켜서 만든 다층 절연막을 사용하면, 보다 큰 용량을 갖는 반도체 기억 장치가 얻어진다.

또, 본 실시예에서는, 셀플레이트 전극(22)을 홈(15)의 내벽면에 따라서 형성하였으나, 다결성 실리콘을 홈(15)의 가운데 파묻어서 형성하여도 좋다. 제4도는, 이 발명의 다른 실시예의 평면도이다. 제4도에 있어서, II-II선에 따른 단면도는 제2도에 표시한 것과 동일하다.

제4도에 표시하는 실시예는, 이하의 점을 제외하고, 제1도 및 제2도에 표시하는 것과 마찬가지이며, 상당하는 부분에는 동일의 참조번호를 부여하고, 그 설명을 생략한다. 제1도에 표시하는 실시예에서는, 도전성 부재(43)가 홈(15)을 에워 싸도록 형성되어 있으나, 본 실시예에서는 홈(15)의 양측에 도전성 부재(431)와 도전성부재(432)가 분리하여 형성되어 있다.

이 실시예에 관한 반도체 장치에 있어서는, 제4도 및 제2도를 참조하여, 홈(15)의 내벽면에 형성된 스토리지 노드(16)와 커패시터 절연막(20)과 셀플레이트 전극(22)으로부터 홈형의 제1의 커패시터가 형성되고, 홈(15)의 한쪽의 측에 설치된 도전성부재(431)와 커패시터 절연막(20)과 셀플레이트 전극(22)으로부터 제2의 커패시터가 형성되고, 홈(15)의 다른쪽의 측에 설치된 도전성 부재(432)와 캐패시터절연막(20)과 셀플레이트 전극(22)으로 부터 제3의 커패시터가 형성되어 있다.

제1의 커패시터와 제2의 커패시터와 제3의 커패시터는, 커패시터 절연막(20)과 셀플레이트 전극(22)을 공유하고 있으므로, 제1의 커패시터와 제2의 커패시터와 제3의 커패시터는 병렬로 결합되어 있는 것이 된다. 이와같은 구성에 있어서도, 실시예와 마찬가지의 효과를 실현한다. 이상, 본 발명을 요약하면 다음과 같다.

(1)특허청구의 범위 제1항에 기재된 것에 있어서, 상기 트랜지스터는 상기 반도체 기판의 주표면에 형성된 소스영역 및 드레인 영역을 포함하고, 상기 제2도전영역은 상기 소스 영역 혹은 드레인 영역에 접속된다.

(2)특허청구의 범위 제1항의 기재에 있어서, 상기 트랜지스터는 상기 반도체 기판의 주표면상의 게이트 절연막을 사이에 두고 설치된 게이트 전극을 포함하고, 상기 도전성 부재의 외연은 상기 게이트 전극의 위쪽 위치에 까지 뻗고 있다.

(3)특허청구의 범위 제1항의 기재에 있어서, 상기 반도체 기판의 주표면에는 소자와 소자와를 분리하기 위한 분리 산화막이 설치되어 있고, 상기 도전성 부재의 외연은 상기 분리 산화막의 위쪽위치에까지 뻗혀 있다.

(4)특허청구의 범위 제1항의 기재에 있어서, 상기 도전성부재는 상기 홈을 에워싸도록 설치되어 있다.

(5)상기 제4항의 기재에 있어서, 상기 도전성부재의 내쪽단면과, 상기 홈의 내벽면과는, 동일평면상에 형성되어 있다.

(6)특허청구의 범위 제1항의 기재에 있어서, 상기 도전성 부재는 다결성 실리콘에서 형성된다.

(7)특허청구의 범위 제1항의 기재에 있어서, 상기 도전성 부재는 상기 홈의 양측에 설치되어 있다.

(8)특허청구의 범위 제2항의 기재에 있어서, 상기 홈형 커패시터의 홈의 형성은, 상기 도전성부재 보다도 상기 반도체 기판을 선택적으로 에칭하는 고선택성 에칭 조건하에서 자기 정합적으로 행하여진다. 이하 설명한 것에 의하여, 이 발명에 관한 반도체 기억 장치에 의하면, 홈의 내벽에 형성된 제1의 도전영역, 커패시터 절연막 및 셀플레이트 전극으로 이루어지는 홈형의 제1의 커패시터와, 홈의 주변부에 설치된 도전성 부재, 커패시터 절연막 및 셀플레이트 전극으로 이루어지는 제2의 커패시터를 구비한다.

그러므로, 이 반도체 기억장치에서는, 종래의 홈형 커패시터만을 구비한 반도체 기억장치와 비하여, 제2의 커패시터의 기억 용량분만큼, 기억용량이 증대한다. 따라서, 종래의 반도체 기억장치의 기억 용량과 같은 것을 얻으려고하면, 홈의 길이를 얕게 할 수 있다. 그 결과, 양산성이 향상한다.

또, 제2의 커패시터는 홈의 주변부상에 형성되므로, 집적도는 하등 감소하지 않는다. 또, 이 발명의 다른 국면에 따른 반도체 기억장치의 제조 방법에 의하면, 반도체 기판의 주표면에 홈을 형성하는데 있어서, 고정밀도의 마스크 맞추기는 요구되지 않는다.그 결과 생산성이 현저하게 향상하는 효과를 낸다.

Claims (2)

- 홈형 커패시터에 축적된 전하의 유무에 의하여 정보를 기억하는 반도체 기억장치에 있어서, 주표면과 이 주표면에 형성되 홈(15)을 구비하되, 상기 홈(15)은 측벽면과 저면으로 이루어진 반도체 기판(11)과, 상기 기판(11)상에 형성된 트랜지스터와, 상기 홈(15)의 측벽면과 저면에 형성된 제1의 도전영역(31)과, 상기 반도체 기판(11)의 주표면에 설치되어 상기 제1도전영역(31)과 상기 트랜지스터와를 전기적으로 접속하는 제2도전영역(19)과, 상기 반도체 기판(11)상에 설치되어 상기 제2도전영역(19)과 접촉하도록 하되 상기 홈(15)을 노출시키는 개구부를 갖는 도전성 부재(43)와, 상기 홈(15)의 측벽면과 공연하는 상기 도전재(43)의 개구부를 정의하는 측면과, 상기 도전성 부재(43)의 측면 및 상기 홈(15%)의 벽면을 덮도록 설치된 커패시터 절연막(20)과, 상기 커패시터 절연막(20)을 덮도록 설치된 셀플레이트 전극(22)을 구비한 것을 특징으로 하는 반도체 기억장치.

- 홈형 커패시터에 축적된 전하의 유무에 의하여 정보를 기억하는 반도체 기억장치의 제조방법에 있어서, 반도체 기판(11)의 주표면상에 트랜지스터의 게이트 전극(14)을 형성하는 공정과, 상기 반도체 기판(11)의 주표면상에 있어서 또한 상기 게이트전극(14)의 양측에 위치하는 부분에, 제1의 불순물확산층(28)을 형성하는 공정과, 상기 제1의 불순물확산층(28)을 형성한후 상기 반도체 기판(11)의 주표면상에 도전성부재(43)를 퇴적하는 공정과, 적어도 상기 홈혐 커패시터를 형성하여야할 영역의 윗부분에 소망의 형상의 개구부가 되도록, 상기 도전성 부재(43)를 패터닝하는 공정과, 상기 홈형커패서터용의 홈(15)을 형성하기 위하여 상기 개구부가 형성되는 것에 의하여 노출한 상기 반도체 기판(11)의 주표면의 일부를 선택적으로 에칭제거하는 공정과, 상기 홈(15)의 적어도 측벽면에, 제2의 불순물 확산층(31)을 형성하는 공정과, 상기 도전성 부재(43)의 노출면 및 상기 홈(15)의 내면을 덮도록, 상기 반도체 기판(11)의 주표면상에 커패시터 절연막(20)을 형성하는 공정과, 상기 커패시터 절연막(20)의 위에 셀플레이트 전극(22)을 형성하는 공정을 구비한 것을 특징으로 하는 반도체 기억장치의 제조방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP1-129252 | 1989-05-22 | ||

| JP1129252A JPH0770618B2 (ja) | 1989-05-22 | 1989-05-22 | 半導体記憶装置およびその製造方法 |

| JP01-129252 | 1989-05-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR900019236A KR900019236A (ko) | 1990-12-24 |

| KR930007523B1 true KR930007523B1 (ko) | 1993-08-12 |

Family

ID=15004973

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019900006855A KR930007523B1 (ko) | 1989-05-22 | 1990-05-14 | 반도체 기억 장치 및 그 제조방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5089868A (ko) |

| JP (1) | JPH0770618B2 (ko) |

| KR (1) | KR930007523B1 (ko) |

| DE (1) | DE4001872A1 (ko) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5225698A (en) * | 1989-08-12 | 1993-07-06 | Samsung Electronics Co., Inc. | Semi-conductor device with stacked trench capacitor |

| KR910013554A (ko) * | 1989-12-08 | 1991-08-08 | 김광호 | 반도체 장치 및 그 제조방법 |

| US5363327A (en) * | 1993-01-19 | 1994-11-08 | International Business Machines Corporation | Buried-sidewall-strap two transistor one capacitor trench cell |

| US5808335A (en) * | 1996-06-13 | 1998-09-15 | Vanguard International Semiconductor Corporation | Reduced mask DRAM process |

| US6476435B1 (en) | 1997-09-30 | 2002-11-05 | Micron Technology, Inc. | Self-aligned recessed container cell capacitor |

| US20040061990A1 (en) * | 2002-09-26 | 2004-04-01 | Dougherty T. Kirk | Temperature-compensated ferroelectric capacitor device, and its fabrication |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60126861A (ja) * | 1983-12-13 | 1985-07-06 | Fujitsu Ltd | 半導体記憶装置 |

| JPS60213053A (ja) * | 1984-04-09 | 1985-10-25 | Oki Electric Ind Co Ltd | 半導体メモリ素子 |

| JPS6155957A (ja) * | 1984-08-27 | 1986-03-20 | Toshiba Corp | 半導体記憶装置 |

| JPS6156444A (ja) * | 1984-08-28 | 1986-03-22 | Toshiba Corp | 半導体装置 |

| US4914739A (en) * | 1984-10-31 | 1990-04-03 | Texas Instruments, Incorporated | Structure for contacting devices in three dimensional circuitry |

| JPS61150366A (ja) * | 1984-12-25 | 1986-07-09 | Nec Corp | Mis型メモリ−セル |

| JPS61234067A (ja) * | 1985-04-10 | 1986-10-18 | Oki Electric Ind Co Ltd | 高密度型dramセル |

| JPS627153A (ja) * | 1985-07-03 | 1987-01-14 | Hitachi Ltd | 半導体メモリ |

| JPS6237962A (ja) * | 1985-08-13 | 1987-02-18 | Matsushita Electronics Corp | 半導体メモリ装置 |

| JPS6265559A (ja) * | 1985-09-17 | 1987-03-24 | Toshiba Corp | フアクシミリ通信システム |

| JPH0650766B2 (ja) * | 1985-09-27 | 1994-06-29 | 株式会社東芝 | 半導体メモリ装置 |

| JPS6284543A (ja) * | 1985-10-08 | 1987-04-18 | Toshiba Corp | 半導体装置の製造方法 |

| JPS62120070A (ja) * | 1985-11-20 | 1987-06-01 | Toshiba Corp | 半導体記憶装置 |

| JPS62136069A (ja) * | 1985-12-10 | 1987-06-19 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JPS62190868A (ja) * | 1986-02-18 | 1987-08-21 | Matsushita Electronics Corp | 半導体記憶装置 |

| JPS62248248A (ja) * | 1986-04-22 | 1987-10-29 | Matsushita Electronics Corp | 半導体記憶装置 |

| JPS63146461A (ja) * | 1986-12-10 | 1988-06-18 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US4835589A (en) * | 1987-09-28 | 1989-05-30 | Motorola, Inc. | Ram cell having trench sidewall load |

| JPH01154551A (ja) * | 1987-12-11 | 1989-06-16 | Oki Electric Ind Co Ltd | 半導体メモリ集積回路装置及びその製造方法 |

| JPH02177359A (ja) * | 1988-12-27 | 1990-07-10 | Nec Corp | 半導体記憶装置 |

| JPH0738869B2 (ja) * | 1993-02-18 | 1995-05-01 | 工業技術院長 | 下肢装具の靴底 |

-

1989

- 1989-05-22 JP JP1129252A patent/JPH0770618B2/ja not_active Expired - Fee Related

-

1990

- 1990-01-23 DE DE4001872A patent/DE4001872A1/de active Granted

- 1990-05-14 KR KR1019900006855A patent/KR930007523B1/ko not_active IP Right Cessation

-

1991

- 1991-04-02 US US07/680,010 patent/US5089868A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH02307262A (ja) | 1990-12-20 |

| KR900019236A (ko) | 1990-12-24 |

| DE4001872A1 (de) | 1990-11-29 |

| JPH0770618B2 (ja) | 1995-07-31 |

| US5089868A (en) | 1992-02-18 |

| DE4001872C2 (ko) | 1993-09-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR940005888B1 (ko) | 반도체기억장치 및 그 제조방법 | |

| US5032882A (en) | Semiconductor device having trench type structure | |

| EP0337436A2 (en) | Semiconductor memory device having improved dynamic memory cell structure | |

| EP0175378A2 (en) | Dynamic random access memory (DRAM) | |

| KR930010823B1 (ko) | 반도체 기억장치 | |

| JPH0412564A (ja) | 半導体記憶装置およびその製造方法 | |

| US5441916A (en) | Method of manufacturing semiconductor device comprising interconnection | |

| US5247196A (en) | Semiconductor memory device including capacitor having stacked structure and manufacturing method thereof | |

| US5185284A (en) | Method of making a semiconductor memory device | |

| US5225699A (en) | Dram having a large dielectric breakdown voltage between an adjacent conductive layer and a capacitor electrode and method of manufacture thereof | |

| KR960015522B1 (ko) | 반도체 기억장치 | |

| US5229314A (en) | Method of manufacturing field effect transistor having a multilayer interconnection layer therein with tapered sidewall insulation | |

| US4921815A (en) | Method of producing a semiconductor memory device having trench capacitors | |

| KR930007523B1 (ko) | 반도체 기억 장치 및 그 제조방법 | |

| US5272103A (en) | DRAM having a large dielectric breakdown voltage between an adjacent conductive layer and a capacitor electrode and method of manufacture thereof | |

| US5068698A (en) | MOS semiconductor device having high-capacity stacked capacitor | |

| US5183774A (en) | Method of making a semiconductor memory device | |

| US4891327A (en) | Method for manufacturing field effect transistor | |

| JPS59191374A (ja) | 半導体集積回路装置 | |

| US5300444A (en) | Method of manufacturing a semiconductor device having a stacked structure formed of polycrystalline silicon film and silicon oxide film | |

| JPH0612804B2 (ja) | 半導体記憶装置 | |

| US5180683A (en) | Method of manufacturing stacked capacitor type semiconductor memory device | |

| EP0299525A2 (en) | Semiconductor memory device with improved capacitor structure | |

| JP2514435B2 (ja) | 半導体記憶装置およびその製造方法 | |

| JP2512902B2 (ja) | 半導体記憶装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20040809 Year of fee payment: 12 |

|

| LAPS | Lapse due to unpaid annual fee |