KR20180098221A - 수직형 전력 트랜지스터에 대한 종단 영역 아키텍처 - Google Patents

수직형 전력 트랜지스터에 대한 종단 영역 아키텍처 Download PDFInfo

- Publication number

- KR20180098221A KR20180098221A KR1020187012069A KR20187012069A KR20180098221A KR 20180098221 A KR20180098221 A KR 20180098221A KR 1020187012069 A KR1020187012069 A KR 1020187012069A KR 20187012069 A KR20187012069 A KR 20187012069A KR 20180098221 A KR20180098221 A KR 20180098221A

- Authority

- KR

- South Korea

- Prior art keywords

- region

- epitaxial layer

- termination

- transistor structures

- edge

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/665—Vertical DMOS [VDMOS] FETs having edge termination structures

-

- H01L29/7811—

-

- H01L29/0619—

-

- H01L29/0634—

-

- H01L29/0696—

-

- H01L29/404—

-

- H01L29/7395—

-

- H01L29/8611—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/411—Insulated-gate bipolar transistors [IGBT]

- H10D12/441—Vertical IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/01—Manufacture or treatment

- H10D62/051—Forming charge compensation regions, e.g. superjunctions

- H10D62/054—Forming charge compensation regions, e.g. superjunctions by high energy implantations in bulk semiconductor bodies, e.g. forming pillars

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/106—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE] having supplementary regions doped oppositely to or in rectifying contact with regions of the semiconductor bodies, e.g. guard rings with PN or Schottky junctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/105—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices by having particular doping profiles, shapes or arrangements of PN junctions; by having supplementary regions, e.g. junction termination extension [JTE]

- H10D62/109—Reduced surface field [RESURF] PN junction structures

- H10D62/111—Multiple RESURF structures, e.g. double RESURF or 3D-RESURF structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/126—Top-view geometrical layouts of the regions or the junctions

- H10D62/127—Top-view geometrical layouts of the regions or the junctions of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/111—Field plates

- H10D64/112—Field plates comprising multiple field plate segments

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

- H10D8/411—PN diodes having planar bodies

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Chemical & Material Sciences (AREA)

- Composite Materials (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

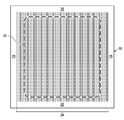

도 2a 및 2b는 실시예들이 구현될 수 있는 VDMOS 트랜지스터의 레이아웃의 평면도이다.

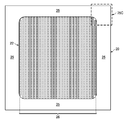

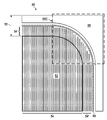

도 3a는 실시예에 따라 구성된 VDMOS 트랜지스터를 포함하는 집적 회로의 코너 부분의 평면도이다.

도 3b 및 3c는 본 실시예에 따른 도 3a의 집적 회로 부분의 상이한 구현체의 단면도이다.

도 3d는 도 3a에 나타낸 코너 부분의 평면도이며, 종래의 구성과의 비교를 나타낸다.

도 3e는 실시예에 따라 구성된 VDMOS 트랜지스터를 포함하는 집적 회로의 코너 부분의 평면도이다.

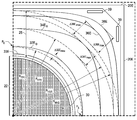

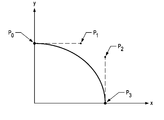

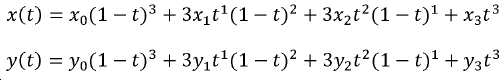

도 4a 및 4b는 본 실시예와 관련하여 사용되는 큐빅 베지어() 곡선의 플롯이다.

도 5a 내지 5d는 특정 실시예에 따라 구성된 VDMOS 트랜지스터의 레이아웃의 평면도이다.

도 6a 및 6b는 도 5a 및 5b의 실시예에 따라 구성된 집적 회로의 부분의 절단도이다.

Claims (32)

- 집적 회로에 있어서,

제1 도전성 타입의 반도체 기판;

상기 기판 위에 놓이고, 상기 기판보다 더 약한 도펀트 농도를 갖는 상기 제1 도전성 타입의 에피택셜 층;

상기 에피택셜 층의 표면에 배치되고, 전기적으로 병렬로 접속된 단자 노드들을 갖는 수직형 트랜지스터 구조체들의 어레이를 포함하는 코어 영역으로서, 상기 기판은 상기 수직형 트랜지스터 구조체들의 상기 단자 노드들 중 하나로서의 역할을 하고, 상기 코어 영역은 상기 집적 회로의 에지들과 병렬로 정렬된 복수의 면을 갖는 것인 상기 코어 영역;

상기 코어 영역을 둘러싸는 종단 영역; 및

상기 종단 영역의 일부 위에 놓이고 상기 종단 영역의 표면 또는 그 부근에 배치되는 부분을 갖는 제1 종단 구조체

를 포함하고,

상기 제1 종단 구조체의 제1 에지는 상기 코어 영역의 면에 평행한 적어도 하나의 실질적으로 선형인 부분과, 국소 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제1항에 있어서,

상기 제1 종단 구조체는,

상기 종단 영역의 일부 위에 놓이고 상기 종단 영역의 표면 또는 그 부근에 배치되는 부분을 갖고, 상기 코어 영역을 둘러싸는 연속적인 도전성 요소를 포함하는, 제1 전계판을 포함하고,

상기 제1 종단 구조체의 상기 제1 에지는 상기 제1 전계판의 외부 에지에 대응하는, 집적 회로. - 제2항에 있어서,

상기 제1 전계판은, 상기 코어 영역의 면에 평행한 적어도 하나의 실질적으로 선형인 부분을 갖는 내부 에지와, 국부 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제2항에 있어서,

상기 제1 전계판의 일부 위에 놓이는 부분을 가지며, 상기 코어 영역을 둘러싸는 연속적인 도전성 요소를 포함하는 제2 전계판을 더 포함하고;

상기 제2 전계판의 외부 에지는, 상기 코어 영역의 면에 평행한 적어도 하나의 실질적으로 선형인 부분과, 국소 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제4항에 있어서,

상기 제1 전계판은 폴리실리콘으로 구성되고, 상기 제2 전계판은 금속으로 구성되는, 집적 회로. - 제4항에 있어서,

상기 제2 전계판의 외부 에지는 상기 제1 전계판의 외부 에지보다 상기 코어 영역으로부터 더 멀리 배치되는, 집적 회로. - 제1항에 있어서,

상기 에피택셜 층의 주변 액티브 영역은 상기 코어 영역을 둘러싸는, 상기 집적 회로의 에지 부근의 표면까지 연장되고;

상기 제1 종단 구조체의 상기 제1 에지의 상기 적어도 하나의 굴곡된 코너 부분은 상기 주변 액티브 영역과 상기 코어 영역 사이의 전계의 등각 매핑 솔루션(conformally mapped soltion)을 실질적으로 따르는, 집적 회로. - 제1항에 있어서,

상기 에피택셜 층의 주변 액티브 영역은 상기 코어 영역을 둘러싸는, 상기 집적 회로의 에지 부근의 표면까지 연장되고, 상기 주변 액티브 영역은 내부 에지를 갖고,

상기 주변 액티브 영역과 전기적으로 접촉하여 상기 표면 부근에 배치되고, 상기 주변 액티브 영역의 적어도 일부 위에 놓이는 부분을 가지며, 상기 코어 영역을 둘러싸는 내부 에지를 갖는 주변 도전체 요소를 더 포함하고,

상기 주변 도전체 요소의 상기 내부 에지는 국소 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제9항에 있어서,

상기 표면 부근에 배치되고, 상기 주변 도전체 요소의 아래에 놓이는 부분을 갖는 두꺼운 산화물 층을 더 포함하고,

상기 제1 종단 구조체의 상기 제1 에지는 상기 두꺼운 산화물 층의 에지에 대응하는, 집적 회로. - 제1항에 있어서,

상기 수직형 트랜지스터 구조체들은 수직형 금속-산화물-반도체 전계-효과-트랜지스터들이고, 각각은 상기 에피택셜 층의 표면에 형성된 제2 도전성 타입의 바디 영역, 상기 바디 영역의 표면에 배치되는 상기 제1 도전성 타입의 소스 영역, 상기 에피택셜 층 내의 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이의 상기 바디 영역의 일부 부근에 배치되는 게이트 전극을 포함하고,

상기 수직형 트랜지스터 구조체들의 상기 소스 영역들은 공통으로 접속되고;

상기 수직형 트랜지스터 구조체들의 상기 게이트 전극들은 공통으로 접속되고;

상기 기판은 상기 수직형 트랜지스터 구조체들의 공통 드레인으로서의 역할을 하는, 집적 회로. - 제11항에 있어서,

상기 수직형 트랜지스터 구조체들의 각각은,

상기 바디 영역의 아래에 놓이고 상기 바디 영역과 접촉하는 위치에서 상기 에피택셜 층에 형성된 상기 제2 도전성 타입의 도핑된 기둥(pillar)을 포함하는, 집적 회로. - 제12항에 있어서,

상기 에피택셜 층에 형성되고 상기 종단 영역에 적어도 부분적으로 배치되는 상기 제2 도전성 타입의 논-액티브(non-active) 기둥을 더 포함하고,

상기 도핑된 기둥 및 논-액티브 기둥은 서로 평행한 스트라이프(stripe)로 상기 표면을 따라 연장되고;

상기 제1 종단 구조체는 상기 종단 영역 내의 상기 도핑된 기둥 및 상기 논-액티브 기둥의 일부를 포함하고,

상기 제1 종단 구조체의 상기 제1 에지는 상기 종단 영역 내의 상기 도핑된 기둥 및 상기 논-액티브 기둥의 종점에 대응하는, 집적 회로. - 제1항에 있어서,

상기 코어 영역은 그 인접 면들 사이의 그 코너 위치들에서 국부 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 외부 경계를 갖는, 집적 회로. - 제1항에 있어서,

상기 제1 에지의 상기 적어도 하나의 굴곡된 코너 부분의 국소 곡률 반경은 상기 코어 영역으로부터 가장 먼 점에서 최소인, 집적 회로. - 제1항에 있어서,

상기 에피택셜 층의 주변 액티브 영역은 상기 코어 영역을 둘러싸는, 상기 집적 회로의 상기 에지들 부근의 표면까지 연장되고;

상기 종단 영역의 일부를 둘러싸고, 상기 코어 영역과 상기 주변 액티브 영역 사이의 상기 에피택셜 층의 표면에 형성되는 제2 도전성 타입의 도핑된 영역을 포함하는 제1 전기적 부유(floating) 연속 가드 링을 더 포함하는, 집적 회로. - 제16항에 있어서,

상기 수직형 트랜지스터 구조체들은 수직형 초접합(superjunction) 금속-산화물-반도체 전계-효과 트랜지스터들이고, 각각은 상기 에피택셜 층에 일정한 깊이로 연장되는 상기 제2 도전성 타입의 기둥 영역, 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 바디 영역, 상기 바디 영역의 표면에 배치되는 상기 제1 도전성 타입의 소스 영역, 상기 에피택셜 층 내의 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이의 상기 바디 영역의 일부 부근에 배치된 게이트 전극을 포함하고,

상기 수직형 트랜지스터 구조체들의 상기 소스 영역들은 공통으로 접속되고,

상기 수직형 트랜지스터 구조체들의 상기 게이트 전극들은 공통으로 접속되고,

상기 기판은 상기 수직형 트랜지스터 구조체들의 공통 드레인으로서의 역할을 하고,

상기 제1 가드 링은 실질적으로 상기 기둥 영역의 깊이와 같은 깊이까지 연장되는, 집적 회로. - 제16항에 있어서,

상기 수직형 트랜지스터 구조체들은 수직형 초접합 금속-산화물-반도체 전계-효과 트랜지스터들이고, 각각은 상기 에피택셜 층에 일정한 깊이로 연장되는 상기 제2 도전성 타입의 기둥 영역, 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 바디 영역, 상기 바디 영역의 표면에 배치된 상기 제1 도전성 타입의 소스 영역, 상기 에피택셜 층 내의 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이의 상기 바디 영역의 일부 부근에 배치된 게이트 전극을 포함하고,

상기 수직형 트랜지스터 구조체들의 상기 소스 영역들은 공통으로 접속되고,

상기 수직형 트랜지스터 구조체들의 상기 게이트 전극들은 공통으로 접속되고,

상기 기판은 상기 수직형 트랜지스터 구조체들의 공통 드레인으로서의 역할을 하고,

상기 제1 가드 링은 상기 기둥 영역의 깊이보다 작은 깊이까지 연장되는, 집적 회로. - 제16항에 있어서,

상기 종단 영역의 일부를 둘러싸고, 상기 제1 가드 링과 상기 주변 액티브 영역 사이의 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 도핑된 영역을 포함하는 제2 전기적 부유 연속 가드 링을 더 포함하는, 집적 회로. - 제19항에 있어서,

상기 수직형 트랜지스터 구조체들은 수직형 초접합 금속-산화물-반도체 전계-효과 트랜지스터들이고, 각각은 상기 에피택셜 층에 일정한 깊이로 연장되는 상기 제2 도전성 타입의 기둥 영역, 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 바디 영역, 상기 바디 영역의 표면에 배치된 상기 제1 도전성 타입의 소스 영역, 상기 에피택셜 층 내의 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이의 상기 바디 영역의 일부 부근에 배치된 게이트 전극을 포함하고,

상기 수직형 트랜지스터 구조체들의 상기 소스 영역들은 공통으로 접속되고,

상기 수직형 트랜지스터 구조체들의 상기 게이트 전극들은 공통으로 접속되고,

상기 기판은 상기 수직형 트랜지스터 구조체들의 공통 드레인으로서의 역할을 하고,

상기 제1 가드 링과 상기 제2 가드 링 중 적어도 하나는 실질적으로 상기 기둥 영역의 깊이와 같은 깊이까지 연장되는, 집적 회로. - 제19항에 있어서,

상기 수직형 트랜지스터 구조체들은 수직형 초접합 금속-산화물-반도체 전계-효과 트랜지스터들이고, 각각은 상기 에피택셜 층에 일정한 깊이로 연장되는 상기 제2 도전성 타입의 기둥 영역, 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 바디 영역, 상기 바디 영역의 표면에 배치된 상기 제1 도전성 타입의 소스 영역, 상기 에피택셜 층 내의 드레인 영역, 및 상기 소스 영역과 상기 드레인 영역 사이의 상기 바디 영역의 일부 부근에 배치된 게이트 전극을 포함하고,

상기 수직형 트랜지스터 구조체들의 상기 소스 영역들은 공통으로 접속되고,

상기 수직형 트랜지스터 구조체들의 상기 게이트 전극들은 공통으로 접속되고,

상기 기판은 상기 수직형 트랜지스터 구조체들의 공통 드레인으로서의 역할을 하고,

상기 제1 가드 링과 상기 제2 가드 링 중 적어도 하나는 상기 기둥 영역의 깊이보다 작은 깊이까지 연장되는, 집적 회로. - 집적 회로에 있어서,

제1 도전성 타입의 반도체 기판;

상기 기판 위에 놓이고, 상기 기판보다 더 약한 도펀트 농도를 갖는 상기 제1 도전성 타입의 에피택셜 층;

상기 에피택셜 층의 표면에 배치되고, 전기적으로 병렬로 접속된 단자 노드들을 갖는 수직형 초접합 트랜지스터 구조체들의 어레이를 포함하는 코어 영역으로서, 상기 기판은 상기 수직형 트랜지스터 구조체들의 상기 단자 노드들 중 하나로서의 역할을 하고, 상기 코어 영역은 상기 집적 회로의 에지들과 병렬로 정렬된 적어도 하나의 면을 갖는 것인 상기 코어 영역;

상기 코어 영역을 둘러싸고, 상기 에피택셜 층에 일정한 깊이로 연장되는 제2 도전성 타입의 하나 이상의 논-액티브 기둥을 포함하는 종단 영역;

상기 코어 영역을 둘러싸는, 상기 집적 회로의 상기 에지들 부근의 표면으로 연장되는 상기 에피택셜 층의 주변 액티브 영역; 및

상기 종단 영역에서 상기 하나 이상의 논-액티브 기둥을 둘러싸고, 상기 논-액티브 기둥과 상기 주변 액티브 영역 사이의 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 도핑된 영역을 포함하는 제1 전기적 부유 연속 가드 링

을 포함하는, 집적 회로. - 제22항에 있어서,

상기 종단 영역에서 상기 하나 이상의 논-액티브 기둥을 둘러싸고, 상기 제1 가드 링과 상기 주변 액티브 영역 사이의 상기 에피택셜 층의 표면에 형성된 상기 제2 도전성 타입의 도핑된 영역을 포함하는 제2 전기적 부유 연속 가드 링을 더 포함하는, 집적 회로. - 제23항에 있어서,

상기 제1 가드 링과 상기 제2 가드 링 중 적어도 하나는 상기 논-액티브 기둥의 깊이보다 작은 깊이까지 연장되는, 집적 회로. - 제23항에 있어서,

상기 제1 가드 링과 상기 제2 가드 링의 각각은 실질적으로 상기 논-액티브 기둥의 깊이까지 연장되는, 집적 회로. - 제22항에 있어서,

상기 제1 가드 링은 상기 논-액티브 기둥의 깊이보다 작은 깊이까지 연장되는, 집적 회로. - 제22항에 있어서,

상기 제1 가드 링은 실질적으로 상기 논-액티브 기둥의 깊이까지 연장되는, 집적 회로. - 집적 회로에 있어서,

제1 도전성 타입의 반도체 기판;

상기 기판의 표면에 배치되고, 전기적으로 병렬로 접속된 단자 노드들을 갖는 수직형 전력 디바이스 구조체들의 어레이를 포함하는 코어 영역으로서, 상기 기판의 후면은 상기 수직형 전력 디바이스 구조체들의 상기 단자 노드들 중 하나로서의 역할을 하고, 상기 코어 영역은 상기 집적 회로의 에지들과 병렬로 정렬된 복수의 면을 갖는 것인 상기 코어 영역;

상기 코어 영역을 둘러싸는 종단 영역; 및

상기 종단 영역의 일부 위에 놓이고 상기 종단 영역의 표면 또는 그 부근에 배치되는 부분을 갖는 제1 종단 구조체

를 포함하고,

상기 제1 종단 구조체의 제1 에지는 상기 코어 영역의 면에 평행한 적어도 하나의 실질적으로 선형인 부분과, 국소 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제28항에 있어서,

상기 제1 종단 구조체는,

상기 종단 영역의 일부 위에 놓이고 상기 종단 영역의 표면 또는 그 부근에 배치된 부분을 갖고, 상기 코어 영역을 둘러싸는 연속적인 도전성 요소를 포함하는 제1 전계판을 포함하고,

상기 제1 종단 구조체의 상기 제1 에지는 상기 제1 전계판의 외부 에지에 대응하는, 집적 회로. - 제29항에 있어서,

상기 제1 전계판의 일부 위에 놓이는 부분을 가지며, 상기 코어 영역을 둘러싸는 연속적인 도전성 요소를 포함하는 제2 전계판을 더 포함하고,

상기 제2 전계판의 외부 에지는, 상기 코어 영역의 면에 평행한 적어도 하나의 실질적으로 선형인 부분과, 국소 곡률 반경이 변하는 2차의 매끄러운 곡선을 실질적으로 따르는 적어도 하나의 굴곡된 코너 부분을 갖는, 집적 회로. - 제28항에 있어서,

상기 기판의 상기 후면은 제2 도전성 타입의 도펀트로 도핑되는, 집적 회로. - 제28항에 있어서,

상기 기판의 상기 후면은 상기 제1 도전성 타입의 도펀트로 추가로 도핑되는, 집적 회로.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US14/873,831 US9806186B2 (en) | 2015-10-02 | 2015-10-02 | Termination region architecture for vertical power transistors |

| US14/873,831 | 2015-10-02 | ||

| PCT/US2016/053934 WO2017058776A1 (en) | 2015-10-02 | 2016-09-27 | Termination region architecture for vertical power transistors |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180098221A true KR20180098221A (ko) | 2018-09-03 |

Family

ID=58424269

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020187012069A Ceased KR20180098221A (ko) | 2015-10-02 | 2016-09-27 | 수직형 전력 트랜지스터에 대한 종단 영역 아키텍처 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US9806186B2 (ko) |

| EP (1) | EP3357091A4 (ko) |

| KR (1) | KR20180098221A (ko) |

| CN (1) | CN108701709A (ko) |

| TW (1) | TW201731097A (ko) |

| WO (1) | WO2017058776A1 (ko) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6844228B2 (ja) * | 2016-12-02 | 2021-03-17 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| US10601413B2 (en) * | 2017-09-08 | 2020-03-24 | Cree, Inc. | Power switching devices with DV/DT capability and methods of making such devices |

| US10720517B2 (en) * | 2017-10-17 | 2020-07-21 | University Of Zagreb Faculty Of Electrical Engineering And Computing | Horizontal current bipolar transistor with floating field regions |

| DE102018115637A1 (de) * | 2018-06-28 | 2020-01-02 | Infineon Technologies Ag | Leistungshalbleiterbauelement |

| JP7113230B2 (ja) * | 2019-02-19 | 2022-08-05 | パナソニックIpマネジメント株式会社 | 半導体素子 |

| CN110911475A (zh) * | 2019-10-30 | 2020-03-24 | 深圳深爱半导体股份有限公司 | 晶体管终端结构及其制造方法 |

| CN111564500A (zh) * | 2020-06-04 | 2020-08-21 | 杭州华芯微科技有限公司 | 一种650v高压vdmos器件 |

| US11222858B1 (en) * | 2020-06-19 | 2022-01-11 | Alpha And Omega Semiconductor International Lp | Semiconductor package having enlarged gate pad and method of making the same |

| CN112635566A (zh) * | 2020-12-28 | 2021-04-09 | 捷捷微电(无锡)科技有限公司 | 一种mosfet器件的终端结构 |

| KR102820902B1 (ko) * | 2021-03-03 | 2025-06-13 | 주식회사 디비하이텍 | 플로팅 영역을 포함하는 슈퍼정션 반도체 소자 및 제조방법 |

| US12132124B2 (en) * | 2021-05-29 | 2024-10-29 | Marvin Motsenbocker | Semiconductor by-pass switch |

| CN113421875B (zh) * | 2021-06-23 | 2024-02-20 | 华北电力大学 | 一种压接型高压大功率芯片结构及功率器件 |

| EP4113623A1 (en) * | 2021-07-01 | 2023-01-04 | Infineon Technologies Austria AG | Transistor device |

| US20230187537A1 (en) * | 2021-11-17 | 2023-06-15 | Panjit International Inc. | Method of forming power semiconductor device |

| CN114823873B (zh) * | 2022-04-28 | 2023-10-27 | 电子科技大学 | 一种超结功率器件终端结构 |

| CN114864670A (zh) * | 2022-05-13 | 2022-08-05 | 电子科技大学 | 缓解体内曲率效应的均匀电场器件及制造方法 |

| US20230378254A1 (en) * | 2022-05-19 | 2023-11-23 | Panjit International Inc. | Semiconductor device and manufacturing method thereof |

| CN115188800A (zh) * | 2022-06-30 | 2022-10-14 | 深圳市千屹芯科技有限公司 | 超级结功率器件 |

| CN120282541B (zh) * | 2025-06-11 | 2025-08-26 | 江苏应能微电子股份有限公司 | 一种沟槽式功率金氧半场效晶体管及其制备工艺 |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3909119A (en) | 1974-02-06 | 1975-09-30 | Westinghouse Electric Corp | Guarded planar PN junction semiconductor device |

| US5877529A (en) | 1996-04-26 | 1999-03-02 | Megamos Corporation | Mosfet termination design and core cell configuration to increase breakdown voltage and to improve device ruggedness |

| JP3908572B2 (ja) * | 2002-03-18 | 2007-04-25 | 株式会社東芝 | 半導体素子 |

| US7638841B2 (en) | 2003-05-20 | 2009-12-29 | Fairchild Semiconductor Corporation | Power semiconductor devices and methods of manufacture |

| JP4289123B2 (ja) | 2003-10-29 | 2009-07-01 | 富士電機デバイステクノロジー株式会社 | 半導体装置 |

| JP4903055B2 (ja) * | 2003-12-30 | 2012-03-21 | フェアチャイルド・セミコンダクター・コーポレーション | パワー半導体デバイスおよびその製造方法 |

| JP2006073740A (ja) | 2004-09-01 | 2006-03-16 | Toshiba Corp | 半導体装置及びその製造方法 |

| DE102005023668B3 (de) * | 2005-05-23 | 2006-11-09 | Infineon Technologies Ag | Halbleiterbauelement mit einer Randstruktur mit Spannungsdurchbruch im linearen Bereich |

| JP2008187125A (ja) | 2007-01-31 | 2008-08-14 | Toshiba Corp | 半導体装置 |

| JP2009088345A (ja) * | 2007-10-01 | 2009-04-23 | Toshiba Corp | 半導体装置 |

| CN102318045B (zh) | 2008-02-14 | 2014-08-06 | 马克斯半导体股份有限公司 | 改良式击穿电压的边缘端点 |

| JP4635067B2 (ja) * | 2008-03-24 | 2011-02-16 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US8222689B2 (en) * | 2008-09-30 | 2012-07-17 | Niko Semiconductor Co., Ltd. | High-voltage metal oxide semiconductor device and fabrication method thereof |

| US8803277B2 (en) | 2011-02-10 | 2014-08-12 | Cree, Inc. | Junction termination structures including guard ring extensions and methods of fabricating electronic devices incorporating same |

| US8786010B2 (en) | 2011-04-27 | 2014-07-22 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| US8673700B2 (en) | 2011-04-27 | 2014-03-18 | Fairchild Semiconductor Corporation | Superjunction structures for power devices and methods of manufacture |

| US9548352B2 (en) * | 2011-07-19 | 2017-01-17 | Alpha And Omega Semiconductor Incorporated | Semiconductor device with field threshold MOSFET for high voltage termination |

| US8802529B2 (en) | 2011-07-19 | 2014-08-12 | Alpha And Omega Semiconductor Incorporated | Semiconductor device with field threshold MOSFET for high voltage termination |

| CN103534809B (zh) * | 2011-08-05 | 2016-08-17 | 富士电机株式会社 | 半导体器件及半导体器件的制造方法 |

| US8680613B2 (en) | 2012-07-30 | 2014-03-25 | Alpha And Omega Semiconductor Incorporated | Termination design for high voltage device |

| US9224852B2 (en) | 2011-08-25 | 2015-12-29 | Alpha And Omega Semiconductor Incorporated | Corner layout for high voltage semiconductor devices |

| CN103000665B (zh) * | 2011-09-08 | 2015-08-19 | 上海华虹宏力半导体制造有限公司 | 超级结器件及制造方法 |

| WO2013046544A1 (ja) * | 2011-09-27 | 2013-04-04 | 株式会社デンソー | 半導体装置 |

| WO2013105350A1 (ja) * | 2012-01-12 | 2013-07-18 | トヨタ自動車株式会社 | 半導体装置とその製造方法 |

| CN106887385B (zh) * | 2012-03-19 | 2020-06-12 | 富士电机株式会社 | 半导体装置的制造方法 |

| JP2013239488A (ja) * | 2012-05-11 | 2013-11-28 | Rohm Co Ltd | 半導体装置 |

| US8487372B1 (en) | 2012-06-29 | 2013-07-16 | Force Mos Technology Co., Ltd. | Trench MOSFET layout with trenched floating gates and trenched channel stop gates in termination |

| US20140097491A1 (en) | 2012-10-05 | 2014-04-10 | Texas Instruments Incorporated | Dielectrically Terminated Superjunction FET |

| US9117899B2 (en) | 2012-11-26 | 2015-08-25 | D3 Semiconductor LLC | Device architecture and method for improved packing of vertical field effect devices |

| JP6263966B2 (ja) * | 2012-12-12 | 2018-01-24 | 富士電機株式会社 | 半導体装置 |

| KR20150131195A (ko) | 2013-03-13 | 2015-11-24 | 디3 세미컨덕터 엘엘씨 | 수직 전계 효과 디바이스들의 온도 보상을 위한 디바이스 아키텍처 및 방법 |

| JP6101183B2 (ja) * | 2013-06-20 | 2017-03-22 | 株式会社東芝 | 半導体装置 |

| US9437673B2 (en) * | 2014-02-05 | 2016-09-06 | Alpha And Omega Semiconductor Incorporated | Floating guard ring for HV interconnect |

| US9590092B2 (en) * | 2014-11-13 | 2017-03-07 | Ixys Corporation | Super junction field effect transistor with internal floating ring |

-

2015

- 2015-10-02 US US14/873,831 patent/US9806186B2/en not_active Expired - Fee Related

-

2016

- 2016-09-27 EP EP16852402.3A patent/EP3357091A4/en not_active Withdrawn

- 2016-09-27 KR KR1020187012069A patent/KR20180098221A/ko not_active Ceased

- 2016-09-27 WO PCT/US2016/053934 patent/WO2017058776A1/en not_active Ceased

- 2016-09-27 CN CN201680067333.3A patent/CN108701709A/zh active Pending

- 2016-09-30 TW TW105131488A patent/TW201731097A/zh unknown

-

2017

- 2017-10-17 US US15/786,246 patent/US10134890B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO2017058776A1 (en) | 2017-04-06 |

| US9806186B2 (en) | 2017-10-31 |

| US20170098705A1 (en) | 2017-04-06 |

| CN108701709A (zh) | 2018-10-23 |

| EP3357091A4 (en) | 2019-06-19 |

| US10134890B2 (en) | 2018-11-20 |

| EP3357091A1 (en) | 2018-08-08 |

| US20180277673A1 (en) | 2018-09-27 |

| TW201731097A (zh) | 2017-09-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10134890B2 (en) | Termination region architecture for vertical power transistors | |

| CN105431946B (zh) | 具有平面状通道的垂直功率金氧半场效晶体管元胞 | |

| US10446679B2 (en) | Method for forming a lateral super-junction MOSFET device and termination structure | |

| US9397154B2 (en) | Termination design by metal strapping guard ring trenches shorted to a body region to shrink termination area | |

| US8704292B2 (en) | Vertical capacitive depletion field effect transistor | |

| US7948033B2 (en) | Semiconductor device having trench edge termination structure | |

| US20130020635A1 (en) | Semiconductor device with field threshold MOSFET for high voltage termination | |

| US9543396B2 (en) | Vertical transistor device structure with cylindrically-shaped regions | |

| JP2016534581A (ja) | 高電圧mosfetデバイスおよび該デバイスを製造する方法 | |

| US20090273031A1 (en) | Semiconductor device | |

| US10325988B2 (en) | Vertical transistor device structure with cylindrically-shaped field plates | |

| US9818743B2 (en) | Power semiconductor device with contiguous gate trenches and offset source trenches | |

| US20230268433A1 (en) | Semiconductor device | |

| US12453139B2 (en) | Transistor device and method for producing a transistor device | |

| EP3158590B1 (en) | Modulated super junction power mosfet devices | |

| US20250234601A1 (en) | Sic mosfets with saturation current pinching structures | |

| KR101550798B1 (ko) | 래치업 억제구조를 가지는 전력용 반도체 장치 및 그 제조방법 | |

| EP1703566A1 (en) | MOS device having at least two channel regions | |

| KR20230046263A (ko) | 트랜지스터 디바이스 및 트랜지스터 디바이스의 제조 방법 | |

| US20250324680A1 (en) | Gate trench power semiconductor devices having enhanced avalanche robustness and methods of forming such devices | |

| KR20220121393A (ko) | 소스 영역 면적이 감소된 슈퍼정션 반도체 소자 및 제조방법 | |

| HK1123125B (en) | Semiconductor device having trench edge termination structure |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20180427 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20210927 Comment text: Request for Examination of Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20221206 Patent event code: PE09021S01D |

|

| E601 | Decision to refuse application | ||

| PE0601 | Decision on rejection of patent |

Patent event date: 20230605 Comment text: Decision to Refuse Application Patent event code: PE06012S01D Patent event date: 20221206 Comment text: Notification of reason for refusal Patent event code: PE06011S01I |