KR101984681B1 - 세트 및 리셋 전압들을 동시에 제공하기 위한 장치들 및 방법들 - Google Patents

세트 및 리셋 전압들을 동시에 제공하기 위한 장치들 및 방법들 Download PDFInfo

- Publication number

- KR101984681B1 KR101984681B1 KR1020147030963A KR20147030963A KR101984681B1 KR 101984681 B1 KR101984681 B1 KR 101984681B1 KR 1020147030963 A KR1020147030963 A KR 1020147030963A KR 20147030963 A KR20147030963 A KR 20147030963A KR 101984681 B1 KR101984681 B1 KR 101984681B1

- Authority

- KR

- South Korea

- Prior art keywords

- voltage

- memory device

- state material

- delete delete

- variable state

- Prior art date

Links

- 238000000034 method Methods 0.000 title abstract description 5

- 239000000463 material Substances 0.000 claims abstract description 55

- 230000005404 monopole Effects 0.000 claims description 4

- 210000004027 cell Anatomy 0.000 description 28

- 238000010586 diagram Methods 0.000 description 10

- 230000008859 change Effects 0.000 description 3

- 230000006399 behavior Effects 0.000 description 2

- 230000005764 inhibitory process Effects 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 230000006978 adaptation Effects 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 210000003850 cellular structure Anatomy 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0097—Erasing, e.g. resetting, circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0026—Bit-line or column circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0028—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0038—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0061—Timing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0083—Write to perform initialising, forming process, electro forming or conditioning

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0085—Write a page or sector of information simultaneously, e.g. a complete row or word line

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/0088—Write with the simultaneous writing of a plurality of cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/79—Array wherein the access device being a transistor

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Materials Engineering (AREA)

- Semiconductor Memories (AREA)

Abstract

어레이에서의 상이한 가변 상태 재료 메모리 셀들에 리셋 및 세트 전압들을 동시에 제공하도록 구성되는 드라이버 회로들을 수반한 것들과 같은, 장치들 및 방법들이 설명된다. 부가적인 장치들, 및 방법들이 설명된다.

Description

우선권 출원

본 출원은, 전체적으로 여기에 참조로서 통합되는, 2012년 4월 12일에 출원된, 미국 출원 일련 번호 제13/445,577호에 대한 우선권의 이득을 주장한다.

몇몇 반도체 디바이스들은 가변 상태 재료들을 포함한다. 예를 들면, 저항성 랜덤 액세스 메모리(RRAM) 셀들과 같은 메모리 셀들은 그 상태가 고 저항 상태에서 저 저항 상태로 및 다시 원래대로 변경될 수 있는 가변 상태 재료를 포함한다. 가변 상태 재료들은 종종 비-휘발성이며 작은 폼 팩터를 가진 메모리 셀들에서 구성될 수 있다. 그러나, 몇몇 구성들에서, 가변 상태 재료들은 플래시 메모리와 같은 다른 저장 기술들보다 긴 프로그램 시간들을 보여줄 수 있다. 속도 및 신뢰성과 같은, 성능에서의 개선들을 제공하는 반도체 디바이스 설계들이 요구된다.

도 1은 본 발명의 실시예에 따른 메모리 셀 구성요소의 제 1 상태의 블록도 설정을 도시한다.

도 2는 본 발명의 실시예에 따라, 도 1로부터 메모리 셀 구성요소의 제 2 상태를 설정하는 블록도를 도시한다.

도 3은 본 발명의 실시예에 따른 가변 저항 재료의 전압-전류 다이어그램을 도시한다.

도 4는 본 발명의 실시예에 따른 메모리 디바이스의 회로도를 도시한다.

도 5는 본 발명의 실시예에 따른 전압 테이블을 도시한다.

도 6은 본 발명의 실시예에 따른 메모리 디바이스의 블록도를 도시한다.

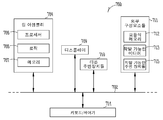

도 7은 본 발명의 실시예에 따른, 메모리 디바이스를 포함한, 정보 핸들링 시스템을 도시한다.

도 2는 본 발명의 실시예에 따라, 도 1로부터 메모리 셀 구성요소의 제 2 상태를 설정하는 블록도를 도시한다.

도 3은 본 발명의 실시예에 따른 가변 저항 재료의 전압-전류 다이어그램을 도시한다.

도 4는 본 발명의 실시예에 따른 메모리 디바이스의 회로도를 도시한다.

도 5는 본 발명의 실시예에 따른 전압 테이블을 도시한다.

도 6은 본 발명의 실시예에 따른 메모리 디바이스의 블록도를 도시한다.

도 7은 본 발명의 실시예에 따른, 메모리 디바이스를 포함한, 정보 핸들링 시스템을 도시한다.

본 발명의 다양한 실시예들의 다음의 상세한 설명에서, 그 일부를 형성하며, 본 발명의 실시될 수 있는 특정 실시예들이 예시로서 도시되는 첨부한 도면들에 대한 참조가 이루어진다. 이들 실시예들은 이 기술분야의 숙련자들이 본 발명을 실시할 수 있게 하기 위해 충분히 상세히 설명된다. 다른 실시예들이 이용될 수 있으며 구조적, 논리적, 및 전기적 변화들이 이루어질 수 있다.

도 1은 본 발명의 실시예에 따른 메모리 셀의 예시적인 구성요소(100)를 도시한다. 가변 상태 재료(102)가 제 1 전극(104) 및 제 2 전극(106) 사이에 위치되어 도시된다. 단지 가변 상태 재료(102)가 도시되지만, 선택된 예들에서, 개재 재료 층들과 같은 다른 구조들이 제 1 및 제 2 전극들(104, 106) 사이에 위치된 가변 상태 재료와 함께 포함될 수 있다. 일 예에서, 가변 상태 재료(102)는 저항 스위칭 재료이다. 가변 상태 재료들(102)의 다른 예들은 자기 스위칭 재료들, 또는 검출 가능한 전자 상태를 가진 다른 스위칭 재료들을 포함할 수 있다.

일 예에서, 전압이 가변 상태 재료(102)에 걸친 방향(110)으로 인가될 때, 가변 상태 재료(102)의 상태는 고 저항 상태(103)로부터 저 저항 상태(105)로 변경된다. 구성요소(100)와 같은 구성요소를 포함한 메모리 셀들의 어레이에서, 고 저항 상태는 로직 1 또는 로직 0 값과 같은, 데이터의 디지털 비트를 표현할 수 있다. 로우 및 컬럼 선택 회로와 같은, 선택 회로는 셀들의 어레이로부터 원하는 메모리 셀(가변 상태 재료(102)를 포함한)을 선택하고, 저항 상태를 질의하고 및/또는 변경하기 위해 사용될 수 있으며, 그에 따라 데이터 호출 및 저장 능력을 제공한다.

다수의 메커니즘들이 가변 상태 재료(102)의 물리 상태(및 그러므로, 저항)를 변경하기 위해 사용될 수 있다. 일 예에서, 가변 상태 재료(102)는 실질적으로 비정질 상태에서 실질적으로 결정질 상태로 변경된다. 또 다른 예에서, 전압의 인가 시, 하나 이상의 도전성 필라멘트들이 제 1 전극(104) 및 제 2 전극(106) 사이에서의 거리를 브리징하는 가변 상태 재료(102) 내에 형성된다. 다양한 메커니즘들에서, 상태 변화는 가역적이다.

도 2는 저 저항 상태(105)에서, 도 1로부터의 예시적인 구성요소(100)를 도시한다. 도 1에 도시된 것으로부터 반대 방향으로 제 2 전압(112)의 인가에 의해, 가변 상태 재료(102)는 저 저항 상태(105)로부터 다시 고 저항 상태(103)로 반전된다. 이러한 식으로, 가변 상태 재료(102)의 물리적 상태(및 그에 따라 저항)는 적어도 두 개의 가능한 상태들 중 선택된 것을 차지하기 위해 원하는 대로 변경될 수 있다.

도 3은 쌍극 가변 상태 재료의 예시적인 전압/전류 다이어그램(300)을 도시한다. 다이어그램은 X-축(302) 상에서의 전압 및 Y-축(304) 상에서의 전류를 도시한다. 동작에 있어서, 가변 상태 재료는 예시된 곡선(301)의 고 저항 부분(306)을 따라 고 저항 행동을 보여준다. 인가된 전압이 기준 전압 레벨(318)에 대하여 제 1 전압 범위(310), 또는 제 2 전압 범위(312) 내에 있다면, 가변 상태 재료는 곡선(301)의 고 저항 부분(306) 내에 남아있다. 인가된 전압이 기준 전압 레벨(318)에 대하여 제 3 전압(314)보다 크거나 또는 동일하다면(결과적으로 전압 범위(310)의 상한보다 큰), 가변 상태 재료는 곡선(301) 상에서의 포인트(303)에 의해 예시된 바와 같이 저 저항을 보여주며 곡선(301)의 저 저항 부분(308)으로 이동한다. 가변 상태 재료는 인가된 전압 크기가 기준 전압 레벨(318)에 대하여 제 4 전압(316)보다 크거나 또는 동일할 때까지(결과적으로 전압 범위(312)의 크기보다 큰) 곡선(301)의 저 저항 부분(308)에 남아있을 것이다. 그 후 가변 상태 재료는 다시 곡선(301)의 고 저항 부분(306)으로 리턴할 것이다.

도 3은 쌍극 가변 상태 재료 행동을 예시하지만, 여기에 설명된 몇몇 디바이스들은 단극 가변 상태 재료를 사용할 수 있다. 단극 가변 상태 재료에서, 상태는 동일한 방향으로 인가된 전압의 상이한 크기들의 인가에 의해 변경될 수 있다. 하나의 쌍극 예에서, 기준 전압(318)은 대략 0 볼트들이며, 제 3 전압(314) 및 제 4 전압(316)은 크기가 실질적으로 동일하며, 극성이 반대이다. 예를 들면 제 3 전압(314)은 대략 1 볼트일 수 있으며, 제 4 볼트(316)는 대략 -1 볼트일 수 있다.

양 전용 전압 범위 예에서, 전압 오프셋에 의해 정의된 바와 같이, 기준 전압(318)은 동일한 크기의 제 3 전압(314) 및 제 4 전압(316)을 갖고, 대략 3 볼트들일 수 있다. 예를 들면, 제 3 전압(314)은 대략 4 볼트들(기준 전압(318) 더하기 약 1 볼트의 전압 오프셋)일 수 있으며 제 4 전압(316)은 대략 2 볼트들(기준 전압(318) 빼기 약 1 볼트의 전압 오프셋)일 수 있다.

가변 상태 재료들은 비교적 작은, 비-휘발성 메모리 셀들로 형성될 수 있다. 일 예에서, 6개의 트랜지스터들을 사용하는 트랜지스터-기반 정적 랜덤 액세스 메모리(SRAM) 셀들과 대조적으로, 1 트랜지스터, 1 저항기(1T1R) 구성이 가능하다.

도 4는 본 발명의 실시예에 따른 가변 상태 재료를 포함한 장치(400)의 예시적인 회로도를 도시한다. 일 예에서, 장치(400)는 메모리 디바이스를 포함한다. 여기에 사용된 바와 같이, “장치”는 이에 제한되지 않지만, 시스템들, 디바이스들, 회로들, 칩 어셈블리들 등을 포함한, 다수의 상이한 구조들 중 임의의 것을 나타내기 위해 광범위하게 사용된다. 도 4의 예에서, 장치(400)는 메모리 셀들(410)의 어레이(402), 및 드라이버 회로(404)를 포함한다. 일 예에서, 드라이버 회로(404)는 어레이(402)에서의 상이한 메모리 셀들(410)에 상이한 전압들을 동시에 제공하도록 구성된다.

어레이(402)에서의 셀들(410) 중 적어도 몇몇은 가변 상태 재료 구성요소(412)를 포함한다. 일 예에서, 가변 상태 재료 구성요소(412)는 도 1 및 도 2에 설명된 예들과 유사하거나 또는 동일한, 제 1 전극 및 제 2 전극 사이에 결합된 가변 상태 재료를 포함한다. 어레이(402)에서의 메모리 셀들(410)은 선택기 디바이스(414)를 더 포함할 수 있다. 선택된 예들에서, 크로스 포인트 아키텍처와 같이, 선택기 디바이스가 포함되지 않을 수 있다. 일 예에서, 선택기 디바이스(414)는 n-형 금속 산화물(NMOS) 트랜지스터를 포함한다. 일 예에서, 선택기 디바이스(414)는 p-형 금속 산화물(PMOS) 트랜지스터를 포함한다. 선택기 디바이스들(414)의 다른 예들은 부가적인 회로, 다이오드들, 및 다른 전자 디바이스들을 포함할 수 있다.

도 4는 어레이(402)에서의 선택기 디바이스들(414)에 결합된 다수의 액세스 라인들(408)을 추가로 도시한다. 일 예에서, 다수의 액세스 라인들(408)은 다수의 워드 라인들을 포함한다. 소스(403), 및 다수의 데이터 라인들(406a 내지 406c)이 어레이(402)에서의 메모리 셀들(410)에 결합되어 도시된다. 일 예에서, 다수의 데이터 라인들(406)은 다수의 비트 라인들을 포함한다. 도 4의 예에서, 드라이버 회로(404)는 컬럼 드라이버로서 구성된다.

일 예에서, 드라이버 회로(404)는 상이한 메모리 셀들의 데이터 라인들(406a 내지 406c)에 다수의 상이한 전압들을 동시에 제공하도록 구성된다. 드라이버 회로(404)는 제 1 전압 입력 노드(420), 제 2 전압 입력 노드(422), 및 제 3 전압 입력 노드(424)를 포함하여 도시된다. 3개의 상이한 전압 입력 노드들이 도시되지만, 두 개의 전압 입력 노드들, 또는 3개 이상의 전압 입력 노드들을 포함한 다른 구성들이 다양한 실시예들의 범위 내에 있다.

드라이버 회로는 또한 상이한 메모리 셀들에 전압 입력 노드들(420, 422, 및 424)을 동시에 선택적으로 결합하기 위해 선택 회로(404)를 포함할 수 있다. 선택 회로(404)는 각각이 전압 입력 노드들(420, 422, 및 424) 중 임의의 하나를 선택하며 그에 따라 어레이(402)에서의 하나 이상의 선택된 메모리 셀들(410)에 선택된 전압을 인가할 수 있는 다수의 선택기 회로들(405a 내지 405c)을 포함할 수 있다. 도시된 예에서, 선택기 회로들(405a 내지 405c)은 어레이(402)에서의 상이한 메모리 셀들(410)에 상이한 전압들을 인가하기 위해 개별적으로 선택 가능하다. 일 예에서, 상이한 전압은 그것들이 인가되는 시간에 걸쳐 실질적으로 일정한 별개의 전압들이다. 일 예에서, 전압 입력 노드들(420, 422, 424) 상에서의 상이한 전압들은 시간의 선택된 길이에 걸쳐 가변적일 수 있다.

일 예에서, 전압 입력 노드들(420, 422, 424)은 세트 전압 노드, 리셋 전압 노드, 및 금지 전압 노드로서 구성된다. 예로서 도 3을 사용하여, 기준 전압(318)은 금지 전압을 포함한다. 금지 전압을 수신하는 어레이(402)에서의 메모리 셀들(410)은 고 저항 상태로 프로그램되지 않거나, 또는 고 저항 상태로부터 저 저항 상태로 반전될 것이다.

세트 전압은 제 3 전압(314)과 같이, 금지 전압 더하기 오프셋 전압을 포함할 수 있다. 리셋 전압은 제 4 전압(316)과 같이, 금지 전압 빼기 오프셋 전압을 포함할 수 있다.

예를 들면, 제 1 선택기 회로(405a)는 데이터 라인(406a)에 제 2 전압 입력 노드(422)를 선택적으로 결합하여 도시된다. 일 예에서 제 2 전압 입력 노드(422)는 세트 전압을 포함한다. 일 예에서, 세트 전압은 대략 4 볼트들과 같다.

제 2 선택기 회로(405b)는 데이터 라인(406b)에 제 3 전압 입력 노드(424)를 선택적으로 결합하여 도시된다. 일 예에서, 제 3 전압 입력 노드(424)는 리셋 전압을 포함한다. 일 예에서, 리셋 전압은 대략 2 볼트들과 같다.

제 3 선택기 회로(405c)는 데이터 라인(406c)에 제 1 전압 입력 노드(420)를 선택적으로 결합하여 도시된다. 일 예에서, 제 1 전압 입력 노드(420)는 금지 전압을 포함한다. 일 예에서, 금지 전압은 대략 3 볼트들과 같다.

동작에 있어서, 선택기 회로들(405a 내지 405c)의 각각은 개별적으로 선택 가능하며, 전압 입력 라인들(420, 422, 424) 로부터 임의의 원하는 데이터 라인(406a 내지 406c)으로 임의의 원하는 전압을 동시에 제공할 수 있다. 장치(400)의 성능은 도 4에 도시된 드라이버 회로(404)를 사용하여 강화될 수 있다. 예를 들면, 어레이(402)의 주어진 컬럼에서 선택된 셀들은 저 저항 상태로 설정되지만, 어레이(402)의 상이한 주어진 컬럼에서 다른 선택된 셀들이 동시에 리셋될 수 있다. 부가적으로, 동시에, 어레이(402)에서의 다른 셀들은 인가된 금지 전압의 결과로서 그것들 상에 수행된 어떤 동작도 없을 수 있다. 데이터 프로그래밍 동작 횟수들은 단지 한 번에 하나의 전압을 어레이로 구동시킬 수 있는 디바이스들에 비교될 때 2배 이상만큼 감소될 수 있다.

도 5는 선택된 데이터 라인(502), 선택되지 않은 데이터 라인(504), 선택된 액세스 라인(506), 및 선택되지 않은 액세스 라인(508)의 동작을 도시한 예시적인 전압 테이블을 예시한다. 일 예에서, 도 4로부터의 드라이버 회로(404)는 도 5의 테이블에 도시된 전압들을 구동시킨다. 예시적인 판독 동작에서, 선택된 데이터 라인(502)은 판독 전압으로 구동된다. 일 예에서, 판독 전압은 도 3으로부터의 제 1 전압 범위(310)와 동일하다. 뿐만 아니라 예시적인 판독 동작에서, 선택된 액세스 라인(506)은 논리적 고 전압으로 구동되며, 선택되지 않은 액세스 라인(508)은 대략 접지로 구동된다. 일 예에서, 선택되지 않은 데이터 라인(504)은 대기 전압으로 구동된다.

예시적인 세트 동작에서, 선택된 데이터 라인(502)은 금지 전압 더하기 전압 오프셋으로 구동된다. 일 예에서, 세트 전압은 도 3으로부터의 제 3 전압(314)과 동일하다. 뿐만 아니라 예시적인 세트 동작에서, 선택된 액세스 라인(506)은 논리적 고 전압으로 구동되며, 선택되지 않은 액세스 라인(508)은 대략 접지로 구동된다. 일 예에서, 선택되지 않은 데이터 라인(504)은 금지 전압으로 구동된다. 일 예에서, 금지 전압은 도 3으로부터의 기준 전압(318)과 동일하다.

예시적인 리셋 동작에서, 선택된 데이터 라인(502)은 금지 전압 빼기 전압 오프셋으로 구동된다. 일 예에서, 리셋 전압은 도 3으로부터의 제 4 전압(316)을 포함한다. 뿐만 아니라 예시적인 리셋 동작에서, 선택된 액세스 라인(506)은 논리적 고 전압으로 구동되며, 선택되지 않은 액세스 라인(508)은 대략 접지로 구동된다. 일 예에서, 선택되지 않은 데이터 라인(504)은 금지 전압으로 구동된다. 일 예에서 금지 전압은 도 3으로부터의 기준 전압(318)을 포함한다.

도 6은 도 4로부터의 드라이버 회로(404)와 유사하거나 또는 동일한 드라이버 회로를 통합한 메모리 시스템(600)의 형태에서의 장치의 일 부분을 예시한다. 메모리 시스템(600)은 메모리 셀들의 어레이(602)를 포함하며, 이것은 예를 들면 RRAM 또는 상기 다양한 실시예들에 설명된 바와 같이 동작하는 가변 상태 재료를 통합한 다른 메모리 셀들을 포함할 수 있다. 메모리 시스템(600)은 명령어 버스(608)를 통해 메모리 명령어들을 수신하며 다양한 메모리 동작들을 실행하기 위해 메모리 시스템(600) 내에서 대응하는 제어 신호들을 발생시키는 명령어 디코더(606)를 포함한다. 로우 및 컬럼 어드레스 신호들은 어드레스 버스(620)를 통해 메모리 시스템(600)에 인가되며 어드레스 래치(610)에 제공된다. 어드레스 래치는 그 후 별개의 컬럼 어드레스 및 별개의 로우 어드레스를 출력한다.

로우 및 컬럼 어드레스들은 어드레스 래치(610)에 의해, 각각 로우 어드레스 디코더(622) 및 컬럼 어드레스 디코더(628)와 같은, 선택 회로에 제공된다. 컬럼 어드레스 디코더(628)는 각각의 컬럼 어드레스들에 대응하는 어레이(602)를 통해 연장된 데이터 라인들을 선택한다. 일 예에서 컬럼 어드레스 디코더(628)는 도 4의 드라이버 회로(404)와 유사한 드라이버 회로를 포함한다. 로우 어드레스 디코더(622)는 수신된 로우 어드레스들에 대응하는 어레이(602)에서의 메모리 셀들의 각각의 로우들을 활성화시키는 액세스 라인 드라이버(624)에 연결된다. 일 예에서 어레이(602)에서의 메모리 셀들의 로우들은 도 4로부터의 데이터 라인들(408)에 대응한다. 명령어 디코더(606)는 메모리 어레이(602) 상에서 다양한 동작들을 수행하기 위해 명령어 버스(608)에 인가된 메모리 명령어들에 응답한다. 특히, 명령어 디코더(606)는 메모리 어레이(602)로부터 데이터를 판독하며 그것으로 데이터를 기록하도록 내부 제어 신호들을 발생시키기 위해 사용된다.

컴퓨터와 같은, 정보 핸들링 시스템의 형태에서의 장치의 실시예가 고-레벨 디바이스 애플리케이션의 실시예를 도시하기 위해 도 7에 포함된다. 도 7은 본 발명의 실시예에 따른 메모리 디바이스(707)(예로서, 도 4에 도시된 장치(400) 및/또는 도 6에 도시된 장치(600)와 유사하거나 또는 동일한 디바이스)를 포함하는 적어도 하나의 칩 또는 칩 어셈블리(704)를 통합한 정보 핸들링 시스템(700)의 블록도이다. 어셈블리(704)는 또한 프로세스(706) 및 다른 로직(708)을 포함할 수 있다.

일 예에서, 메모리 디바이스(707)는 RRAM과 같은 가변 상태 재료 메모리 디바이스를 포함한다. 도 7에 도시된 정보 핸들링 시스템(700)은 단지 본 발명이 사용될 수 있는 시스템의 일 예이다. 다른 예들은 이에 제한되지 않지만, 개인용 데이터 보조기들(PDA들), 태블릿 컴퓨터들, 카메라들, 셀룰러 전화기들, MP3 플레이어들, 항공기, 위성들, 군용 차량들 등을 포함한다.

이 예에서, 정보 핸들링 시스템(700)은 시스템의 다양한 구성요소들을 결합하기 위해 시스템 버스(702)를 포함하는 데이터 프로세싱 시스템을 포함한다. 시스템 버스(702)는 정보 핸들링 시스템(700)의 다양한 구성요소들 중에서 통신 링크들을 제공하며 단일 버스로서, 버스들의 조합으로서, 또는 임의의 다른 적절한 방식으로 구현될 수 있다.

칩 어셈블리(704)는 시스템 버스(702)에 결합된다. 칩 어셈블리(704)는 임의의 회로 또는 회로들의 동작 가능하게 호환 가능한 조합을 포함할 수 있다. 일 실시예에서, 칩 어셈블리(704)는 임의의 유형일 수 있는 프로세서(706)를 포함한다. 여기에 사용된 바와 같이, "프로세서"는 이에 제한되지는 않지만, 마이크로프로세서, 마이크로제어기, 그래픽스 프로세서, 디지털 신호 프로세서(DSP), 또는 임의의 다른 유형의 프로세서 또는 프로세싱 회로와 같은 임의의 유형의 계산 회로를 의미한다. “다중-코어” 디바이스들과 같은 다중 프로세서들이 또한 본 발명의 범위 내에 있다.

일 실시예에서, 상기 실시예들에 설명된 메모리 디바이스와 같은, 메모리 디바이스(707)가 칩 어셈블리(704)에 포함된다. 이 기술분야의 숙련자들은 다양한 메모리 디바이스 구성들이 칩 어셈블리(704)에서 사용될 수 있다는 것을 인식할 것이다. 상기 논의된 바와 같이, 선택된 실시예들에서, 메모리 구성은 RRAM을 포함한다. 선택된 실시예들에서, 메모리 셀들은 NAND 메모리 또는 NOR 메모리와 같은, 상이한 논리 구성들로 배열된다.

일 실시예에서, 프로세서 칩들 외에 부가적인 논리 칩들(708)이 칩 어셈블리(704)에 포함된다. 프로세서 외에 논리 칩(708)의 예는 아날로그-디지털 변환기를 포함한다. 맞춤 회로들, 애플리케이션-특정 집적 회로(ASIC) 등과 같은 논리 칩들(708) 상에서의 다른 회로들이 또한 본 발명의 일 실시예에 포함된다.

정보 핸들링 시스템(700)은 또한 외부 메모리(711)를 포함할 수 있으며, 이것은 결과적으로 하나 이상의 하드 드라이브들(712), 및/또는 플래시 드라이브들, 콤팩트 디스크들(CD들), 디지털 비디오 디스크들(DVD들) 등과 같은 착탈 가능한 미디어(713)를 핸들링하는 하나 이상의 드라이브들과 같은, 특정한 애플리케이션에 적합한 하나 이상의 메모리 소자들을 포함할 수 있다.

정보 핸들링 시스템(700)은 또한 모니터와 같은 디스플레이 디바이스(709), 스피커들 등과 같은 부가적인 주변 구성요소들(710), 및 마우스, 터치스크린 인터페이스, 또는 시스템 사용자로 하여금 정보 핸들링 시스템(700)으로 정보를 입력하고 그로부터 정보를 수신하도록 허용하는 임의의 다른 디바이스를 포함할 수 있는 키보드 및/또는 제어기(714)를 포함할 수 있다.

본 발명의 다수의 실시예들이 설명되지만, 상기 리스트들은 철저한 것으로 의도되지는 않는다. 특정 실시예들이 여기에 예시되고 설명되었지만, 동일한 목적을 달성하기 위해 산출되는 임의의 배열은 도시된 특정 실시예들을 위해 대체될 수 있다는 것이 이 기술분야의 숙련자들에 의해 이해될 것이다. 이러한 애플리케이션은 본 발명의 임의의 각색들 또는 변형들을 커버하도록 의도된다. 상기 설명은 예시적이며 제한적이지 않도록 의도된다는 것이 이해될 것이다. 상기 실시예들의 조합들, 및 다른 실시예들이 상기 설명을 연구할 때 이 기술분야의 숙련자들에게 명백할 것이다.

Claims (33)

- 메모리 디바이스로서,

행과 열로 배열된 메모리 셀들의 어레이 - 상기 셀들의 각각은

가변 상태 재료 영역; 및

상기 가변 상태 재료 영역에 결합된 액세스 트랜지스터를 포함함 - ; 및

상기 어레이에서의 상이한 메모리 셀들에 3개의 상이한 전압들을 동시에 제공하기 위해 상기 메모리 셀들의 어레이에 결합된 드라이버

를 포함하며,

상기 상이한 메모리 셀들의 각각은 한번에 상기 3개의 전압들 중 하나의 전압을 수신하고, 상기 3개의 상이한 전압들은 동시에 상기 어레이의 상이한 열들로 제공되는 세트(set) 및 리셋(reset) 및 금지(inhibit) 전압들을 포함하고, 소스 라인이 상기 상이한 메모리 셀들에 결합되고 상기 금지 전압을 제공하기 위한 금지 전압 라인에 공통으로 결합되어 있는, 메모리 디바이스. - 청구항 1에 있어서, 상기 가변 상태 재료 영역은 저항 스위칭 재료를 포함하는, 메모리 디바이스.

- 청구항 2에 있어서, 상기 가변 상태 재료 영역은 단극 가변 상태 재료를 포함하는, 메모리 디바이스.

- 청구항 2에 있어서, 상기 가변 상태 재료 영역은 쌍극 가변 상태 재료를 포함하는, 메모리 디바이스.

- 청구항 1에 있어서, 상기 드라이버는 컬럼 드라이버인, 메모리 디바이스.

- 청구항 1에 있어서, 상기 세트 전압은 4 볼트에서 동작되도록 구성되는, 메모리 디바이스.

- 청구항 1에 있어서, 상기 리셋 전압은 2 볼트에서 동작되도록 구성되는, 메모리 디바이스.

- 청구항 1에 있어서, 상기 액세스 트랜지스터는 N 채널 액세스 트랜지스터를 포함하는, 메모리 디바이스.

- 청구항 1에 있어서, 상기 액세스 트랜지스터는 P 채널 액세스 트랜지스터를 포함하는, 메모리 디바이스.

- 메모리 디바이스로서,

행과 열로 배열된 메모리 셀들의 어레이 - 상기 셀들의 각각은

가변 상태 재료 영역; 및

상기 가변 상태 재료 영역에 결합된 액세스 트랜지스터를 포함함 - ; 및

상기 어레이의 상이한 열들에 세트, 리셋 및 금지 전압들을 동시에 제공하기 위해 상기 메모리 셀들의 어레이에 결합된 드라이버

를 포함하고, 소스 라인이 상기 메모리 셀들에 결합되고 상기 금지 전압을 제공하기 위한 금지 전압 라인에 공통으로 결합되어 있는, 메모리 디바이스. - 청구항 10에 있어서, 상기 가변 상태 재료 영역은 저항 스위칭 재료를 포함하는, 메모리 디바이스.

- 청구항 11에 있어서, 상기 가변 상태 재료 영역은 단극 가변 상태 재료를 포함하는, 메모리 디바이스.

- 청구항 11에 있어서, 상기 가변 상태 재료 영역은 쌍극 가변 상태 재료를 포함하는, 메모리 디바이스.

- 청구항 10에 있어서, 상기 세트 전압은 4 볼트에서 동작되도록 구성되는, 메모리 디바이스.

- 청구항 14에 있어서, 상기 리셋 전압은 2 볼트에서 동작되도록 구성되는, 메모리 디바이스.

- 청구항 15에 있어서, 상기 금지 전압은 3 볼트에서 동작되도록 구성되는, 메모리 디바이스.

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

- 삭제

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/445,577 | 2012-04-12 | ||

| US13/445,577 US9053784B2 (en) | 2012-04-12 | 2012-04-12 | Apparatuses and methods for providing set and reset voltages at the same time |

| PCT/US2013/036209 WO2013155326A1 (en) | 2012-04-12 | 2013-04-11 | Apparatuses and methods for providing set and reset voltages at the same time |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20150002759A KR20150002759A (ko) | 2015-01-07 |

| KR101984681B1 true KR101984681B1 (ko) | 2019-05-31 |

Family

ID=49324939

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020147030963A KR101984681B1 (ko) | 2012-04-12 | 2013-04-11 | 세트 및 리셋 전압들을 동시에 제공하기 위한 장치들 및 방법들 |

Country Status (7)

| Country | Link |

|---|---|

| US (3) | US9053784B2 (ko) |

| EP (1) | EP2837000B1 (ko) |

| JP (1) | JP2015518230A (ko) |

| KR (1) | KR101984681B1 (ko) |

| CN (2) | CN104335283A (ko) |

| TW (1) | TWI585763B (ko) |

| WO (1) | WO2013155326A1 (ko) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9053784B2 (en) | 2012-04-12 | 2015-06-09 | Micron Technology, Inc. | Apparatuses and methods for providing set and reset voltages at the same time |

| KR102151183B1 (ko) * | 2014-06-30 | 2020-09-02 | 삼성전자주식회사 | 저항성 메모리 장치 및 저항성 메모리 장치의 동작방법 |

| CN104794261A (zh) * | 2015-03-27 | 2015-07-22 | 山东华芯半导体有限公司 | 一种具有复位功能的阻变型随机存储器模型及存储方法 |

| GB2545264B (en) * | 2015-12-11 | 2020-01-15 | Advanced Risc Mach Ltd | A storage array |

| TWI626660B (zh) * | 2017-04-21 | 2018-06-11 | 瞻誠科技股份有限公司 | 記憶體裝置及其製作方法 |

| JP6723402B1 (ja) * | 2019-02-28 | 2020-07-15 | ウィンボンド エレクトロニクス コーポレーション | 抵抗変化型ランダムアクセスメモリ |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090135637A1 (en) * | 2007-10-05 | 2009-05-28 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US20120014163A1 (en) * | 2010-07-16 | 2012-01-19 | Shinobu Yamazaki | Semiconductor memory device and method of driving the same |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6032248A (en) * | 1998-04-29 | 2000-02-29 | Atmel Corporation | Microcontroller including a single memory module having a data memory sector and a code memory sector and supporting simultaneous read/write access to both sectors |

| TWI355661B (en) | 2003-12-18 | 2012-01-01 | Panasonic Corp | Method for using a variable-resistance material as |

| US7362604B2 (en) * | 2005-07-11 | 2008-04-22 | Sandisk 3D Llc | Apparatus and method for programming an array of nonvolatile memory cells including switchable resistor memory elements |

| KR100757410B1 (ko) * | 2005-09-16 | 2007-09-11 | 삼성전자주식회사 | 상 변화 메모리 장치 및 그것의 프로그램 방법 |

| JP4203506B2 (ja) | 2006-01-13 | 2009-01-07 | シャープ株式会社 | 不揮発性半導体記憶装置及びその書き換え方法 |

| KR100816748B1 (ko) * | 2006-03-16 | 2008-03-27 | 삼성전자주식회사 | 프로그램 서스펜드/리줌 모드를 지원하는 상 변화 메모리장치 및 그것의 프로그램 방법 |

| JP4958244B2 (ja) * | 2006-09-15 | 2012-06-20 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP4088323B1 (ja) * | 2006-12-06 | 2008-05-21 | シャープ株式会社 | 不揮発性半導体記憶装置 |

| US8154003B2 (en) | 2007-08-09 | 2012-04-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Resistive non-volatile memory device |

| JP5214208B2 (ja) * | 2007-10-01 | 2013-06-19 | スパンション エルエルシー | 半導体装置及びその制御方法 |

| KR101202429B1 (ko) * | 2007-10-11 | 2012-11-16 | 삼성전자주식회사 | 저항체를 이용한 비휘발성 메모리 장치 |

| JP5072564B2 (ja) | 2007-12-10 | 2012-11-14 | 株式会社東芝 | 半導体記憶装置及びメモリセル電圧印加方法 |

| KR101407362B1 (ko) * | 2008-06-23 | 2014-06-16 | 삼성전자주식회사 | 상 변화 메모리 장치 |

| KR20100045077A (ko) | 2008-10-23 | 2010-05-03 | 삼성전자주식회사 | 면적을 감소시킨 가변 저항 메모리 장치 |

| JP5549105B2 (ja) | 2009-04-15 | 2014-07-16 | ソニー株式会社 | 抵抗変化型メモリデバイスおよびその動作方法 |

| JP4796640B2 (ja) | 2009-05-19 | 2011-10-19 | シャープ株式会社 | 半導体記憶装置、及び、電子機器 |

| JP2011004830A (ja) | 2009-06-23 | 2011-01-13 | Shimadzu Corp | X線撮影装置 |

| JP5214566B2 (ja) * | 2009-09-02 | 2013-06-19 | 株式会社東芝 | 抵抗変化メモリ装置 |

| US8625328B2 (en) | 2009-10-15 | 2014-01-07 | Panasonic Corporation | Variable resistance nonvolatile storage device |

| KR101068333B1 (ko) | 2009-12-23 | 2011-09-28 | 주식회사 하이닉스반도체 | Rfid 장치 |

| US8446753B2 (en) * | 2010-03-25 | 2013-05-21 | Qualcomm Incorporated | Reference cell write operations at a memory |

| JP5054803B2 (ja) | 2010-05-26 | 2012-10-24 | シャープ株式会社 | 半導体記憶装置 |

| JP5521850B2 (ja) * | 2010-07-21 | 2014-06-18 | ソニー株式会社 | 抵抗変化型メモリデバイスおよびその駆動方法 |

| JP5598338B2 (ja) | 2011-01-13 | 2014-10-01 | ソニー株式会社 | 記憶装置およびその動作方法 |

| JP5250722B1 (ja) * | 2011-09-09 | 2013-07-31 | パナソニック株式会社 | クロスポイント型抵抗変化不揮発性記憶装置及びその書き込み方法 |

| ITTO20120192A1 (it) * | 2012-03-05 | 2013-09-06 | St Microelectronics Srl | Architettura e metodo di decodifica per dispositivi di memoria non volatile a cambiamento di fase |

| US9053784B2 (en) | 2012-04-12 | 2015-06-09 | Micron Technology, Inc. | Apparatuses and methods for providing set and reset voltages at the same time |

| JP2013254545A (ja) * | 2012-06-08 | 2013-12-19 | Sharp Corp | 不揮発性半導体記憶装置、及び、可変抵抗素子の抵抗制御方法 |

| US20130336037A1 (en) * | 2012-06-15 | 2013-12-19 | Sandisk 3D Llc | 3d memory having vertical switches with surround gates and method thereof |

| KR20140028480A (ko) * | 2012-08-29 | 2014-03-10 | 에스케이하이닉스 주식회사 | 가변 저항 메모리 장치 및 그것의 동작 방법 |

| US9190146B2 (en) * | 2013-02-28 | 2015-11-17 | Kabushiki Kaisha Toshiba | Variable resistance memory system with redundancy lines and shielded bit lines |

| KR102179275B1 (ko) * | 2014-02-21 | 2020-11-16 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 리셋 방법 |

| US9697896B2 (en) * | 2014-02-26 | 2017-07-04 | Stmicroelectronics S.R.L. | High throughput programming system and method for a phase change non-volatile memory device |

-

2012

- 2012-04-12 US US13/445,577 patent/US9053784B2/en active Active

-

2013

- 2013-04-11 WO PCT/US2013/036209 patent/WO2013155326A1/en active Application Filing

- 2013-04-11 CN CN201380026853.6A patent/CN104335283A/zh active Pending

- 2013-04-11 KR KR1020147030963A patent/KR101984681B1/ko active IP Right Grant

- 2013-04-11 EP EP13775893.4A patent/EP2837000B1/en active Active

- 2013-04-11 CN CN202010488121.0A patent/CN111640464B/zh active Active

- 2013-04-11 JP JP2015505916A patent/JP2015518230A/ja active Pending

- 2013-04-12 TW TW102113165A patent/TWI585763B/zh active

-

2015

- 2015-06-08 US US14/733,603 patent/US9570172B2/en active Active

-

2017

- 2017-02-13 US US15/431,364 patent/US9711218B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090135637A1 (en) * | 2007-10-05 | 2009-05-28 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| US20120014163A1 (en) * | 2010-07-16 | 2012-01-19 | Shinobu Yamazaki | Semiconductor memory device and method of driving the same |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI585763B (zh) | 2017-06-01 |

| EP2837000B1 (en) | 2020-03-25 |

| CN104335283A (zh) | 2015-02-04 |

| US20150269999A1 (en) | 2015-09-24 |

| US9053784B2 (en) | 2015-06-09 |

| US9570172B2 (en) | 2017-02-14 |

| CN111640464B (zh) | 2023-09-29 |

| JP2015518230A (ja) | 2015-06-25 |

| US20130272053A1 (en) | 2013-10-17 |

| WO2013155326A1 (en) | 2013-10-17 |

| US20170154676A1 (en) | 2017-06-01 |

| EP2837000A4 (en) | 2015-07-08 |

| US9711218B2 (en) | 2017-07-18 |

| CN111640464A (zh) | 2020-09-08 |

| KR20150002759A (ko) | 2015-01-07 |

| EP2837000A1 (en) | 2015-02-18 |

| TW201403604A (zh) | 2014-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9711218B2 (en) | Apparatuses and methods for providing set and reset voltages at the same time | |

| US10910052B2 (en) | Material implication operations in memory | |

| US10210928B2 (en) | Apparatuses including current compliance circuits and methods | |

| US9508427B2 (en) | Apparatuses and methods including supply current in memory | |

| US9899079B2 (en) | Memory devices | |

| US7548446B2 (en) | Phase change memory device and associated wordline driving circuit | |

| US10255974B2 (en) | Electronic devices having semiconductor magnetic memory units | |

| Kumar et al. | A novel design of a memristor-based look-up table (LUT) for FPGA | |

| US9105320B2 (en) | Memory devices and methods of operating the same | |

| US20180075905A1 (en) | Electronic device | |

| US20170117045A1 (en) | Electronic device | |

| US11475951B2 (en) | Material implication operations in memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E90F | Notification of reason for final refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |