KR101160105B1 - 반도체 기억 장치 및 그 제조 방법 - Google Patents

반도체 기억 장치 및 그 제조 방법 Download PDFInfo

- Publication number

- KR101160105B1 KR101160105B1 KR1020100089932A KR20100089932A KR101160105B1 KR 101160105 B1 KR101160105 B1 KR 101160105B1 KR 1020100089932 A KR1020100089932 A KR 1020100089932A KR 20100089932 A KR20100089932 A KR 20100089932A KR 101160105 B1 KR101160105 B1 KR 101160105B1

- Authority

- KR

- South Korea

- Prior art keywords

- diffusion layer

- type

- pmos access

- access transistor

- transistor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 58

- 238000004519 manufacturing process Methods 0.000 title claims description 22

- 238000009792 diffusion process Methods 0.000 claims abstract description 246

- 239000000758 substrate Substances 0.000 claims abstract description 57

- 229910021332 silicide Inorganic materials 0.000 claims abstract description 20

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims abstract description 20

- 230000003068 static effect Effects 0.000 claims abstract description 4

- 238000000034 method Methods 0.000 claims description 17

- 238000002955 isolation Methods 0.000 claims description 13

- 230000006870 function Effects 0.000 claims description 11

- 238000003860 storage Methods 0.000 claims description 11

- 238000005530 etching Methods 0.000 claims description 6

- 238000001459 lithography Methods 0.000 claims description 6

- 230000002265 prevention Effects 0.000 abstract description 2

- 239000010410 layer Substances 0.000 description 265

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 36

- 229910052710 silicon Inorganic materials 0.000 description 36

- 239000010703 silicon Substances 0.000 description 36

- 238000002347 injection Methods 0.000 description 13

- 239000007924 injection Substances 0.000 description 13

- 239000012535 impurity Substances 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 7

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 7

- 239000007943 implant Substances 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/0203—Particular design considerations for integrated circuits

- H01L27/0207—Geometrical layout of the components, e.g. computer aided design; custom LSI, semi-custom LSI, standard cell technique

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823814—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823885—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of vertical transistor structures, i.e. with channel vertical to the substrate surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823892—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the wells or tubs, e.g. twin tubs, high energy well implants, buried implanted layers for lateral isolation [BILLI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/107—Substrate region of field-effect devices

- H01L29/1075—Substrate region of field-effect devices of field-effect transistors

- H01L29/1079—Substrate region of field-effect devices of field-effect transistors with insulated gate

- H01L29/1083—Substrate region of field-effect devices of field-effect transistors with insulated gate with an inactive supplementary region, e.g. for preventing punch-through, improving capacity effect or leakage current

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B10/00—Static random access memory [SRAM] devices

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Engineering & Computer Science (AREA)

- Ceramic Engineering (AREA)

- Semiconductor Memories (AREA)

Abstract

4개의 MOS 트랜지스터를 이용하여 구성된 스태틱 메모리 셀에 있어서, 메모리 셀을 구성하는 트랜지스터는 기판 상에 형성되고, 드레인, 게이트, 소스가 수직방향으로 배치되고, 게이트가 주상 반도체층을 둘러싸는 구조를 갖는다. 이 메모리 셀에 있어서, 제 1 기억 노드(제 2 기억 노드)로서 기능을 하는 각각의 제 1 확산층(제 2 확산층)이, 그들의 표면에 형성된 제 1 실리사이드층(제 2 실리사이드층)을 개재하여 접속되어 있다. 이에 의해, 작은 면적의 SRAM 셀을 실현하고 있다. 또한, 기판 상에 형성된 제 1 웰과 당해 제 1 웰과 동일 도전형을 갖는 제 1 확산층(제 2 확산층) 사이에, 제 1 웰과 반대 도전형을 갖는 제 1 누설방지 확산층(제 2 누설방지 확산층)이 형성되어 있는 것에 의해, 기판에 대한 누설이 억제된다.

Description

본 발명은 반도체 기억 장치에 관한 것으로서, 특히 SRAM(Static Random Access Memory)으로 구성되는 반도체 기억 장치에 관한 것이다.

반도체 장치의 고집적화, 고성능화를 진전시키기 위한 방책으로서, SGT(Surrounding Gate Transistor)에 관한 기술(예를 들면, 일본 공개특허 h2-188966호 공보 및 일본 공개특허 h7-99311호 공보에 개시)이 알려져 있다. SGT는 반도체 기판의 표면에 주상(columnar) 반도체층을 형성하고, 그 측벽에 당해 주상 반도체층을 둘러싸는 게이트를 형성한 수직형 게이트 트랜지스터이다. SGT에서는 드레인, 게이트, 소스가 수직방향으로 배치되기 때문에, 종래의 평면형 트랜지스터에 비해 점유 면적을 대폭 축소할 수 있다.

근래, LSI(대규모 집적 회로)에 탑재되는 SRAM에 대한 대용량화의 요구는 점점 높아지고 있고, 상기 SGT를 채용한 작은 셀 면적을 갖는 SRAM의 실현화가 기대되고 있다.

도 19a는, 일본 공개특허 h7-99311호 공보의 실시예에 개시된, 6개의 SGT에 의해 구성되는 CMOS 6T-SRAM 메모리 셀의 평면도이고, 도 19b는 도 19a의 A-A' 단면도이다. 이들의 도면에 있어서, 비트 라인(801a, 801b)은 n+확산층으로 형성되고, 접지 전위 배선(GND)은 n+확산층(802)으로 형성되고, 전원 전위 배선(Vcc)은 p+확산층(803)으로 형성되어 있다.

이들의 확산층 상에는 메모리 셀에 액세스하기 위한 액세스 트랜지스터(810a, 810b), 메모리 셀을 구동하기 위한 드라이버 트랜지스터(811a, 811b), 메모리 셀에 전하를 공급하는 로드 트랜지스터(812a, 812b)를 각각 구성하는 주상 실리콘층이 형성되어 있다. 그리고, 이들의 주상 실리콘층을 둘러싸도록 게이트(804a, 804b, 804c, 804d)가 형성되어 있다. 또한, 기억 노드는 배선층(807a, 807b)에 의해 구성되어 있다. 상기와 같은 메모리 셀(SRAM 셀)에 있어서, 각 트랜지스터는 주상 실리콘층 상에 수직방향으로 소스, 게이트, 드레인이 형성되어 있기 때문에, 작은 SRAM 셀을 설계할 수 있다.

상기 SRAM 셀에 있어서, 전원 전위 배선(803) 및 접지 전위 배선(802)이 최소 치수 정도로 형성되는 경우에는, 작은 셀 면적을 실현하는 것이 가능하다. 하지만, 전원 전위 배선(803) 및 접지 전위 배선(802)은 각각 p+확산층 및 n+확산층에 의해 형성되어 있기 때문에, 이들이 최소 치수 정도로 형성되면, 매우 높은 저항으로 되어, SRAM을 고속으로 동작시키기 어려워진다. 반면, SRAM을 고속으로 동작시키기 위하여 전원 전위 배선(803) 및 접지 전위 배선(802)의 치수를 크게 하면, SRAM 셀 면적이 증가해버린다.

또한, 종래의 평면형 트랜지스터를 이용한 SRAM에 있어서는, 전원 전위 배선 및 접지 전위 배선은 저항이 낮은 Cu 배선으로 형성되어 있다. 이 때문에, SGT를 이용한 SRAM에 있어서 평면형 트랜지스터를 이용한 SRAM과 동등한 동작 속도를 달성하기 위해서는, 전원 전위 배선 및 접지 전위 배선을 Cu 배선에 의해 형성하는 것이 필수적이다.

CMOS 6T-SRAM보다 더욱 SRAM 셀 면적을 작게 할 수 있는 SRAM으로서, Loadless 4T-SRAM이 제안되어 있다(예를 들면, 일본 특허공개 2000-12705호 공보에 개시). 도 1에 Loadless 4T-SRAM의 메모리 셀의 등가회로를 나타낸다. 이 SRAM 셀은 메모리에 액세스하기 위한 2개의 PMOS 액세스 트랜지스터(Qp11, Qp21)와, 메모리를 구동하기 위한 2개의 NMOS 드라이버 트랜지스터(Qn11, Qn21)를 포함하는 합계 4개의 트랜지스터에 의해 구성되어 있다.

이하, 도 1의 메모리 셀의 동작에 대한 일례로서, 기억 노드(Qa1)에 "L" 데이터가 기억되어 있고, 기억 노드(Qb1)에 "H" 데이터가 기억되어 있는 경우의 데이터 유지동작에 대해 설명한다. 데이터 유지 중에는, 워드 라인(WL1), 비트 라인(BL1, BLB1)은 모두 "H" 전위로 구동되어 있다. 액세스 트랜지스터(Qp11, Qp21)의 임계값은 드라이버 트랜지스터(Qn11, Qn21)의 임계값보다 낮게 설정되어 있다. 또한, 액세스 트랜지스터(Qp11, Qp21)의 오프-누설 전류(off-leak current)는 드라이버 트랜지스터(Qn11, Qn21)의 오프-누설 전류에 비해, 예를 들면 평균적으로 10배~1000배 정도 커지도록 설정되어 있다. 이 때문에, 액세스 트랜지스터(Qp21)를 통해 비트 라인(BLB1)으로부터 기억 노드(Qb1)에 오프-누설 전류가 흐르는 것에 의해, 기억 노드(Qb1)의 "H" 레벨은 유지된다. 한편, 기억 노드(Qa1)의 "L" 레벨은 드라이버 트랜지스터(Qn11)에 의해 안정적으로 유지된다.

SGT를 이용한 경우에도, CMOS 6T-SRAM에 비해 상기 Loadless 4T-SRAM이 더욱 작은 SRAM 셀 면적을 실현할 수 있다.

상기 사정을 비추어, 본 발명은 SGT를 이용한 Loadless 4T-SRAM에 있어서, 면적을 작게 할 수 있고, 나아가 충분한 동작 마진을 갖는 SRAM 셀을 실현하는 것을 목적으로 한다.

상기 목적을 달성하기 위하여, 본 발명에 따른 반도체 기억 장치는, 4개의 MOS 트랜지스터가 기판 상에 배열된 스태틱(Static) 메모리 셀을 구비하는 반도체 기억 장치이고, 상기 4개의 MOS 트랜지스터 각각은, 소스 확산층, 드레인 확산층 및 주상 반도체층이 기판 상에 수직방향으로 계층적으로 배치되고, 상기 주상 반도체층은 상기 소스 확산층과 상기 드레인 확산층 사이에 배치되고, 상기 주상 반도체층의 측벽에 게이트 전극이 형성되어 있고, 메모리 셀 데이터를 유지하기 위하여 전하를 공급함과 함께 메모리에 액세스하기 위한 제 1 및 제 2 PMOS 액세스 트랜지스터와, 메모리 셀의 데이터를 리드아웃 하기 위하여 기억 노드를 구동하는 제 1 및 제 2 NMOS 드라이버 트랜지스터로서 기능을 하고, 상기 제 1 PMOS 액세스 트랜지스터 및 상기 제 1 NMOS 드라이버 트랜지스터는 서로 인접하여 배열되고, 상기 제 2 PMOS 액세스 트랜지스터 및 상기 제 2 NMOS 드라이버 트랜지스터는 서로 인접하여 배열되고, 상기 기판에는, 당해 기판에 전위를 부여하기 위한 복수의 메모리 셀에 공통인 제 1 웰이 형성되고, 상기 제 1 PMOS 액세스 트랜지스터의 저부에 형성되는 제 1 P형 확산층 및 상기 제 1 NMOS 드라이버 트랜지스터의 저부에 형성되는 제 1 N형 확산층은, 각각의 표면에 형성된 제 1 실리사이드층을 개재하여 서로 접속되고, 상기 서로 접속된 제 1 P형 확산층 및 제 1 N형 확산층은, 메모리 셀에 기억되는 데이터를 유지하기 위한 제 1 기억 노드로서 기능을 하고, 상기 제 1 N형 확산층 또는 제 1 P형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 1 N형 확산층 또는 제 1 P형 확산층과 상기 제 1 웰 사이에 상기 제 1 웰과 반대 도전형을 갖는 제 1 누설방지 확산층이 형성되고, 상기 제 1 누설방지 확산층은, 상기 제 1 P형 확산층 또는 제 1 N형 확산층과 직접 접속되고, 상기 제 2 PMOS 액세스 트랜지스터의 저부에 형성되는 제 2 P형 확산층 및 상기 제 2 NMOS 드라이버 트랜지스터의 저부에 형성되는 제 2 N형 확산층은, 각각의 표면에 형성된 제 2 실리사이드층을 개재하여 서로 접속되고, 상기 서로 접속된 제 2 P형 확산층 및 제 2 N형 확산층은, 메모리 셀에 기억되는 데이터를 유지하기 위한 제 2 기억 노드로서 기능을 하고, 상기 제 2 N형 확산층 또는 제 2 P형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 2 N형 확산층 또는 제 2 P형 확산층과 상기 제 1 웰 사이에 상기 제 1 웰과 반대 도전형을 갖는 제 2 누설방지 확산층이 형성되고, 상기 제 2 누설방지 확산층은, 상기 제 2 P형 확산층 또는 제 2 N형 확산층과 직접 접속되어 있는 것을 특징으로 한다.

상기 제 1 누설방지 확산층은, 상기 제 1 N형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 1 N형 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 제 1 P형 확산층과 직접 접속되고, 상기 제 2 누설방지 확산층은, 상기 제 2 N형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 2 N형 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 제 2 P형 확산층과 직접 접속되어 있어도 좋다. 또는, 상기 제 1 누설방지 확산층은, 상기 제 1 P형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 1 P형 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 제 1 N형 확산층과 직접 접속되고, 상기 제 2 누설방지 확산층은, 상기 제 2 P형 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 제 2 P형 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 제 2 N형 확산층과 직접 접속되어 있어도 좋다.

또한, 본 발명의 다른 바람직한 실시형태에서는, 상기 반도체 기억 장치에 있어서, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트 중의 적어도 하나를, 인접하는 메모리 셀의 PMOS 액세스 트랜지스터 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트와 공통화한다.

또한, 본 발명의 다른 바람직한 실시형태에서는, 상기 제 1 기억 노드로서 기능을 하는 상기 제 1 확산층 상에 형성되는 상기 제 1 NMOS 드라이버 트랜지스터 게이트로부터 연장되는 게이트 배선이, 상기 제 2 기억 노드로서 기능을 하는 상기 제 2 확산층과 공통의 콘택트에 의해 접속되고, 상기 제 2 기억 노드로서 기능을 하는 상기 제 2 확산층 상에 형성되는 제 2 NMOS 드라이버 트랜지스터 게이트로부터 연장되는 게이트 배선이, 상기 제 1 기억 노드로서 기능을 하는 상기 제 1 확산층과 공통의 콘택트에 의해 접속된다.

또한, 본 발명의 다른 바람직한 실시형태에서는, 상기 제 1 및 제 2 NMOS 드라이버 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이는, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이 이상의 값을 갖고, 또는 상기 제 1 및 제 2 NMOS 드라이버 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이는, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이 이하의 값을 갖는 것을 특징으로 한다.

또한, 상기 4개의 MOS 트랜지스터는, 상기 기판 상에 2행 2열에 배열되고, 상기 제 1 PMOS 액세스 트랜지스터는 1행 1열째에 배열되고, 상기 제 1 NMOS 드라이버 트랜지스터는 2행 1열째에 배열되고, 상기 제 2 PMOS 액세스 트랜지스터는 1행 2열째에 배열되고, 상기 제 2 NMOS 드라이버 트랜지스터는 2행 2열째에 배열되도록 해도 좋다.

또한, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트를 공유하도록 해도 좋다.

또한, 상기 4개의 MOS 트랜지스터에 있어서, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터는 인접하여 배열되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 PMOS 액세스 트랜지스터에 인접하여 상기 제 1 확산층 상에 제 1 콘택트가 배치되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 PMOS 액세스 트랜지스터에 인접하여 상기 제 2 확산층 상에 제 2 콘택트가 배치되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 NMOS 드라이버 트랜지스터는 상기 제 1 PMOS 액세스 트랜지스터와 인접하여 배열되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 NMOS 드라이버 트랜지스터는 상기 제 2 PMOS 액세스 트랜지스터와 인접하여 배열되도록 해도 좋다.

또한, 상기 4개의 MOS 트랜지스터에 있어서, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터는 인접하여 배열되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 NMOS 드라이버 트랜지스터는 상기 제 1 PMOS 액세스 트랜지스터와 인접하여 배열되고, 상기 제 1 NMOS 드라이버 트랜지스터와 상기 제 1 PMOS 액세스 트랜지스터 사이의 확산층 상에는 제 3 콘택트가 형성되고, 상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 NMOS 드라이버 트랜지스터는 상기 제 2 PMOS 액세스 트랜지스터와 인접하여 배열되고, 상기 제 2 NMOS 드라이버 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터 사이의 확산층 상에는 제 4 콘택트가 형성되도록 해도 좋다.

또한, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 상기 주상 반도체층의 상부에 형성되는 콘택트 중의 적어도 하나를, 인접하는 메모리 셀의 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 상부에 형성되는 콘택트와 공유화하도록 해도 좋다.

본 발명에 따른 반도체 기억 장치의 제조 방법은, 상기한 반도체 기억 장치를 제조하는 방법이고, 상기 주상 반도체층 상에 형성되는 콘택트와, 상기 기판 상에 형성되는 콘택트 또는 게이트 배선 상에 형성되는 콘택트를 상이한 리소그래피 공정 또는 에칭 공정에 의해 형성하는 것을 특징으로 한다.

본 발명에 의하면, SGT를 이용한 Loadless 4T-SRAM에 있어서, 면적을 작게 할 수 있고, 나아가 충분한 동작 마진을 갖는 SRAM 셀을 실현할 수 있다.

도 1은 본 발명의 실시형태 1에 따른 SRAM을 나타내는 등가회로.

도 2는 본 발명의 실시형태 1에 따른 SRAM의 평면도.

도 3a는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3b는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3c는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3d는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 4a는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4b는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4c는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4d는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 5a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (1)을 나타내는 평면도.

도 5b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (1)을 나타내는 단면도.

도 6a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (2)를 나타내는 평면도.

도 6b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (2)를 나타내는 단면도.

도 7a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (3)을 나타내는 평면도.

도 7b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (3)을 나타내는 단면도.

도 8a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (4)를 나타내는 평면도.

도 8b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (4)를 나타내는 단면도.

도 9a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (5)를 나타내는 평면도.

도 9b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (5)를 나타내는 단면도.

도 10a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (6)을 나타내는 평면도.

도 10b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (6)을 나타내는 단면도.

도 11a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (7)을 나타내는 평면도.

도 11b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (7)을 나타내는 단면도.

도 12a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (8)을 나타내는 평면도.

도 12b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (8)을 나타내는 단면도.

도 13a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (9)를 나타내는 평면도.

도 13b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (9)를 나타내는 단면도.

도 14는 본 발명의 실시형태 2에 따른 SRAM의 평면도.

도 15는 본 발명의 실시형태 3에 따른 SRAM의 평면도.

도 16은 본 발명의 실시형태 4에 따른 SRAM의 평면도.

도 17은 본 발명의 실시형태 5에 따른 SRAM의 평면도.

도 18은 본 발명의 실시형태 6에 따른 SRAM의 평면도.

도 19a는 종래의 SGT를 이용한 SRAM의 평면도.

도 19b는 종래의 SGT를 이용한 SRAM의 단면도.

도 2는 본 발명의 실시형태 1에 따른 SRAM의 평면도.

도 3a는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3b는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3c는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 3d는 본 발명의 실시형태 1에 따른 SRAM의 단면도.

도 4a는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4b는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4c는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 4d는 본 발명의 실시형태 1의 다른 예에 따른 SRAM의 단면도.

도 5a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (1)을 나타내는 평면도.

도 5b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (1)을 나타내는 단면도.

도 6a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (2)를 나타내는 평면도.

도 6b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (2)를 나타내는 단면도.

도 7a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (3)을 나타내는 평면도.

도 7b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (3)을 나타내는 단면도.

도 8a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (4)를 나타내는 평면도.

도 8b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (4)를 나타내는 단면도.

도 9a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (5)를 나타내는 평면도.

도 9b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (5)를 나타내는 단면도.

도 10a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (6)을 나타내는 평면도.

도 10b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (6)을 나타내는 단면도.

도 11a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (7)을 나타내는 평면도.

도 11b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (7)을 나타내는 단면도.

도 12a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (8)을 나타내는 평면도.

도 12b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (8)을 나타내는 단면도.

도 13a는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (9)를 나타내는 평면도.

도 13b는 본 발명의 실시형태 1에 따른 SRAM의 제조 공정 (9)를 나타내는 단면도.

도 14는 본 발명의 실시형태 2에 따른 SRAM의 평면도.

도 15는 본 발명의 실시형태 3에 따른 SRAM의 평면도.

도 16은 본 발명의 실시형태 4에 따른 SRAM의 평면도.

도 17은 본 발명의 실시형태 5에 따른 SRAM의 평면도.

도 18은 본 발명의 실시형태 6에 따른 SRAM의 평면도.

도 19a는 종래의 SGT를 이용한 SRAM의 평면도.

도 19b는 종래의 SGT를 이용한 SRAM의 단면도.

이하, 본 발명의 실시형태에 대해, 도면을 참조하여 상세하게 설명한다. 또한, 이하의 각 실시형태에 있어서, 본 발명의 반도체 기억 장치는 Loadless 4T-SRAM으로 구성되어 있는 것을 예로 한다.

(실시형태 1) 도 1은 실시형태 1에 따른 Loadless 4T-SRAM을 구성하는 메모리 셀(SRAM 셀)의 등가회로를 나타내는 도면이다. 도 1에 있어서, BL1 및 BLB1은 비트 라인, WL1은 워드 라인, Vss1은 접지 전위, Qp11 및 Qp21은 액세스 트랜지스터, Qn11 및 Qn21은 드라이버 트랜지스터, Qa1 및 Qb1은 데이터를 기억하기 위한 기억 노드를 나타내고 있다. 액세스 트랜지스터(Qp11, Qp21)는 메모리 셀에 액세스하기 위하여, 및 기억 노드를 "H"로 차지(charge)하는 기능을 갖는다. 드라이버 트랜지스터(Qn11, Qn21)는 메모리 셀의 데이터를 리드아웃 및 기록하기 위하여 기억 노드를 구동한다.

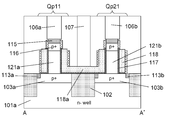

도 2는 본 발명의 실시형태 1에 따른 SRAM의 평면도이다. SRAM 셀 어레이 내에 있어서 도 2에 나타낸 유닛 셀(UC)이 반복적으로 배치되어 있다. 도 3a~도 3d에 도 2의 커트라인 A-A', B-B', C-C' 및 D-D'에 따른 단면구조를 각각 나타낸다.

우선, 도 2, 도 3a~도 3d를 참조하여 본 실시형태의 레이아웃에 대해 설명한다. 기판의 SRAM 셀 어레이 내에는 제 1 웰(101a)인 n-well이 형성되고, 소자분리(102)에 의해 기판 상의 확산층은 분리되어 있다. 기판 상의 확산층에 의해 형성되는 제 1 기억 노드(Qa1)는, 제 1 p+확산층(103a)과 제 1 n+확산층(104a)에 의해 형성되고, 기판 표면에 형성되는 제 1 실리사이드층(113a)에 의해 접속되어 있다. 마찬가지로, 기판 상의 확산층에 의해 형성되는 제 2 기억 노드(Qb1)는, 제 2 p+확산층(103b)과 제 2 n+확산층(104b)에 의해 형성되고, 기판 표면에 형성되는 제 2 실리사이드층(113b)에 의해 접속되어 있다. 제 1 웰(101a)인 n-well과 동일 도전형을 갖는 제 1 n+확산층(104a)으로부터 기판에 대한 누설을 억제하기 위하여, 제 1 웰(101a)과 제 1 n+확산층(104a) 사이에 p+확산층인 제 1 누설방지 확산층(101b), 또는 제 2 누설방지 확산층(101c)이 형성되어 있다. 제 1 누설방지 확산층(101b), 제 2 누설방지 확산층(101c)은 소자분리(102)에 의해, 각각의 기판 상의 확산층별로 분리되어 있다.

Qp11 및 Qp21은 메모리 셀에 액세스하기 위한 PMOS 액세스 트랜지스터이고, Qn11 및 Qn21은 메모리 셀을 구동하는 NMOS 드라이버 트랜지스터이다.

본 실시형태에서는, 1개의 유닛 셀(UC)은, 기판 상에 2행 2열로 배열된 트랜지스터를 구비하고 있다. 1열째에는, 제 1 기억 노드(Qa1) 상에, 도면에 있어서의 상측으로부터 액세스 트랜지스터(Qp11) 및 드라이버 트랜지스터(Qn11)가 각각 배열되어 있다. 또한 2열째에는, 제 2 기억 노드(Qb) 상에, 도면에 있어서의 상측으로부터 액세스 트랜지스터(Qp21) 및 드라이버 트랜지스터(Qn21)가 각각 배열되어 있다. 본 실시형태의 SRAM 셀 어레이는, 이러한 4개의 트랜지스터를 구비한 유닛 셀(UC)을 도면의 상하방향으로 연속적으로 배열하는 것에 의해 구성된다.

제 1 기억 노드(Qa1) 상에 형성되는 콘택트(110a)는 노드 접속 배선(Na1)에 의해, 드라이버 트랜지스터(Qn21)의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트(111b)와 접속되어 있다. 또한, 제 2 기억 노드(Qb1) 상에 형성되는 콘택트(110b)는 노드 접속 배선(Nb1)에 의해, 드라이버 트랜지스터(Qn11)의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트(111a)와 접속되어 있다. 액세스 트랜지스터(Qp11)의 상부에 형성되는 콘택트(106a)는 비트 라인(BL1)에 접속되고, 액세스 트랜지스터(Qp21)의 상부에 형성되는 콘택트(106b)는 비트 라인(BLB1)에 접속되어 있다. 액세스 트랜지스터(Qp11) 및 액세스 트랜지스터(Qp21)의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 공통의 콘택트(107)는 워드 라인(WL1)에 접속되어 있다. 또, 액세스 트랜지스터(Qp11, Qp21)의 게이트 전극으로부터 연장되는 게이트 배선을 횡방향으로 인접하는 셀과 공통화하고, 인접하는 셀과의 사이에 게이트 배선 상의 콘택트를 형성해도 좋다.

드라이버 트랜지스터(Qn11, Qn21)의 상부에 형성되는 콘택트(108a, 108b)는 접지 전위인 배선층(Vss1)에 접속되어 있다. 워드 라인의 배선, 비트 라인의 배선 및 접지 전위 배선은, 다른 메모리 셀의 배선과 공용하기 위하여, 바람직하게는, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층으로 접속된다.

또, 상기 계층적인 배선 구성의 일례로서, 각 배선이 접촉하지 말아야할 콘택트와 접촉하지 않도록, 노드 접속 배선(Na1), 노드 접속 배선(Nb1) 및 접지 전위 배선(Vss1)은 비트 라인(BL1, BLB1)보다 하위층으로 배선하고, 워드 라인(WL1)은 비트 라인(BL1, BLB1)보다 상위층으로 배선하는 구성을 실현할 수 있다.

도 2에 n+주입 영역(125) 및 p+주입 영역(124)을 나타낸다. 본 실시형태의 SRAM 셀 어레이 영역에 있어서는 n+주입 영역(125) 및 p+주입 영역(124)을 형성하는 패턴은 단순한 라인 & 스페이스에 의해 형성된다. 이 때문에 치수 편차나 위치 맞춤의 편차 영향이 작아, n+주입 영역(125)과 p+주입 영역(124)의 경계 부근의 치수 마진을 최소로 억제할 수 있고, 도면상에 있어서, SRAM 셀의 종방향의 길이(각 SRAM 셀의 접속 방향의 길이)의 축소에 유효하다.

또한, 본 실시형태에 있어서는, 도 2의 레이아웃에 나타내는 기억 노드(Qa1, Qb1)나 게이트 배선의 형상이 직사각형 형상만으로 구성되어 있기 때문에, OPC(Optical Proximity Correction)에 의한 패턴 형상의 보정이 용이하고, 작은 SRAM 셀 면적의 실현에 적합하다.

본 발명에 있어서, SRAM 셀을 구성하는 각 트랜지스터 소스 및 드레인을, 하기와 같이 정의한다. 드라이버 트랜지스터(Qn11, Qn21)에 대해서는, 접지 전압에 접속되는 주상 반도체층의 상부에 형성되는 확산층을 소스 확산층, 주상 반도체층의 하부에 형성되는 확산층을 드레인 확산층으로 정의한다. 액세스 트랜지스터(Qp11, Qp21)에 대해서는, 동작 상태에 따라서는 주상 반도체층의 상부에 형성되는 확산층 및 하부에 형성되는 확산층이 모두 소스 또는 드레인이 되지만, 편의적으로 주상 반도체층의 상부에 형성되는 확산층을 소스 확산층, 주상 반도체층의 하부에 형성되는 확산층을 드레인 확산층으로 정의한다.

이어서, 도 3a~도 3d에 나타내는 단면구조를 참조하여 본 발명에 따른 SRAM의 구조에 대해 설명한다. 도 3a에 나타내는 바와 같이, 기판에 SRAM 셀 어레이에 대해 공통되는 제 1 웰(101a)인 n-well이 형성되고, 소자분리(102)에 의해 기판 상의 확산층이 분리되어 있다. 기판 상의 확산층에 의해 형성되는 제 1 기억 노드(Qa1)에는 불순물주입 등에 의해 제 1 p+드레인 확산층(103a)이 형성되고, 기판 상의 확산층에 의해 형성되는 제 2 기억 노드(Qb1)에는 불순물주입 등에 의해 제 2 p+드레인 확산층(103b)이 형성되어 있다. 또한, 제 1, 제 2 p+드레인 확산층(103a, 103b) 상에는 제 1, 제 2 실리사이드층(113a, 113b)이 각각 형성되어 있다. 제 1 p+드레인 확산층(103a) 상에 액세스 트랜지스터(Qp11)를 구성하는 주상 실리콘층(121a)이 형성되고, 제 2 p+드레인 확산층(103b) 상에 액세스 트랜지스터(Qp21)를 구성하는 주상 실리콘층(121b)이 형성되어 있다.

각각의 주상 실리콘층의 주위에는 게이트 절연막(117) 및 게이트 전극(118)이 형성되어 있다. 주상 실리콘층의 상부에는 p+소스 확산층(116)이 불순물주입 등에 의해 형성되고, 소스 확산층의 표면에는 실리사이드층(115)이 형성되어 있다. 액세스 트랜지스터(Qp11) 상에 형성되는 콘택트(106a)는 비트 라인(BL1)에 접속되고, 액세스 트랜지스터(Qp21) 상에 형성되는 콘택트(106b)는 비트 라인(BLB1)에 접속되고, 액세스 트랜지스터(Qp11, Qp21)의 게이트로부터 연장되는 게이트 배선(118a) 상에 형성되는 콘택트(107)는 워드 라인(WL1)에 접속되어 있다.

도 3b에 나타내는 바와 같이, 기판에 SRAM 셀 어레이에 대해 공통되는 제 1 웰(101a)인 n-well이 형성되고, 소자분리(102)에 의해 기판 상의 확산층이 분리되어 있다. 기판 상의 확산층에 의해 형성되는 제 1 기억 노드(Qa1)에는 불순물주입 등에 의해 제 1 n+드레인 확산층(104a)이 형성되고, 기판 상의 확산층에 의해 형성되는 제 2 기억 노드(Qb1)에는 불순물주입 등에 의해 제 2 n+드레인 확산층(104b)이 형성되어 있다. 또한, 제 1, 제 2 n+드레인 확산층(104a, 104b) 상에는 제 1, 제 2 실리사이드층(113a, 113b)이 각각 형성되어 있다. 제 1 n+드레인 확산층(104a) 상에 형성되는 콘택트(111a)는 제 1 p+드레인 확산층(103a)과 제 1 n+드레인 확산층(104a)의 경계 부근 상에 형성되고, 기억 노드 접속 배선(Na1)을 통해 드라이버 트랜지스터(Qn11)의 게이트 전극으로부터 연장되는 게이트 배선(118b) 상에 형성되는 콘택트(111a)에 접속된다.

제 1 웰(101a)과 동일 도전형을 갖는 제 1 n+드레인 확산층(104a)으로부터 기판에 대한 누설을 억제하기 위하여, 제 1 웰(101a)과 제 1 n+드레인 확산층(104a) 사이에 p+확산층인 제 1 누설방지 확산층(101b)이 형성되어 있다. 또한, 제 1 웰(101a)과 동일 도전형을 갖는 제 2 n+드레인 확산층(104b)으로부터 기판에 대한 누설을 억제하기 위하여, 제 1 웰(101a)과 제 2 n+드레인 확산층(104b) 사이에 p+확산층인 제 2 누설방지 확산층(101c)이 형성되어 있다.

도 3c에 나타내는 바와 같이, 기판 상에 SRAM 셀 어레이에 대해 공통되는 제 1 웰(101a)인 n-well이 형성되고, 소자분리(102)에 의해 기판 상의 확산층이 분리되어 있다. 기판 상의 확산층에 의해 형성되는 제 1 기억 노드(Qa1)에는 불순물주입 등에 의해 제 1 n+드레인 확산층(104a)이 형성되고, 기판 상의 확산층에 의해 형성되는 제 2 기억 노드(Qb1)에는 불순물주입 등에 의해 제 2 n+드레인 확산층(104b)이 형성되어 있다. 또한, 제 1, 제 2 n+드레인 확산층(104a, 104b)의 표면에는 제 1, 제 2 실리사이드층(113a, 113b)이 각각 형성되어 있다. 제 1 웰(101a)과 제 1 n+드레인 확산층(104a) 사이에 p+확산층인 제 1 누설방지 확산층(101b)이 형성되어 있다. 또한, 제 1 웰(101a)과 동일 도전형을 갖는 제 2 n+드레인 확산층(104b)으로부터 기판에 대한 누설을 억제하기 위하여, 제 1 웰(101a)과 제 2 n+확산층(104b) 사이에 p+확산층인 제 2 누설방지 확산층(101c)이 형성되어 있다.

제 1 n+드레인 확산층(104a)에 드라이버 트랜지스터(Qn11)를 형성하는 주상 실리콘층(122a)이 형성되고, 제 2 n+드레인 확산층(104b)에 드라이버 트랜지스터(Qn21)를 형성하는 주상 실리콘층(122b)이 형성되어 있다. 각각의 주상 실리콘층의 주위에는 게이트 절연막(117) 및 게이트 전극(118)이 형성되어 있다. 주상 실리콘층의 상부에는 n+소스 확산층(114)이 불순물주입 등에 의해 형성되고, 소스 확산층의 표면에는 실리사이드층(115)이 형성되어 있다. 드라이버 트랜지스터(Qn11, Qn21) 상에 형성되는 콘택트(108a, 108b)는, 함께 배선층을 통해 접지 전위(Vss1)에 접속되어 있다.

도 3d에 나타내는 바와 같이, 기판 상에 SRAM 셀 어레이에 대해 공통되는 제 1 웰(101a)인 n-well이 형성되고, 소자분리(102)에 의해 기판 상의 확산층이 분리되어 있다. 기판 상의 확산층에 의해 형성되는 제 2 기억 노드(Qb)에는 불순물주입 등에 의해, 제 2 p+드레인 확산층(103b) 및 제 2 n+드레인 확산층(104b)이 형성되어 있다. 드레인 확산층 상에는 제 2 실리사이드층(113b)이 형성되고, 제 2 실리사이드층(113b)에 의해, 제 2 p+드레인 확산층(103b)과 제 2 n+드레인 확산층(104b)이 직접 접속되어 있다. 이 때문에, n+드레인 확산층과 p+드레인 확산층을 분리하기 위한 소자분리나, n+드레인 확산층과 p+드레인 확산층을 접속하기 위한 콘택트의 형성이 불필요하므로, 메모리 셀 면적을 축소할 수 있다. 제 1 웰(101a)과 동일 도전형을 갖는 제 2 n+드레인 확산층(104b)으로부터 기판에 대한 누설을 억제하기 위하여, 제 1 웰(101a)과 제 2 n+드레인 확산층(104b) 사이에 p+확산층인 제 2 누설방지 확산층(101c)이 형성되어 있다.

제 2 p+드레인 확산층(103b) 상에는 액세스 트랜지스터(Qp21)를 구성하는 주상 실리콘층(122b)이 형성되고, 제 2 n+드레인 확산층(104b) 상에는 드라이버 트랜지스터(Qn21)를 구성하는 주상 실리콘층(122b)이 형성되어 있다. p, n 각각의 주상 실리콘층의 주위에 게이트 절연막(117) 및 게이트 전극(118)이 형성되어 있다. 각각의 주상 실리콘층의 상부에는 소스 확산층이 불순물주입 등에 의해 형성되고, 소스 확산층의 표면에는 실리사이드층(115)이 형성되어 있다. 액세스 트랜지스터(Qp21) 상에 형성되는 콘택트(108b)는 비트 라인(BLB1)에 접속되고, 드라이버 트랜지스터(Qn21) 상에 형성되는 콘택트(108b)는 접지 전위(Vss1)에 접속된다.

드라이버 트랜지스터(Qn21)의 게이트 전극으로부터 연장되는 게이트 배선(118c) 상에는 콘택트(110b)가 형성되고, 콘택트(110b)는 기억 노드 접속 배선(Na1)을 통해 제 1 n+드레인 확산층(104a) 상에 형성되는 콘택트(111a)에 접속되어 있다. 제 2 n+드레인 확산층(104b) 상에는 콘택트(111b)가 형성되고, 콘택트(111b)는 기억 노드 접속 배선(Nb1)을 통해 드라이버 트랜지스터(Qn11)의 게이트 전극으로부터 연장되는 게이트 배선(118b) 상에 형성된 콘택트(111a)에 접속되어 있다.

상기한 바와 같이, 본 발명에 있어서는, 기억 노드(Qa1, Qb1)가 형성되는 n+드레인 확산층과 p+드레인 확산층이 실리사이드층에 의하여 직접 접속되는 것에 의해, 액세스 트랜지스터 및 드라이버 트랜지스터의 드레인 확산층은 공통화되어, SRAM의 기억 노드로서 기능을 하고 있다. 이 때문에, n+드레인 확산층과 p+드레인 확산층을 분리하기 위한 소자분리가 불필요하게 되고, SRAM의 2개 기억 노드만을 분리하는 소자분리만으로 충분하기 때문에, 작은 SRAM 셀 면적을 실현할 수 있다.

도 4a~도 4d에 나타내는 바와 같이, 제 1 웰(201a)이 p-well이고, n+확산층과 기판 사이에 n+확산층인 제 1 누설방지 확산층(201b) 및 제 2 누설방지 확산층(201c)이 형성되는 구조에 있어서도, 마찬가지로 SRAM 셀을 형성할 수 있다. 이 경우에는, p+드레인 확산층(203a)과 제 1 웰(201a) 사이에 제 1 누설방지 확산층(201b)이 형성되고, p+드레인 확산층(203b)과 제 1 웰(201a) 사이에 제 2 누설방지 확산층(201c)이 형성되는 것에 의해, 확산층으로부터 기판에 대한 누설을 억제할 수 있다.

이하, 본 발명의 반도체 기억 장치의 제조 방법의 일례에 대해, 도 5a~도 13b를 참조하여 설명한다. 각 도면에 있어서 a는 평면도, b는 a의 D-D' 단면도이다.

도 5a 및 도 5b에 나타내는 바와 같이, 기판 상에 실리콘 질화막 등을 성막 하여, 주상 실리콘층(121a, 122a, 121b, 122b)의 패턴을 리소그래피에 의해 형성하고, 에칭하는 것에 의해, 실리콘 질화막 마스크(119) 및 주상 실리콘층(121a, 122a, 121b, 122b)을 형성한다. 이어서, 불순물주입 등에 의해, SRAM 셀 어레이 내에 제 1 웰(101a)인 n-well을 형성한다.

도 6a 및 도 6b에 나타내는 바와 같이, 소자분리(102)를 형성한다. 소자분리는, 우선 트랜치 패턴을 에칭하여, CVD 등에 의해 트랜치 패턴에 산화막을 채워넣고, 기판 상의 여분 산화막을 드라이 에칭이나 습식 에칭 등에 의해 제거하는 방법 등에 의해 형성한다. 이에 의해, 기판 상에 제 1 기억 노드(Qa1) 및 제 2 기억 노드(Qb1)가 되는 확산층의 패턴이 형성된다.

도 7a 및 도 7b에 나타내는 바와 같이, p+주입 영역(124) 및 n+주입 영역(125)에 각각 이온주입 등에 의해 불순물을 도입하여, 기판 상에 주상 실리콘층 하부의 드레인 확산층(103a, 103b, 104a, 104b)을 형성한다. 제 1 웰(101a)인 n-well과 동일 도전형을 갖는 n+드레인 확산층(104b)으로부터 기판에 대한 누설을 억제하기 위하여, p+확산층인 제 2 누설방지 확산층(101c)이 형성된다. 제 2 누설방지 확산층(101c)은 n+주입 영역(125)의 마스크를 이용하여 불순물주입 등에 의해 형성할 수 있다.

도 8a 및 도 8b에 나타내는 바와 같이, 게이트 절연막(117) 및 게이트 전극(118)을 성막한다. 게이트 절연막(117)은 산화막이나 High-k막에 의해 형성된다. 또한, 게이트 전극(118)은 폴리 실리콘이나 금속막에 의해 형성된다.

도 9a 및 도 9b에 나타내는 바와 같이, 레지스트(133)를 이용하여, 리소그래피에 의해 게이트 배선 패턴을 형성한다.

도 10a 및 도 10b에 나타내는 바와 같이, 레지스트(133)를 마스크로 하여 게이트 절연막(117) 및 게이트 전극(118)을 에칭하고 제거한다. 이에 의해 게이트 배선(118a~118c)이 형성된다. 그 후, 필러 상의 마스크(119)를 제거한다.

도 11a 및 도 11b에 나타내는 바와 같이, 실리콘 질화막 등의 절연막을 성막한 후, 에치 백(etched back) 처리하여, 주상 실리콘층의 측벽 및 게이트 전극의 측벽을 실리콘 질화막 등의 절연막(134)으로 덮는 구조로 한다.

도 12a 및 도 12b에 나타내는 바와 같이, p+주입 영역(124) 및 n+주입 영역(125)에 각각 이온주입 등에 의해 불순물을 도입하여, 주상 실리콘층 상부의 소스 확산층(114, 116)을 형성한다. 이어서, Ni 등의 금속을 스퍼터하여 열처리를 하는 것에 의해, 드레인 확산층 상의 실리사이드층(113a, 113b) 및 주상 실리콘층 상부의 소스 확산층 상의 실리사이드층(115)을 형성한다.

여기서, 주상 실리콘층 및 게이트 전극의 측벽을 덮고 있는 실리콘 질화막 등의 절연막(134)에 의해, 실리사이드층에 기인하는 드레인과 게이트 사이 및 소스와 게이트 사이의 합선을 억제할 수 있다.

도 13a 및 도 13b에 나타내는 바와 같이, 층간막인 실리콘 산화막을 형성한 후에 콘택트(106a~111a, 106b~111b)를 형성한다.

본 발명에 있어서의 SRAM 셀은 콘택트 사이의 최소간격에 의해, 레이아웃이 제한되어 있은 개소가 많다. 이 때문에, 콘택트 형성시에 첫 번째 리소그래피 및 에칭에 의해 주상 실리콘층 상의 콘택트만을 형성하고, 두 번째 리소그래피 및 에칭에 의해 확산층 상 및 게이트 상의 콘택트를 형성하는 것에 의해, 주상 실리콘층 상의 콘택트와, 확산층 상 및 게이트 상의 콘택트의 최소간격을 축소할 수 있어, 더욱 SRAM 셀 면적을 축소할 수 있다. 또, 게이트 상의 콘택트는 주상 실리콘층 상의 콘택트와 동일 공정에 의해 형성해도 좋다.

(실시형태 2) 도 14는 본 발명의 실시형태 2에 따른 SRAM의 평면도이다. 본 실시형태는 하기의 점에서 실시형태 1과 상이하다. 실시형태 2에서는, 기판 상의 제 1 확산층에 의해 형성되는 기억 노드인 Qa3과, 드라이버 트랜지스터(Qn23)의 게이트 전극으로부터 연장되는 게이트 배선은, 양자에 걸쳐서 형성되는 공통의 콘택트(310a)에 의해 접속되어 있다. 또한, 기판 상의 제 2 확산층에 의해 형성되는 기억 노드인 Qb3과, 드라이버 트랜지스터(Qn13)의 게이트 전극으로부터 연장되는 게이트 배선은, 양자에 걸쳐서 형성되는 공통의 콘택트(310b)에 의해 접속된다. 상기한 바와 같이, 게이트와 기억 노드를 배선층이 아닌 콘택트에 의해 접속 함으로써, SRAM 셀 내에 있어서의 콘택트의 수를 줄일 수 있으므로, 주상 실리콘층이나 콘택트의 배치를 조정하는 것에 의해, 셀 면적을 축소할 수 있다.

또, 실시형태 1에서 기술한 바와 같이, 워드 라인의 배선, 비트 라인의 배선 및 접지 전위 배선은, 바람직하게는, 다른 메모리 셀의 배선과 공용하기 위하여, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층에 배치된다. 또, 본 실시형태에서는, 노드 접속 배선은 콘택트에 의해 형성되어 있다. 이외의 점에 관해서는 실시형태 1에 나타내는 구성과 동일하므로 설명을 생략한다.

(실시형태 3) 도 15는 본 발명의 실시형태 3에 따른 SRAM의 평면도이다. 본 실시형태는 하기의 점에서 실시형태 1, 실시형태 2와 상이하다. 실시형태 1, 실시형태 2에서는, 기억 노드(Qa) 상에 있어서 콘택트(110a, 210a)는 드라이버 트랜지스터(Qn11, Qn12)에만 인접하여 배치되어 있지만, 기억 노드(Qb) 상에 있어서 콘택트(110b, 210b)는 드라이버 트랜지스터(Qn21, Qn22)와 액세스 트랜지스터(Qp21, Qp22) 사이의 확산층 상에 배치되어 있다. 이러한 레이아웃의 비대칭성에 의해, SRAM 셀의 특성에 비대칭성이 발생하여, 동작 마진이 좁아질 가능성이 있다. 본 실시형태에서는, 레이아웃이 상하(종)방향, 좌우(횡)방향 모두 대칭이기 때문에, 상기와 같은 비대칭성에 기인하는 동작 마진의 열화가 없고, 넓은 동작 마진을 갖는 SRAM 셀을 실현할 수 있다.

또한, 실시형태 2와 마찬가지로, 기판 상의 제 1 확산층에 의해 형성되는 기억 노드인 Qa4와, 드라이버 트랜지스터(Qn24)의 게이트 전극으로부터 연장되는 게이트 배선은, 양자에 걸쳐서 형성되는 공통의 콘택트(410a)에 의해 접속되고, 기판 상의 제 2 확산층에 의해 형성되는 기억 노드인 Qb4와, 드라이버 트랜지스터(Qn14)의 게이트 전극으로부터 연장되는 게이트 배선은, 양자에 걸쳐서 형성되는 공통의 콘택트(410b)에 의해 접속되어 있다.

또, 워드 라인의 배선, 비트 라인의 배선 및 접지 전위 배선은, 바람직하게는, 다른 메모리 셀의 배선과 공용하기 위하여, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층에 배치된다. 본 실시형태에서는, 노드 접속 배선은 콘택트에 의해 형성되어 있다.

상기 계층적인 배선 구성의 일례로서, 각 배선이 접촉하지 말아야할 콘택트와 접촉하지 않도록, 접지 전위 배선(Vss4)과 워드 라인(WL4)은 동일층으로 배선하고, 비트 라인(BL4, BLB4)은 워드 라인(WL4)보다 상위층으로 배선하는 구성을 실현할 수 있다.

(실시형태 4) 도 16은 본 발명의 실시형태 4에 따른 SRAM의 평면도이다. 본 실시형태에 있어서는, 실시형태 3과 마찬가지로 레이아웃이 상하(종)방향, 좌우(횡)방향 모두 대칭이기 때문에, 상기와 같은 비대칭성에 기인하는 문제가 발생하지 않는다. 이 때문에, 더욱 넓은 동작 마진을 갖는 SRAM 셀을 실현할 수 있다. 또, 워드 라인의 배선, 비트 라인의 배선 및 접지 전위 배선은, 바람직하게는, 다른 메모리 셀의 배선과 공용하기 위하여, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층에 배치된다.

상기 계층적인 배선 구성의 일례로서, 각 배선이 접촉하지 말아야할 콘택트와 접촉하지 않도록, 노드 접속 배선(Na5), 노드 접속 배선(Nb5), 및 접지 전위 배선(Vss5)은 워드 라인(WL5)보다 하위층으로 배선하고, 비트 라인(BL5, BLB5)은 워드 라인(WL5)보다 상위층으로 배선하는 구성을 실현할 수 있다.

(실시형태 5) 도 17은 본 발명의 실시형태 5에 따른 SRAM의 평면도이다. 본 실시형태에 있어서 실시형태 1과 상이한 점은, 액세스 트랜지스터를 형성하는 주상 실리콘층의 형상과 드라이버 트랜지스터를 형성하는 주상 실리콘층의 크기가 상이한 점이다. 본 발명의 Loadless 4T-SRAM에서는, 액세스 트랜지스터의 누설 전류를 드라이버 트랜지스터의 누설 전류보다 크게 설정할 필요가 있다. 도 17과 같이 액세스 트랜지스터를 형성하는 주상 실리콘층을 크게 설정함으로써, 액세스 트랜지스터의 누설 전류를 증가시킬 수 있다.

한편, 리드아웃 마진을 개선하고자하는 경우에는, 드라이버 트랜지스터의 주상 실리콘층을 크게 형성하여, 드라이버 트랜지스터의 전류를 크게 함으로써, 리드아웃 마진을 개선할 수 있다.

본 실시형태에 있어서는, 일례로서 실시형태 1과 동일한 레이아웃을 채용하였지만, 실제로는 실시형태 1의 레이아웃에 한정되지않고, 다른 실시형태의 레이아웃에 있어서도 동일하게 본 실시형태를 적용할 수 있다.

또, 실시형태 1에서 기술한 바와 같이, 워드 라인의 배선, 비트 라인의 배선, 전원 전위의 배선 및 접지 전위 배선은, 바람직하게는, 다른 메모리 셀의 배선과 공용하기 위하여, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층에 배치된다. 이 점에 있어서 계층적인 배선의 구성은, 일례로서, 상기 실시형태 1과 동일한 구성을 실현할 수 있다. 이외의 점에 관해서는 실시형태 1에 나타내는 구성과 동일하므로 설명을 생략한다.

(실시형태 6) 도 18은 본 발명의 실시형태 6에 따른 SRAM의 평면도이다. 본 실시형태는 하기의 점에서 실시형태 1과 상이하다. 본 실시형태에 있어서는, 유닛 셀(UC)로 나타낸 SRAM 셀의 상하로 배치된 셀이, 실시형태 1의 경우와 비교하여 상하방향으로 반전하여 배치되어 있다. 또한, 액세스 트랜지스터(Qp17, Qp27) 상에 형성된 비트 라인에 접속되는 콘택트(706a, 706b)가, 상방향으로 배치된 SRAM 셀의 비트 라인에 접속되는 콘택트와 공통화되어 있다. 상기한 바와 같이, 비트 라인에 접속되는 콘택트를 인접하는 셀과 공통화하는 것에 의해 콘택트(706a, 706b)를 크게 형성할 수 있기 때문에, 콘택트의 형성이 쉬워지고, 또한 콘택트 저항을 줄일 수 있다. 콘택트(706a, 706b) 이외의 SRAM 셀의 레이아웃은 실시형태 1의 경우와 동일하다.

본 실시형태에 있어서는, 일례로서 실시형태 1과 동일한 레이아웃을 채용하였지만, 실제로는 실시형태 1의 레이아웃에 한정되지않고, 다른 실시형태의 레이아웃에 있어서도 동일하게 본 실시형태를 적용할 수 있다.

또, 실시형태 1에서 기술한 바와 같이, 워드 라인의 배선, 비트 라인의 배선, 전원 전위의 배선 및 접지 전위 배선은, 바람직하게는, 다른 메모리 셀의 배선과 공용하기 위하여, 각 메모리 셀 내의 배선인 노드 접속 배선보다 상위층에 배치된다. 이 점에 있어서 계층적인 배선의 구성은, 일례로서, 상기 실시형태 1과 동일한 구성을 실현할 수 있다. 이외의 점에 관해서는 실시형태 1에 나타내는 구성과 동일하므로 설명을 생략한다.

본원에 대해서는, 2009년 9월 14일에 출원된 일본국 특허출원 특원 2009-211300을 기초로 하는 우선권을 주장하고, 당해 기초출원의 내용을 모두 본원에 도입한다.

101a, 201a: 제 1 웰

101b, 201b: 제 1 누설방지 확산층

101c, 201c: 제 2 누설방지 확산층

102, 202, 302, 402, 502, 602, 702: 소자분리

106a, 206a, 306a, 406a, 506a, 606a, 706a, 106b, 206b, 306b, 406b, 506b, 606b, 706b: 액세스 트랜지스터 주상 실리콘층 상의 콘택트

107, 207, 307, 407, 507a, 507b, 607, 707: 액세스 트랜지스터 게이트 배선 상의 콘택트

108a, 208a, 308a, 408a, 508a, 608a, 708a, 108b, 208b, 308b, 408b, 508b, 608b, 708b: 드라이버 트랜지스터 주상 실리콘층 상의 콘택트

110a, 210a, 310a, 410a, 510a, 610a, 710a, 110b, 210b, 310b, 410b, 510b, 610b, 710b: 기억 노드 상의 콘택트

111a, 211a, 511a, 611a, 711a, 111b, 211b, 511b, 611b, 711b: 게이트 배선 상의 콘택트

113a, 113b, 115, 213a, 213b, 215: 실리사이드층

114, 214: n+소스 확산층

116, 216: p+소스 확산층

117, 217: 게이트 절연막

118, 218, 804a, 804b, 804c, 804d: 게이트 전극

118a, 118b, 118c, 218a, 218b, 218c: 게이트 배선

119: 실리콘 산화막 등의 마스크층

120: 실리콘층

121a, 121b, 810a, 810b: 액세스 트랜지스터 주상 실리콘층

122a, 122b, 811a, 811b: 드라이버 트랜지스터 주상 실리콘층

812a, 812b: 로드 트랜지스터 주상 실리콘층

124, 324, 424, 524, 624, 724: p+주입 영역

125, 325, 425, 525, 625, 725: n+주입 영역

131: 실리콘 산화막

132: 실리콘 질화막 사이드월(side wall)

133: 레지스트

134, 334, 434, 534, 634, 734: 실리콘 질화막

801a, 801b: 비트 라인(bit line)

802: 접지 전위

803: 전원 전위

807a, 807b: 배선층

Qa1, Qa3, Qa4, Qa7, Qb1, Qb3, Qb4, Qb7: 기억 노드

Qp11, Qp21, Qp12, Qp22, Qp13, Qp23, Qp14, Qp24, Qp15, Qp25, Qp16, Qp26, Qp17, Qp27: 액세스 트랜지스터

Qn11, Qn21, Qn12, Qn22, Qn13, Qn23, Qn14, Qn24, Qn15, Qn25, Qn16, Qn26, Qn17, Qn27: 드라이버 트랜지스터

BL1, BL3, BL4, BL5, BL6, BL7, BLB1, BLB3, BLB4, BLB5, BLB6, BLB7: 비트 라인

WL1, WL3, WL4, WL5, WL6, WL7: 워드 라인(word line)

Vss1, Vss3, Vss4, Vss5, Vss6, Vss7: 접지 전위 배선

Na1, Nb1, Na5, Nb5, Na6, Nb6, Na7, Nb7: 노드 접속 배선

101b, 201b: 제 1 누설방지 확산층

101c, 201c: 제 2 누설방지 확산층

102, 202, 302, 402, 502, 602, 702: 소자분리

106a, 206a, 306a, 406a, 506a, 606a, 706a, 106b, 206b, 306b, 406b, 506b, 606b, 706b: 액세스 트랜지스터 주상 실리콘층 상의 콘택트

107, 207, 307, 407, 507a, 507b, 607, 707: 액세스 트랜지스터 게이트 배선 상의 콘택트

108a, 208a, 308a, 408a, 508a, 608a, 708a, 108b, 208b, 308b, 408b, 508b, 608b, 708b: 드라이버 트랜지스터 주상 실리콘층 상의 콘택트

110a, 210a, 310a, 410a, 510a, 610a, 710a, 110b, 210b, 310b, 410b, 510b, 610b, 710b: 기억 노드 상의 콘택트

111a, 211a, 511a, 611a, 711a, 111b, 211b, 511b, 611b, 711b: 게이트 배선 상의 콘택트

113a, 113b, 115, 213a, 213b, 215: 실리사이드층

114, 214: n+소스 확산층

116, 216: p+소스 확산층

117, 217: 게이트 절연막

118, 218, 804a, 804b, 804c, 804d: 게이트 전극

118a, 118b, 118c, 218a, 218b, 218c: 게이트 배선

119: 실리콘 산화막 등의 마스크층

120: 실리콘층

121a, 121b, 810a, 810b: 액세스 트랜지스터 주상 실리콘층

122a, 122b, 811a, 811b: 드라이버 트랜지스터 주상 실리콘층

812a, 812b: 로드 트랜지스터 주상 실리콘층

124, 324, 424, 524, 624, 724: p+주입 영역

125, 325, 425, 525, 625, 725: n+주입 영역

131: 실리콘 산화막

132: 실리콘 질화막 사이드월(side wall)

133: 레지스트

134, 334, 434, 534, 634, 734: 실리콘 질화막

801a, 801b: 비트 라인(bit line)

802: 접지 전위

803: 전원 전위

807a, 807b: 배선층

Qa1, Qa3, Qa4, Qa7, Qb1, Qb3, Qb4, Qb7: 기억 노드

Qp11, Qp21, Qp12, Qp22, Qp13, Qp23, Qp14, Qp24, Qp15, Qp25, Qp16, Qp26, Qp17, Qp27: 액세스 트랜지스터

Qn11, Qn21, Qn12, Qn22, Qn13, Qn23, Qn14, Qn24, Qn15, Qn25, Qn16, Qn26, Qn17, Qn27: 드라이버 트랜지스터

BL1, BL3, BL4, BL5, BL6, BL7, BLB1, BLB3, BLB4, BLB5, BLB6, BLB7: 비트 라인

WL1, WL3, WL4, WL5, WL6, WL7: 워드 라인(word line)

Vss1, Vss3, Vss4, Vss5, Vss6, Vss7: 접지 전위 배선

Na1, Nb1, Na5, Nb5, Na6, Nb6, Na7, Nb7: 노드 접속 배선

Claims (12)

- 4 개의 MOS 트랜지스터가 기판 상에 배열된 스태틱형 메모리 셀을 구비한 반도체 기억 장치로서,

상기 4 개의 MOS 트랜지스터 각각은,

메모리 셀 데이터를 유지하기 위하여 전하를 공급함과 함께 메모리에 액세스하기 위한 제 1 및 제 2 PMOS 액세스 트랜지스터와, 메모리 셀의 데이터를 판독하기 위하여 기억 노드를 구동하는 제 1 및 제 2 NMOS 드라이버 트랜지스터로서 기능을 하고,

메모리 셀 데이터를 유지하기 위하여 전하를 공급함과 함께 메모리에 액세스하기 위한 제 1 및 제 2 PMOS 액세스 트랜지스터에 있어서,

P 형의 제 1 확산층, 제 1 주상 반도체층 및 P 형의 제 2 확산층이 기판 상에 수직 방향으로 계층적으로 배치되고, 상기 제 1 주상 반도체층은 상기 제 1 주상 반도체층의 저부에 형성되는 상기 제 1 확산층과 상기 제 1 주상 반도체층의 상부에 형성되는 상기 제 2 확산층 사이에 배치되고, 상기 제 1 주상 반도체층의 측벽에 제 1 게이트가 형성되어 있고,

메모리 셀의 데이터를 판독하기 위하여 기억 노드를 구동하는 제 1 및 제 2 NMOS 드라이버 트랜지스터에 있어서,

N 형의 제 3 확산층, 제 2 주상 반도체층 및 N 형의 제 4 확산층이 기판 상에 수직 방향으로 계층적으로 배치되고, 상기 제 2 주상 반도체층은 상기 제 2 주상 반도체층의 저부에 형성되는 상기 제 3 확산층과 상기 제 1 주상 반도체층의 상부에 형성되는 상기 제 4 확산층 사이에 배치되고, 상기 제 2 주상 반도체층의 측벽에 제 2 게이트가 형성되어 있고,

상기 제 1 PMOS 액세스 트랜지스터 및 상기 제 1 NMOS 드라이버 트랜지스터는 서로 인접하여 배열되고,

상기 제 2 PMOS 액세스 트랜지스터 및 상기 제 2 NMOS 드라이버 트랜지스터는 서로 인접하여 배열되고,

상기 기판에는, 그 기판에 전위를 부여하기 위한 복수의 메모리 셀에 공통의 제 1 웰이 형성되고,

상기 제 1 PMOS 액세스 트랜지스터의 저부에 형성되는 상기 P 형의 제 1 확산층 및 상기 제 1 NMOS 드라이버 트랜지스터의 저부에 형성되는 상기 N 형의 제 3 확산층은, 각각의 표면에 형성된 제 1 실리사이드층을 통해 서로 접속되고,

상기 서로 접속된 상기 P 형의 제 1 확산층 및 N 형의 제 3 확산층은, 메모리 셀에 기억되는 데이터를 유지하기 위한 제 1 기억 노드로서 기능을 하고,

상기 N 형의 제 3 확산층 또는 P 형의 제 1 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 N 형의 제 3 확산층 또는 P 형의 제 1 확산층과 상기 제 1 웰 사이에 상기 제 1 웰과 반대 도전형을 갖는 제 1 누설방지 확산층의 저부가 소자 분리보다 얕아지도록 형성되고,

상기 제 1 누설방지 확산층은, 상기 P 형의 제 1 확산층 또는 N 형의 제 3 확산층과 직접 접속되고,

상기 제 2 PMOS 액세스 트랜지스터의 저부에 형성되는 상기 P 형의 제 1 확산층 및 상기 제 2 NMOS 드라이버 트랜지스터의 저부에 형성되는 상기 N 형의 제 3 확산층은, 각각의 표면에 형성된 제 2 실리사이드층을 통해 서로 접속되고,

상기 서로 접속된 상기 P 형의 제 1 확산층 및 N 형의 제 3 확산층은, 메모리 셀에 기억되는 데이터를 유지하기 위한 제 2 기억 노드로서 기능을 하고,

상기 N 형의 제 3 확산층 또는 P 형의 제 1 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 N 형의 제 3 확산층 또는 P 형의 제 1 확산층과 상기 제 1 웰 사이에 상기 제 1 웰과 반대 도전형을 갖는 제 2 누설방지 확산층의 저부가 소자 분리보다 얕아지도록 형성되고,

상기 제 2 누설방지 확산층은, 상기 P 형의 제 1 확산층 또는 N 형의 제 3 확산층과 직접 접속되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항에 있어서,

상기 제 1 누설방지 확산층은, 상기 N 형의 제 3 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 N 형의 제 3 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 P 형의 제 1 확산층과 직접 접속되고,

상기 제 2 누설방지 확산층은, 상기 N 형의 제 3 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 N 형의 제 3 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 P 형의 제 1 확산층과 직접 접속되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항에 있어서,

상기 제 1 누설방지 확산층은, 상기 P 형의 제 1 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 P 형의 제 1 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 N 형의 제 3 확산층과 직접 접속되고,

상기 제 2 누설방지 확산층은, 상기 P 형의 제 1 확산층과 상기 제 1 웰 사이의 누설을 방지하기 위하여, 상기 P 형의 제 1 확산층과 상기 제 1 웰 사이에 형성됨과 함께, 상기 N 형의 제 3 확산층과 직접 접속되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 제 1 및 제 2 PMOS 액세스 트랜지스터의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트의 적어도 하나를, 인접하는 메모리 셀의 PMOS 액세스 트랜지스터의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트와 공통화한 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 제 1 기억 노드로서 기능을 하는 상기 제 1 PMOS 액세스 트랜지스터의 P형의 제 1 확산층 또는 상기 제 1 NMOS 드라이버 트랜지스터의 N형의 제 3 확산층 상에 형성되는 상기 제 1 NMOS 드라이버 트랜지스터의 게이트로부터 연장되는 게이트 배선이, 상기 제 2 기억 노드로서 기능을 하는 상기 제 2 PMOS 액세스 트랜지스터의 P형의 제 1 확산층 또는 상기 제 2 NMOS 드라이버 트랜지스터의 N형의 제 3 확산층과 공통의 콘택트에 의해 접속되고,

상기 제 2 기억 노드로서 기능을 하는 상기 제 2 PMOS 액세스 트랜지스터의 P형의 제 1 확산층 또는 상기 제 2 NMOS 드라이버 트랜지스터의 N형의 제 3 확산층 상에 형성되는 상기 제 2 NMOS 드라이버 트랜지스터의 게이트로부터 연장되는 게이트 배선이, 상기 제 1 기억 노드로서 기능을 하는 상기 제 1 PMOS 액세스 트랜지스터의 P형의 제 1 확산층 또는 상기 제 1 NMOS 드라이버 트랜지스터의 N형의 제 3 확산층과 공통의 콘택트에 의해 접속되는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 제 1 및 제 2 NMOS 드라이버 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이는, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이 이상의 값을 갖고, 또는

상기 제 1 및 제 2 NMOS 드라이버 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이는, 상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 측벽의 둘레 길이 이하의 값을 갖는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 4개의 MOS 트랜지스터는 상기 기판 상에 2행 2열에 배열되고,

상기 제 1 PMOS 액세스 트랜지스터는 1행 1열째에 배열되고,

상기 제 1 NMOS 드라이버 트랜지스터는 2행 1열째에 배열되고,

상기 제 2 PMOS 액세스 트랜지스터는 1행 2열째에 배열되고,

상기 제 2 NMOS 드라이버 트랜지스터는 2행 2열째에 배열되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 7 항에 있어서,

상기 제 1 및 제 2 PMOS 액세스 트랜지스터의 게이트 전극으로부터 연장되는 게이트 배선 상에 형성되는 콘택트를 공유한 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 4개의 MOS 트랜지스터에 있어서,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터는 인접하여 배열되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 PMOS 액세스 트랜지스터에 인접하여 상기 제 1 확산층 상에 제 1 콘택트가 배치되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 PMOS 액세스 트랜지스터에 인접하여 상기 제 2 확산층 상에 제 2 콘택트가 배치되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 NMOS 드라이버 트랜지스터는 상기 제 1 PMOS 액세스 트랜지스터와 인접하여 배열되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 NMOS 드라이버 트랜지스터는 상기 제 2 PMOS 액세스 트랜지스터와 인접하여 배열되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 4개의 MOS 트랜지스터에 있어서,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터는 인접하여 배열되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 일측의 방향에 있어서, 상기 제 1 NMOS 드라이버 트랜지스터는 상기 제 1 PMOS 액세스 트랜지스터와 인접하여 배열되고,

상기 제 1 NMOS 드라이버 트랜지스터와 상기 제 1 PMOS 액세스 트랜지스터 사이의 확산층 상에는 제 3 콘택트가 형성되고,

상기 제 1 PMOS 액세스 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터의 인접방향으로 직교하는 타측의 방향에 있어서, 상기 제 2 NMOS 드라이버 트랜지스터는 상기 제 2 PMOS 액세스 트랜지스터와 인접하여 배열되고,

상기 제 2 NMOS 드라이버 트랜지스터와 상기 제 2 PMOS 액세스 트랜지스터 사이의 확산층 상에는 제 4 콘택트가 형성되어 있는 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 제 1 및 제 2 PMOS 액세스 트랜지스터를 형성하는 상기 주상 반도체층의 상부에 형성되는 콘택트의 적어도 하나를, 인접하는 메모리 셀의 PMOS 액세스 트랜지스터를 형성하는 주상 반도체층의 상부에 형성되는 콘택트와 공유화한 것을 특징으로 하는 반도체 기억 장치. - 제 1 항 내지 제 3 항 중 어느 한 항에 기재된 반도체 기억 장치를 제조하는 방법으로서,

상기 주상 반도체층 상에 형성되는 콘택트와, 상기 기판 상에 형성되는 콘택트 또는 게이트 배선 상에 형성되는 콘택트를 상이한 리소그래피 공정 또는 에칭 공정에 의해 형성하는 것을 특징으로 하는 반도체 기억 장치의 제조 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009211300A JP5524547B2 (ja) | 2009-09-14 | 2009-09-14 | 半導体記憶装置 |

| JPJP-P-2009-211300 | 2009-09-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110029101A KR20110029101A (ko) | 2011-03-22 |

| KR101160105B1 true KR101160105B1 (ko) | 2012-06-26 |

Family

ID=43034204

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100089932A KR101160105B1 (ko) | 2009-09-14 | 2010-09-14 | 반도체 기억 장치 및 그 제조 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US8169030B2 (ko) |

| EP (1) | EP2296176B1 (ko) |

| JP (1) | JP5524547B2 (ko) |

| KR (1) | KR101160105B1 (ko) |

| CN (1) | CN102024815B (ko) |

| TW (1) | TW201110327A (ko) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013016243A (ja) * | 2011-06-09 | 2013-01-24 | Semiconductor Energy Lab Co Ltd | 記憶装置 |

| US8755219B2 (en) | 2012-02-15 | 2014-06-17 | Unisantis Electronics Singapore Pte. Ltd. | Hierarchical wordline loadless 4GST-SRAM with a small cell area |

| CN103370781A (zh) * | 2012-02-15 | 2013-10-23 | 新加坡优尼山帝斯电子私人有限公司 | 半导体存储器件 |

| KR20130118949A (ko) * | 2012-02-15 | 2013-10-30 | 유니산티스 일렉트로닉스 싱가포르 프라이빗 리미티드 | 반도체 기억 장치 |

| US8836051B2 (en) * | 2012-06-08 | 2014-09-16 | Unisantis Electronics Singapore Pte. Ltd. | Method for producing semiconductor device and semiconductor device |

| KR101925012B1 (ko) * | 2012-07-17 | 2018-12-05 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그의 제조 방법 |

| US9082838B2 (en) * | 2012-09-28 | 2015-07-14 | Unisantis Electronics Singapore Pte. Ltd. | Method for producing a semiconductor device and semiconductor device |

| US8969949B2 (en) * | 2013-03-10 | 2015-03-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Structure and method for static random access memory device of vertical tunneling field effect transistor |

| WO2015008387A1 (ja) * | 2013-07-19 | 2015-01-22 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体装置の製造方法、及び、半導体装置 |

| JP2015032651A (ja) * | 2013-08-01 | 2015-02-16 | マイクロン テクノロジー, インク. | 半導体装置 |

| WO2015019444A1 (ja) * | 2013-08-07 | 2015-02-12 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体装置の製造方法、及び、半導体装置 |

| US10361270B2 (en) * | 2013-11-20 | 2019-07-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Nanowire MOSFET with different silicides on source and drain |

| JP5832057B1 (ja) | 2014-02-24 | 2015-12-16 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 記憶装置、半導体装置、及び記憶装置、半導体装置の製造方法 |

| WO2015129021A1 (ja) | 2014-02-28 | 2015-09-03 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体装置、及び半導体装置の製造方法 |

| JP6114425B2 (ja) * | 2016-03-11 | 2017-04-12 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッドUnisantis Electronics Singapore Pte Ltd. | 半導体装置の製造方法、及び、半導体装置 |

| KR102195321B1 (ko) * | 2016-08-31 | 2020-12-24 | 마이크론 테크놀로지, 인크 | 감지 증폭기 구성물 |

| EP3507831B1 (en) | 2016-08-31 | 2021-03-03 | Micron Technology, Inc. | Memory arrays |

| US11211384B2 (en) | 2017-01-12 | 2021-12-28 | Micron Technology, Inc. | Memory cells, arrays of two transistor-one capacitor memory cells, methods of forming an array of two transistor-one capacitor memory cells, and methods used in fabricating integrated circuitry |

| US10290639B2 (en) * | 2017-09-12 | 2019-05-14 | Globalfoundries Inc. | VNW SRAM with trinity cross-couple PD/PU contact and method for producing the same |

| US10566453B2 (en) | 2018-06-29 | 2020-02-18 | International Business Machines Corporation | Vertical transistor contact for cross-coupling in a memory cell |

| US10559572B2 (en) | 2018-06-29 | 2020-02-11 | International Business Machines Corporation | Vertical transistor contact for a memory cell with increased density |

| CN109326650B (zh) * | 2018-10-10 | 2022-04-19 | 中国科学院微电子研究所 | 半导体器件及其制造方法及包括该器件的电子设备 |

| US11640987B2 (en) * | 2021-02-04 | 2023-05-02 | Applied Materials, Inc. | Implant to form vertical FETs with self-aligned drain spacer and junction |

| WO2022239196A1 (ja) * | 2021-05-13 | 2022-11-17 | ユニサンティス エレクトロニクス シンガポール プライベート リミテッド | 半導体素子を用いたメモリ装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5641699A (en) | 1993-03-03 | 1997-06-24 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing a semiconductor device having a dummy cell |

| KR20010062611A (ko) * | 1999-12-23 | 2001-07-07 | 윌리엄 비. 켐플러 | 동적 임계 전압 4t sram 셀 |

| JP2004193588A (ja) | 2002-12-11 | 2004-07-08 | Internatl Business Mach Corp <Ibm> | 垂直MOSFET(verticalMOSFET)SRAMセル |

| WO2009096466A1 (ja) | 2008-01-29 | 2009-08-06 | Unisantis Electronics (Japan) Ltd. | 半導体記憶装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60128654A (ja) * | 1983-12-16 | 1985-07-09 | Hitachi Ltd | 半導体集積回路 |

| JPS63239973A (ja) | 1986-10-08 | 1988-10-05 | テキサス インスツルメンツ インコーポレイテツド | 集積回路およびその製造方法 |

| JP2703970B2 (ja) | 1989-01-17 | 1998-01-26 | 株式会社東芝 | Mos型半導体装置 |

| JP3403231B2 (ja) * | 1993-05-12 | 2003-05-06 | 三菱電機株式会社 | 半導体装置およびその製造方法 |

| JP3036588B2 (ja) * | 1997-02-03 | 2000-04-24 | 日本電気株式会社 | 半導体記憶装置 |

| JP3467416B2 (ja) | 1998-04-20 | 2003-11-17 | Necエレクトロニクス株式会社 | 半導体記憶装置及びその製造方法 |

| US6229161B1 (en) * | 1998-06-05 | 2001-05-08 | Stanford University | Semiconductor capacitively-coupled NDR device and its applications in high-density high-speed memories and in power switches |

| US6583452B1 (en) * | 2001-12-17 | 2003-06-24 | T-Ram, Inc. | Thyristor-based device having extended capacitive coupling |

| WO2003082954A1 (fr) * | 2002-03-28 | 2003-10-09 | Communications Research Laboratory, Independent Administrative Institution | Procede de production de dispositifs moleculaires |

| JP2005303111A (ja) * | 2004-04-14 | 2005-10-27 | Renesas Technology Corp | 半導体記憶装置 |

| JP5114968B2 (ja) * | 2007-02-20 | 2013-01-09 | 富士通セミコンダクター株式会社 | 半導体装置及びその製造方法 |

| US8288795B2 (en) * | 2010-03-02 | 2012-10-16 | Micron Technology, Inc. | Thyristor based memory cells, devices and systems including the same and methods for forming the same |

-

2009

- 2009-09-14 JP JP2009211300A patent/JP5524547B2/ja not_active Expired - Fee Related

-

2010

- 2010-09-13 TW TW099130837A patent/TW201110327A/zh unknown

- 2010-09-14 US US12/881,554 patent/US8169030B2/en active Active

- 2010-09-14 KR KR1020100089932A patent/KR101160105B1/ko active IP Right Grant

- 2010-09-14 EP EP10009572.8A patent/EP2296176B1/en active Active

- 2010-09-14 CN CN2010102843051A patent/CN102024815B/zh active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5641699A (en) | 1993-03-03 | 1997-06-24 | Matsushita Electric Industrial Co., Ltd. | Method of manufacturing a semiconductor device having a dummy cell |

| KR20010062611A (ko) * | 1999-12-23 | 2001-07-07 | 윌리엄 비. 켐플러 | 동적 임계 전압 4t sram 셀 |

| JP2004193588A (ja) | 2002-12-11 | 2004-07-08 | Internatl Business Mach Corp <Ibm> | 垂直MOSFET(verticalMOSFET)SRAMセル |

| WO2009096466A1 (ja) | 2008-01-29 | 2009-08-06 | Unisantis Electronics (Japan) Ltd. | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP2296176B1 (en) | 2014-08-20 |

| KR20110029101A (ko) | 2011-03-22 |

| CN102024815A (zh) | 2011-04-20 |

| TW201110327A (en) | 2011-03-16 |

| US20110062523A1 (en) | 2011-03-17 |

| EP2296176A1 (en) | 2011-03-16 |

| JP5524547B2 (ja) | 2014-06-18 |

| JP2011061110A (ja) | 2011-03-24 |

| CN102024815B (zh) | 2013-04-10 |

| US8169030B2 (en) | 2012-05-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101160105B1 (ko) | 반도체 기억 장치 및 그 제조 방법 | |

| KR101147582B1 (ko) | 반도체 기억 장치와 그 제조방법 | |

| KR101182025B1 (ko) | 반도체 기억장치 | |

| JP4756221B2 (ja) | 半導体記憶装置 | |

| KR101146869B1 (ko) | 반도체 기억장치 | |

| US8507995B2 (en) | Semiconductor memory device | |

| KR101176287B1 (ko) | 반도체 기억장치 | |

| WO2013121536A1 (ja) | 半導体記憶装置 | |

| WO2013121537A1 (ja) | 半導体記憶装置 | |

| JP2014099664A (ja) | 半導体記憶装置 | |

| JP5489272B2 (ja) | 半導体記憶装置 | |

| KR20070023458A (ko) | 풀 씨모스형 에스램 셀 | |

| JPWO2013121537A1 (ja) | 半導体記憶装置 | |

| JP5566697B2 (ja) | 半導体記憶装置 | |

| JPWO2013121536A1 (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| N231 | Notification of change of applicant | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20150612 Year of fee payment: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20160613 Year of fee payment: 5 |

|

| FPAY | Annual fee payment |

Payment date: 20170609 Year of fee payment: 6 |