JP7516786B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP7516786B2 JP7516786B2 JP2020040801A JP2020040801A JP7516786B2 JP 7516786 B2 JP7516786 B2 JP 7516786B2 JP 2020040801 A JP2020040801 A JP 2020040801A JP 2020040801 A JP2020040801 A JP 2020040801A JP 7516786 B2 JP7516786 B2 JP 7516786B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- layer

- semiconductor device

- base material

- circuit element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/131—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed

- H10W74/137—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed the encapsulations being directly on the semiconductor body

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/20—Arrangements for cooling

- H10W40/22—Arrangements for cooling characterised by their shape, e.g. having conical or cylindrical projections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

- H10D10/80—Heterojunction BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/10—Arrangements for heating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/20—Arrangements for cooling

- H10W40/25—Arrangements for cooling characterised by their materials

- H10W40/253—Semiconductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W40/00—Arrangements for thermal protection or thermal control

- H10W40/20—Arrangements for cooling

- H10W40/25—Arrangements for cooling characterised by their materials

- H10W40/255—Arrangements for cooling characterised by their materials having a laminate or multilayered structure, e.g. direct bond copper [DBC] ceramic substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W42/00—Arrangements for protection of devices

- H10W42/121—Arrangements for protection of devices protecting against mechanical damage

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/01—Manufacture or treatment

- H10W70/02—Manufacture or treatment of conductive package substrates serving as an interconnection, e.g. of metal plates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/01—Manufacture or treatment

- H10W70/05—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers

- H10W70/093—Connecting or disconnecting other interconnections thereto or therefrom, e.g. connecting bond wires or bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/65—Shapes or dispositions of interconnections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W95/00—Packaging processes not covered by the other groups of this subclass

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

- H10D10/80—Heterojunction BJTs

- H10D10/821—Vertical heterojunction BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

- H10W72/01231—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition

- H10W72/01233—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating

- H10W72/01235—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating by plating, e.g. electroless plating or electroplating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

- H10W72/01251—Changing the shapes of bumps

- H10W72/01255—Changing the shapes of bumps by using masks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

- H10W72/01251—Changing the shapes of bumps

- H10W72/01257—Changing the shapes of bumps by reflowing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/019—Manufacture or treatment of bond pads

- H10W72/01931—Manufacture or treatment of bond pads using blanket deposition

- H10W72/01933—Manufacture or treatment of bond pads using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating

- H10W72/01935—Manufacture or treatment of bond pads using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating by plating, e.g. electroless plating or electroplating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07231—Techniques

- H10W72/07236—Soldering or alloying

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/221—Structures or relative sizes

- H10W72/222—Multilayered bumps, e.g. a coating on top and side surfaces of a bump core

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/221—Structures or relative sizes

- H10W72/227—Multiple bumps having different sizes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/241—Dispositions, e.g. layouts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/251—Materials

- H10W72/252—Materials comprising solid metals or solid metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/261—Functions other than electrical connecting

- H10W72/265—Providing thermal transfer, e.g. thermal bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/261—Functions other than electrical connecting

- H10W72/267—Multiple bump connectors having different functions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/923—Bond pads having multiple stacked layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/926—Multiple bond pads having different sizes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/951—Materials of bond pads

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/951—Materials of bond pads

- H10W72/952—Materials of bond pads comprising metals or metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Wire Bonding (AREA)

- Physics & Mathematics (AREA)

- Geometry (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Integrated Circuits (AREA)

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Bipolar Transistors (AREA)

Description

表面に回路素子及び当該回路素子に接続される電極を有する基板と、当該基板上に設けられ、前記回路素子又は前記電極に接して電気的に接続された外部接続用の導体突起部と、を備え、前記基板は、第1基材と、当該第1基材上に配置された第2基材とを含み、前記回路素子及び前記電極が前記第2基材に形成された、半導体装置の製造方法であって、

表面に前記回路素子及び前記電極を有する半導体薄膜を、剥離層を介して化合物半導体基材に形成する工程と、

前記剥離層をエッチングにより除去して前記半導体薄膜を前記化合物半導体基材から剥離する工程と、

前記第1基材を構成する単体半導体基材上の所定位置に、前記第2基材を構成する前記半導体薄膜を接合する工程と、

前記第2基材上に設けられ、前記回路素子又は前記電極に接続される外部接続用の導体突起部を形成する工程と、

を有する。

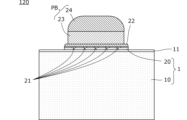

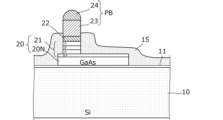

図1は第1の実施形態に係る半導体装置110の断面図である。この半導体装置110は、基板1と、この基板1上に設けられた第2基材側電極22に接して電気的に接続された導体ピラー23と、この導体ピラー23上に形成されたはんだ層24と、を備える。この導体ピラー23及びはんだ層24によって導体ピラーバンプPBが構成されている。

第2の実施形態では、第1の実施形態とは導体突起部の構成が異なる半導体装置について示す。

第3の実施形態では、平坦化樹脂層を備える幾つかの半導体装置について例示する。

第4の実施形態では、複数箇所に外部接続用の導体突起を備える一つの半導体装置の例について示す。

第5の実施形態では、第2基材の製造方法、及び第1基材に対する第2基材の接合方法について示す。

第6の実施形態では、第1基材10と第2基材20とを接合する接合層の構造に特徴を有する半導体装置について示す。

第7の実施形態では、第1基材10と第2基材20とを接合する接合層の構造に特徴を有する半導体装置について示す。

(1)第1基材10の表面に、第1層としての絶縁体層17を形成する。

(2)その絶縁体層17の表面に第2層としての金属層18Aを形成する。

(3)この金属層18の表面に第3層としての絶縁体層17を形成する。

(4)この絶縁体層17の所定位置(下層の金属層18Aの形成位置)に開口を形成する。

(5)絶縁体層17上に金属層18Cを形成するとともに、上記開口内に金属層18Bを形成する。

(6)最上層としての絶縁体層17を形成する。

1…基板

10…第1基材

11…接合層

12…第1基材側電極

15…平坦化樹脂層

16…絶縁体層

20…第2基材

20D…エピタキシャル層

20N…半導体基材

21…回路素子

22…第2基材側電極

13,23…導体ピラー

14,24…はんだ層

29…剥離層

30…GaAs基板

32,42…電極

33,43…導体ピラー

34,44…はんだ層

51A,51B…ヘテロ接合バイポーラトランジスタ

52…スパイラルインダクタ

53…MIMC

85…レジスト膜

90…実装基板

91,92…実装基板側電極

110,111,120,130A,130B,131,140,160,170…半導体装置

200…母基板

Claims (13)

- 表面に回路素子及び当該回路素子に接続される電極を有する基板と、

前記基板上に設けられ、前記回路素子又は前記電極に接続された外部接続用の導体突起部と、

を備え、

前記基板は、第1基材と、当該第1基材上に配置され、前記第1基材とは材料が異なる第2基材とを含み、

前記回路素子及び前記電極は前記第2基材に形成され、

前記第1基材と前記第2基材との間に、前記第1基材と前記第2基材とを接合する接合層を備え、

前記第1基材は前記第2基材に比べて熱伝導率が高く、

前記接合層は前記第2基材に比べて熱伝導率が高く、

前記接合層は前記第1基材に比較して電気抵抗率が高い絶縁体である、

半導体装置。 - 表面に回路素子及び当該回路素子に接続される電極を有する基板と、

前記基板上に設けられ、前記回路素子又は前記電極に接続された外部接続用の導体突起部と、

を備え、

前記基板は、第1基材と、当該第1基材上に配置され、前記第1基材とは材料が異なる第2基材とを含み、

前記回路素子及び前記電極は前記第2基材に形成され、

前記第1基材と前記第2基材との間に、前記第1基材と前記第2基材とを接合する接合層を備え、

前記第1基材は前記第2基材に比べて熱伝導率が高く、

前記接合層は前記第2基材に比べて熱伝導率が高く、

前記接合層は、絶縁体層と金属層とを含む複合材料の層である、

半導体装置。 - 前記第1基材は単体半導体の基材であり、

前記第2基材は化合物半導体の基材である、

請求項1または請求項2に記載の半導体装置。 - 前記第2基材は前記第1基材より薄い、

請求項1乃至請求項3のいずれかに記載の半導体装置。 - 前記回路素子は動作時に発熱する発熱体であり、前記導体突起部は前記発熱体である前記回路素子の直近に設けられている、

請求項1乃至請求項4のいずれかに記載の半導体装置。 - 前記第2基材は前記第1基材の外縁からはみ出さない、

請求項1乃至請求項5のいずれかに記載の半導体装置。 - 前記接合層は、前記第1基材に比べて熱伝導率が高い、

請求項1に記載の半導体装置。 - 前記第1基材はSi基材であり、

前記絶縁体層はSi化合物の層である、

請求項2に記載の半導体装置。 - 前記絶縁体層の少なくとも一部は樹脂である、

請求項2に記載の半導体装置。 - 前記第1基材の、前記第2基材に重ならない位置の表面に第1基材側電極が形成され、

前記導体突起部は前記第1基材側電極に接続された、

請求項1乃至請求項9のいずれかに記載の半導体装置。 - 前記導体突起部は、導体ピラー上にはんだ層が形成された導体ピラーである、

請求項1乃至請求項10のいずれかに記載の半導体装置。 - 表面に回路素子及び当該回路素子に接続される電極を有する基板と、当該基板上に設けられ、前記回路素子又は前記電極に接して電気的に接続された外部接続用の導体突起部と、を備え、前記基板は、第1基材と、当該第1基材上に配置された第2基材とを含み、前記回路素子及び前記電極が前記第2基材に形成された、半導体装置の製造方法であって、

表面に前記回路素子及び前記電極を有する半導体薄膜を、剥離層を介して化合物半導体基材に形成する工程と、

前記剥離層をエッチングにより除去して前記半導体薄膜を前記化合物半導体基材から剥離する工程と、

前記第2基材に比べて熱伝導率が高い前記第1基材を構成する単体半導体基材上の所定位置に、前記第2基材に比べて熱伝導率が高く、前記第1基材に比較して電気抵抗率が高い絶縁体である接合層を用いて、前記第2基材を構成する前記半導体薄膜を接合する工程と、

前記第2基材上に設けられ、前記回路素子又は前記電極に接続される外部接続用の導体突起部を形成する工程と、

を有する半導体装置の製造方法。 - 表面に回路素子及び当該回路素子に接続される電極を有する基板と、当該基板上に設けられ、前記回路素子又は前記電極に接して電気的に接続された外部接続用の導体突起部と、を備え、前記基板は、第1基材と、当該第1基材上に配置された第2基材とを含み、前記回路素子及び前記電極が前記第2基材に形成された、半導体装置の製造方法であって、

表面に前記回路素子及び前記電極を有する半導体薄膜を、剥離層を介して化合物半導体基材に形成する工程と、

前記剥離層をエッチングにより除去して前記半導体薄膜を前記化合物半導体基材から剥離する工程と、

前記第2基材に比べて熱伝導率が高い前記第1基材を構成する単体半導体基材上の所定位置に、前記第2基材に比べて熱伝導率が高く、絶縁体層と金属層とを含む複合材料の層である接合層を用いて、前記第2基材を構成する前記半導体薄膜を接合する工程と、

前記第2基材上に設けられ、前記回路素子又は前記電極に接続される外部接続用の導体突起部を形成する工程と、

を有する半導体装置の製造方法。

Priority Applications (17)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020040801A JP7516786B2 (ja) | 2019-06-21 | 2020-03-10 | 半導体装置及びその製造方法 |

| TW113136387A TWI915980B (zh) | 2019-06-21 | 2020-05-14 | 半導體裝置 |

| TW112130657A TWI854787B (zh) | 2019-06-21 | 2020-05-14 | 半導體裝置 |

| TW113118768A TWI879574B (zh) | 2019-06-21 | 2020-05-14 | 半導體裝置 |

| TW109116022A TWI825318B (zh) | 2019-06-21 | 2020-05-14 | 半導體裝置及其製造方法 |

| US16/901,980 US11677018B2 (en) | 2019-06-21 | 2020-06-15 | Semiconductor device and method for producing the same |

| CN202411653853.5A CN119694993A (zh) | 2019-06-21 | 2020-06-19 | 半导体装置 |

| CN202411653966.5A CN119694995A (zh) | 2019-06-21 | 2020-06-19 | 半导体装置 |

| CN202010564522.XA CN112117246A (zh) | 2019-06-21 | 2020-06-19 | 半导体装置及其制造方法 |

| CN202411653903.XA CN119694994A (zh) | 2019-06-21 | 2020-06-19 | 半导体装置 |

| CN202411653284.4A CN119694992A (zh) | 2019-06-21 | 2020-06-19 | 半导体装置 |

| US18/296,778 US12136664B2 (en) | 2019-06-21 | 2023-04-06 | Semiconductor device and method for producing the same |

| JP2024077830A JP7677497B2 (ja) | 2019-06-21 | 2024-05-13 | 半導体装置及びその製造方法 |

| US18/903,862 US20250022942A1 (en) | 2019-06-21 | 2024-10-01 | Semiconductor device and method for producing the same |

| JP2025074306A JP2025114644A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074305A JP2025114643A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074304A JP2025114642A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019115560 | 2019-06-21 | ||

| JP2019115560 | 2019-06-21 | ||

| JP2020040801A JP7516786B2 (ja) | 2019-06-21 | 2020-03-10 | 半導体装置及びその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024077830A Division JP7677497B2 (ja) | 2019-06-21 | 2024-05-13 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2021002644A JP2021002644A (ja) | 2021-01-07 |

| JP2021002644A5 JP2021002644A5 (ja) | 2022-11-17 |

| JP7516786B2 true JP7516786B2 (ja) | 2024-07-17 |

Family

ID=73798971

Family Applications (5)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020040801A Active JP7516786B2 (ja) | 2019-06-21 | 2020-03-10 | 半導体装置及びその製造方法 |

| JP2024077830A Active JP7677497B2 (ja) | 2019-06-21 | 2024-05-13 | 半導体装置及びその製造方法 |

| JP2025074304A Pending JP2025114642A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074305A Pending JP2025114643A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074306A Pending JP2025114644A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

Family Applications After (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2024077830A Active JP7677497B2 (ja) | 2019-06-21 | 2024-05-13 | 半導体装置及びその製造方法 |

| JP2025074304A Pending JP2025114642A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074305A Pending JP2025114643A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

| JP2025074306A Pending JP2025114644A (ja) | 2019-06-21 | 2025-04-28 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US11677018B2 (ja) |

| JP (5) | JP7516786B2 (ja) |

| CN (5) | CN119694992A (ja) |

| TW (3) | TWI825318B (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7516786B2 (ja) | 2019-06-21 | 2024-07-17 | 株式会社村田製作所 | 半導体装置及びその製造方法 |

| CN113517209A (zh) * | 2020-04-10 | 2021-10-19 | 长鑫存储技术有限公司 | 半导体结构及其形成方法 |

| WO2022259923A1 (ja) * | 2021-06-11 | 2022-12-15 | 株式会社村田製作所 | 半導体装置 |

| US20250080063A1 (en) * | 2023-09-06 | 2025-03-06 | Wolfspeed, Inc. | Transistor with gate layout, device implementing the transistor with output pre-matching, and process of implementing the same |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009190918A (ja) | 2008-02-13 | 2009-08-27 | New Japan Radio Co Ltd | 窒化物半導体基板の製造方法及び窒化物半導体装置の製造方法 |

| JP2012169586A (ja) | 2011-01-24 | 2012-09-06 | Fujitsu Ltd | ヒートスプレッダ及びその製造方法、半導体装置、電子装置 |

| JP2013191655A (ja) | 2012-03-13 | 2013-09-26 | Nippon Telegr & Teleph Corp <Ntt> | ヘテロ接合バイポーラトランジスタおよびその製造方法 |

| JP2019009409A (ja) | 2017-06-28 | 2019-01-17 | 株式会社村田製作所 | 半導体チップ |

| JP2019075536A (ja) | 2017-10-11 | 2019-05-16 | 株式会社村田製作所 | パワーアンプモジュール |

Family Cites Families (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05190488A (ja) * | 1991-07-10 | 1993-07-30 | Nec Corp | オーミック電極の製造方法 |

| US7247892B2 (en) * | 2000-04-24 | 2007-07-24 | Taylor Geoff W | Imaging array utilizing thyristor-based pixel elements |

| JP4701506B2 (ja) * | 2000-09-14 | 2011-06-15 | ソニー株式会社 | 回路ブロック体の製造方法、配線回路装置の製造方法並びに半導体装置の製造方法 |

| JP2003229366A (ja) * | 2002-02-05 | 2003-08-15 | Matsushita Electric Ind Co Ltd | 半導体積層構造 |

| JP2005129825A (ja) * | 2003-10-27 | 2005-05-19 | Sumitomo Chemical Co Ltd | 化合物半導体基板の製造方法 |

| KR100687758B1 (ko) * | 2005-12-08 | 2007-02-27 | 한국전자통신연구원 | 이종 접합 바이폴라 트랜지스터 및 그 제조방법 |

| JP2008204968A (ja) * | 2007-02-16 | 2008-09-04 | Furukawa Electric Co Ltd:The | 半導体パッケージ基板とその製造方法 |

| JP2010206020A (ja) * | 2009-03-04 | 2010-09-16 | Panasonic Corp | 半導体装置 |

| US20100270591A1 (en) * | 2009-04-27 | 2010-10-28 | University Of Seoul Industry Cooperation Foundation | High-electron mobility transistor |

| CN102714176A (zh) * | 2010-02-26 | 2012-10-03 | 住友化学株式会社 | 电子器件及电子器件的制造方法 |

| JP2012089828A (ja) * | 2010-09-22 | 2012-05-10 | Toshiba Corp | 半導体装置の製造方法 |

| US8772817B2 (en) * | 2010-12-22 | 2014-07-08 | Cree, Inc. | Electronic device submounts including substrates with thermally conductive vias |

| DE112012006007T5 (de) * | 2012-03-09 | 2014-11-20 | Mitsubishi Electric Corp. | Halbleitermodul |

| JP6307832B2 (ja) * | 2013-01-22 | 2018-04-11 | 三菱マテリアル株式会社 | パワーモジュール用基板、ヒートシンク付パワーモジュール用基板、ヒートシンク付パワーモジュール |

| JP6120704B2 (ja) * | 2013-07-03 | 2017-04-26 | 三菱電機株式会社 | 半導体装置 |

| JP6004343B2 (ja) * | 2013-09-13 | 2016-10-05 | 日本電信電話株式会社 | 半導体装置の製造方法 |

| JP2015065241A (ja) * | 2013-09-24 | 2015-04-09 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法および半導体装置 |

| JP2015144248A (ja) * | 2013-12-25 | 2015-08-06 | キヤノン株式会社 | 半導体装置、及びその製造方法 |

| KR102019914B1 (ko) * | 2014-06-11 | 2019-11-04 | 엘지이노텍 주식회사 | 발광 소자 |

| US20160141220A1 (en) * | 2014-11-18 | 2016-05-19 | Sumitomo Electric Industries, Ltd. | Hetero-bipolar transistor and method for producing the same |

| JP6071009B2 (ja) * | 2014-11-27 | 2017-02-01 | 株式会社村田製作所 | 化合物半導体装置 |

| JP2016171172A (ja) * | 2015-03-12 | 2016-09-23 | 日本電信電話株式会社 | ヘテロ接合バイポーラトランジスタおよびその製造方法 |

| JP6415381B2 (ja) * | 2015-04-30 | 2018-10-31 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JP6348451B2 (ja) | 2015-05-25 | 2018-06-27 | 日本電信電話株式会社 | ヘテロ接合バイポーラトランジスタ |

| CN107771352B (zh) * | 2015-06-26 | 2022-05-10 | 英特尔公司 | 设计的硅衬底上的gan器件 |

| US20180309025A1 (en) * | 2015-10-29 | 2018-10-25 | Kyocera Corporation | Light-emitting device, light receiving and emitting device module, and optical sensor |

| JP2018026406A (ja) * | 2016-08-08 | 2018-02-15 | 株式会社村田製作所 | ヘテロ接合バイポーラトランジスタ |

| US9997590B2 (en) * | 2016-10-24 | 2018-06-12 | International Büsiness Machines Corporation | FinFET resistor and method to fabricate same |

| US10847436B2 (en) * | 2017-10-11 | 2020-11-24 | Murata Manufacturing Co., Ltd. | Power amplifier module |

| JP2019102724A (ja) * | 2017-12-06 | 2019-06-24 | 株式会社村田製作所 | 半導体素子 |

| CN108598158B (zh) * | 2018-03-09 | 2019-06-07 | 苏州闻颂智能科技有限公司 | 一种共射共基异质结双极型晶体管 |

| JP7516786B2 (ja) | 2019-06-21 | 2024-07-17 | 株式会社村田製作所 | 半導体装置及びその製造方法 |

-

2020

- 2020-03-10 JP JP2020040801A patent/JP7516786B2/ja active Active

- 2020-05-14 TW TW109116022A patent/TWI825318B/zh active

- 2020-05-14 TW TW112130657A patent/TWI854787B/zh active

- 2020-05-14 TW TW113118768A patent/TWI879574B/zh active

- 2020-06-15 US US16/901,980 patent/US11677018B2/en active Active

- 2020-06-19 CN CN202411653284.4A patent/CN119694992A/zh active Pending

- 2020-06-19 CN CN202411653853.5A patent/CN119694993A/zh active Pending

- 2020-06-19 CN CN202411653966.5A patent/CN119694995A/zh active Pending

- 2020-06-19 CN CN202411653903.XA patent/CN119694994A/zh active Pending

- 2020-06-19 CN CN202010564522.XA patent/CN112117246A/zh active Pending

-

2023

- 2023-04-06 US US18/296,778 patent/US12136664B2/en active Active

-

2024

- 2024-05-13 JP JP2024077830A patent/JP7677497B2/ja active Active

- 2024-10-01 US US18/903,862 patent/US20250022942A1/en active Pending

-

2025

- 2025-04-28 JP JP2025074304A patent/JP2025114642A/ja active Pending

- 2025-04-28 JP JP2025074305A patent/JP2025114643A/ja active Pending

- 2025-04-28 JP JP2025074306A patent/JP2025114644A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009190918A (ja) | 2008-02-13 | 2009-08-27 | New Japan Radio Co Ltd | 窒化物半導体基板の製造方法及び窒化物半導体装置の製造方法 |

| JP2012169586A (ja) | 2011-01-24 | 2012-09-06 | Fujitsu Ltd | ヒートスプレッダ及びその製造方法、半導体装置、電子装置 |

| JP2013191655A (ja) | 2012-03-13 | 2013-09-26 | Nippon Telegr & Teleph Corp <Ntt> | ヘテロ接合バイポーラトランジスタおよびその製造方法 |

| JP2019009409A (ja) | 2017-06-28 | 2019-01-17 | 株式会社村田製作所 | 半導体チップ |

| JP2019075536A (ja) | 2017-10-11 | 2019-05-16 | 株式会社村田製作所 | パワーアンプモジュール |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2025114644A (ja) | 2025-08-05 |

| TW202504100A (zh) | 2025-01-16 |

| JP2021002644A (ja) | 2021-01-07 |

| JP2025114643A (ja) | 2025-08-05 |

| US11677018B2 (en) | 2023-06-13 |

| CN112117246A (zh) | 2020-12-22 |

| US12136664B2 (en) | 2024-11-05 |

| TWI825318B (zh) | 2023-12-11 |

| TW202101762A (zh) | 2021-01-01 |

| US20230246094A1 (en) | 2023-08-03 |

| JP2025114642A (ja) | 2025-08-05 |

| US20250022942A1 (en) | 2025-01-16 |

| CN119694995A (zh) | 2025-03-25 |

| US20200403088A1 (en) | 2020-12-24 |

| CN119694993A (zh) | 2025-03-25 |

| TW202435452A (zh) | 2024-09-01 |

| JP2024102316A (ja) | 2024-07-30 |

| CN119694992A (zh) | 2025-03-25 |

| JP7677497B2 (ja) | 2025-05-15 |

| TWI854787B (zh) | 2024-09-01 |

| TW202349706A (zh) | 2023-12-16 |

| CN119694994A (zh) | 2025-03-25 |

| TWI879574B (zh) | 2025-04-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7677497B2 (ja) | 半導体装置及びその製造方法 | |

| TWI333278B (en) | Group iii nitride bases flip-chip integrated circuit and method for fabricating | |

| JP2021197447A (ja) | 半導体装置 | |

| JP2004319552A (ja) | フリップチップ型対面電極hemt | |

| JP7625825B2 (ja) | 半導体装置 | |

| JP7608814B2 (ja) | Rf回路モジュール及びその製造方法 | |

| US12199083B2 (en) | RF circuit module and manufacturing method therefor | |

| TWI915980B (zh) | 半導體裝置 | |

| JP3744828B2 (ja) | 半導体装置 | |

| JP2012209334A (ja) | ミリ波帯用薄型パッケージおよびその製造方法 | |

| JP5562898B2 (ja) | 半導体装置およびその製造方法 | |

| WO2019208295A1 (ja) | バイポーラトランジスタおよびその製造方法 | |

| JP2010186962A (ja) | 半導体パッケージおよびその作製方法 | |

| JPH09246812A (ja) | 高周波半導体装置 | |

| JPS5929377Y2 (ja) | 高周波高出力トランジスタ装置 | |

| TW202601943A (zh) | 表面黏著功率元件及其製作方法 | |

| WO2024202593A1 (ja) | 化合物半導体増幅器及び回路モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20221109 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230926 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20231124 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20240213 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240513 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20240520 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240604 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240617 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7516786 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |