JP2019102724A - 半導体素子 - Google Patents

半導体素子 Download PDFInfo

- Publication number

- JP2019102724A JP2019102724A JP2017234277A JP2017234277A JP2019102724A JP 2019102724 A JP2019102724 A JP 2019102724A JP 2017234277 A JP2017234277 A JP 2017234277A JP 2017234277 A JP2017234277 A JP 2017234277A JP 2019102724 A JP2019102724 A JP 2019102724A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- electrode

- emitter

- semiconductor device

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 123

- 239000004020 conductor Substances 0.000 claims abstract description 44

- 239000003870 refractory metal Substances 0.000 claims abstract description 10

- 238000000926 separation method Methods 0.000 claims abstract description 7

- 239000007769 metal material Substances 0.000 claims abstract description 3

- 239000002184 metal Substances 0.000 claims description 50

- 229910052751 metal Inorganic materials 0.000 claims description 50

- 239000000758 substrate Substances 0.000 claims description 20

- 238000002844 melting Methods 0.000 claims description 15

- 230000008018 melting Effects 0.000 claims description 15

- 229910052750 molybdenum Inorganic materials 0.000 claims description 10

- 229910052715 tantalum Inorganic materials 0.000 claims description 10

- 229910052721 tungsten Inorganic materials 0.000 claims description 10

- 229910052804 chromium Inorganic materials 0.000 claims description 8

- 230000005669 field effect Effects 0.000 claims description 6

- 230000035882 stress Effects 0.000 abstract description 78

- 230000008646 thermal stress Effects 0.000 abstract description 43

- 230000003247 decreasing effect Effects 0.000 abstract description 3

- 239000010410 layer Substances 0.000 description 305

- 230000004048 modification Effects 0.000 description 16

- 238000012986 modification Methods 0.000 description 16

- 230000008859 change Effects 0.000 description 15

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 12

- 239000011347 resin Substances 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- 238000004088 simulation Methods 0.000 description 8

- 150000002739 metals Chemical class 0.000 description 7

- 229910000679 solder Inorganic materials 0.000 description 7

- 229910052719 titanium Inorganic materials 0.000 description 7

- 229910045601 alloy Inorganic materials 0.000 description 6

- 239000000956 alloy Substances 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 6

- 230000000694 effects Effects 0.000 description 6

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 244000126211 Hericium coralloides Species 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 230000017525 heat dissipation Effects 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000010030 laminating Methods 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910016006 MoSi Inorganic materials 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910004166 TaN Inorganic materials 0.000 description 1

- -1 TaN and TiN Chemical class 0.000 description 1

- 229910010038 TiAl Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000009429 distress Effects 0.000 description 1

- 238000011156 evaluation Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8222—Bipolar technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/8252—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using III-V technology

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

- H01L23/3677—Wire-like or pin-like cooling fins or heat sinks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/562—Protection against mechanical damage

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/082—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including bipolar components only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/082—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including bipolar components only

- H01L27/0823—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including bipolar components only including vertical bipolar transistors only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/04—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body

- H01L27/08—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind

- H01L27/085—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only

- H01L27/098—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being a semiconductor body including only semiconductor components of a single kind including field-effect components only the components being PN junction gate field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0804—Emitter regions of bipolar transistors

- H01L29/0817—Emitter regions of bipolar transistors of heterojunction bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1004—Base region of bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/201—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys

- H01L29/205—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys in different semiconductor regions, e.g. heterojunctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41708—Emitter or collector electrodes for bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41758—Source or drain electrodes for field effect devices for lateral devices with structured layout for source or drain region, i.e. the source or drain region having cellular, interdigitated or ring structure or being curved or angular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42304—Base electrodes for bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/45—Ohmic electrodes

- H01L29/452—Ohmic electrodes on AIII-BV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/73—Bipolar junction transistors

- H01L29/737—Hetero-junction transistors

- H01L29/7371—Vertical transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/05124—Aluminium [Al] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05144—Gold [Au] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05166—Titanium [Ti] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05171—Chromium [Cr] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/0518—Molybdenum [Mo] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05181—Tantalum [Ta] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05184—Tungsten [W] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

- H01L2224/05572—Disposition the external layer being disposed in a recess of the surface the external layer extending out of an opening

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05663—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05666—Titanium [Ti] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05663—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05671—Chromium [Cr] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05663—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/0568—Molybdenum [Mo] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05663—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05681—Tantalum [Ta] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/056—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05663—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05684—Tungsten [W] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

- H01L2224/05686—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1301—Shape

- H01L2224/13012—Shape in top view

- H01L2224/13014—Shape in top view being circular or elliptic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13024—Disposition the bump connector being disposed on a redistribution layer on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13026—Disposition relative to the bonding area, e.g. bond pad, of the semiconductor or solid-state body

- H01L2224/13028—Disposition relative to the bonding area, e.g. bond pad, of the semiconductor or solid-state body the bump connector being disposed on at least two separate bonding areas, e.g. bond pads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13075—Plural core members

- H01L2224/1308—Plural core members being stacked

- H01L2224/13082—Two-layer arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13075—Plural core members

- H01L2224/1308—Plural core members being stacked

- H01L2224/13083—Three-layer arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/13111—Tin [Sn] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/13138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/13155—Nickel [Ni] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/1613—Disposition the bump connector connecting within a semiconductor or solid-state body, i.e. connecting two bonding areas on the same semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8138—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/81399—Material

- H01L2224/81486—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8138—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/81399—Material

- H01L2224/81486—Material with a principal constituent of the material being a non metallic, non metalloid inorganic material

- H01L2224/81487—Ceramics, e.g. crystalline carbides, nitrides or oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8138—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/81399—Material

- H01L2224/8149—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13051—Heterojunction bipolar transistor [HBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13063—Metal-Semiconductor Field-Effect Transistor [MESFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

Abstract

【課題】バンプと半導体層との熱膨張係数の相違に起因して発生する熱応力を低減させるとともに、配線層の層数を少なくすることが可能な半導体素子を提供する。【解決手段】トランジスタが、基板に設けられた半導体領域、及び3種類の端子電極を含み、少なくとも1つの端子電極は複数の導体パターンで構成された分離電極構造を持つ。分離電極構造を持つ端子電極の上に、複数の導体パターンを相互に電気的に接続するバンプが配置されている。トランジスタの半導体領域とバンプとの間に、高融点金属を含む金属材料からなる応力緩和層が配置されている。導体パターンとバンプとの間には、複数の導体パターンを相互に接続する電流経路が配置されていない。【選択図】図2

Description

本発明は、半導体素子に関する。

バンプを介して半導体素子を実装基板に実装し、バンプを放熱経路として利用する技術が公知である(特許文献1、2)。

特許文献1に開示された半導体装置においては、化合物半導体基板に形成された複数の単位トランジスタを並列接続することによりヘテロ接合バイポーラトランジスタ(HBT)が構成されている。複数の単位トランジスタのエミッタにバンプが電気的に接続されている。複数の単位トランジスタは第1の方向に配列され、バンプは第1の方向に延伸して配置されている。

特許文献2に開示された半導体装置においては、配線層に含まれる電流経路が導電性ピラーに接続されている。導電性ピラーは、HBTのエミッタに接続されている。

特許文献1に開示された複数の単位トランジスタの各々は、コレクタ、ベース、及びエミッタの三端子を有する。複数の単位トランジスタのコレクタ同士、ベース同士、及びエミッタ同士が、それぞれまとめ配線で接続される。三端子をそれぞれまとめ配線に接続するために配線を交差させる必要があるため、少なくとも2層の配線層が必要である。

特許文献2に開示された半導体装置においては、導電性ピラー(バンプ)と半導体層との熱膨張係数の相違により半導体層に熱応力が発生する。この熱応力により、半導体装置の信頼性の低下、電気的特性のばらつき、電気的特性の不良等が発生しやすくなる。

本発明の目的は、バンプと半導体層との熱膨張係数の相違に起因して発生する熱応力を低減させるとともに、配線層の層数を少なくすることが可能な半導体素子を提供することである。

本発明の第1の観点による半導体素子は、

基板に設けられた半導体領域、及び3種類の端子電極を含み、少なくとも1つの前記端子電極は複数の導体パターンで構成された分離電極構造を持つトランジスタと、

前記分離電極構造を持つ前記端子電極の上に配置され、複数の前記導体パターンを相互に電気的に接続するバンプと、

前記トランジスタの半導体領域と前記バンプとの間に配置され、高融点金属を含む金属材料からなる応力緩和層と

を有し、

前記導体パターンと前記バンプとの間には、複数の前記導体パターンを相互に接続する電流経路が配置されていない。

基板に設けられた半導体領域、及び3種類の端子電極を含み、少なくとも1つの前記端子電極は複数の導体パターンで構成された分離電極構造を持つトランジスタと、

前記分離電極構造を持つ前記端子電極の上に配置され、複数の前記導体パターンを相互に電気的に接続するバンプと、

前記トランジスタの半導体領域と前記バンプとの間に配置され、高融点金属を含む金属材料からなる応力緩和層と

を有し、

前記導体パターンと前記バンプとの間には、複数の前記導体パターンを相互に接続する電流経路が配置されていない。

応力緩和層を配置することにより、トランジスタの半導体領域に発生する熱応力を低減させることができる。分離電極構造を持つ端子電極の複数の導体パターンがバンプによって相互に電気的に接続されているため、複数の導体パターンを相互に接続する配線層を配置する必要がない。このため、配線層の層数を少なくすることが可能になる。

本発明の第2の観点による半導体素子は、第1の観点による半導体素子の構成に加えて、

前記応力緩和層は、W、Mo、Ta、及びCrからなる群より選択された少なくとも1つの高融点金属を含み、その厚さが100nm以上であるという特徴を有する。

前記応力緩和層は、W、Mo、Ta、及びCrからなる群より選択された少なくとも1つの高融点金属を含み、その厚さが100nm以上であるという特徴を有する。

応力緩和層をこのような構成にすることにより、熱応力を低減させる十分な効果が得られる。

本発明の第3の観点による半導体素子は、第1の観点による半導体素子の構成に加えて、

前記応力緩和層は、高融点金属としてTiを含み、その厚さが300nm以上であるという特徴を有する。

前記応力緩和層は、高融点金属としてTiを含み、その厚さが300nm以上であるという特徴を有する。

応力緩和層をこのような構成にすることにより、熱応力を低減させる十分な効果が得られる。

本発明の第4の観点による半導体素子は、第1から第3のまでの観点による半導体素子の構成に加えて、

前記応力緩和層は、前記バンプの下地層として形成され、前記バンプの平面形状と同一の平面形状を有するという特徴を有する。

前記応力緩和層は、前記バンプの下地層として形成され、前記バンプの平面形状と同一の平面形状を有するという特徴を有する。

バンプの下地層となる応力緩和層が、バンプと半導体領域との間に配置されることにより、バンプの熱膨張率と半導体領域の熱膨張率との差に起因して半導体領域に発生する熱応力を低減させる。

本発明の第5の観点による半導体素子は、第1から第3のまでの観点による半導体素子の構成に加えて、

前記応力緩和層は、前記分離電極構造を持つ前記端子電極の一部を構成するという特徴を有する。

前記応力緩和層は、前記分離電極構造を持つ前記端子電極の一部を構成するという特徴を有する。

端子電極が応力緩和層として機能することにより、半導体領域に発生する熱応力を低減させることができる。

本発明の第6の観点による半導体素子は、第1から第5のまでの観点による半導体素子の構成に加えて、

さらに、前記端子電極と前記バンプとの間に配置された1つの配線層を有し、

前記バンプ及び前記導体パターンは、前記配線層に含まれる配線に、他の配線層を介することなく接続されているという特徴を有する。

さらに、前記端子電極と前記バンプとの間に配置された1つの配線層を有し、

前記バンプ及び前記導体パターンは、前記配線層に含まれる配線に、他の配線層を介することなく接続されているという特徴を有する。

1層の配線層を介してバンプと複数の導体パターンとが接続され、複数の導体パターンがバンプによって相互に接続されるため、2層以上の配線層を配置する必要がない。これにより、製造コストの低減を図ることができる。

本発明の第7の観点による半導体素子は、第1から第6のまでの観点による半導体素子の構成に加えて、

前記トランジスタは、コレクタ層、ベース層、エミッタ層を含むバイポーラトランジスタであり、

3つの前記端子電極は、それぞれ前記コレクタ層、前記ベース層、及び前記エミッタ層に接続されたコレクタ電極、ベース電極、及びエミッタ電極を含むという特徴を有する。

前記トランジスタは、コレクタ層、ベース層、エミッタ層を含むバイポーラトランジスタであり、

3つの前記端子電極は、それぞれ前記コレクタ層、前記ベース層、及び前記エミッタ層に接続されたコレクタ電極、ベース電極、及びエミッタ電極を含むという特徴を有する。

バイポーラトランジスタの半導体領域に発生する熱応力を低減させることにより、バイポーラトランジスタの信頼性の低下、電気的特性のばらつき等を抑制することができる。

本発明の第8の観点による半導体素子は、第7の観点による半導体素子の構成に加えて、

平面視において、前記バンプの内側に前記エミッタ層が配置されているという特徴を有する。

平面視において、前記バンプの内側に前記エミッタ層が配置されているという特徴を有する。

エミッタ層で発生する熱を、バンプを通して効率的に外部に放熱することができる。バンプと半導体領域との間に応力緩和層が配置されているため、平面視においてバンプの内側にエミッタ層が配置されている場合であっても、エミッタ層に発生する熱応力が低減されるため、信頼性の低下、特性のばらつき等を抑制することができる。

本発明の第9の観点による半導体素子は、第1から第6までの観点による半導体素子の構成に加えて、

前記トランジスタは、前記基板の表層部に画定された活性領域を含む電界効果トランジスタであり、

3つの前記端子電極は、それぞれ前記活性領域の上に配置されたソース電極、ドレイン電極、及びゲート電極を含むという特徴を有する。

前記トランジスタは、前記基板の表層部に画定された活性領域を含む電界効果トランジスタであり、

3つの前記端子電極は、それぞれ前記活性領域の上に配置されたソース電極、ドレイン電極、及びゲート電極を含むという特徴を有する。

電界効果トランジスタの半導体領域に発生する熱応力を低減させることにより、電界効果トランジスタの信頼性の低下、電気的特性のばらつき等を抑制することができる。

本発明の第10の観点による半導体素子は、第9の観点による半導体素子の構成に加えて、

平面視において、前記ゲート電極と前記活性領域とが重なる領域が前記バンプの内側に配置されているという特徴を有する。

平面視において、前記ゲート電極と前記活性領域とが重なる領域が前記バンプの内側に配置されているという特徴を有する。

ゲート電極と活性領域とが重なる動作領域で発生する熱を、バンプを通して効率的に外部に放熱することができる。バンプと半導体領域との間に応力緩和層が配置されているため、平面視においてバンプの内側に動作領域が配置されている場合であっても、動作領域に発生する熱応力が低減されるため、信頼性の低下、特性のばらつき等を抑制することができる。

応力緩和層を配置することにより、トランジスタの半導体領域に発生する熱応力を低減させることができる。分離電極構造を持つ端子電極の複数の導体パターンがバンプによって相互に電気的に接続されているため、複数の導体パターンを相互に接続する配線層を配置する必要がない。このため、配線層の層数を少なくすることが可能になる。

[第1実施例]

図1、図2、及び図3を参照して、第1実施例による半導体素子について説明する。

図1は、第1実施例による半導体素子の平面図である。半導体素子の基板の上面をxy面とし、上面の法線方向をx軸の正方向とするxyz直交座標系を定義する。第1実施例による半導体素子は、トランジスタ及びトランジスタに接続された配線、及びバンプを含む。このトランジスタは、相互に並列に接続された2つの単位トランジスタ21を含む。

図1、図2、及び図3を参照して、第1実施例による半導体素子について説明する。

図1は、第1実施例による半導体素子の平面図である。半導体素子の基板の上面をxy面とし、上面の法線方向をx軸の正方向とするxyz直交座標系を定義する。第1実施例による半導体素子は、トランジスタ及びトランジスタに接続された配線、及びバンプを含む。このトランジスタは、相互に並列に接続された2つの単位トランジスタ21を含む。

2つの単位トランジスタ21は、x軸方向に並んで配置されている。単位トランジスタ21の各々は、エミッタ層、ベース層、及びコレクタ層、及びこれらにそれぞれ接続されたエミッタ電極E0、ベース電極B0、及びコレクタ電極C0を含む。図1において、エミッタ電極E0、ベース電極B0、及びコレクタ電極C0にハッチングを付している。

エミッタ電極E0の各々は、y軸方向に長い長方形の平面形状を有する。ベース電極B0が、x軸方向に関して正及び負の側、及びy軸に関して正の側の三方向からエミッタ電極E0の各々を取り囲むように配置されている。x軸方向に関してベース電極B0の両側にそれぞれコレクタ電極C0が配置されている。2つの単位トランジスタ21のベース電極B0の間に配置されたコレクタ電極C0は、2つの単位トランジスタ21で共用される。

実施例による半導体素子は、1層目の配線層に配置されたエミッタ配線E1、コレクタ配線C1、及びベース配線B1を含む。1層目のエミッタ配線E1は、2つのエミッタ電極E0にそれぞれ重なるように配置された2つの孤立した導体パターンで構成され、導体パターンの各々は、その下のエミッタ電極E0に電気的に接続されている。

1層目のコレクタ配線C1は櫛歯型の平面形状を有する。1層目のコレクタ配線C1の櫛歯部分が、それぞれコレクタ電極C0と重なるように配置されている。コレクタ電極C0を構成する複数の導体パターンは、1層目のコレクタ配線C1によって相互に接続されている。

1層目のベース配線B1は、2つの単位トランジスタ21の各々のベース電極B0を相互に接続する。

バンプ30が、1層目のエミッタ配線E1の2つの導体パターンと重なるように配置されている。バンプ30は、1層目のエミッタ配線E1の2つの導体パターンに電気的に接続されている。2つの単位トランジスタ21のエミッタ電極E0を構成する2つの導体パターンは、バンプ30により相互に電気的に接続されている。

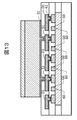

図2は、図1の一点鎖線2−2における断面図である。半絶縁性のGaAsからなる基板20の上にサブコレクタ層23が配置されている。サブコレクタ層23は、高濃度のn型GaAsで形成され、その厚さは例えば0.5μmである。サブコレクタ層23の一部は、イオン注入により絶縁化されたアイソレーション領域23aとされている。サブコレクタ層23は、2つの単位トランジスタ21で共用される。

サブコレクタ層23の上に、単位トランジスタ21ごとにコレクタ層24、ベース層25、及びエミッタ層26が順番に積層されている。コレクタ層24は、n型GaAsで形成され、その厚さは例えば1μmである。ベース層25はp型GaAsで形成され、その厚さは例えば100nmである。ベース層25とコレクタ層24とは、同一の平面形状を有し、コレクタメサを構成する。

エミッタ層26は、ベース層25の一部の領域の上に配置されている。エミッタ層26は、例えば、ベース層25側から順番に配置された厚さ30nm〜40nmのn型InGaP層、厚さ100nmの高濃度のn型GaAs層、及び厚さ100nmの高濃度のn型InGaAs層を含む。高濃度のn型InGaAs層は、その上に配置されるエミッタ電極E0とオーミックコンタクトを取るためのものである。

サブコレクタ層23の上に、コレクタ電極C0が配置されており、サブコレクタ層23にオーミックに接続されている。コレクタ電極C0は、3個の導体パターンで構成されており、3個の導体パターンは、x軸方向に関してコレクタメサの間、及び2つのコレクタメサの外側に配置されている。コレクタ電極C0は、例えば厚さ60nmのAuGe膜、厚さ10nmのNi膜、及び厚さ200nmのAu膜を積層することにより形成される。

ベース電極B0がベース層25の上に配置されており、ベース層25にオーミックに接続されている。図2に示した断面において、ベース電極B0はエミッタ層26の両側に配置されている。ベース電極B0は、例えば厚さ50nmのTi膜、厚さ50nmのPt膜、厚さ200nmのAu膜を積層することにより形成される。

エミッタ層26の上にエミッタ電極E0が配置されている。エミッタ電極E0として、例えば厚さ50nmのTi膜が用いられる。

単位トランジスタ21を覆うように、絶縁膜27が配置されている。絶縁膜27として、例えばSiN膜とポリイミド等の樹脂膜との積層膜が用いられる。絶縁膜27の上面は平坦化されている。なお、絶縁膜27をSiN膜の単層で構成してもよい。

絶縁膜27の上に、1層目のエミッタ配線E1及びコレクタ配線C1が配置されている。エミッタ配線E1は、絶縁膜27に設けられた開口を経由してエミッタ電極E0に電気的に接続されている。1層目のコレクタ配線C1は、絶縁膜27に設けられた開口を経由してコレクタ電極C0に電気的に接続されている。図2に示した断面には表れていないが、絶縁膜27の上に、1層目のベース配線B1(図1)も配置されている。ベース配線B1は、絶縁膜27に設けられた開口を経由してベース電極B0に電気的に接続されている。

1層目のエミッタ配線E1、コレクタ配線C1、及びベース配線B1は、例えば厚さ50nmのTi膜と、その上に配置された厚さ1μmのAu膜との2層構造を有する。

1層目のエミッタ配線E1、コレクタ配線C1、及びベース配線B1を覆うように、絶縁膜27の上に、上層の絶縁膜28が配置されている。絶縁膜28として、例えばSiN膜、またはSiN膜と樹脂膜との積層膜が用いられる。

絶縁膜28の上に、バンプ30が配置されている。バンプ30は、絶縁膜28に1層目のエミッタ配線E1ごとに設けられた開口を経由してエミッタ配線E1に電気的に接続されている。バンプ30は、メタルポスト32、及びその上のハンダ層33を含む。バンプ30の下に、下地層としてアンダーバンプメタル層31が配置されている。

アンダーバンプメタル層31は、例えばTiで形成される。メタルポスト32として、例えば厚さ50μmのCu膜が用いられる。ハンダ層33として、例えば厚さ30μmのSn膜が用いられる。メタルポスト32とハンダ層33との間に、Ni等からなる相互拡散防止用のバリアメタル層を配置してもよい。

次に、第1実施例による半導体素子の構造を採用することにより得られる優れた効果について、図3に示した比較例による半導体素子と比較しながら説明する。

図3は、比較例による半導体素子の概略平面図である。複数の単位トランジスタを並列に接続するために、コレクタまとめ配線CC、エミッタまとめ配線EC、及びベースまとめ配線BCが配置されている。コレクタまとめ配線CCは複数のコレクタ電極C0を相互に接続する。エミッタまとめ配線ECは複数のエミッタ電極E0を相互に接続する。ベースまとめ配線BCは複数のベース電極B0を相互に接続する。3種類の電極を、それぞれ対応するまとめ配線に接続するためには、通常、少なくとも2つの配線を交差させなければならない。例えば、図3に示した比較例では、エミッタ電極E0をエミッタまとめ配線ECに接続するための配線が、コレクタまとめ配線CCと交差している。このため、複数の単位トランジスタ21を並列に接続するために、少なくとも2層の配線層が必要である。

第1実施例では、図1に示したように、1層目のコレクタ配線C1及びベース配線B1が、それぞれコレクタまとめ配線及びベースまとめ配線としての役割を担う。1層目のエミッタ配線E1は、エミッタ電極E0の2つの導体パターンごとに配置されており、エミッタまとめ配線としての役割を持たない。第1実施例では、バンプ30がエミッタ電極E0の2つの導体パターンを相互に接続しており、エミッタまとめ配線としての役割を担う。このように、バンプ30が、本来の外部接続用の端子としての機能の他に、エミッタ電極E0の2つの導体パターンを相互に接続するまとめ配線としての機能を持つ。このため、図3に示したコレクタまとめ配線CCと交差する配線を設ける必要がない。

上述のように、第1実施例では、必ずしも2層の配線層を設ける必要がないため、比較例(図3)に比べて配線層の層数を減らすことが可能になる。配線層の層数を減らすことにより、製造コストの低減を図ることができる。

次に、アンダーバンプメタル層31(図2)を配置することにより得られる優れた効果について説明する。GaAs、InGaAs等の半導体からなるエミッタ層26、ベース層25、及びコレクタ層24の熱膨張率と、CuやSn等からなるメタルポスト32及びハンダ層33の熱膨張率との差に起因して、エミッタ層26等の半導体層に熱応力が発生する。例えば、GaAsの熱膨張率が約6ppm/℃、InGaPの熱膨張率が5ppm/℃以上6ppm/℃以下の範囲内であるのに対し、Cuの熱膨張率は17ppm/℃、Snの熱膨張率は22ppm/℃である。また、半導体素子を実装するプリント回路板の熱膨張率も、一般的に15ppm/℃以上20ppm/℃以下の範囲内である。

アンダーバンプメタル層31に用いられているTiの熱膨張率は8.6ppm/℃であり、半導体層の熱膨張率に近い。このため、アンダーバンプメタル層31が、半導体層に発生する熱応力を緩和する応力緩和層として機能する。

半導体層に、熱応力による歪みが発生すると、高温での通電動作時にバイポーラトランジスタの電流増幅率が低下してしまう。第1実施例では、半導体層に発生する熱応力が低減されるため、電流増幅率の低下を抑制することができる。

さらに、第1実施例では、発熱源となるエミッタ層26等がバンプ30の真下に配置されている。発熱源からバンプ30までの熱伝達経路が短くなるため、バンプ30を介した良好な放熱特性を確保することができる。この結果、バイポーラトランジスタの温度上昇による高周波特性の低下を抑制することができる。

次に、第1実施例の第1変形例について説明する。第1実施例ではアンダーバンプメタル層31(図2)にTiを用いたが、その他の高融点金属、高融点金属を含む化合物、または高融点金属を含む合金を用いてもよい。高融点金属として、Tiの他にTa、Mo、Cr、Wが挙げられる。高融点金属を含む化合物として、TaN、TiN等の高融点金属の窒化物、MoSi、WSi等の高融点金属のシリサイドが挙げられる。高融点金属を含む合金として、TiW等が挙げられる。

アンダーバンプメタル層31として、SiN等の下地の絶縁膜28(図1)に対して接着性のよいTi膜と、その上に配置されたW等の応力緩和作用の高い膜とを含む多層構造を採用してもよい。このように、アンダーバンプメタル層31を、複数の金属膜からなる積層構造としてもよい。