JP6619210B2 - 半導体装置を形成する方法および半導体装置 - Google Patents

半導体装置を形成する方法および半導体装置 Download PDFInfo

- Publication number

- JP6619210B2 JP6619210B2 JP2015221920A JP2015221920A JP6619210B2 JP 6619210 B2 JP6619210 B2 JP 6619210B2 JP 2015221920 A JP2015221920 A JP 2015221920A JP 2015221920 A JP2015221920 A JP 2015221920A JP 6619210 B2 JP6619210 B2 JP 6619210B2

- Authority

- JP

- Japan

- Prior art keywords

- carbon

- semiconductor substrate

- protons

- concentration

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 227

- 238000000034 method Methods 0.000 title claims description 104

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 246

- 229910052799 carbon Inorganic materials 0.000 claims description 246

- 239000000758 substrate Substances 0.000 claims description 125

- 238000009792 diffusion process Methods 0.000 claims description 31

- 238000005496 tempering Methods 0.000 claims description 24

- 238000009826 distribution Methods 0.000 claims description 20

- 238000005259 measurement Methods 0.000 claims description 13

- 239000001257 hydrogen Substances 0.000 claims description 12

- 229910052739 hydrogen Inorganic materials 0.000 claims description 12

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 11

- 239000013078 crystal Substances 0.000 claims description 9

- 238000000151 deposition Methods 0.000 claims description 8

- 238000004519 manufacturing process Methods 0.000 claims description 8

- 230000008021 deposition Effects 0.000 claims description 7

- 238000001773 deep-level transient spectroscopy Methods 0.000 claims description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 5

- 239000001301 oxygen Substances 0.000 claims description 5

- 229910052760 oxygen Inorganic materials 0.000 claims description 5

- 239000001307 helium Substances 0.000 claims description 4

- 229910052734 helium Inorganic materials 0.000 claims description 4

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims description 4

- 239000002245 particle Substances 0.000 claims description 4

- 238000010521 absorption reaction Methods 0.000 claims description 3

- 235000012431 wafers Nutrition 0.000 description 42

- 238000002513 implantation Methods 0.000 description 30

- 230000008569 process Effects 0.000 description 25

- 210000000746 body region Anatomy 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 15

- 230000006870 function Effects 0.000 description 11

- 229910052710 silicon Inorganic materials 0.000 description 11

- 239000010703 silicon Substances 0.000 description 11

- 238000000137 annealing Methods 0.000 description 7

- 239000007943 implant Substances 0.000 description 7

- 238000002347 injection Methods 0.000 description 7

- 239000007924 injection Substances 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 230000000694 effects Effects 0.000 description 6

- -1 aluminum ions Chemical class 0.000 description 5

- 125000004432 carbon atom Chemical group C* 0.000 description 5

- 230000001419 dependent effect Effects 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000012360 testing method Methods 0.000 description 4

- 125000004429 atom Chemical group 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 238000010348 incorporation Methods 0.000 description 3

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 3

- 229910010271 silicon carbide Inorganic materials 0.000 description 3

- 239000007787 solid Substances 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910002601 GaN Inorganic materials 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 238000004590 computer program Methods 0.000 description 2

- 238000013500 data storage Methods 0.000 description 2

- 238000000407 epitaxy Methods 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- 230000008018 melting Effects 0.000 description 2

- 238000002844 melting Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 241000270666 Testudines Species 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- JJWKPURADFRFRB-UHFFFAOYSA-N carbonyl sulfide Chemical compound O=C=S JJWKPURADFRFRB-UHFFFAOYSA-N 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 230000004807 localization Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- IJGRMHOSHXDMSA-UHFFFAOYSA-N nitrogen Substances N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- 238000009377 nuclear transmutation Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000010349 pulsation Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000005204 segregation Methods 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

- 241000894007 species Species 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 230000000153 supplemental effect Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/12—Measuring as part of the manufacturing process for structural parameters, e.g. thickness, line width, refractive index, temperature, warp, bond strength, defects, optical inspection, electrical measurement of structural dimensions, metallurgic measurement of diffusions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/20—Sequence of activities consisting of a plurality of measurements, corrections, marking or sorting steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/36—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the concentration or distribution of impurities in the bulk material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/14—Measuring as part of the manufacturing process for electrical parameters, e.g. resistance, deep-levels, CV, diffusions by electrical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- High Energy & Nuclear Physics (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Bipolar Transistors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

また、本願は以下に記載する態様を含む。

(態様1)

半導体基板中に規定ドーズ量の陽子を注入する工程(110)と規定温度プロフィルに基づき前記半導体基板を焼き戻しする工程(120)とを含む半導体装置を形成する方法(100)であって、

前記規定ドーズ量の陽子と前記規定温度プロフィルのうちの少なくとも1つは、前記半導体基板の少なくとも一部分内の炭素濃度に関する情報を示す炭素関連パラメータに依存して選択される、方法。

(態様2)

前記半導体基板の少なくとも一部分内の前記炭素濃度は1×10 15 cm −3 より高い、態様1に記載の方法。

(態様3)

前記規定ドーズ量の陽子を注入する(110)前に前記半導体基板の少なくとも一部分中に炭素を取り込む工程をさらに含む態様1または2に記載の方法。

(態様4)

前記炭素を取り込む工程は前記半導体基板の少なくとも一部分中に炭素を注入または拡散する工程を含む、態様3に記載の方法。

(態様5)

前記炭素を取り込む工程は前記半導体基板の少なくとも一部分中に炭素を拡散する工程を含み、前記半導体基板中の室温における炭素の溶解度より多くの炭素が前記拡散処理中に供給される、態様3に記載の方法。

(態様6)

規定拡散温度プロフィルに従って前記半導体基板を焼き戻しすることにより前記半導体基板から炭素を拡散する工程をさらに含む態様1〜5のいずれか一項に記載の方法。

(態様7)

結晶成長中またはエピタキシャル層の堆積中に規定炭素分布で前記半導体基板の前記少なくとも一部分内に前記炭素を取り込む工程をさらに含む態様1または2に記載の方法。

(態様8)

前記規定ドーズ量の陽子は1×10 14 cm −2 より高い、態様1〜7のいずれか一項に記載の方法。

(態様9)

前記規定温度プロフィルは500℃未満の最大温度を含む、態様1〜8のいずれか一項に記載の方法。

(態様10)

前記半導体装置の後続の製造工程は前記規定ドーズ量の陽子の注入(110)後に500℃未満の温度で行われる、態様1〜9のいずれか一項に記載の方法。

(態様11)

前記半導体基板の少なくとも一部分の炭素濃度または前記形成される半導体装置の前記半導体基板と共に製造される別の半導体基板の少なくとも一部分の炭素濃度を測定する工程をさらに含む態様1〜10のいずれか一項に記載の方法。

(態様12)

規定深さ分布を有する格子間半導体原子を生成するために規定エネルギー分布で前記半導体基板内に、電子、アルファ粒子、ヘリウムまたはさらなる陽子を注入する工程をさらに含む態様1〜11のいずれか一項に記載の方法。

(態様13)

前記規定ドーズ量の陽子は、前記半導体基板の前記少なくとも一部分内に規定濃度の格子間炭素を生成するように半導体基板内に注入される(110)、態様1〜12のいずれか一項に記載の方法。

(態様14)

前記半導体基板中に前記規定ドーズ量の陽子を注入する工程(110)は前記形成される半導体装置のドリフト層領域中に規定ドーズ量の陽子を注入する工程を含む、態様1〜13のいずれか一項に記載の方法。

(態様15)

前記形成される半導体装置のフィールドストップ層領域内に炭素を注入または拡散する工程であって、前記ドリフト層領域内の平均炭素濃度が前記フィールドストップ層領域内の平均炭素濃度より低くなるように注入または拡散する工程をさらに含む態様1〜14のいずれか一項に記載の方法。

(態様16)

前記炭素関連パラメータは深準位過渡分光法により測定されたCiOi濃度または赤外線計測により測定された吸収係数である、態様1〜15のいずれか一項に記載の方法。

(態様17)

エミッタまたはソース端子(210)とコレクタまたはドレイン端子(220)とを含む少なくとも1つのトランジスタ構造を含む半導体装置(200)であって、

前記エミッタまたはソース端子(210)と前記コレクタまたはドレイン端子(220)間に位置する半導体基板領域(240)内の炭素濃度(230)が前記エミッタまたはソース端子(210)と前記コレクタまたはドレイン端子(220)間で変化する、半導体装置。

(態様18)

前記トランジスタ構造は前記エミッタまたはソース端子(210)と前記コレクタまたはドレイン端子(220)間に位置するドリフト層(370、470)を含み、

前記トランジスタ構造は前記ドリフト層(370、470)と前記コレクタまたはドレイン端子(220)間に位置するフィールドストップ層を含み、

前記フィールドストップ層は前記ドリフト層(370、470)の平均炭素濃度の少なくとも2倍の平均炭素濃度を含む、態様17に記載の半導体装置。

(態様19)

前記トランジスタ構造は、コレクタ層(360、460)、ドリフト層(370、470)、複数のボディ領域(380、480)、複数のソース領域(385、485)および複数のゲート(390、490)を含む半導体構造を含む絶縁ゲートバイポーラトランジスタ配置であり、

前記複数のソース領域(385、485)および前記ドリフト層(370、470)は少なくとも第1の導電型を主に含み、

前記複数のボディ領域(380、480)および前記コレクタ層(360、460)は少なくとも第2の導電型を主に含み、

前記複数のゲート(390、490)は、前記ゲートが前記ボディ領域(380、480)を介し前記ソース領域(385、485)と前記ドリフト層(370、470)との間に導電チャネルを引き起こすことができるように配置される、態様17または18に記載の半導体装置。

(態様20)

前記半導体装置の半導体基板は200μm未満の厚さを含む、態様17〜19のいずれか一項に記載の半導体装置。

(態様21)

半導体装置を形成する方法(600)であって、

第1の半導体ウェハ中に第1の規定ドーズ量の陽子を注入する工程(610)と、

第1の規定温度プロフィルに従って前記第1の半導体ウェハを焼き戻しする工程(620)であって、前記第1の規定ドーズ量の陽子と前記第1の規定温度プロフィルのうちの少なくとも1つは、前記第1の半導体ウェハの少なくとも一部分内の第1の炭素濃度に関する情報を示す炭素関連パラメータに依存して選択される、工程(620)と、

第2の半導体ウェハ中に第2の規定ドーズ量の陽子を注入する工程(630)と、

第2の規定温度プロフィルに従って前記第2の半導体ウェハを焼き戻しする工程(630)であって、前記第2の規定ドーズ量の陽子と前記第2の規定温度プロフィルのうちの少なくとも1つは、前記第2の半導体ウェハの少なくとも一部分内の第2の炭素濃度に関する情報を示す炭素関連パラメータに依存して選択され、前記第1の炭素濃度は前記第2の炭素濃度と異なる、工程(630)とを含む方法。

110 注入工程

120 焼き戻し工程

200 半導体装置

210 エミッタまたはソース端子

220 コレクタまたはドレイン端子

230 炭素濃度

240 半導体基板

350 絶縁ゲートバイポーラトランジスタ配置

360 コレクタ層

370 ドリフト層

380 ボディ領域

385 ソース領域

390 ゲート

392 導電チャネル

394 絶縁層

400 メサ絶縁ゲートバイポーラトランジスタ構造

460 コレクタ層

462 裏側コレクタ金属層

464 電気コンタクト

470 ドリフト層

480 ボディ領域

485 ソース領域

486 ソース金属層

487 電気的コンタクト

490 ゲート

492 ゲート配線

510 陽子フィールドストッププロファイル(従来)

511 炭素分布(従来)

520 フィールドストッププロファイル

521 炭素分布(提案)

530 ドリフト層

540 フィールドストップ層

550 コレクタ層

600 方法

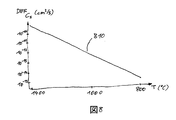

710 炭素の溶解度限界

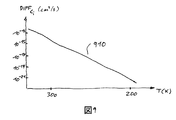

810 置換型炭素の拡散定数

910 格子間炭素の拡散定数

Claims (18)

- 半導体装置を形成する方法(100)であって、

半導体基板であってその少なくとも一部分内の炭素濃度を有する半導体基板を供給する工程と、

前記半導体基板の前記少なくとも一部分内の前記炭素濃度に関する情報を示す測定を実行することによって、炭素関連パラメータを決定する工程と、

半導体基板中に規定ドーズ量の陽子を注入して、規定の濃度の格子間炭素(Ci)を前記半導体基板の少なくとも一部分に生成する工程(110)であって、前記格子間炭素(Ci)は、前記半導体基板内で利用可能な酸素及び水素とともに、CiOi−H複合体又はCiO2i−H複合体の内の少なくとも1つを形成する工程と、

規定温度プロフィルに基づき前記半導体基板を焼き戻しする工程(120)とを含み、

前記規定ドーズ量の陽子と前記規定温度プロフィルのうちの少なくとも1つは、前記炭素関連パラメータに依存し、前記CiOi−H複合体は非常に低い拡散定数を有する、方法。 - 前記半導体基板の少なくとも一部分内の前記炭素濃度は1×1015cm−3より高い、請求項1に記載の方法。

- 前記規定ドーズ量の陽子を注入する(110)前に前記半導体基板の少なくとも一部分中に炭素を取り込む工程をさらに含む請求項1または2に記載の方法。

- 前記炭素を取り込む工程は前記半導体基板の少なくとも一部分中に炭素を注入または拡散する工程を含む、請求項3に記載の方法。

- 前記炭素を取り込む工程は前記半導体基板の少なくとも一部分中に炭素を拡散する工程を含み、前記半導体基板中の室温における炭素の溶解度より多くの炭素が前記拡散処理中に供給される、請求項3に記載の方法。

- 規定拡散温度プロフィルに従って前記半導体基板を焼き戻しすることにより前記半導体基板から炭素を拡散する工程をさらに含む請求項1から5のいずれか一項に記載の方法。

- 結晶成長中またはエピタキシャル層の堆積中に規定炭素分布で前記半導体基板の前記少なくとも一部分内に前記炭素を取り込む工程をさらに含む請求項1または2に記載の方法。

- 前記規定ドーズ量の陽子は1×1014cm−2より高い、請求項1から7のいずれか一項に記載の方法。

- 前記規定温度プロフィルは500℃未満の最大温度を含む、請求項1から8のいずれか一項に記載の方法。

- 半導体装置を形成する前記方法における、前記規定ドーズ量の陽子の注入(110)後の後続の製造工程は500℃未満の温度で行われる、請求項1から9のいずれか一項に記載の方法。

- 前記炭素関連パラメータを決定する工程は、前記半導体基板の少なくとも一部分の格子間炭素濃度または前記形成される半導体装置の前記半導体基板と共に製造される別の半導体基板の少なくとも一部分の炭素濃度を測定する工程を含む請求項1から10のいずれか一項に記載の方法。

- 規定深さ分布を有する格子間半導体原子を生成するために規定エネルギー分布で前記半導体基板内に、電子、アルファ粒子、ヘリウムまたはさらなる陽子を注入する工程をさらに含む請求項1から11のいずれか一項に記載の方法。

- 前記規定ドーズ量の陽子は、前記半導体基板の前記少なくとも一部分内に規定濃度の格子間炭素を生成するように半導体基板内に注入される(110)、請求項1から12のいずれか一項に記載の方法。

- 前記半導体基板中に前記規定ドーズ量の陽子を注入する工程(110)は前記形成される半導体装置のドリフト層領域中に規定ドーズ量の陽子を注入する工程を含む、請求項1から13のいずれか一項に記載の方法。

- 前記形成される半導体装置のフィールドストップ層領域内に炭素を注入または拡散する工程であって、前記ドリフト層領域内の平均炭素濃度が前記フィールドストップ層領域内の平均炭素濃度より低くなるように注入または拡散する工程をさらに含む請求項14に記載の方法。

- 前記炭素関連パラメータはCiOi濃度または吸収係数であり、前記CiOi濃度は深準位過渡分光法による測定で決定され、前記吸収係数は赤外線計測により測定で決定される、請求項1から15のいずれか一項に記載の方法。

- 半導体装置を形成する方法(600)であって、該方法は、

第1の半導体ウェハであってその少なくとも一部分内の第1の炭素濃度を有する第1の半導体ウェハとを供給する工程と、

前記第1の半導体ウェハの前記少なくとも一部分内の前記第1の炭素濃度に関する情報を示す測定を実行することによって、第1の炭素関連パラメータを決定する工程と、

前記第1の半導体ウェハに第1の規定ドーズ量の陽子を注入する工程(610)と、

第1の規定温度プロフィルに基づき前記第1の半導体ウェハを焼き戻しする工程(620)と、

第2の半導体ウェハであってその少なくとも一部分内の第2の炭素濃度を有する第2の半導体ウェハとを供給する工程と、

前記第2の半導体ウェハの前記少なくとも一部分内の前記第2の炭素濃度に関する情報を示す測定を実行することによって、第2の炭素関連パラメータを決定する工程と、

前記第2の半導体ウェハに第2の規定ドーズ量の陽子を注入する工程(630)と、

第2の規定温度プロフィルに基づき前記半導体ウェハを焼き戻しする工程(640)とを含み、

前記第1の規定ドーズ量の陽子と前記第1の規定温度プロフィルのうちの少なくとも1つは、前記第1の炭素関連パラメータに依存し、前記第2の規定ドーズ量の陽子と前記第2の規定温度プロフィルのうちの少なくとも1つは、前記第2の炭素関連パラメータに依存し、

前記第1の炭素濃度は前記第2の炭素濃度と異なり、前記第1または第2の規定ドーズ量の陽子が1×10 14 cm −2 より高い、方法。 - 半導体装置を形成する方法(100)であって、

半導体基板であってその少なくとも一部分内の炭素濃度を有する半導体基板を供給する工程と、

前記半導体基板の前記少なくとも一部分内の前記炭素濃度に関する情報を示す測定を実行することによって、炭素関連パラメータを決定する工程と、

半導体基板中に規定ドーズ量の陽子を注入する工程(110)と、

規定温度プロフィルに基づき前記半導体基板を焼き戻しする工程(120)とを含み、

前記規定ドーズ量の陽子と前記規定温度プロフィルのうちの少なくとも1つは、前記炭素関連パラメータに依存し、それによって、前記陽子を前記半導体装置のフィールドストップ層領域に、ドリフト層領域内の平均格子間炭素濃度が前記フィールドストップ層領域内の平均格子間炭素濃度より低くなるように注入する、方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102014116666.3 | 2014-11-14 | ||

| DE102014116666.3A DE102014116666B4 (de) | 2014-11-14 | 2014-11-14 | Ein Verfahren zum Bilden eines Halbleiterbauelements |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017151202A Division JP6835682B2 (ja) | 2014-11-14 | 2017-08-04 | 半導体装置を形成する方法および半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016096338A JP2016096338A (ja) | 2016-05-26 |

| JP6619210B2 true JP6619210B2 (ja) | 2019-12-11 |

Family

ID=55855294

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015221920A Active JP6619210B2 (ja) | 2014-11-14 | 2015-11-12 | 半導体装置を形成する方法および半導体装置 |

| JP2017151202A Active JP6835682B2 (ja) | 2014-11-14 | 2017-08-04 | 半導体装置を形成する方法および半導体装置 |

| JP2021016333A Active JP7140860B2 (ja) | 2014-11-14 | 2021-02-04 | 半導体装置を形成する方法および半導体装置 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017151202A Active JP6835682B2 (ja) | 2014-11-14 | 2017-08-04 | 半導体装置を形成する方法および半導体装置 |

| JP2021016333A Active JP7140860B2 (ja) | 2014-11-14 | 2021-02-04 | 半導体装置を形成する方法および半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US9972704B2 (ja) |

| JP (3) | JP6619210B2 (ja) |

| CN (1) | CN105609407B (ja) |

| DE (1) | DE102014116666B4 (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105814694B (zh) | 2014-10-03 | 2019-03-08 | 富士电机株式会社 | 半导体装置以及半导体装置的制造方法 |

| DE102016112139B3 (de) * | 2016-07-01 | 2018-01-04 | Infineon Technologies Ag | Verfahren zum Reduzieren einer Verunreinigungskonzentration in einem Halbleiterkörper |

| WO2018060679A1 (en) * | 2016-09-30 | 2018-04-05 | Anvil Semiconductors Limited | 3c-sic igbt |

| JP6646876B2 (ja) * | 2016-12-15 | 2020-02-14 | 信越半導体株式会社 | シリコン結晶の炭素濃度測定方法 |

| JP7045005B2 (ja) * | 2017-05-19 | 2022-03-31 | 学校法人東北学院 | 半導体装置 |

| JP7052322B2 (ja) | 2017-11-28 | 2022-04-12 | 富士電機株式会社 | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 |

| JP6835291B2 (ja) | 2018-03-19 | 2021-02-24 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP6645546B1 (ja) * | 2018-09-03 | 2020-02-14 | 株式会社Sumco | シリコン試料の炭素濃度評価方法、シリコンウェーハ製造工程の評価方法、シリコンウェーハの製造方法およびシリコン単結晶インゴットの製造方法 |

| JP7067636B2 (ja) | 2018-10-18 | 2022-05-16 | 富士電機株式会社 | 半導体装置および製造方法 |

| WO2020100995A1 (ja) * | 2018-11-16 | 2020-05-22 | 富士電機株式会社 | 半導体装置および製造方法 |

| WO2020100997A1 (ja) | 2018-11-16 | 2020-05-22 | 富士電機株式会社 | 半導体装置および製造方法 |

| DE102018132236B4 (de) * | 2018-12-14 | 2023-04-27 | Infineon Technologies Ag | Leistungshalbleiterbauelement und Verfahren zu dessen Herstellung |

| CN112204710B (zh) | 2018-12-28 | 2024-07-09 | 富士电机株式会社 | 半导体装置及制造方法 |

| CN113169123A (zh) | 2019-05-16 | 2021-07-23 | 富士电机株式会社 | 半导体装置及半导体装置的制造方法 |

| JP7363336B2 (ja) * | 2019-10-11 | 2023-10-18 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| DE112020001029T5 (de) | 2019-10-11 | 2021-11-25 | Fuji Electric Co., Ltd. | Halbleitervorrichtung und herstellungsverfahren einer halbleitervorrichtung |

| WO2021125140A1 (ja) | 2019-12-17 | 2021-06-24 | 富士電機株式会社 | 半導体装置 |

| WO2021125064A1 (ja) | 2019-12-18 | 2021-06-24 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| DE112021000055T5 (de) | 2020-02-18 | 2022-06-30 | Fuji Electric Co., Ltd. | Halbleitervorrichtung |

| JP7361634B2 (ja) * | 2020-03-02 | 2023-10-16 | 三菱電機株式会社 | 半導体装置及び半導体装置の製造方法 |

| EP4123686A4 (en) * | 2020-03-17 | 2024-05-01 | Shin-Etsu Handotai Co., Ltd. | METHOD FOR CONTROLLING THE DONOR CONCENTRATION IN A SILICON SINGLE CRYSTAL SUBSTRATE |

| JP7264100B2 (ja) * | 2020-04-02 | 2023-04-25 | 信越半導体株式会社 | シリコン単結晶基板中のドナー濃度の制御方法 |

| JP7424512B2 (ja) * | 2020-11-17 | 2024-01-30 | 富士電機株式会社 | 半導体装置 |

| CN118160101A (zh) | 2022-05-30 | 2024-06-07 | 富士电机株式会社 | 半导体装置的制造方法 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS526074B1 (ja) | 1971-06-04 | 1977-02-18 | ||

| JPS4888882A (ja) * | 1972-02-22 | 1973-11-21 | ||

| JPS486675Y1 (ja) | 1972-04-13 | 1973-02-20 | ||

| GB0130018D0 (en) * | 2001-12-15 | 2002-02-06 | Koninkl Philips Electronics Nv | Semiconductor devices and their manufacture |

| DE102004004045B4 (de) * | 2004-01-27 | 2009-04-02 | Infineon Technologies Ag | Halbleiterbauelement mit temporärem Feldstoppbereich und Verfahren zu dessen Herstellung |

| JP4595450B2 (ja) * | 2004-09-02 | 2010-12-08 | 信越半導体株式会社 | 炭素ドープシリコン単結晶の製造方法 |

| JP4919700B2 (ja) | 2005-05-20 | 2012-04-18 | トヨタ自動車株式会社 | 半導体装置及びその製造方法 |

| WO2007005489A2 (en) * | 2005-07-05 | 2007-01-11 | Mattson Technology, Inc. | Method and system for determining optical properties of semiconductor wafers |

| JP4802019B2 (ja) | 2006-03-14 | 2011-10-26 | パナソニック株式会社 | 基板処理装置の温度制御方法、基板処理装置および基板処理システム |

| US8946811B2 (en) | 2006-07-10 | 2015-02-03 | Taiwan Semiconductor Manufacturing Company, Ltd. | Body-tied, strained-channel multi-gate device and methods of manufacturing same |

| JP5155536B2 (ja) * | 2006-07-28 | 2013-03-06 | 一般財団法人電力中央研究所 | SiC結晶の質を向上させる方法およびSiC半導体素子の製造方法 |

| JP5127235B2 (ja) * | 2007-01-10 | 2013-01-23 | 株式会社豊田中央研究所 | 半導体装置の製造方法 |

| JP2008177296A (ja) * | 2007-01-17 | 2008-07-31 | Toyota Central R&D Labs Inc | 半導体装置、pnダイオード、igbt、及びそれらの製造方法 |

| JP5320679B2 (ja) | 2007-02-28 | 2013-10-23 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| JP2009141304A (ja) * | 2007-11-13 | 2009-06-25 | Toyota Motor Corp | 半導体装置とその製造方法 |

| JP5374883B2 (ja) * | 2008-02-08 | 2013-12-25 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| EP2269864A4 (en) * | 2008-03-26 | 2015-04-22 | Ts Tech Co Ltd | STAINABLE VEHICLE SEAT |

| JP2010034330A (ja) | 2008-07-29 | 2010-02-12 | Sumco Corp | エピタキシャルウェーハおよびその製造方法 |

| JP5440693B2 (ja) | 2010-04-08 | 2014-03-12 | 信越半導体株式会社 | シリコンエピタキシャルウエーハ、シリコンエピタキシャルウエーハの製造方法、及び半導体素子又は集積回路の製造方法 |

| DE102011003439B4 (de) * | 2011-02-01 | 2014-03-06 | Globalfoundries Dresden Module One Llc & Co. Kg | Verfahren zur Durchlassstromerhöhung in Feldeffekttransistoren durch asymmetrische Konzentrationsprofile von Legierungssubstanzen einer Kanalhalbleiterlegierung und Halbleiterbauelement |

| GB201114365D0 (en) | 2011-08-22 | 2011-10-05 | Univ Surrey | Method of manufacture of an optoelectronic device and an optoelectronic device manufactured using the method |

| EP2790208B1 (en) * | 2012-03-19 | 2020-12-02 | Fuji Electric Co., Ltd. | Production method for semiconductor device |

| US9029243B2 (en) | 2012-10-08 | 2015-05-12 | Infineon Technologies Ag | Method for producing a semiconductor device and field-effect semiconductor device |

| JP6020342B2 (ja) | 2013-05-10 | 2016-11-02 | 信越半導体株式会社 | シリコンエピタキシャルウェーハ及びシリコンエピタキシャルウェーハの製造方法 |

| JP6271309B2 (ja) * | 2014-03-19 | 2018-01-31 | 株式会社東芝 | 半導体基板の製造方法、半導体基板および半導体装置 |

| JP6415946B2 (ja) * | 2014-11-26 | 2018-10-31 | 株式会社東芝 | 半導体装置の製造方法及び半導体装置 |

| DE102016112139B3 (de) * | 2016-07-01 | 2018-01-04 | Infineon Technologies Ag | Verfahren zum Reduzieren einer Verunreinigungskonzentration in einem Halbleiterkörper |

-

2014

- 2014-11-14 DE DE102014116666.3A patent/DE102014116666B4/de active Active

-

2015

- 2015-11-09 US US14/935,830 patent/US9972704B2/en active Active

- 2015-11-12 JP JP2015221920A patent/JP6619210B2/ja active Active

- 2015-11-13 CN CN201510776583.1A patent/CN105609407B/zh active Active

-

2017

- 2017-08-04 JP JP2017151202A patent/JP6835682B2/ja active Active

- 2017-12-04 US US15/831,247 patent/US10529838B2/en active Active

-

2021

- 2021-02-04 JP JP2021016333A patent/JP7140860B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| DE102014116666A1 (de) | 2016-05-19 |

| JP7140860B2 (ja) | 2022-09-21 |

| US9972704B2 (en) | 2018-05-15 |

| CN105609407B (zh) | 2019-04-30 |

| US20160141399A1 (en) | 2016-05-19 |

| US10529838B2 (en) | 2020-01-07 |

| CN105609407A (zh) | 2016-05-25 |

| JP2017228783A (ja) | 2017-12-28 |

| DE102014116666B4 (de) | 2022-04-21 |

| JP2021082829A (ja) | 2021-05-27 |

| US20180102423A1 (en) | 2018-04-12 |

| JP2016096338A (ja) | 2016-05-26 |

| JP6835682B2 (ja) | 2021-02-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6619210B2 (ja) | 半導体装置を形成する方法および半導体装置 | |

| JP2017228783A5 (ja) | ||

| JP6100307B2 (ja) | 半導体デバイスを形成するための方法および半導体デバイス | |

| TWI384555B (zh) | 改進SiC晶質之方法及SiC半導體元件 | |

| US8361893B2 (en) | Semiconductor device and substrate with chalcogen doped region | |

| US11972950B2 (en) | Semiconductor device and method for manufacturing | |

| US9887125B2 (en) | Method of manufacturing a semiconductor device comprising field stop zone | |

| CN106128953B (zh) | 制造半导体器件的方法与含氧相关热施主的半导体器件 | |

| JP2007266233A (ja) | 電力用半導体装置及びその製造方法 | |

| JP6109432B2 (ja) | 電力用半導体装置の製造方法 | |

| JP2017063187A5 (ja) | ||

| JPWO2016203545A1 (ja) | 半導体装置の製造方法 | |

| JP5528515B2 (ja) | SiCバイポーラ型半導体素子 | |

| US9960044B2 (en) | Semiconductor device and methods for forming a semiconductor device | |

| JP2017092283A (ja) | 半導体装置およびその製造方法 | |

| US10312133B2 (en) | Method of manufacturing silicon on insulator substrate | |

| JP2023554043A (ja) | 半導体デバイスのための構造体および半導体デバイスのための構造体を製造するための方法 | |

| CN103456611A (zh) | 提高锗材料n型掺杂载流子浓度的方法与应用 | |

| CN101090094A (zh) | 制造半导体器件的方法 | |

| Han et al. | Influence of Proton Irradiation dose on the Performance of Local Lifetime Controlled Power Diode with Proximity Gettering of Platinum |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20151112 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161129 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170227 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170404 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190408 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190508 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20190610 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190704 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20191114 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6619210 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |