JP6335444B2 - 再成長構造を用いたiii族窒化物トランジスタ - Google Patents

再成長構造を用いたiii族窒化物トランジスタ Download PDFInfo

- Publication number

- JP6335444B2 JP6335444B2 JP2013132779A JP2013132779A JP6335444B2 JP 6335444 B2 JP6335444 B2 JP 6335444B2 JP 2013132779 A JP2013132779 A JP 2013132779A JP 2013132779 A JP2013132779 A JP 2013132779A JP 6335444 B2 JP6335444 B2 JP 6335444B2

- Authority

- JP

- Japan

- Prior art keywords

- barrier layer

- layer

- gate

- resistive

- regrowth structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010410 layer Substances 0.000 claims description 282

- 230000004888 barrier function Effects 0.000 claims description 139

- 239000000463 material Substances 0.000 claims description 86

- 238000000034 method Methods 0.000 claims description 64

- 238000000151 deposition Methods 0.000 claims description 29

- 239000000758 substrate Substances 0.000 claims description 25

- 239000012212 insulator Substances 0.000 claims description 20

- 229910002601 GaN Inorganic materials 0.000 claims description 19

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 18

- 230000015572 biosynthetic process Effects 0.000 claims description 17

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 claims description 15

- 239000010931 gold Substances 0.000 claims description 13

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 12

- 229910052782 aluminium Inorganic materials 0.000 claims description 12

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 12

- 229910052733 gallium Inorganic materials 0.000 claims description 12

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 claims description 9

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 claims description 9

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 claims description 9

- 229910052738 indium Inorganic materials 0.000 claims description 9

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 9

- 229910052757 nitrogen Inorganic materials 0.000 claims description 9

- 239000003989 dielectric material Substances 0.000 claims description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 7

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 claims description 7

- AUCDRFABNLOFRE-UHFFFAOYSA-N alumane;indium Chemical compound [AlH3].[In] AUCDRFABNLOFRE-UHFFFAOYSA-N 0.000 claims description 6

- 238000005530 etching Methods 0.000 claims description 6

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 6

- 229910052737 gold Inorganic materials 0.000 claims description 6

- 239000002356 single layer Substances 0.000 claims description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 5

- 239000004065 semiconductor Substances 0.000 claims description 5

- 229910052710 silicon Inorganic materials 0.000 claims description 5

- 239000010703 silicon Substances 0.000 claims description 5

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 claims description 4

- 229910052750 molybdenum Inorganic materials 0.000 claims description 4

- 239000011733 molybdenum Substances 0.000 claims description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 claims description 4

- 230000005533 two-dimensional electron gas Effects 0.000 claims description 4

- 239000007772 electrode material Substances 0.000 claims description 3

- 229910052741 iridium Inorganic materials 0.000 claims description 3

- 229910052759 nickel Inorganic materials 0.000 claims description 3

- 229910052697 platinum Inorganic materials 0.000 claims description 3

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 claims description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 2

- 239000010408 film Substances 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 11

- 239000002184 metal Substances 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- 239000004020 conductor Substances 0.000 description 10

- 238000005137 deposition process Methods 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 239000010936 titanium Substances 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000003877 atomic layer epitaxy Methods 0.000 description 6

- 238000004871 chemical beam epitaxy Methods 0.000 description 6

- 150000004767 nitrides Chemical class 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 239000002800 charge carrier Substances 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 3

- 238000000231 atomic layer deposition Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 230000015556 catabolic process Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- 150000002739 metals Chemical class 0.000 description 3

- 238000001451 molecular beam epitaxy Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- -1 GaN Chemical class 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000003321 amplification Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000005684 electric field Effects 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 230000006978 adaptation Effects 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000003750 conditioning effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 239000012777 electrically insulating material Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000012467 final product Substances 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 230000009349 indirect transmission Effects 0.000 description 1

- 230000005404 monopole Effects 0.000 description 1

- 230000006911 nucleation Effects 0.000 description 1

- 238000010899 nucleation Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66446—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET]

- H01L29/66462—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET] with a heterojunction interface channel or gate, e.g. HFET, HIGFET, SISFET, HJFET, HEMT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2006—Amorphous materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7786—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

Description

Claims (29)

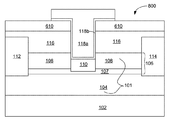

- 基板上に配置され、ガリウム(Ga)と窒素(N)とを含むバッファ層と、

前記バッファ層上に配置され、アルミニウム(Al)と窒素(N)とを含むバリア層と、

前記バリア層内に配置されて前記バリア層に接続され、窒素(N)とアルミニウム(Al)とを含む抵抗性再成長構造であって、非晶質材料および多結晶材料の少なくとも一方を備える抵抗性再成長構造と、

前記バリア層内に配置されたゲート端子と、を備え、

前記抵抗性再成長構造は、前記ゲート端子と前記バッファ層間に配置され、前記バッファ層と前記ゲート端子間に絶縁層を提供することを特徴とする装置。 - 前記抵抗性再成長構造は、窒化アルミニウム(AlN)、窒化インジウムアルミニウム(InAlN)、窒化アルミニウムガリウム(AlGaN)または窒化インジウムガリウムアルミニウム(InGaAlN)を含むことを特徴とする請求項1に記載の装置。

- 前記バリア層は、第1の層と第2の層とを含む複数の層で構成され、

前記第1の層は、前記バッファ層にエピタキシャルに接続され、また、窒化アルミニウム(AlN)を含んでおり、

前記第2の層は、前記第1の層にエピタキシャルに接続され、また、窒化インジウムアルミニウム(InAlN)、窒化アルミニウムガリウム(AlGaN)または窒化インジウムガリウムアルミニウム(InGaAlN)を含んでおり、

前記抵抗性再成長構造は、前記第1の層と前記第2の層とに物理的に直接接触していることを特徴とする請求項1または2に記載の装置。 - 前記バリア層は、窒化アルミニウムガリウム(AlGaN)の単独層で構成されていることを特徴とする請求項1または2に記載の装置。

- 前記抵抗性再成長構造と前記バッファ層間の前記バリア層の厚みは、10Å〜50Åであることを特徴とする請求項1乃至4のいずれか1項に記載の装置。

- 前記抵抗性再成長構造のバンドギャップエネルギーは5eV以上であることを特徴とする請求項1乃至5のいずれか1項に記載の装置。

- 前記抵抗性再成長構造のバンドギャップエネルギーは、第1のバンドギャップエネルギーであり、

前記バリア層は、前記第1のバンドギャップエネルギーより小さい第2のバンドギャップエネルギーを有しており、

前記バッファ層は、前記第2のバンドギャップエネルギーより小さい第3のバンドギャップエネルギーを有していることを特徴とする請求項6に記載の装置。 - 前記抵抗性再成長構造の厚みは200Å以下であることを特徴とする請求項1乃至7のいずれか1項に記載の装置。

- 前記抵抗性再成長構造は、前記ゲート端子と前記バッファ層間に配置されたゲート領域における二次元電子ガス(2DEG)の形成を阻止する動作機能を有しており、

前記ゲート端子は、エンハンスメントモード(Eモード)高電子移動度トランジスタ(HEMT)デバイスのスイッチングを制御するように構成されていることを特徴とする請求項1乃至8のいずれか1項に記載の装置。 - 前記ゲート端子は、前記バリア層の材料に接続されてショットキー接合または金属−絶縁体−半導体(MIS)接合を形成することを特徴とする請求項1乃至9のいずれか1項に記載の装置。

- 前記バリア層に接続されたソースと、

前記バリア層に接続されたドレインと、をさらに備え、前記ソースと前記ドレインは、前記バリア層を通って前記バッファ層内に延在することを特徴とする請求項1乃至10のいずれか1項に記載の装置。 - 前記バリア層上に配置され、前記ゲート端子の一部分を封入する誘電材料をさらに備えることを特徴とする請求項11に記載の装置。

- 前記ゲート端子は、T形のフィールドプレートゲートであり、

前記ゲート端子は、ニッケル(Ni)、白金(Pt)、イリジウム(Ir)、モリブデン(Mo)または金(Au)を含むことを特徴とする請求項12に記載の装置。 - 前記誘電材料上に配置され、前記誘電材料を通して、前記ソースに電気的に接続され、また、前記ゲート端子に容量接続されたフィールドプレートをさらに備えることを特徴とする請求項13に記載の装置。

- シリコン(Si)、炭化ケイ素(SiC)、サファイア(Al2O3)、窒化ガリウム(GaN)または窒化アルミニウム(AlN)を含む基板をさらに備えることを特徴とする請求項1乃至14のいずれか1項に記載の装置。

- 前記抵抗性再成長構造は、前記バリア層のシート抵抗を増加させることを特徴とする請求項1から15のいずれか1項に記載の装置。

- 前記抵抗性再成長構造は、前記ゲート領域のシート抵抗を増加させることを特徴とする請求項9に記載の装置。

- ガリウム(Ga)と窒素(N)とを基板上にバッファ層を形成するステップと、

アルミニウム(Al)と窒素(N)とを含むバリア層を前記バッファ層上に形成するステップと、

前記バリア層の材料を除去してその中に開口部を形成し、600℃以下の温度で、窒素(N)とアルミニウム(Al)とを含む抵抗性再成長構造を前記バリア層の開口部内に堆積することによって、前記バリア層内に抵抗性再成長構造を形成するステップと、を備えることを特徴とする方法。 - 前記バッファ層を形成するステップは、前記基板上にバッファ層材料をエピタキシャルに堆積するステップを備え、

前記バリア層を形成するステップは、前記バッファ層上にバリア層材料をエピタキシャルに堆積するステップを備えることを特徴とする請求項18に記載の方法。 - 前記抵抗性再成長構造の材料は、窒化アルミニウム(AlN)、窒化インジウムアルミニウム(InAlN)、窒化アルミニウムガリウム(AlGaN)または窒化インジウムガリウムアルミニウム(InGaAlN)を含むことを特徴とする請求項18または19に記載の方法。

- 前記バリア層を形成するステップは、第1の層と第2の層とを含む複数の層を形成するステップを備え、

前記第1の層は、前記バッファ層にエピタキシャルに接続され、また、窒化アルミニウム(AlN)を含んでおり、

前記第2の層は、前記第1の層にエピタキシャルに接続され、また、窒化インジウムアルミニウム(InAlN)、窒化アルミニウムガリウム(AlGaN)または窒化インジウムガリウムアルミニウム(InGaAlN)を含んでおり、

前記抵抗性再成長構造は、前記第1の層と前記第2の層とに物理的に直接接触していることを特徴とする請求項18乃至20のいずれか1項に記載の方法。 - 前記バリア層を形成するステップは、窒化アルミニウムガリウム(AlGaN)の単独層を形成するステップを備えることを特徴とする請求項18乃至20のいずれか1項に記載の方法。

- 前記バリア層の材料を除去するステップによって、前記抵抗性再成長構造と前記バッファ層間の前記バリア層の厚みが10Å〜50Åとなることを特徴とする請求項18乃至22のいずれか1項に記載の方法。

- 前記抵抗性再成長構造の材料を堆積するステップは、前記抵抗性再成長構造の材料を200Å以下の厚みで堆積するステップを備えることを特徴とする請求項18乃至23のいずれか1項に記載の方法。

- 前記バリア層の開口部内の前記抵抗性再成長構造上にゲート絶縁体膜の材料を堆積し、前記バリア層の材料に接続されてショットキー接合または金属−絶縁体−半導体(MIS)接合を形成するゲート電極の材料を前記ゲート絶縁体膜上に堆積することによって、前記バリア層内にゲート端子を形成するステップをさらに備えることを特徴とする請求項18乃至24のいずれか1項に記載の方法。

- 前記バリア層内に前記ゲート端子を形成するステップは、

前記バリア層の材料を除去してバリア層内に開口部を形成するステップをさらに備え、

前記バリア層の材料を除去するステップは、エッチングプロセスで行われることを特徴とする請求項25に記載の方法。 - 前記抵抗性再成長構造は、前記ゲート端子と前記バッファ層間に配置されたゲート領域における二次元電子ガス(2DEG)の形成を阻止する動作機能を有しており、

前記ゲート端子は、エンハンスメントモード(Eモード)高電子移動度トランジスタ(HEMT)デバイスのスイッチングを制御するように構成されていることを特徴とする請求項25に記載の方法。 - 前記バリア層に接続されたソースとドレインとを形成するステップをさらに備え、前記ソースと前記ドレインは、前記バリア層を通って前記バッファ層内に延在することを特徴とする請求項18乃至27のいずれか1項に記載の方法。

- 前記バリア層上に誘電材料を堆積するステップをさらに備えることを特徴とする請求項18乃至28のいずれか1項に記載の方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/535,127 | 2012-06-27 | ||

| US13/535,127 US8975664B2 (en) | 2012-06-27 | 2012-06-27 | Group III-nitride transistor using a regrown structure |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017243108A Division JP6554530B2 (ja) | 2012-06-27 | 2017-12-19 | 再成長構造を用いたiii族窒化物トランジスタ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014011462A JP2014011462A (ja) | 2014-01-20 |

| JP2014011462A5 JP2014011462A5 (ja) | 2016-07-14 |

| JP6335444B2 true JP6335444B2 (ja) | 2018-05-30 |

Family

ID=49754231

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013132779A Expired - Fee Related JP6335444B2 (ja) | 2012-06-27 | 2013-06-25 | 再成長構造を用いたiii族窒化物トランジスタ |

| JP2017243108A Expired - Fee Related JP6554530B2 (ja) | 2012-06-27 | 2017-12-19 | 再成長構造を用いたiii族窒化物トランジスタ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017243108A Expired - Fee Related JP6554530B2 (ja) | 2012-06-27 | 2017-12-19 | 再成長構造を用いたiii族窒化物トランジスタ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8975664B2 (ja) |

| JP (2) | JP6335444B2 (ja) |

| DE (1) | DE102013010487A1 (ja) |

| TW (1) | TWI610438B (ja) |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7501669B2 (en) | 2003-09-09 | 2009-03-10 | Cree, Inc. | Wide bandgap transistor devices with field plates |

| US9773877B2 (en) | 2004-05-13 | 2017-09-26 | Cree, Inc. | Wide bandgap field effect transistors with source connected field plates |

| US11791385B2 (en) | 2005-03-11 | 2023-10-17 | Wolfspeed, Inc. | Wide bandgap transistors with gate-source field plates |

| JP5966301B2 (ja) | 2011-09-29 | 2016-08-10 | 富士通株式会社 | 化合物半導体装置及びその製造方法 |

| US9123533B2 (en) | 2012-08-10 | 2015-09-01 | Avogy, Inc. | Method and system for in-situ etch and regrowth in gallium nitride based devices |

| US8884334B2 (en) * | 2012-11-09 | 2014-11-11 | Taiwan Semiconductor Manufacturing Co., Ltd. | Composite layer stacking for enhancement mode transistor |

| CN104037212B (zh) * | 2013-03-05 | 2019-03-22 | 首尔半导体株式会社 | 氮化物半导体元件及其制造方法 |

| US9847411B2 (en) * | 2013-06-09 | 2017-12-19 | Cree, Inc. | Recessed field plate transistor structures |

| US9679981B2 (en) * | 2013-06-09 | 2017-06-13 | Cree, Inc. | Cascode structures for GaN HEMTs |

| US9755059B2 (en) | 2013-06-09 | 2017-09-05 | Cree, Inc. | Cascode structures with GaN cap layers |

| JP6212124B2 (ja) * | 2013-08-30 | 2017-10-11 | 国立研究開発法人科学技術振興機構 | InGaAlN系半導体素子 |

| EP3235005A4 (en) * | 2014-12-18 | 2018-09-12 | Intel Corporation | N-channel gallium nitride transistors |

| TWI569439B (zh) * | 2015-03-31 | 2017-02-01 | 晶元光電股份有限公司 | 半導體單元 |

| CN106298903A (zh) * | 2015-05-18 | 2017-01-04 | 中国科学院苏州纳米技术与纳米仿生研究所 | 二次外延p型ⅲ族氮化物实现增强型hemt的方法及增强型hemt |

| TWI563654B (en) * | 2015-08-26 | 2016-12-21 | Globalwafers Co Ltd | Enhancement-Mode High-Electron-Mobility Transistor Structure |

| JP6746887B2 (ja) * | 2015-09-16 | 2020-08-26 | 住友電気工業株式会社 | 高電子移動度トランジスタ、及び高電子移動度トランジスタの製造方法 |

| CN105355555A (zh) * | 2015-10-28 | 2016-02-24 | 中国科学院微电子研究所 | 一种GaN基增强型功率电子器件及其制备方法 |

| US10068976B2 (en) * | 2016-07-21 | 2018-09-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Enhancement mode field-effect transistor with a gate dielectric layer recessed on a composite barrier layer for high static performance |

| CN106876443A (zh) * | 2017-03-03 | 2017-06-20 | 上海新傲科技股份有限公司 | 高击穿电压的氮化镓高电子迁移率晶体管及其形成方法 |

| TWI661555B (zh) * | 2017-12-28 | 2019-06-01 | 新唐科技股份有限公司 | 增強型高電子遷移率電晶體元件 |

| TWI726282B (zh) * | 2019-02-19 | 2021-05-01 | 世界先進積體電路股份有限公司 | 半導體裝置及其製造方法 |

| CN111668302B (zh) * | 2019-03-08 | 2023-03-14 | 世界先进积体电路股份有限公司 | 半导体装置及其制造方法 |

| US11335797B2 (en) | 2019-04-17 | 2022-05-17 | Vanguard International Semiconductor Corporation | Semiconductor devices and methods for fabricating the same |

| CN110676316B (zh) * | 2019-09-20 | 2023-04-11 | 中国电子科技集团公司第十三研究所 | 增强型场效应晶体管 |

| US11658233B2 (en) * | 2019-11-19 | 2023-05-23 | Wolfspeed, Inc. | Semiconductors with improved thermal budget and process of making semiconductors with improved thermal budget |

| JP7262379B2 (ja) * | 2019-12-16 | 2023-04-21 | 株式会社東芝 | 半導体装置 |

| CN111463259B (zh) * | 2020-03-10 | 2022-09-13 | 安徽长飞先进半导体有限公司 | 高电子迁移率场效应晶体管及其制备方法 |

| CN111668101B (zh) * | 2020-06-03 | 2022-07-01 | 西安电子科技大学 | 一种增强型氮化镓高电子迁移率晶体管及其制备方法 |

| DE112021003124T5 (de) * | 2020-06-04 | 2023-03-16 | Mitsubishi Electric Corporation | Halbleitereinheit |

| US11658234B2 (en) * | 2020-10-27 | 2023-05-23 | Wolfspeed, Inc. | Field effect transistor with enhanced reliability |

| US11502178B2 (en) | 2020-10-27 | 2022-11-15 | Wolfspeed, Inc. | Field effect transistor with at least partially recessed field plate |

| US11749726B2 (en) | 2020-10-27 | 2023-09-05 | Wolfspeed, Inc. | Field effect transistor with source-connected field plate |

| WO2022124868A1 (ko) * | 2020-12-11 | 2022-06-16 | 경북대학교 산학협력단 | 고전자이동도 트랜지스터 및 그 제조방법 |

| CN113113478B (zh) * | 2021-03-01 | 2022-10-04 | 西安电子科技大学 | 基于欧姆再生长的GaN基射频功率器件及其制备方法 |

| US20230078017A1 (en) * | 2021-09-16 | 2023-03-16 | Wolfspeed, Inc. | Semiconductor device incorporating a substrate recess |

| KR102535264B1 (ko) * | 2021-12-09 | 2023-05-26 | 울산대학교 산학협력단 | 고전자 이동성 트랜지스터의 제조방법 |

| WO2023239942A1 (en) * | 2022-06-10 | 2023-12-14 | The Board Of Trustees Of The Leland Stanford Junior University | Passivation and high temperature oxidation of iridium oxide schottky contacts for iii-nitride devices |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5915164A (en) | 1995-12-28 | 1999-06-22 | U.S. Philips Corporation | Methods of making high voltage GaN-A1N based semiconductor devices |

| CA2456662A1 (en) * | 2001-08-07 | 2003-02-20 | Jan Kuzmik | High electron mobility devices |

| JP2006032552A (ja) * | 2004-07-14 | 2006-02-02 | Toshiba Corp | 窒化物含有半導体装置 |

| US7238560B2 (en) | 2004-07-23 | 2007-07-03 | Cree, Inc. | Methods of fabricating nitride-based transistors with a cap layer and a recessed gate |

| JP2006286698A (ja) * | 2005-03-31 | 2006-10-19 | Furukawa Electric Co Ltd:The | 電子デバイス及び電力変換装置 |

| EP2312635B1 (en) * | 2005-09-07 | 2020-04-01 | Cree, Inc. | Transistors with fluorine treatment |

| JP5100002B2 (ja) * | 2005-12-14 | 2012-12-19 | 新日本無線株式会社 | 窒化物半導体装置 |

| JP5087240B2 (ja) * | 2006-06-28 | 2012-12-05 | 新日本無線株式会社 | 窒化物半導体装置の製造方法 |

| JP2008124374A (ja) * | 2006-11-15 | 2008-05-29 | Sharp Corp | 絶縁ゲート電界効果トランジスタ |

| JP2008153330A (ja) * | 2006-12-15 | 2008-07-03 | Oki Electric Ind Co Ltd | 窒化物半導体高電子移動度トランジスタ |

| JP2008270794A (ja) | 2007-03-29 | 2008-11-06 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2008288405A (ja) * | 2007-05-18 | 2008-11-27 | Nippon Telegr & Teleph Corp <Ntt> | ヘテロ構造電界効果トランジスタ |

| TWI512831B (zh) * | 2007-06-01 | 2015-12-11 | Univ California | 氮化鎵p型/氮化鋁鎵/氮化鋁/氮化鎵增強型場效電晶體 |

| JP2008306130A (ja) * | 2007-06-11 | 2008-12-18 | Sanken Electric Co Ltd | 電界効果型半導体装置及びその製造方法 |

| US7795642B2 (en) | 2007-09-14 | 2010-09-14 | Transphorm, Inc. | III-nitride devices with recessed gates |

| US20090072269A1 (en) * | 2007-09-17 | 2009-03-19 | Chang Soo Suh | Gallium nitride diodes and integrated components |

| JP2009231396A (ja) * | 2008-03-19 | 2009-10-08 | Sumitomo Chemical Co Ltd | 半導体装置および半導体装置の製造方法 |

| US7985986B2 (en) * | 2008-07-31 | 2011-07-26 | Cree, Inc. | Normally-off semiconductor devices |

| JP2010103478A (ja) * | 2008-09-25 | 2010-05-06 | Panasonic Corp | 窒化物半導体装置及びその製造方法 |

| US8754496B2 (en) | 2009-04-14 | 2014-06-17 | Triquint Semiconductor, Inc. | Field effect transistor having a plurality of field plates |

| WO2010151721A1 (en) | 2009-06-25 | 2010-12-29 | The Government Of The United States Of America, As Represented By The Secretary Of The Navy | Transistor with enhanced channel charge inducing material layer and threshold voltage control |

| JP2011082216A (ja) * | 2009-10-02 | 2011-04-21 | Fujitsu Ltd | 化合物半導体装置及びその製造方法 |

| US8748244B1 (en) * | 2010-01-13 | 2014-06-10 | Hrl Laboratories, Llc | Enhancement and depletion mode GaN HMETs on the same substrate |

| JP2011187623A (ja) * | 2010-03-08 | 2011-09-22 | Furukawa Electric Co Ltd:The | 半導体素子、および半導体素子の製造方法 |

| US20110241020A1 (en) * | 2010-03-31 | 2011-10-06 | Triquint Semiconductor, Inc. | High electron mobility transistor with recessed barrier layer |

| KR102065115B1 (ko) * | 2010-11-05 | 2020-01-13 | 삼성전자주식회사 | E-모드를 갖는 고 전자 이동도 트랜지스터 및 그 제조방법 |

| KR20130004760A (ko) * | 2011-07-04 | 2013-01-14 | 삼성전자주식회사 | 파워소자 및 이의 제조방법 |

| DE112011105988B4 (de) | 2011-12-23 | 2020-08-06 | Intel Corporation | III-N-Materialstruktur für Gate-Aussparungstransistoren |

-

2012

- 2012-06-27 US US13/535,127 patent/US8975664B2/en active Active

-

2013

- 2013-06-24 DE DE102013010487.4A patent/DE102013010487A1/de not_active Withdrawn

- 2013-06-24 TW TW102122338A patent/TWI610438B/zh not_active IP Right Cessation

- 2013-06-25 JP JP2013132779A patent/JP6335444B2/ja not_active Expired - Fee Related

-

2017

- 2017-12-19 JP JP2017243108A patent/JP6554530B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW201405823A (zh) | 2014-02-01 |

| JP2018082192A (ja) | 2018-05-24 |

| TWI610438B (zh) | 2018-01-01 |

| US20140001478A1 (en) | 2014-01-02 |

| JP6554530B2 (ja) | 2019-07-31 |

| US8975664B2 (en) | 2015-03-10 |

| DE102013010487A1 (de) | 2014-01-02 |

| JP2014011462A (ja) | 2014-01-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6554530B2 (ja) | 再成長構造を用いたiii族窒化物トランジスタ | |

| US9054167B2 (en) | High electron mobility transistor structure and method | |

| US20130320349A1 (en) | In-situ barrier oxidation techniques and configurations | |

| US9508807B2 (en) | Method of forming high electron mobility transistor | |

| JP2013247363A (ja) | 電荷誘導層を有するiii族窒化物トランジスタ | |

| KR101697825B1 (ko) | Hemt 디바이스를 위한 측벽 패시베이션 | |

| US8946779B2 (en) | MISHFET and Schottky device integration | |

| US20130099284A1 (en) | Group iii-nitride metal-insulator-semiconductor heterostructure field-effect transistors | |

| US20050258451A1 (en) | Methods of fabricating nitride-based transistors having regrown ohmic contact regions and nitride-based transistors having regrown ohmic contact regions | |

| US9112010B2 (en) | Nitride-based semiconductor device | |

| US11316038B2 (en) | HEMT transistor with adjusted gate-source distance, and manufacturing method thereof | |

| JP6510815B2 (ja) | ドープされた窒化ガリウム高電子移動度トランジスタ | |

| JP6279294B2 (ja) | フッ化物系または塩化物系化合物を含むゲート誘電体を備えたiii族窒化物系トランジスタ | |

| US20170309712A1 (en) | Semiconductor device and method for manufacturing the semiconductor device | |

| US20180358359A1 (en) | Transistor, semiconductor device, electronic apparatus, and method for producing transistor | |

| US20230261099A1 (en) | Semiconductor device, semiconductor module, and wireless communication apparatus | |

| US10424659B1 (en) | High electron mobility transistor |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160527 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170321 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170616 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170822 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171219 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20171227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180330 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180410 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180501 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6335444 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |