JP6202972B2 - メモリシステム及びそれの読み出し校正方法 - Google Patents

メモリシステム及びそれの読み出し校正方法 Download PDFInfo

- Publication number

- JP6202972B2 JP6202972B2 JP2013210121A JP2013210121A JP6202972B2 JP 6202972 B2 JP6202972 B2 JP 6202972B2 JP 2013210121 A JP2013210121 A JP 2013210121A JP 2013210121 A JP2013210121 A JP 2013210121A JP 6202972 B2 JP6202972 B2 JP 6202972B2

- Authority

- JP

- Japan

- Prior art keywords

- memory

- data

- read

- controller

- memory cells

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1068—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in sector programmable memories, e.g. flash disk

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1072—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in multilevel memories

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0253—Garbage collection, i.e. reclamation of unreferenced memory

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5671—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge trapping in an insulator

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/52—Protection of memory contents; Detection of errors in memory contents

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Quality & Reliability (AREA)

- Read Only Memory (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Memory System (AREA)

Description

例示的な実施形態において、前記メモリ制御器は、ホストによって要請された書き込み動作が完了した後、前記読み出し校正動作の少なくとも一部を実行する。

例示的な実施形態において、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記要請された書き込み動作の時、移動するデータの量は、ホストによって要請された書き込み動作が完了した後、前記ホストのタイムアウト区間のうち、残った時間を考慮して決められる。

例示的な実施形態において、書き込み動作が要請される時、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記第1メモリ領域の一つのメモリブロックの格納容量に対応するデータは、前記第1メモリ領域のメモリブロックに移動する。

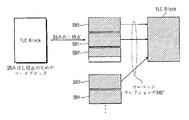

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックのうち、空の格納空間を有するメモリブロックを除いた残りのメモリブロックに格納されたデータは、前記メモリ制御器のバックグラウンド動作の時、前記第1メモリ領域のメモリブロックのうちデータで完全に満たされたメモリブロックのデータと共に前記第2メモリ領域のメモリブロックのうちで選択されたメモリブロックに移動し、前記第2メモリ領域の選択されたメモリブロックは、オープンワードラインを含まない。

例示的な実施形態において、前記mビットのデータは、1ビットのデータであり、前記nビットのデータは、3ビットのデータである。

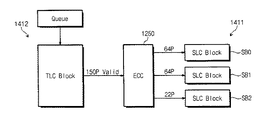

例示的な実施形態において、書き込み動作が要請されるたびに、前記メモリ制御器は、ホストのタイムアウト条件を回避するように、前記バッファメモリのキュー情報に対応する前記第2メモリ領域のメモリブロックに対する前記読み出し校正動作を時分割方式で行う。

例示的な実施形態において、前記読み出し校正動作の対象となる前記第2メモリ領域のメモリブロックの有効データのうち、前記第1メモリ領域の一つのメモリブロックの格納容量に対応するデータは、前記書き込み動作が要請された時、前記第1メモリ領域のメモリブロックに移動する。

例示的な実施形態において、前記メモリ制御器は、前記第2メモリ領域のメモリブロックに読み出されたデータが訂正できない場合、読み出しリトライ動作を実行し、前記読み出しリトライ動作を通じて前記第2メモリ領域のメモリブロックに読み出されたデータが訂正可能である時、前記キュー情報を前記バッファメモリに格納する。

例示的な実施形態において、前記メモリ制御器は、前記第2メモリ領域のメモリブロックに読み出されたデータのエラービットの数が基準を超えた時、前記キュー情報を前記バッファメモリに格納する。

例示的な実施形態において、前記読み出し校正動作の少なくとも一部は、書き込み動作が要請される時に実行される。

例示的な実施形態において、前記読み出し校正動作の少なくとも一部は、ホストによって要請された書き込み動作が完了した後に実行される。

例示的な実施形態において、読み出し校正動作の対象となる前記第2メモリブロックの有効データのうち、第1メモリブロックの格納容量に対応するデータは、書き込み動作が要請される時、前記第1メモリブロックに移動する。

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックに格納されたデータは、前記メモリ制御器のガーベッジコレクションの動作の時に前記第2メモリブロックのうちの一つのメモリブロックに移動する。

例示的な実施形態において、前記mビットのデータは、1ビットのデータであり、前記nビットのデータは、3ビットのデータである。

例示的な実施形態において、前記メモリ制御器から提供されるデータは、バッファプログラム動作により前記第1メモリブロックに格納され、前記第1メモリブロックに格納されたデータは、メインプログラム動作により前記第2メモリブロックに格納される。

例示的な実施形態において、前記少なくとも一つ以上のメモリブロックのうち、空の格納空間を有するメモリブロックを除いた残りのメモリブロックに格納されたデータは、前記ガーベッジコレクションの際、前記第1メモリブロックのうちデータで完全に満たされたメモリブロックのデータと共に前記第2メモリブロックのうち選択されたメモリブロックに移動し、前記第2メモリブロックの選択されたメモリブロックは、オープンワードラインを含まない。

例示的な実施形態において、前記mビットのデータは、1ビットのデータであり、前記nビットのデータは、3ビットのデータである。

例示的な実施形態において、前記第2メモリブロックから読み出されたデータは、LSBページデータ、CSBページデータ、またはMSBページデータである。

図面において、本発明の実施形態は、図示された特定の形態に限定されず、明確性のために誇張されている。また、明細書の全体にわたって同一の参照番号として表示された部分は、同一の構成要素を示す。

図1は、本発明に係る再プログラミング方式により実行されるメインプログラム動作を示す図である。図1は、3ビットデータ(または、LSBページのデータ、CSBページのデータ、MSBページのデータで構成される3ページのデータ)が再プログラム方式によってプログラムされる例を示す。しかし、再プログラム方式は3ビットデータに限定されない。再プログラム方式は、第1プログラム段階、第2プログラム段階、及び第3プログラム段階を含み、これは、以下詳細に説明する。

例示的な実施形態において、第1プログラミング段階は検証動作を含む。検証動作の時、少なくとも一つのプログラム状態のみに対して検証動作を実行することができる。例えば、第1プログラミング段階で、プログラム状態P12、P14、P16の検証動作が実行される一方、プログラム状態P11、P13、P15、P17の検証動作は実行されない。つまり、プログラム状態P12、P14、P16が検証パスされれば、第1プログラミング段階は終了する。

例示的な実施形態において、第2プログラミング段階は、検証動作を含む。検証動作はすべてのプログラム状態に対して行われる。すべてのプログラム状態P21〜P27が検証パスされれば、第2プログラミング段階は終了する。

ここで、状態P31〜P37は、図1に示すように、第2プログラミング段階の読み出しマージンより大きい読み出しマージンを有するように隣接することができる。すなわち、第3プログラム段階では、第2プログラミング段階でプログラムされた3ビットのデータが再プログラムされる。上述のように、第3プログラム段階で使われる3ビットのデータは、第1及び第2プログラミング段階で使われたものと同様であり、第1メモリ領域から再び読み出される。第3プログラミング段階が行われることによって、第2プログラミング段階の状態P21は、第3プログラム段階の状態P31に再プログラムされる。これは、第3プログラム段階の状態P31に対応する閾値電圧のばらつきが第2プログラミング段階の状態P21に対応する閾値電圧のばらつきより狭くする。すなわち、第3プログラム段階の状態31を検証するための検証電圧VR31が第2プログラミング段階の状態P21を検証するための検証電圧VR21より高い。

例示的な実施形態において、第3プログラム段階では、すべてのプログラム状態に対して検証動作が実行される。すべてのプログラム状態P31〜P37が検証パスされれば、第3プログラム段階は終了する。

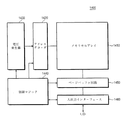

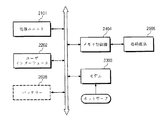

図2を参照すると、本発明の実施形態に係るメモリシステム1000は、メモリ制御器1200と、マルチビットメモリ装置として不揮発性メモリ装置1400とを含む。メモリ制御器1200は、外部(例えば、ホスト)からの要請(例えば、書き込み要請、読み出し要請等)に応答して不揮発性メモリ装置1400を制御する。メモリ制御器1200は、外部からの要請なしに内部的な要請(例えば、サドンパワーオフ(Sudden Power Off)に係る動作、ウエアレベリング動作、読み出し校正(read reclaim)動作など)に応じて不揮発性メモリ装置1400を制御する。メモリ制御器1200の内部的な要請に対応する動作は、ホストからの要請が処理された後、ホストのタイムアウト区間内で行われる。または、メモリ制御器1200の内部的な要請に対応する動作は、メモリ制御器1200の遊休時間に行われる。不揮発性メモリ装置1400は、メモリ制御器1200の制御に応答して動作し、データの情報を格納する一種の格納媒体として使用される。格納媒体は、一つ以上のメモリチップで構成することができる。不揮発性メモリ装置1400とメモリ制御器1200は、一つ以上のチャネルを介して通信する。不揮発性メモリ装置1400は、例えば、NANDフラッシュメモリ装置を含む。

不揮発性メモリ装置1400は、例えば、NANDフラッシュメモリ装置である。しかし、本発明は、NANDフラッシュメモリ装置に限定されない。例えば、不揮発性メモリ装置1400は、NORフラッシュメモリ装置、RRAM(登録商標)(Resistive Random Access Memory)装置、PRAM(Phase−Change Memory)装置、MRAM(Magnetoresistive Random Access Memory)装置、FRAM(登録商標)(Ferroelectric Random Access Memory)装置、STT−RAM(Spin Transfer Torque Random Access Memory)などで構成することができる。また、本発明の不揮発性メモリ装置1400は、3次元アレイ構造を有するように実現することができる。3次元アレイ構造を有する不揮発性メモリ装置は、垂直NANDフラッシュメモリ装置と呼ばれる。本発明は、電荷格納層が伝導性の浮遊ゲートで構成されたフラッシュメモリ装置だけではなく、電荷格納層が絶縁膜で構成されるチャージトラップ型フラッシュ(Charge Trap Flash、“CTF”という)メモリ装置にも適用可能である。

メモリセルアレイ1410は、行(例えば、ワードライン)と、列(例えば、ビットライン)との交差領域に配列されたメモリセルを含む。メモリセルの各々は、1ビットのデータまたはマルチビットのデータを格納する。アドレスデコーダ1420は、制御ロジック1440によって制御され、メモリセルアレイ1410の行(例えば、ワードライン、ストリング選択ライン、接地選択ライン、共通ソースラインなど)の選択及び駆動を行う。電圧発生器1430は、制御ロジック1440によって制御され、各動作に必要な電圧(例えば、高電圧、プログラム電圧、読み出し電圧、検証電圧、消去電圧、パス電圧、バルク電圧など)を発生する。電圧発生器1430によって生成された電圧は、アドレスデコーダ1420を通じてメモリセルアレイ1410に提供される。制御ロジック1440は、不揮発性メモリ装置1400の全体的な動作を制御するように構成される。

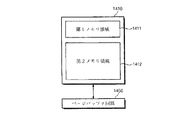

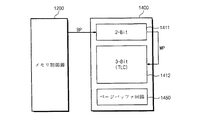

図5を参照すると、メモリセルアレイ1410は、複数のメモリブロックで構成され、複数のメモリブロックは、第1メモリ領域1411と第2メモリ領域1412とに区分される。ここで、第1及び第2メモリ領域1411、1412の区分は物理的なものではなく、論理的に行われる。第1及び第2メモリ領域1411、1412の区分は、論理的に可変可能である。つまり、第1及び第2メモリ領域1411、1412の物理的なサイズがメモリ制御器1200の制御の下に論理的に可変可能である。第1メモリ領域1411に属するメモリブロックは、第2メモリ領域1412に属するメモリブロックとは異なる方法でプログラムされる。例えば、第1メモリ領域1411に属するメモリブロックは、単一ビットプログラム方法(または、SLCプログラム方式という)に基づいてプログラムされ、第2メモリ領域1412に属するメモリブロックは、マルチビットプログラム方法(または、MLC/TLCプログラム方式という)(例えば、上述の3ステップ再プログラム方式)に基づいてプログラムされる。つまり、第1メモリ領域1411に属するメモリセルの各々は、1ビットのデータを格納し、第2メモリ領域1412に属するメモリセルの各々は、Mビットデータ(Mは3以上の整数)を格納する。また、第1メモリ領域1411に属するメモリセルの各々は、第2メモリ領域1412に属するメモリセルの各々に格納されるデータビットの数より少ない数のデータビットを格納する。ここで、第1メモリ領域1411に属するメモリセルの各々が1ビットのデータを格納することに限定されない。例えば、第1メモリ領域1411に属するメモリセルの各々に格納されるビットの数は、第2メモリ領域1412に属するメモリセルの各々に格納されるビットの数より少ない。

上述のように、マルチビットメモリ装置1400は、第1メモリ領域1411と第2メモリ領域1412とを含む。ここで、第1メモリ領域1411と第2メモリ領域1412は、マルチビットメモリ装置1400のメモリセルアレイを構成する。図示しないが、メモリセルアレイは、より多くの領域(例えば、メタ領域、予備領域など)を含む。メモリセルアレイのメモリ領域は物理的に区分されず、論理的に区分される。これは、メモリ制御器1200のアドレスマッピングに基づいて、メモリ領域が定義されることを意味する。

メモリセルの閾値電圧のばらつきは、様々な原因(例えば、温度変化、読み出し動作の繰り返し等)により移動することがある。閾値電圧のばらつきの移動は、メモリセルから読み出されたページのデータでエラービットが発生するようにする。例えば、閾値電圧のばらつきの移動は、エラービットの数を増加させる。特に、セル当たり3ビットのデータが格納されるTLCブロックの場合、閾値電圧のばらつきの移動は、エラービットの数をさらに増加させる。したがって、読み出されたデータの整合性を確保するために読み出し校正動作を実行することができる。読み出し校正動作は、訂正できないと判断されたページのデータを含んだTLCブロックの有効データを新しいブロックに移動させる動作を意味する。または、読み出し校正動作は、エラービットの数が今後増加する可能性が高いページのデータを含んだTLCブロックの有効データを新しいブロックに移動させる動作を意味する。読み出し校正動作は、ページのデータが格納されたメモリセルの閾値電圧のばらつきの移動が隣接したメモリセルにも影響を与えるため行われる。

TLCブロックに格納された有効なページのデータのすべてが、第1メモリ領域1411に移動すれば、CPU1230は、TLCブロックに対するFTLの読み出し校正動作を完了したと処理する。例えば、キューに格納された情報(読み出し校正動作の対象ブロック)が変更される。

図9は、読み出し校正動作を通じて生成されたSLCブロックのデータがTLCブロックに格納される例を示す図である。

例示的な実施形態において、空の格納空間を有するSLCブロックSB2のデータは、空の格納空間を有する他のSLCブロックのデータと共に他のSLCブロックに、またはTLCブロックに移動することができる。

メモリ制御器1200は、キューに格納された情報に基づいて、読み出し校正動作を実行し、これは図8A、図8B、及び図9での説明と同様に行われる。

メモリ制御器1200は、キューに格納された情報に基づいて、読み出し校正動作を実行し、これは図8A、8b、及び図9での説明と同様に行われる。

図12を参照すると、読み出し校正動作は、読み出し動作の時、読み出しフェイルされる可能性が高いページのデータを含んだTLCブロックの有効なデータを新しいブロックに移動させる動作として、データの整合性を確保するために行われる。本発明では、特に、読み出し校正動作の対象ブロックとして決められたTLCブロックを示す情報がキューに格納される。ホストからの要請(例えば、書き込み要請)の時、例えば、要請された動作が完了し、キューに格納された情報に基づいてTLCブロックの有効なページのデータのうちの一部(または、すべて)がSLCブロックに移動する。SLCブロックへのデータ移動は、ECC回路1250の符号化及びバッファプログラミングを通じて行われる。

したがって、本発明の読み出し校正動作は、ホストのタイムアウト条件を満たしながら実行することができる。また、本発明のメモリシステムは、TLCブロックにオープンワードラインが生成されることを防止することができる。

図14を参照すると、半導体ドライブ4000(SSD)は、格納媒体4100と、制御器4200とを含む。格納媒体4100は、複数のチャンネルCH0〜CHn1を通じて制御器4200と接続する。各チャンネルには、複数の不揮発性メモリが共通に接続するようになる。制御器4200は、図2に示したものと実質的に同一に構成され、格納媒体4100の不揮発性メモリ装置の各々は、図4に示した不揮発性メモリ装置と実質的に同一に構成される。例えば、制御器4200は、読み出し校正動作の対象ブロックであるTLCブロックを、キューを利用して管理し、特定の時間(例えば、ホストの書き込み要請の時)に、キューに格納された情報に基づいてTLCブロックを選択し、選択されたTLCブロックの有効なページのデータが格納媒体4100の不揮発性メモリ装置に含まれたSLCブロックに移動するように格納媒体4100を制御する。制御器4200は、選択されたTLCブロックの有効なページのデータが格納媒体4100の不揮発性メモリ装置に含まれたSLCブロックに移動する時、選択されたTLCブロックに対する読み出し校正動作を完了したと処理する。

本発明の実施形態に係る半導体ドライブ4000は、ストレージを構成するために使用することができる。図15に示すように、ストレージは、図14での説明と実質的に同一に構成される複数の半導体ドライブを含む。本発明の実施形態に係る半導体ドライブ4000は、ストレージサーバを構成するために使用することができる。図16に示すように、ストレージサーバは、図14での説明と実質的に同一に構成される複数の半導体ドライブ4000と、サーバ4000Aとを含む。また、この分野でよく知られているRAID制御器4000Bをストレージサーバに提供することができることを容易に理解することができる。

本発明に係るMoviNAND5000は、大容量のデータの格納に有利であるだけでなく、向上した読み出し動作特性を有する。本発明の実施形態に係るMoviNAND5000は、小型及び低電力が要求されるモバイル製品(例えば、GALAXY S、GALAXY Note、iPhoneなど)に応用可能である。

モバイル装置に関するより詳細な説明は、特許文献4、5、6、7及び8に記載されている。

図19に示すように、本発明の実施形態に係る半導体ドライブは、メールサーバ8100にも適用可能である。

メモリカードは、例えば、MMCカード、SDカード、マルチユース(multiuse)カード、マイクロSDカード、メモリスティック、コンパクトSDカード、IDカード、PCMCIAカード、SSDカード、チップカード(chipcard)、スマートカード(smartcard)、USBカードなどになることができる。

制御器9222は、プロセッサとして、不揮発性メモリ装置9207のライト動作及びリード動作を制御することができる。具体的に、制御器9222は、データバスDATAとアドレスバスADDRESSとを通じて不揮発性メモリ装置9207及びインターフェース部9221とカップリングされている。インターフェース部9221は、ホストとメモリカードとの間のデータ交換を実行するためのカードプロトコル(例えば、SD/MMC)を通じてホストとインターフェイシングする。

図21を参照すると、デジタルスチルカメラは、ボディ9301と、スロット9302と、レンズ9303と、ディスプレイ部9308と、シャッターボタン9312と、ストローブ(strobe)9318などを含む。特に、スロット9308には、メモリカード9331を挿入することができ、メモリカード9331は、図1で説明したメモリ制御器と不揮発性メモリ装置とを含む。例えば、メモリ制御器は、読み出し校正動作の対象ブロックであるTLCブロックを、キューを利用して管理し、特定の時間(例えば、ホストの書き込み要請の時)に、キューに格納された情報に基づいてTLCブロックを選択し、選択されたTLCブロックの有効なページのデータが不揮発性メモリ装置に含まれたSLCブロックに移動するように不揮発性メモリ装置を制御する。メモリ制御器は、選択されたTLCブロックの有効なページのデータが不揮発性メモリ装置に含まれたSLCブロックに移動する時、選択されたTLCブロックに対する読み出し校正動作を完了したと処理する。

図22を参照すると、メモリカード9331は、ビデオカメラ(VC)、テレビ(TV)、オーディオ装置(AD)、ゲーム装置(GM)、電子音楽装置(EMD)、携帯電話(HP)、コンピュータ(CP)、PDA(Personal Digital Assistant)、ボイスレコーダ(voice recorder)(VR)、PCカード(PCC)などに使用することができる。

本発明の実施形態において、メモリセルは、可変抵抗メモリセルで構成することができ、例示的な可変抵抗メモリセル及びそれを含むメモリ装置は、特許文献9に掲載されている。

電荷格納層として電荷トラップフラッシュ構造を有するメモリ装置が、特許文献10、11、12に各々掲載されている。ソース/ドレインがないフラッシュ構造は、特許文献13に掲載されている。

1200 メモリ制御器

1210 ホストインターフェース

1220 メモリインターフェース

1230 CPU

1240 バッファメモリ

1250 ECC回路

1400 不揮発性メモリ装置

1410 メモリセルアレイ

1411 第1メモリ領域

1412 第2メモリ領域

1420 アドレスデコーダ

1430 電圧発生器

1440 制御ロジック

1450 ページバッファ回路

1460 入出力インターフェース

Claims (30)

- 3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを含む不揮発性メモリ装置と、

読出し動作、プログラム動作、及び再プログラム動作を遂行するために前記不揮発性メモリ装置を制御する制御器と、を含み、

前記制御器は、エラー訂正された(ECC(error checking and correction)−performed)第1データを生成するために前記第1データに対するECC動作を遂行するように構成され、

前記第1データは、第1電圧レベルで前記複数の第1メモリセルの第1部分から読み出され、

前記エラー訂正された第1データのエラービットの数が前記ECC動作によって修正可能な閾値(threshold)を超過する時、前記制御器は、エラー訂正された第2データを生成するために第2データに対するリードリトライ(read retry)動作及びECC動作を遂行するように構成され、

前記リードリトライ動作は、第2電圧レベルで前記複数の第1メモリセルの前記第1部分に格納された前記第2データを読み出すことを含み、

ここで、前記第2電圧レベルは、前記第1電圧レベルと異なり、

前記第2データは、前記複数の第1メモリセルの前記第1部分から読み出され、

前記制御器は、前記エラー訂正された第1データ及び前記エラー訂正された第2データのうちのいずれか1つを有する第1ページデータを前記不揮発性メモリ装置に出力するように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの第1部分に前記第1ページデータをプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの前記第1部分で前記プログラムされた第1ページデータを読み出すように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの前記第1部分から第1時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの第2部分にプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの前記第1部分から第2時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの前記第2部分に再プログラムするように構成されるメモリシステム。 - 前記第1時間は、前記第2時間と異なる請求項1に記載のメモリシステム。

- 前記制御器は、前記第1ページデータに対する前記ECC動作を遂行せずに、前記複数の第2メモリセルの前記第1部分から前記第1時間に読み出された前記第1ページデータを前記複数の第1メモリセルの前記第2部分にプログラムするように構成される請求項1に記載のメモリシステム。

- 前記制御器は、前記複数の第1メモリセルの前記第1部分から読み出された第3データに対する前記リードリトライ動作及び前記ECC動作を遂行するように構成される請求項1に記載のメモリシステム。

- 前記制御器は、前記複数の第1メモリセルの前記第2部分から読み出された第3データに対する前記ECC動作を遂行するように構成される請求項1に記載のメモリシステム。

- 前記複数の第1メモリセルの前記第1部分及び前記複数の第1メモリセルの前記第2部分は、同一のメモリブロックに含まれる請求項5に記載のメモリシステム。

- 前記第3データは、第2ページデータに含まれ、

前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項5に記載のメモリシステム。 - 前記第1ページデータ及び前記第2ページデータの各々は、有効なページデータである請求項7に記載のメモリシステム。

- 前記制御器が外部装置による要請を処理した後に、前記制御器は、前記複数の第2メモリセルの前記第1部分で前記第1ページデータを読み出し書き込むように構成される請求項1に記載のメモリシステム。

- 前記第1ページデータ及び前記第2ページデータは、事前に決定された時間周期内に前記制御器から前記不揮発性メモリ装置に出力される請求項7に記載のメモリシステム。

- 前記不揮発性メモリ装置は、垂直またはスタック型3次元アレイ構造(vertical or stack−type three−dimensional array structure)を有するメモリセルアレイを含む請求項1に記載のメモリシステム。

- 複数の第1メモリブロックに形成され、セル当たり1ビットデータを格納するように構成されたフラッシュメモリセルの第1グループと、

複数の第2メモリブロックに形成され、セル当たり3ビットデータを格納するように構成されたフラッシュメモリセルの第2グループと、

を含む不揮発性メモリ装置と、

前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、

前記メモリ制御器は、前記複数の第2メモリブロックのうちのいずれか1つに格納された有効なデータを前記複数の第1メモリブロックのうちの1つ以上のメモリブロックに伝送するためのリードリクレイム(read reclaim)動作を遂行するように構成され、

前記リードリクレイム動作は、第1時間に前記有効なデータの第1部分に対して遂行され、前記第1時間と異なる第2時間に前記有効なデータの第2部分に対して遂行され、

前記メモリ制御器は、前記複数の第1メモリブロックのうちの前記1つ以上のメモリブロックから読み出された前記有効なデータの第3部分を前記複数の第2メモリブロックの前記いずれか1つと異なる前記複数の第2メモリブロックのうちのいずれか1つに伝送するように1つ以上のプログラム動作を遂行するように構成されるメモリシステム。 - 前記メモリ制御器は、前記有効なデータに対するECC動作を遂行せずに、前記有効なデータの前記第3部分を前記複数の第2メモリブロックのうちの他の1つに伝送するように前記1つ以上のプログラム動作を遂行するように構成される請求項12に記載のメモリシステム。

- 前記1つ以上のプログラム動作の各々は、3段階プログラミング動作である請求項12に記載のメモリシステム。

- 前記3段階プログラミング動作は、第1プログラム段階及び前記第1プログラム段階の後に発生する第2プログラム段階を含み、

前記第2プログラム段階に対応する第2閾値電圧幅は、前記第1プログラム段階に対応する第1閾値電圧幅より狭い請求項14に記載のメモリシステム。 - 前記リードリクレイム動作は、前記有効なデータの少なくとも一部に対するリードリトライ動作を含む請求項12に記載のメモリシステム。

- 前記リードリクレイム動作は、第1時間周期及び第2時間周期の間に遂行され、

前記第1時間周期及び前記第2時間周期は、互いに分離される請求項16に記載のメモリシステム。 - 前記不揮発性メモリ装置は、垂直またはスタック型3次元アレイ構造を有するメモリセルアレイを含む請求項12に記載のメモリシステム。

- 3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを有する不揮発性メモリ装置及び前記不揮発性メモリ装置を制御する制御器を含む不揮発性メモリシステムの動作方法において、

第1電圧レベルで、前記複数の第1メモリセルの第1部分から第1データを読み出す段階と、

エラー訂正された第1データを生成するために前記第1データに対するECC(error checking and corretion)動作を遂行する段階と、

前記エラー訂正された第1データのエラービットの個数が前記ECC動作によって訂正可能な閾値を超過する時、第2電圧レベルで、前記複数の第1メモリセルの前記第1部分から第2データを読み出す段階と、

エラー訂正された第2データを生成するために前記第2データに対するECC動作を遂行する段階と、

前記エラー訂正された第1データ及び前記エラー訂正された第2データのうちのいずれか1つを有する第1ページデータを前記不揮発性メモリ装置に出力する段階と、

前記複数の第2メモリセルの第1部分に前記第1ページデータをプログラムする段階と、

第1時間に前記複数の第2メモリセルの前記第1部分から前記プログラムされたページデータを読み出す段階と、

前記第1時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの第2部分にプログラムする段階と、

第2時間に前記複数の第2メモリセルの前記第1部分から前記プログラムされた第1ページデータを読み出す段階と、

前記第2時間に読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの前記第2部分に再プログラムする段階と、を含む方法。 - 前記複数の第2メモリセルの前記第2部分に前記第1ページデータをプログラムする段階は、前記第1ページデータに対するECC動作無しで遂行される請求項19に記載の方法。

- 前記複数の第1メモリセルの第3部分から読み出された第3データに対するECC動作を遂行する段階をさらに含み、

前記第3データは、第2ページデータに含まれ、

前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力され、

前記第1ページデータ及び前記第2ページデータは、事前に決定された時間周期内に前記制御器から前記不揮発性メモリ装置に出力される請求項19に記載の方法。 - 前記制御器が外部装置の要請を処理した後に、前記第1ページデータ及び前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項21に記載の方法。

- 前記不揮発性メモリ装置は、垂直またはスタック型3次元アレイ構造を有するメモリセルアレイを含む請求項19に記載の方法。

- 3ビットデータを格納する複数の第1メモリメモリセル及び1ビットデータを格納する複数の第2メモリセルを含むメモリセルアレイを含み、前記メモリセルアレイは、垂直またはスタック型3次元アレイ構造である不揮発性メモリ装置と、

読出し動作、プログラム動作、及び再プログラム動作を遂行するために前記不揮発性メモリ装置を制御する制御器と、を含み、

前記制御器は、エラー訂正された第1データを生成するために前記第1データに対するECC動作を遂行するように構成され、

前記第1データは、第1電圧レベルで前記複数の第1メモリセルの第1部分から読み出され、

前記エラー訂正された第1データのエラービットの個数が前記ECC動作によって訂正可能な閾値を超過する時、前記制御器は、エラー訂正された第2データを生成するためにリードリトライ動作及びECC動作を遂行するように構成され、

前記リードリトライ動作は、前記第1電圧レベルと異なる第2電圧レベルで前記複数の第1メモリセルの前記第1部分に格納された第2データを読み出すことを含み、

前記第2データは、前記複数の第1メモリセルの前記第1部分から読み出され、

前記制御器は、前記エラー訂正された第1データ及び前記エラー訂正された第2データのうちのいずれか1つを含む第1ページデータを前記不揮発性メモリ装置に出力するように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの第1部分に前記第1ページデータをプログラムするように構成され、

前記不揮発性メモリ装置は、前記複数の第2メモリセルの前記第1部分から前記プログラムされた第1ページデータを読み出すように構成され、

前記不揮発性メモリ装置は、第1時間で前記複数の第2メモリセルの前記第1部分から読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの第2部分にプログラムするように構成され、

前記不揮発性メモリ装置は、第2時間で前記複数の第2メモリセルの前記第1部分から読み出された前記プログラムされた第1ページデータを前記複数の第1メモリセルの前記第2部分に再プログラムするように構成され、

前記第1時間は、前記第2時間と異なるメモリシステム。 - 前記制御器は、前記第1ページデータに対する前記ECC動作を遂行せずに、前記第1時間に前記複数の第2メモリセルの前記第1部分から読み出された前記第1ページデータを前記複数の第1メモリセルの前記第2部分にプログラムするように構成される請求項24に記載のメモリシステム。

- 前記制御器は、前記複数の第1メモリセルの前記第1部分から読み出された第3データに対する前記リードリトライ動作及び前記ECC動作を遂行するように構成される請求項24に記載のメモリシステム。

- 前記制御器は、前記複数の第1メモリセルの前記第2部分から読み出された第3データに対する前記ECC動作を遂行するように構成される請求項24に記載のメモリシステム。

- 前記複数の第1メモリセルの前記第1部分と前記複数の第1メモリセルの前記第2部分とは、同一のメモリブロックに含まれる請求項27に記載のメモリシステム。

- 前記第3データは、第2ページデータに含まれ、

前記第2ページデータは、前記制御器から前記不揮発性メモリ装置に出力される請求項27に記載のメモリシステム。 - 前記第1ページデータ及び前記第2ページデータの各々は、有効なページデータである請求項29に記載のメモリシステム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020120110859A KR102025263B1 (ko) | 2012-10-05 | 2012-10-05 | 메모리 시스템 및 그것의 읽기 교정 방법 |

| KR10-2012-0110859 | 2012-10-05 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014078229A JP2014078229A (ja) | 2014-05-01 |

| JP2014078229A5 JP2014078229A5 (ja) | 2016-12-08 |

| JP6202972B2 true JP6202972B2 (ja) | 2017-09-27 |

Family

ID=50407749

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013210121A Active JP6202972B2 (ja) | 2012-10-05 | 2013-10-07 | メモリシステム及びそれの読み出し校正方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US9431117B2 (ja) |

| JP (1) | JP6202972B2 (ja) |

| KR (1) | KR102025263B1 (ja) |

| CN (1) | CN103714856B (ja) |

Families Citing this family (81)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102025263B1 (ko) * | 2012-10-05 | 2019-09-25 | 삼성전자주식회사 | 메모리 시스템 및 그것의 읽기 교정 방법 |

| TWI533305B (zh) * | 2014-02-10 | 2016-05-11 | 慧榮科技股份有限公司 | 將資料寫入至快閃記憶體的方法及相關的記憶裝置與快閃記憶體 |

| US8886877B1 (en) * | 2014-05-15 | 2014-11-11 | Sandisk Technologies Inc. | In-situ block folding for nonvolatile memory |

| CN105224241A (zh) * | 2014-06-23 | 2016-01-06 | 联想(北京)有限公司 | Mram存储器、数据存储系统及数据读取方法 |

| KR20160016421A (ko) * | 2014-08-05 | 2016-02-15 | 삼성전자주식회사 | 비휘발성 메모리 기반의 스토리지 장치의 최적화 방법 |

| US9529668B2 (en) * | 2014-09-26 | 2016-12-27 | Intel Corporation | Method and system for using NAND page buffers to improve the transfer buffer utilization of a solid state drive |

| KR102238652B1 (ko) | 2014-11-12 | 2021-04-09 | 삼성전자주식회사 | 데이터 저장 장치, 이의 작동 방법, 및 이를 포함하는 데이터 처리 시스템의 작동 방법 |

| TWI559314B (zh) * | 2014-12-27 | 2016-11-21 | 群聯電子股份有限公司 | 記憶體管理方法、記憶體儲存裝置及記憶體控制電路單元 |

| KR102277521B1 (ko) | 2015-01-23 | 2021-07-16 | 삼성전자주식회사 | 저장 장치 및 그것의 리드 리클레임 및 읽기 방법 |

| KR102403253B1 (ko) | 2015-07-06 | 2022-05-30 | 삼성전자주식회사 | 불휘발성 메모리 장치를 포함하는 스토리지 장치 |

| KR20170006976A (ko) * | 2015-07-10 | 2017-01-18 | 에스케이하이닉스 주식회사 | 데이터 저장 장치 및 그것의 동작 방법 |

| IN2015CH04361A (ja) * | 2015-08-20 | 2015-09-04 | Wipro Ltd | |

| KR102333746B1 (ko) * | 2015-09-02 | 2021-12-01 | 삼성전자주식회사 | 재사용 주기에 따라 마모도를 관리하는 저장 장치의 동작 방법 |

| KR102387956B1 (ko) | 2015-09-09 | 2022-04-19 | 삼성전자주식회사 | 불휘발성 메모리 장치를 포함하는 메모리 시스템 |

| US10181352B2 (en) * | 2015-09-09 | 2019-01-15 | Toshiba Memory Corporation | Memory system and method of controlling nonvolatile memory |

| KR102501751B1 (ko) * | 2015-09-22 | 2023-02-20 | 삼성전자주식회사 | 메모리 콘트롤러, 불휘발성 메모리 시스템 및 그 동작방법 |

| DE102015120314A1 (de) * | 2015-11-24 | 2017-05-24 | Pilz Gmbh & Co. Kg | Verfahren zum Programmieren einer Sicherheitssteuerung |

| KR102437591B1 (ko) | 2015-12-03 | 2022-08-30 | 삼성전자주식회사 | 불휘발성 메모리 시스템의 동작 방법 및 메모리 컨트롤러의 동작 방법 |

| KR102449337B1 (ko) | 2015-12-14 | 2022-10-04 | 삼성전자주식회사 | 불휘발성 메모리 시스템의 동작 방법 |

| KR102435873B1 (ko) * | 2015-12-18 | 2022-08-25 | 삼성전자주식회사 | 스토리지 장치 및 그것의 리드 리클레임 방법 |

| KR20170076883A (ko) * | 2015-12-24 | 2017-07-05 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 그의 동작방법 |

| CN105677244B (zh) * | 2015-12-31 | 2019-04-09 | 记忆科技(深圳)有限公司 | 一种降低tlc闪存的固态硬盘写放大的方法 |

| US10417125B2 (en) * | 2016-02-11 | 2019-09-17 | Oracle International Corporation | Feedback-based selection of regions for abortable garbage collection |

| JP2017157257A (ja) * | 2016-03-01 | 2017-09-07 | 東芝メモリ株式会社 | 半導体記憶装置及びメモリシステム |

| DE102017106713A1 (de) | 2016-04-20 | 2017-10-26 | Samsung Electronics Co., Ltd. | Rechensystem, nichtflüchtiges Speichermodul und Verfahren zum Betreiben einer Speichervorrichtung |

| US9910772B2 (en) | 2016-04-27 | 2018-03-06 | Silicon Motion Inc. | Flash memory apparatus and storage management method for flash memory |

| TWI614759B (zh) * | 2016-04-27 | 2018-02-11 | 慧榮科技股份有限公司 | 存取快閃記憶體模組的方法及相關的快閃記憶體控制器與記憶裝置 |

| CN107391026B (zh) | 2016-04-27 | 2020-06-02 | 慧荣科技股份有限公司 | 闪存装置及闪存存储管理方法 |

| US10289487B2 (en) | 2016-04-27 | 2019-05-14 | Silicon Motion Inc. | Method for accessing flash memory module and associated flash memory controller and memory device |

| US10025662B2 (en) | 2016-04-27 | 2018-07-17 | Silicon Motion Inc. | Flash memory apparatus and storage management method for flash memory |

| US10019314B2 (en) * | 2016-04-27 | 2018-07-10 | Silicon Motion Inc. | Flash memory apparatus and storage management method for flash memory |

| CN111679787B (zh) | 2016-04-27 | 2023-07-18 | 慧荣科技股份有限公司 | 闪存装置、闪存控制器及闪存存储管理方法 |

| US10133664B2 (en) | 2016-04-27 | 2018-11-20 | Silicon Motion Inc. | Method, flash memory controller, memory device for accessing 3D flash memory having multiple memory chips |

| US10110255B2 (en) | 2016-04-27 | 2018-10-23 | Silicon Motion Inc. | Method for accessing flash memory module and associated flash memory controller and memory device |

| KR20170131796A (ko) * | 2016-05-20 | 2017-11-30 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| US10048873B2 (en) * | 2016-06-10 | 2018-08-14 | SK Hynix Inc. | Memory system for accessing memory dies during program operations and operation method thereof |

| US10049757B2 (en) * | 2016-08-11 | 2018-08-14 | SK Hynix Inc. | Techniques for dynamically determining performance of read reclaim operations |

| KR20180027710A (ko) * | 2016-09-06 | 2018-03-15 | 삼성전자주식회사 | 불휘발성 메모리 장치를 포함하는 스토리지 장치 및 불휘발성 메모리 장치의 액세스 방법 |

| KR20180040288A (ko) * | 2016-10-12 | 2018-04-20 | 삼성전자주식회사 | 비휘발성 메모리 장치의 리클레임 제어 방법, 상기 비휘발성 메모리 장치를 포함하는 저장 장치의 동작 방법 및 저장 장치 |

| CN106547488B (zh) * | 2016-10-21 | 2019-04-19 | 国家计算机网络与信息安全管理中心 | 一种混合缓存管理方法 |

| KR20180076715A (ko) * | 2016-12-28 | 2018-07-06 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작방법 |

| KR20180087496A (ko) * | 2017-01-23 | 2018-08-02 | 에스케이하이닉스 주식회사 | 메모리 시스템 |

| TWI602116B (zh) * | 2017-03-07 | 2017-10-11 | Silicon Motion Inc | 資料儲存裝置及其資料維護方法 |

| KR102224564B1 (ko) * | 2017-03-29 | 2021-03-09 | 에스케이하이닉스 주식회사 | 컨트롤러, 메모리 시스템 및 그것의 동작 방법 |

| US10572344B2 (en) | 2017-04-27 | 2020-02-25 | Texas Instruments Incorporated | Accessing error statistics from DRAM memories having integrated error correction |

| KR20180130140A (ko) * | 2017-05-29 | 2018-12-07 | 에스케이하이닉스 주식회사 | 데이터 처리 시스템 및 데이터 처리 방법 |

| US10453547B2 (en) * | 2017-06-16 | 2019-10-22 | Seagate Technologies Llc | Monitoring a memory for retirement |

| US10261914B2 (en) | 2017-08-25 | 2019-04-16 | Micron Technology, Inc. | Methods of memory address verification and memory devices employing the same |

| US11086790B2 (en) | 2017-08-25 | 2021-08-10 | Micron Technology, Inc. | Methods of memory address verification and memory devices employing the same |

| US10691536B2 (en) * | 2017-09-22 | 2020-06-23 | SK Hynix Inc. | Method to select flash memory blocks for refresh after read operations |

| KR20190052366A (ko) * | 2017-11-08 | 2019-05-16 | 에스케이하이닉스 주식회사 | 컨트롤러 및 컨트롤러의 동작방법 |

| US10521146B1 (en) | 2017-11-09 | 2019-12-31 | Micron Technology, Inc. | UFS based idle time garbage collection management |

| KR20190068197A (ko) * | 2017-12-08 | 2019-06-18 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작방법 |

| KR102468737B1 (ko) * | 2017-12-19 | 2022-11-21 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작방법 |

| KR20190085644A (ko) * | 2018-01-11 | 2019-07-19 | 에스케이하이닉스 주식회사 | 데이터 처리 시스템 및 그것의 동작 방법 |

| KR20190088184A (ko) * | 2018-01-18 | 2019-07-26 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| KR102513691B1 (ko) * | 2018-02-06 | 2023-03-27 | 에스케이하이닉스 주식회사 | 저장 장치 및 그 동작 방법 |

| US11163679B2 (en) * | 2018-04-04 | 2021-11-02 | SK Hynix Inc. | Garbage collection strategy for memory system and method of executing such garbage collection |

| KR102080089B1 (ko) * | 2018-05-18 | 2020-02-21 | 최영준 | 정전시 전력 소모를 감소시키기 위한 데이터 저장 방법 및 데이터 저장 장치 |

| KR102639696B1 (ko) * | 2018-05-23 | 2024-02-23 | 에스케이하이닉스 주식회사 | 메모리 시스템, 컨트롤러 및 그 동작방법 |

| CN109062503B (zh) * | 2018-07-10 | 2021-08-17 | 深圳忆联信息系统有限公司 | 提升ssd断电后读重试效率的方法、装置及计算机设备 |

| CN110910938A (zh) * | 2018-09-17 | 2020-03-24 | 北京兆易创新科技股份有限公司 | 一种数据纠正方法、装置、存储设备及存储介质 |

| WO2020087211A1 (en) | 2018-10-29 | 2020-05-07 | Micron Technology, Inc. | Slc cache allocation |

| KR20200054600A (ko) * | 2018-11-12 | 2020-05-20 | 삼성전자주식회사 | 스토리지 장치의 구동 방법, 이를 수행하는 스토리지 장치 및 이를 포함하는 스토리지 시스템 |

| US10990520B2 (en) * | 2018-12-10 | 2021-04-27 | Storart Technology Co., Ltd. | Method for gabage collecting for non-volatile memory |

| KR20200073017A (ko) * | 2018-12-13 | 2020-06-23 | 에스케이하이닉스 주식회사 | 데이터 저장 장치와, 그것의 동작 방법 |

| KR20200113990A (ko) * | 2019-03-27 | 2020-10-07 | 에스케이하이닉스 주식회사 | 메모리 시스템 내 메모리 장치의 동작 상태를 확인하는 방법 및 장치 |

| KR20200116265A (ko) * | 2019-04-01 | 2020-10-12 | 에스케이하이닉스 주식회사 | 컨트롤러 및 그것의 동작 방법 |

| CN111951857B (zh) * | 2019-05-15 | 2023-06-09 | 兆易创新科技集团股份有限公司 | 一种非易失性存储器的编程方法及控制装置 |

| US10790031B1 (en) * | 2019-06-05 | 2020-09-29 | Western Digital Technologies, Inc. | System handling for first read read disturb |

| KR20200142724A (ko) * | 2019-06-13 | 2020-12-23 | 에스케이하이닉스 주식회사 | 메모리 시스템, 메모리 컨트롤러 및 그 저장 방법 |

| US11119659B2 (en) * | 2019-08-12 | 2021-09-14 | Micron Technology, Inc. | Write buffer implementation for multiple memory array memory spaces |

| US11726869B2 (en) * | 2019-08-20 | 2023-08-15 | Micron Technology, Inc. | Performing error control operation on memory component for garbage collection |

| US11281578B2 (en) | 2019-08-20 | 2022-03-22 | Micron Technology, Inc. | Garbage collection in a memory sub-system during a low battery state |

| US11282567B2 (en) | 2019-08-20 | 2022-03-22 | Micron Technology, Inc. | Sequential SLC read optimization |

| KR20210046348A (ko) * | 2019-10-18 | 2021-04-28 | 삼성전자주식회사 | 복수의 프로세서들에 유연하게 메모리를 할당하기 위한 메모리 시스템 및 그것의 동작 방법 |

| KR20210108208A (ko) * | 2020-02-25 | 2021-09-02 | 에스케이하이닉스 주식회사 | 저장 장치 및 그 동작 방법 |

| US11288160B2 (en) * | 2020-08-17 | 2022-03-29 | Micron Technology, Inc. | Threshold voltage distribution adjustment for buffer |

| KR20220022355A (ko) | 2020-08-18 | 2022-02-25 | 삼성전자주식회사 | 멀티 페이지 데이터를 프로그램하기 위한 불휘발성 메모리 장치의 동작 방법 |

| US11580018B2 (en) * | 2021-04-25 | 2023-02-14 | Silicon Motion, Inc. | Method and apparatus for page validity management and related storage system |

| KR20230050695A (ko) * | 2021-10-08 | 2023-04-17 | 삼성전자주식회사 | 스토리지 장치 |

Family Cites Families (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1996024138A1 (fr) | 1995-01-31 | 1996-08-08 | Hitachi, Ltd. | Dispositif de memoire remanente et procede de regeneration |

| US5671388A (en) | 1995-05-03 | 1997-09-23 | Intel Corporation | Method and apparatus for performing write operations in multi-level cell storage device |

| US5930167A (en) | 1997-07-30 | 1999-07-27 | Sandisk Corporation | Multi-state non-volatile flash memory capable of being its own two state write cache |

| JP2001006374A (ja) | 1999-06-17 | 2001-01-12 | Hitachi Ltd | 半導体記憶装置及びシステム |

| US6675262B1 (en) * | 2001-06-08 | 2004-01-06 | Hewlett-Packard Company, L.P. | Multi-processor computer system with cache-flushing system using memory recall |

| US7253467B2 (en) | 2001-06-28 | 2007-08-07 | Samsung Electronics Co., Ltd. | Non-volatile semiconductor memory devices |

| JP2003015954A (ja) * | 2001-06-28 | 2003-01-17 | Sharp Corp | 半導体記憶装置および情報機器、半導体記憶装置のアクセス期間設定方法 |

| US20060180851A1 (en) | 2001-06-28 | 2006-08-17 | Samsung Electronics Co., Ltd. | Non-volatile memory devices and methods of operating the same |

| DE10228768A1 (de) | 2001-06-28 | 2003-01-16 | Samsung Electronics Co Ltd | Nicht-flüchtige Floating-Trap-Halbleiterspeichervorrichtungen, die Sperrisolationsschichten mit hohen Dielektrizitätskonstanten enthaltend, und Verfahren |

| US7012835B2 (en) | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| KR100568115B1 (ko) | 2004-06-30 | 2006-04-05 | 삼성전자주식회사 | 점진적 머지 방법 및 그것을 이용한 메모리 시스템 |

| KR100673020B1 (ko) | 2005-12-20 | 2007-01-24 | 삼성전자주식회사 | 전계효과 소오스/드레인 영역을 가지는 반도체 장치 |

| KR100764738B1 (ko) | 2006-04-06 | 2007-10-09 | 삼성전자주식회사 | 향상된 신뢰성을 갖는 상변화 메모리 장치, 그것의 쓰기방법, 그리고 그것을 포함한 시스템 |

| JP2007305210A (ja) * | 2006-05-10 | 2007-11-22 | Toshiba Corp | 半導体記憶装置 |

| US7444461B2 (en) | 2006-08-04 | 2008-10-28 | Sandisk Corporation | Methods for phased garbage collection |

| US7450425B2 (en) * | 2006-08-30 | 2008-11-11 | Micron Technology, Inc. | Non-volatile memory cell read failure reduction |

| US8074011B2 (en) * | 2006-12-06 | 2011-12-06 | Fusion-Io, Inc. | Apparatus, system, and method for storage space recovery after reaching a read count limit |

| US8006166B2 (en) | 2007-06-12 | 2011-08-23 | Micron Technology, Inc. | Programming error correction code into a solid state memory device with varying bits per cell |

| KR20090014036A (ko) * | 2007-08-03 | 2009-02-06 | 삼성전자주식회사 | 읽기 디스터번스로 인한 에러를 방지하는 메모리 시스템 및그 방법 |

| JP5096847B2 (ja) | 2007-09-10 | 2012-12-12 | 株式会社リコー | アクセス制御装置、アクセス制御方法、アクセス制御プログラム、記録媒体、記憶装置および画像処理装置 |

| KR100965768B1 (ko) * | 2007-12-26 | 2010-06-24 | 주식회사 하이닉스반도체 | 반도체 메모리 소자 |

| US8281061B2 (en) * | 2008-03-31 | 2012-10-02 | Micron Technology, Inc. | Data conditioning to improve flash memory reliability |

| US8843691B2 (en) | 2008-06-25 | 2014-09-23 | Stec, Inc. | Prioritized erasure of data blocks in a flash storage device |

| US8263623B2 (en) | 2008-07-11 | 2012-09-11 | Pfizer Inc. | Triazol derivatives useful for the treatment of diseases |

| KR101538803B1 (ko) | 2008-09-09 | 2015-07-22 | 삼성전자주식회사 | 펜 테이블로서 기능 할 수 있는 휴대용 전자장치 및 펜 테이블을 사용하는 컴퓨터 시스템 |

| US8040744B2 (en) | 2009-01-05 | 2011-10-18 | Sandisk Technologies Inc. | Spare block management of non-volatile memories |

| KR20100102925A (ko) | 2009-03-12 | 2010-09-27 | 삼성전자주식회사 | 리드 리클레임 신호를 발생하는 불휘발성 메모리 장치 및 이를 포함하는 메모리 시스템 |

| US8447918B2 (en) | 2009-04-08 | 2013-05-21 | Google Inc. | Garbage collection for failure prediction and repartitioning |

| KR101573850B1 (ko) | 2009-06-09 | 2015-12-02 | 삼성전자주식회사 | 마스킹 회로를 포함하는 데이터 처리 시스템과 그 방법 |

| US20100315325A1 (en) | 2009-06-16 | 2010-12-16 | Samsung Electronics Co., Ltd. | Light source unit and display apparatus including the same |

| US8307241B2 (en) | 2009-06-16 | 2012-11-06 | Sandisk Technologies Inc. | Data recovery in multi-level cell nonvolatile memory |

| EP2267724A1 (fr) * | 2009-06-26 | 2010-12-29 | STMicroelectronics Rousset SAS | Architecture de mémoire EEPROM optimisée pour les mémoires embarquées |

| US20100332922A1 (en) * | 2009-06-30 | 2010-12-30 | Mediatek Inc. | Method for managing device and solid state disk drive utilizing the same |

| US8634240B2 (en) * | 2009-10-28 | 2014-01-21 | SanDisk Technologies, Inc. | Non-volatile memory and method with accelerated post-write read to manage errors |

| US8423866B2 (en) | 2009-10-28 | 2013-04-16 | SanDisk Technologies, Inc. | Non-volatile memory and method with post-write read and adaptive re-write to manage errors |

| US8214700B2 (en) * | 2009-10-28 | 2012-07-03 | Sandisk Technologies Inc. | Non-volatile memory and method with post-write read and adaptive re-write to manage errors |

| JP2011128984A (ja) * | 2009-12-18 | 2011-06-30 | Toshiba Corp | メモリシステム |

| KR101727704B1 (ko) * | 2010-10-04 | 2017-04-18 | 삼성전자주식회사 | 리드 성능을 향상시킬 수 있는 리드 파라미터 변경 방법과 상기 방법을 수행할 수 있는 장치들 |

| JP2012089085A (ja) | 2010-10-22 | 2012-05-10 | Toshiba Corp | 半導体メモリ装置および半導体メモリシステム |

| US8886990B2 (en) * | 2011-01-27 | 2014-11-11 | Apple Inc. | Block management schemes in hybrid SLC/MLC memory |

| JP2013122793A (ja) * | 2011-12-09 | 2013-06-20 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8566671B1 (en) * | 2012-06-29 | 2013-10-22 | Sandisk Technologies Inc. | Configurable accelerated post-write read to manage errors |

| KR102025263B1 (ko) * | 2012-10-05 | 2019-09-25 | 삼성전자주식회사 | 메모리 시스템 및 그것의 읽기 교정 방법 |

-

2012

- 2012-10-05 KR KR1020120110859A patent/KR102025263B1/ko active IP Right Grant

-

2013

- 2013-09-26 US US14/037,658 patent/US9431117B2/en active Active

- 2013-10-07 JP JP2013210121A patent/JP6202972B2/ja active Active

- 2013-10-08 CN CN201310464864.4A patent/CN103714856B/zh active Active

-

2015

- 2015-06-30 US US14/754,884 patent/US9368223B2/en active Active

-

2016

- 2016-05-17 US US15/156,912 patent/US9672104B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9431117B2 (en) | 2016-08-30 |

| US20140101372A1 (en) | 2014-04-10 |

| CN103714856B (zh) | 2019-02-05 |

| US9368223B2 (en) | 2016-06-14 |

| KR20140044640A (ko) | 2014-04-15 |

| US20160259685A1 (en) | 2016-09-08 |

| CN103714856A (zh) | 2014-04-09 |

| US9672104B2 (en) | 2017-06-06 |

| US20150302928A1 (en) | 2015-10-22 |

| JP2014078229A (ja) | 2014-05-01 |

| KR102025263B1 (ko) | 2019-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6202972B2 (ja) | メモリシステム及びそれの読み出し校正方法 | |

| JP6072442B2 (ja) | メモリシステム及びそれの動作方法 | |

| JP5660615B2 (ja) | マルチビットメモリ装置を含んだデータ格納システム及びそれの動作方法 | |

| US9361985B2 (en) | Nonvolatile memory devices including simultaneous impedance calibration and input command | |

| US8812807B2 (en) | Nonvolatile memory device and operating method thereof | |

| US8934301B2 (en) | Memory controller for multi-level memory device and error correcting method | |

| US8665643B2 (en) | Non-volatile memory device and read method thereof | |

| US8432735B2 (en) | Memory system and related method of programming | |

| US9183938B2 (en) | Nonvolatile memory device and method of programming nonvolatile memory device | |

| US20140372714A1 (en) | Nonvolatile memory device and nonvolatile memory system and random data read method thereof | |

| US20140223084A1 (en) | Memory system and related method of operation | |

| KR101923157B1 (ko) | 메모리 시스템 및 그것의 프로그램 방법 | |

| US20130124783A1 (en) | Method of operating nonvolatile memory devices storing randomized data generated by copyback operation | |

| US8417879B2 (en) | Method for suppressing errors, and associated memory device and controller thereof | |

| JP2014175040A (ja) | メモリコントローラ及びそれを含むメモリシステム | |

| US20150228344A1 (en) | Partial page programming of nonvolatile memory device | |

| US20150143033A1 (en) | Controlling write speed of nonvolatile memory device | |

| US9189384B2 (en) | Memory system and memory managing method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20141226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161007 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161007 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161021 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170731 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170829 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6202972 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |