JP6196952B2 - 表示装置、表示モジュール、及び電子機器 - Google Patents

表示装置、表示モジュール、及び電子機器 Download PDFInfo

- Publication number

- JP6196952B2 JP6196952B2 JP2014181926A JP2014181926A JP6196952B2 JP 6196952 B2 JP6196952 B2 JP 6196952B2 JP 2014181926 A JP2014181926 A JP 2014181926A JP 2014181926 A JP2014181926 A JP 2014181926A JP 6196952 B2 JP6196952 B2 JP 6196952B2

- Authority

- JP

- Japan

- Prior art keywords

- scanning line

- transistor

- selection signal

- function

- scan line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3674—Details of drivers for scan electrodes

- G09G3/3677—Details of drivers for scan electrodes suitable for active matrices only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C19/00—Digital stores in which the information is moved stepwise, e.g. shift registers

- G11C19/28—Digital stores in which the information is moved stepwise, e.g. shift registers using semiconductor elements

- G11C19/287—Organisation of a multiplicity of shift registers

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134336—Matrix

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0814—Several active elements per pixel in active matrix panels used for selection purposes, e.g. logical AND for partial update

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0267—Details of drivers for scan electrodes, other than drivers for liquid crystal, plasma or OLED displays

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0286—Details of a shift registers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/08—Details of timing specific for flat panels, other than clock recovery

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0219—Reducing feedthrough effects in active matrix panels, i.e. voltage changes on the scan electrode influencing the pixel voltage due to capacitive coupling

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0223—Compensation for problems related to R-C delay and attenuation in electrodes of matrix panels, e.g. in gate electrodes or on-substrate video signal electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

Landscapes

- Engineering & Computer Science (AREA)

- Crystallography & Structural Chemistry (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Liquid Crystal (AREA)

- Shift Register Type Memory (AREA)

- Control Of El Displays (AREA)

- Electroluminescent Light Sources (AREA)

- Diaphragms For Electromechanical Transducers (AREA)

- Measuring Pulse, Heart Rate, Blood Pressure Or Blood Flow (AREA)

- Vehicle Body Suspensions (AREA)

Description

本発明の一態様の表示装置について、図1(A)を参照して説明する。図1(A)は、当該表示装置の一部を示す図である。図1(A)では、一端に選択信号(Sel)又は非選択信号(n−Sel)が入力される走査線10と、ゲートにクロック信号(CK)が入力され、ソースに非選択信号(n−Sel)が入力されるトランジスタ11とを示している。また、走査線10の他端はトランジスタ11のドレインと接続されている。そして、図1(A)に示す走査線10では、一端から入力される信号が選択信号(Sel)から非選択信号(n−Sel)に切り替わるタイミングが、トランジスタ11がオフ状態からオン状態となるタイミングと同一又は略同一となるように信号の入力が行われる。なお、図1(A)においては、トランジスタ11としてNチャネル型トランジスタを図示しているがトランジスタ11をPチャネル型トランジスタに置換してもよい。

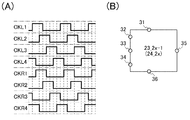

図4(A)は、表示装置の具体例を示す図である。図4(A)に示す表示装置は、m行n列(m、nは偶数)に配設されているm×n個の画素20と、当該画素間において紙面の左右方向に延在するm本の走査線21と、当該画素間において紙面の上下方向に延在するn本の信号線22と、各々が当該m本の走査線21に接続されている走査線駆動回路23、24と、当該n本の信号線22に接続されている信号線駆動回路25とを有する。

図4(B)は、図4(A)に示す表示装置が有する画素20の回路図の一例を示す図である。図4(B)に示す画素20は、ゲートが走査線21に接続され、ソース又はドレインの一方が信号線22に接続されているトランジスタ201と、一方の電極がトランジスタ201のソース又はドレインの他方に接続され、他方の電極が容量電位を供給する配線(容量線ともいう)に接続されている容量素子202と、一方の電極がトランジスタ201のソース又はドレインの他方及び容量素子202の一方の電極に接続され、他方の電極が共通電位を供給する配線(共通電位線ともいう)に電気的に接続されている液晶素子203とを有する。なお、容量電位と共通電位を同一の電位とすることが可能である。また、図4(B)においては、画素20に液晶素子203が設けられる構成を示しているが、本明細書で開示される表示装置の画素は当該構成に限定されない。例えば、本明細書で開示される表示装置においては、画素に発光素子を設けることも可能である。

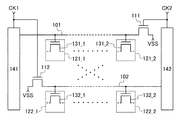

図5は、図4(A)に示す表示装置が有する走査線駆動回路23、24の構成例を示す図である。図5に示す走査線駆動回路23は、各々がクロック信号(CKL1乃至4)のいずれか一を供給する4本の配線と、各々が奇数行目に配設されている複数の走査線21_1、21_3・・・21_m−1のいずれか一に接続されている複数のパルス出力回路23_1、23_3・・・23_m−1と、各々のゲートが当該4本の配線のいずれか一に接続され、ソースが低電源電位(VSS)を供給する配線(以下、低電源電位線という)に接続され、且つドレインが偶数行目に配設された複数の走査線21_2、21_4・・・21_mのいずれか一に接続されている複数のトランジスタ23_2、23_4・・・23_mとを有する。また、図5に示す走査線駆動回路24は、各々がクロック信号(CKR1乃至4)のいずれか一を供給する4本の配線と、各々が偶数行目に配設されている複数の走査線21_2、21_4・・・21_mのいずれか一に接続されている複数のパルス出力回路24_2、24_4・・・24_mと、各々のゲートが当該4本の配線のいずれか一に接続され、ソースが低電源電位線に接続され、且つドレインが奇数行目に配設された複数の走査線21_1、21_3・・・21_m−1のいずれか一に接続されている複数のトランジスタ24_1、24_3・・・24_m−1とを有する。なお、図5に示す走査線駆動回路23においては、パルス出力回路23_1、23_3・・・23_m−1によってシフトレジスタが構成され、図5に示す走査線駆動回路24においては、パルス出力回路24_2、24_4・・・24_mによってシフトレジスタが構成されている。

図7(A)は、図5、図6(B)に示すパルス出力回路の構成例を示す図である。図7(A)に示すパルス出力回路は、トランジスタ41乃至49を有する。なお、パルス出力回路23_m−1、24_mにはトランジスタ43、44を設けなくてもよい。

上述したパルス出力回路の動作例について図7(B)、(C)を参照して説明する。なお、図7(B)は、パルス出力回路23_1に入出力される信号の波形、及びパルス出力回路23_1中のノードA、Bの電位を示す図であり、図7(C)は、パルス出力回路24_2に入出力される信号の波形、及びパルス出力回路24_2中のノードA、Bの電位を示す図である。なお、図7(B)、(C)中において、Goutは、パルス出力回路の走査線に対する出力信号を表し、SRoutは、当該パルス出力回路の後段に設けられているパルス出力回路に対する出力信号を表している。

トランジスタ23_2・・・23_m、24_1・・・24_m−1の動作例について、図8を参照して説明する。図8(A)は、図5の一部を抜粋した図であり、図8(B)は、図7(B)、(C)に示すパルス出力回路23_1、24_2が走査線21_1、21_2に出力する信号の波形及びトランジスタ23_2、24_1のゲートに入力されるクロック信号(CKR2、CKL3)を示す図である。

本明細書で開示される表示装置に設けられる走査線駆動回路23、24は、上述した回路に限定されない。例えば、トランジスタ23_2・・・23_m、24_1・・・24_m−1のゲートを、図5に示す様にクロック信号を供給する配線(CKL1乃至4、CKR1乃至4)のいずれか一に接続させる構成とするのではなく、パルス出力回路23_1・・・23_m−1、24_2・・・24_m−1のいずれか一の端子35に接続させる構成とすることも可能である。

上述した表示装置に含まれるトランジスタとしては、どのようなトランジスタを適用してもよい。例えば、シリコン膜にチャネルが形成されるトランジスタ(シリコン膜にチャネル形成領域を有するトランジスタ)又は酸化物半導体膜にチャネルが形成されるトランジスタ(酸化物半導体膜にチャネル形成領域を有するトランジスタ)を上述した表示装置に含まれるトランジスタとして適用することが可能である。

以下では、上述した表示装置を構成要素の一とする表示モジュールについて、図10を参照して説明する。

以下では、上述した表示装置を用いて製造される最終製品の一例について、図11、12を参照して説明する。

101 走査線

102 走査線

11 トランジスタ

111 トランジスタ

112 トランジスタ

12_1 画素

12_2 画素

121_1 画素

121_2 画素

122_1 画素

122_2 画素

13_1 トランジスタ

13_2 トランジスタ

131_1 トランジスタ

131_2 トランジスタ

132_1 トランジスタ

132_2 トランジスタ

14 トランジスタ

15_1 トランジスタ

15_2 トランジスタ

141 シフトレジスタ

142 シフトレジスタ

20 画素

201 トランジスタ

202 容量素子

203 液晶素子

21 走査線

21_1〜21_m 走査線

22 信号線

23 走査線駆動回路

24 走査線駆動回路

23_1 パルス出力回路

23_3 パルス出力回路

23_5 パルス出力回路

23_m−1 パルス出力回路

24_2 パルス出力回路

24_4 パルス出力回路

24_m パルス出力回路

23_2 トランジスタ

23_4 トランジスタ

23_m トランジスタ

24_1 トランジスタ

24_3 トランジスタ

24_5 トランジスタ

24_m−1 トランジスタ

25 信号線駆動回路

31〜36 端子

41〜49 トランジスタ

7100 バングル型の表示装置

7101 筐体

7102 表示部

7103 操作ボタン

7104 送受信装置

7300 携帯用製品

7301 筐体

7302 表示部

7303 操作ボタン

7304 引き出し部材

7305 制御部

7400 携帯電話機

7401 筐体

7402 表示部

7403 操作ボタン

7404 外部接続ポート

7405 スピーカ

7406 マイク

8000 表示モジュール

8001 上部カバー

8002 下部カバー

8003 FPC

8004 タッチパネル

8005 FPC

8006 表示パネル

8007 バックライトユニット

8008 光源

8009 フレーム

8010 プリント基板

8011 バッテリー

Claims (18)

- 第1の走査線と、第2の走査線と、第1のスイッチと、第2のスイッチと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のスイッチを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のスイッチを介して供給され、

前記第1のスイッチと前記第2のスイッチとの間には、画素部が位置し、

前記第1のスイッチのオンまたはオフは、前記第2の走査線駆動回路によって制御されており、

前記第2のスイッチのオンまたはオフは、前記第1の走査線駆動回路によって制御されている表示装置。 - 第1の走査線と、第2の走査線と、第1のスイッチと、第2のスイッチと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のスイッチを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のスイッチを介して供給され、

前記第1のスイッチの第1の端子は、前記第2のスイッチの第1の端子と同じ電位が与えられており、

前記第1のスイッチの第2の端子は、前記第1の走査線と電気的に接続されており、

前記第2のスイッチの第2の端子は、前記第2の走査線と電気的に接続されており、

前記第1のスイッチと前記第2のスイッチとの間には、画素部が位置し、

前記第1のスイッチのオンまたはオフは、前記第2の走査線駆動回路によって制御されており、

前記第2のスイッチのオンまたはオフは、前記第1の走査線駆動回路によって制御されている表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のスイッチと、第2のスイッチと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のスイッチを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のスイッチを介して供給され、

前記第1のスイッチのオンまたはオフは、前記第2の走査線の電位に従って制御されており、

前記第2のスイッチのオンまたはオフは、前記第4の走査線の電位に従って制御されており、

前記第1のスイッチと前記第2のスイッチとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のスイッチと、第2のスイッチと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のスイッチを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のスイッチを介して供給され、

前記第1のスイッチのオンまたはオフは、前記第2の走査線の電位に従って制御されており、

前記第2のスイッチのオンまたはオフは、前記第4の走査線の電位に従って制御されており、

前記第1のスイッチの第1の端子は、前記第2のスイッチの第1の端子と同じ電位が与えられており、

前記第1のスイッチの第2の端子は、前記第1の走査線と電気的に接続されており、

前記第2のスイッチの第2の端子は、前記第3の走査線と電気的に接続されており、

前記第1のスイッチと前記第2のスイッチとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有する表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのオンまたはオフは、前記第2の走査線駆動回路によって制御されており、

前記第2のトランジスタのオンまたはオフは、前記第1の走査線駆動回路によって制御されている表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第2の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのオンまたはオフは、前記第2の走査線駆動回路によって制御されており、

前記第2のトランジスタのオンまたはオフは、前記第1の走査線駆動回路によって制御されている表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有する表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのゲートは、前記第2の走査線駆動回路に電気的に接続されており、

前記第2のトランジスタのゲートは、前記第1の走査線駆動回路に電気的に接続されており、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域に酸化物半導体を有する表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第2の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのゲートは、前記第2の走査線駆動回路に電気的に接続されており、

前記第2のトランジスタのゲートは、前記第1の走査線駆動回路に電気的に接続されており、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域に酸化物半導体を有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有し、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域に酸化物半導体を有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有し、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域に酸化物半導体を有する表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのゲートは、前記第2の走査線駆動回路に電気的に接続されており、

前記第2のトランジスタのゲートは、前記第1の走査線駆動回路に電気的に接続されており、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域にシリコンを有する表示装置。 - 第1の走査線と、第2の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第2の走査線の一端から第2の選択信号を前記第2の走査線に供給する機能と、前記第2の走査線の一端から第2の非選択信号を前記第2の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第2の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第2の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1のトランジスタのゲートは、前記第2の走査線駆動回路に電気的に接続されており、

前記第2のトランジスタのゲートは、前記第1の走査線駆動回路に電気的に接続されており、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域にシリコンを有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有し、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域にシリコンを有する表示装置。 - 第1の走査線と、第2の走査線と、第3の走査線と、第4の走査線と、第1のトランジスタと、第2のトランジスタと、第1の走査線駆動回路と、第2の走査線駆動回路と、を有し、

前記第1の走査線駆動回路は、前記第1の走査線の一端から第1の選択信号を前記第1の走査線に供給する機能と、前記第1の走査線の一端から第1の非選択信号を前記第1の走査線に供給する機能と、を有し、

前記第2の走査線駆動回路は、前記第3の走査線の一端から第2の選択信号を前記第3の走査線に供給する機能と、前記第3の走査線の一端から第2の非選択信号を前記第3の走査線に供給する機能と、を有し、

前記第1の走査線の他端には、前記第1の選択信号と前記第1の非選択信号のうち前記第1の非選択信号のみが前記第1のトランジスタを介して供給され、

前記第3の走査線の他端には、前記第2の選択信号と前記第2の非選択信号のうち前記第2の非選択信号のみが前記第2のトランジスタを介して供給され、

前記第1のトランジスタのゲートは、前記第2の走査線と電気的に接続されており、

前記第2のトランジスタのゲートは、前記第4の走査線と電気的に接続されており、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と同じ電位が与えられており、

前記第1のトランジスタのソース又はドレインの他方は、前記第1の走査線と電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記第3の走査線と電気的に接続されており、

前記第1のトランジスタと前記第2のトランジスタとの間には、画素部が位置し、

前記第1の走査線駆動回路は、前記第4の走査線の電位を制御する機能を有し、

前記第2の走査線駆動回路は、前記第2の走査線の電位を制御する機能を有し、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル形成領域にシリコンを有する表示装置。 - 請求項1乃至請求項16のいずれか一に記載の表示装置と、FPCと、を有する表示モジュール。

- 請求項17に記載の表示モジュールと、筐体、操作ボタン、スピーカ、またはマイクと、を有する電子機器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014181926A JP6196952B2 (ja) | 2013-09-12 | 2014-09-08 | 表示装置、表示モジュール、及び電子機器 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013189539 | 2013-09-12 | ||

| JP2013189539 | 2013-09-12 | ||

| JP2014181926A JP6196952B2 (ja) | 2013-09-12 | 2014-09-08 | 表示装置、表示モジュール、及び電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017092023A Division JP2017161925A (ja) | 2013-09-12 | 2017-05-03 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015079242A JP2015079242A (ja) | 2015-04-23 |

| JP2015079242A5 JP2015079242A5 (ja) | 2016-03-31 |

| JP6196952B2 true JP6196952B2 (ja) | 2017-09-13 |

Family

ID=52625099

Family Applications (7)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014181926A Active JP6196952B2 (ja) | 2013-09-12 | 2014-09-08 | 表示装置、表示モジュール、及び電子機器 |

| JP2017092023A Withdrawn JP2017161925A (ja) | 2013-09-12 | 2017-05-03 | 表示装置 |

| JP2019086998A Withdrawn JP2019148820A (ja) | 2013-09-12 | 2019-04-29 | 表示装置 |

| JP2021025370A Withdrawn JP2021101240A (ja) | 2013-09-12 | 2021-02-19 | 表示装置 |

| JP2021126497A Withdrawn JP2021185422A (ja) | 2013-09-12 | 2021-08-02 | 表示装置 |

| JP2023076511A Withdrawn JP2023103314A (ja) | 2013-09-12 | 2023-05-08 | 表示装置 |

| JP2024153365A Withdrawn JP2024174954A (ja) | 2013-09-12 | 2024-09-05 | 表示装置 |

Family Applications After (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017092023A Withdrawn JP2017161925A (ja) | 2013-09-12 | 2017-05-03 | 表示装置 |

| JP2019086998A Withdrawn JP2019148820A (ja) | 2013-09-12 | 2019-04-29 | 表示装置 |

| JP2021025370A Withdrawn JP2021101240A (ja) | 2013-09-12 | 2021-02-19 | 表示装置 |

| JP2021126497A Withdrawn JP2021185422A (ja) | 2013-09-12 | 2021-08-02 | 表示装置 |

| JP2023076511A Withdrawn JP2023103314A (ja) | 2013-09-12 | 2023-05-08 | 表示装置 |

| JP2024153365A Withdrawn JP2024174954A (ja) | 2013-09-12 | 2024-09-05 | 表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (7) | US9583063B2 (ja) |

| JP (7) | JP6196952B2 (ja) |

| KR (6) | KR102243098B1 (ja) |

| TW (6) | TWI696164B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5485811B2 (ja) * | 2010-06-23 | 2014-05-07 | 株式会社ジャパンディスプレイ | 双方向シフトレジスタ、及びこれを用いた画像表示装置 |

| CN104751769A (zh) * | 2013-12-25 | 2015-07-01 | 昆山工研院新型平板显示技术中心有限公司 | 扫描驱动器及使用该扫描驱动器的有机发光显示器 |

| WO2018163938A1 (ja) * | 2017-03-07 | 2018-09-13 | シャープ株式会社 | アクティブ基板、それを備えた表示装置 |

| CN110262147B (zh) * | 2018-08-10 | 2021-10-29 | 友达光电股份有限公司 | 半导体基板及驱动方法 |

| TWI703554B (zh) * | 2019-07-11 | 2020-09-01 | 友達光電股份有限公司 | 具影像掃描功能之顯示裝置與掃描方法 |

| CN111624827B (zh) * | 2020-06-28 | 2023-01-10 | 京东方科技集团股份有限公司 | 阵列基板、显示面板和显示装置 |

| CN111883077A (zh) | 2020-07-28 | 2020-11-03 | 北海惠科光电技术有限公司 | 栅极驱动电路、显示模组及显示装置 |

| CN112596314A (zh) * | 2020-12-10 | 2021-04-02 | Tcl华星光电技术有限公司 | 显示面板 |

| CN112820246A (zh) * | 2021-01-04 | 2021-05-18 | Tcl华星光电技术有限公司 | Tft阵列基板 |

| KR102833886B1 (ko) * | 2021-03-15 | 2025-07-16 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 구동 방법 |

| CN117456874A (zh) * | 2023-10-24 | 2024-01-26 | 深圳市华星光电半导体显示技术有限公司 | 栅极驱动电路及显示面板 |

Family Cites Families (80)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH067239B2 (ja) | 1987-08-14 | 1994-01-26 | セイコー電子工業株式会社 | 電気光学装置 |

| JP2739821B2 (ja) | 1994-03-30 | 1998-04-15 | 日本電気株式会社 | 液晶表示装置 |

| JPH07294882A (ja) | 1994-04-22 | 1995-11-10 | Sony Corp | アクティブマトリクス表示装置 |

| JP3271484B2 (ja) | 1995-08-28 | 2002-04-02 | ソニー株式会社 | 液晶表示装置 |

| JPH09146489A (ja) | 1995-11-20 | 1997-06-06 | Sharp Corp | 走査回路および画像表示装置 |

| JP2959509B2 (ja) | 1997-03-11 | 1999-10-06 | 日本電気株式会社 | 液晶表示装置 |

| JP3246546B2 (ja) | 1998-07-14 | 2002-01-15 | 村田機械株式会社 | 単錘駆動型多重撚糸機 |

| WO2001006484A1 (en) | 1999-07-14 | 2001-01-25 | Sony Corporation | Current drive circuit and display comprising the same, pixel circuit, and drive method |

| US7379039B2 (en) | 1999-07-14 | 2008-05-27 | Sony Corporation | Current drive circuit and display device using same pixel circuit, and drive method |

| JP2002055660A (ja) * | 2000-08-11 | 2002-02-20 | Casio Comput Co Ltd | 電子装置 |

| US7385579B2 (en) * | 2000-09-29 | 2008-06-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and method of driving the same |

| JP4011320B2 (ja) | 2001-10-01 | 2007-11-21 | 株式会社半導体エネルギー研究所 | 表示装置及びそれを用いた電子機器 |

| US7180479B2 (en) | 2001-10-30 | 2007-02-20 | Semiconductor Energy Laboratory Co., Ltd. | Signal line drive circuit and light emitting device and driving method therefor |

| CN100354903C (zh) | 2001-12-27 | 2007-12-12 | 株式会社瑞萨科技 | 显示驱动控制系统 |

| JP4115763B2 (ja) | 2002-07-10 | 2008-07-09 | パイオニア株式会社 | 表示装置及び表示方法 |

| KR100499572B1 (ko) * | 2002-12-31 | 2005-07-07 | 엘지.필립스 엘시디 주식회사 | 액정 표시 장치 |

| US7122969B2 (en) | 2003-06-18 | 2006-10-17 | Semiconductor Energy Laboratory Co., Ltd. | Element substrate and light emitting device |

| JP4801329B2 (ja) | 2003-06-18 | 2011-10-26 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP2005250382A (ja) | 2004-03-08 | 2005-09-15 | Seiko Epson Corp | 電気光学装置の駆動方法、電気光学装置および電子機器 |

| JP2005321457A (ja) * | 2004-05-06 | 2005-11-17 | Seiko Epson Corp | 走査線駆動回路、表示装置及び電子機器 |

| US7332742B2 (en) | 2004-06-29 | 2008-02-19 | Semiconductor Energy Laboratory Co., Ltd. | Display device and electronic apparatus |

| JP4207017B2 (ja) * | 2004-08-10 | 2009-01-14 | セイコーエプソン株式会社 | 電気光学装置用基板及びその検査方法、並びに電気光学装置及び電子機器 |

| KR101239162B1 (ko) * | 2004-11-30 | 2013-03-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시장치와 그 구동방법, 반도체장치, 및 전자기기 |

| KR101112213B1 (ko) * | 2005-03-30 | 2012-02-27 | 삼성전자주식회사 | 게이트 구동회로 및 이를 갖는 표시장치 |

| KR20060109343A (ko) | 2005-04-15 | 2006-10-19 | 세이코 엡슨 가부시키가이샤 | 전자 회로, 그 구동 방법, 전기 광학 장치, 및 전자 기기 |

| US7928938B2 (en) * | 2005-04-19 | 2011-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including memory circuit, display device and electronic apparatus |

| EP1720148A3 (en) * | 2005-05-02 | 2007-09-05 | Semiconductor Energy Laboratory Co., Ltd. | Display device and gray scale driving method with subframes thereof |

| TWI429327B (zh) * | 2005-06-30 | 2014-03-01 | Semiconductor Energy Lab | 半導體裝置、顯示裝置、及電子設備 |

| US20070001954A1 (en) * | 2005-07-04 | 2007-01-04 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method of display device |

| US8692740B2 (en) * | 2005-07-04 | 2014-04-08 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof |

| WO2007013646A1 (en) * | 2005-07-29 | 2007-02-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device and driving method thereof |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| US7432737B2 (en) * | 2005-12-28 | 2008-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| TWI430234B (zh) | 2006-04-05 | 2014-03-11 | Semiconductor Energy Lab | 半導體裝置,顯示裝置,和電子裝置 |

| US8330492B2 (en) | 2006-06-02 | 2012-12-11 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and electronic device |

| US8441424B2 (en) | 2006-06-29 | 2013-05-14 | Lg Display Co., Ltd. | Liquid crystal display device and method of driving the same |

| US7781768B2 (en) | 2006-06-29 | 2010-08-24 | Semiconductor Energy Laboratory Co., Ltd. | Display device, method for manufacturing the same, and electronic device having the same |

| JP4240068B2 (ja) * | 2006-06-30 | 2009-03-18 | ソニー株式会社 | 表示装置及びその駆動方法 |

| JP4168290B2 (ja) | 2006-08-03 | 2008-10-22 | ソニー株式会社 | 表示装置 |

| EP1895545B1 (en) | 2006-08-31 | 2014-04-23 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| JP2008070406A (ja) * | 2006-09-12 | 2008-03-27 | Hitachi Displays Ltd | 液晶表示装置 |

| JP4932415B2 (ja) | 2006-09-29 | 2012-05-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5116277B2 (ja) * | 2006-09-29 | 2013-01-09 | 株式会社半導体エネルギー研究所 | 半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器 |

| TWI675358B (zh) * | 2006-09-29 | 2019-10-21 | 日商半導體能源研究所股份有限公司 | 顯示裝置和電子裝置 |

| JP4256888B2 (ja) | 2006-10-13 | 2009-04-22 | 株式会社 日立ディスプレイズ | 表示装置 |

| JP2008152096A (ja) | 2006-12-19 | 2008-07-03 | Sony Corp | 表示装置、表示装置の駆動方法および電子機器 |

| JP5508662B2 (ja) * | 2007-01-12 | 2014-06-04 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2008216436A (ja) | 2007-03-01 | 2008-09-18 | Necディスプレイソリューションズ株式会社 | 画像表示装置 |

| JP2008233123A (ja) * | 2007-03-16 | 2008-10-02 | Sony Corp | 表示装置 |

| JP5309470B2 (ja) * | 2007-05-21 | 2013-10-09 | ソニー株式会社 | 表示装置及びその駆動方法と電子機器 |

| JP5317442B2 (ja) | 2007-07-18 | 2013-10-16 | 三菱電機株式会社 | 画像表示装置及び画像表示装置の駆動方法 |

| JP4981928B2 (ja) * | 2007-12-28 | 2012-07-25 | シャープ株式会社 | 表示駆動回路及び表示装置 |

| US20100315403A1 (en) * | 2008-02-19 | 2010-12-16 | Shotaro Kaneyoshi | Display device, method for driving the display device, and scan signal line driving circuit |

| JP2010002812A (ja) | 2008-06-23 | 2010-01-07 | Videocon Industries Ltd | 液晶表示装置 |

| JP5484109B2 (ja) | 2009-02-09 | 2014-05-07 | 三菱電機株式会社 | 電気光学装置 |

| TWI401663B (zh) * | 2009-03-13 | 2013-07-11 | Au Optronics Corp | 具雙向穩壓功能之液晶顯示裝置 |

| KR102071057B1 (ko) | 2009-06-25 | 2020-01-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 |

| JP5493547B2 (ja) * | 2009-07-29 | 2014-05-14 | 株式会社Jvcケンウッド | 液晶表示装置及び液晶表示装置の駆動方法 |

| WO2011033909A1 (en) | 2009-09-16 | 2011-03-24 | Semiconductor Energy Laboratory Co., Ltd. | Driver circuit, display device including the driver circuit, and electronic device including the display device |

| CN104681568B (zh) * | 2009-10-21 | 2017-11-21 | 株式会社半导体能源研究所 | 显示装置和包括显示装置的电子设备 |

| KR102329497B1 (ko) * | 2009-11-13 | 2021-11-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 표시 장치 및 이 표시 장치를 구비한 전자 기기 |

| KR101747421B1 (ko) | 2010-01-20 | 2017-06-14 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 표시 장치의 구동 방법 |

| JP2011164534A (ja) | 2010-02-15 | 2011-08-25 | Hitachi Displays Ltd | 表示装置 |

| KR101710661B1 (ko) * | 2010-04-29 | 2017-02-28 | 삼성디스플레이 주식회사 | 게이트 구동회로 및 이를 갖는 표시장치 |

| JP5669453B2 (ja) * | 2010-06-22 | 2015-02-12 | 株式会社ジャパンディスプレイ | 双方向シフトレジスタ、及びこれを用いた画像表示装置 |

| JP5485811B2 (ja) | 2010-06-23 | 2014-05-07 | 株式会社ジャパンディスプレイ | 双方向シフトレジスタ、及びこれを用いた画像表示装置 |

| WO2012002040A1 (en) | 2010-07-01 | 2012-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Driving method of liquid crystal display device |

| US9336739B2 (en) * | 2010-07-02 | 2016-05-10 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device |

| TWI541782B (zh) * | 2010-07-02 | 2016-07-11 | 半導體能源研究所股份有限公司 | 液晶顯示裝置 |

| JP5839896B2 (ja) | 2010-09-09 | 2016-01-06 | 株式会社半導体エネルギー研究所 | 表示装置 |

| KR20120033672A (ko) * | 2010-09-30 | 2012-04-09 | 삼성모바일디스플레이주식회사 | 구동 장치 및 이를 포함하는 표시 장치 |

| CN103229229B (zh) * | 2010-11-25 | 2016-05-25 | 夏普株式会社 | 显示装置 |

| KR101262472B1 (ko) | 2010-12-06 | 2013-05-08 | 국민대학교산학협력단 | 컨버터블 차량용 루프장치 |

| KR101778650B1 (ko) | 2011-02-23 | 2017-09-15 | 삼성디스플레이 주식회사 | 표시 패널 및 이를 포함하는 표시 장치 |

| DE112012002065T5 (de) * | 2011-05-13 | 2014-02-20 | Semiconductor Energy Laboratory Co., Ltd. | Anzeigevorrichtung |

| JP5842263B2 (ja) * | 2011-06-08 | 2016-01-13 | 株式会社Joled | 表示素子、表示装置、及び、電子機器 |

| JP2013084333A (ja) * | 2011-09-28 | 2013-05-09 | Semiconductor Energy Lab Co Ltd | シフトレジスタ回路 |

| WO2013080845A1 (en) | 2011-11-30 | 2013-06-06 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| KR101975533B1 (ko) * | 2012-06-29 | 2019-05-08 | 삼성디스플레이 주식회사 | 구동회로, 그를 구비하는 평판표시장치 및 구동회로의 리페어 방법 |

| CN202838908U (zh) | 2012-09-20 | 2013-03-27 | 北京京东方光电科技有限公司 | 栅极驱动电路、阵列基板和显示装置 |

-

2014

- 2014-09-02 US US14/474,330 patent/US9583063B2/en active Active

- 2014-09-04 KR KR1020140117660A patent/KR102243098B1/ko not_active Expired - Fee Related

- 2014-09-08 JP JP2014181926A patent/JP6196952B2/ja active Active

- 2014-09-11 TW TW107144907A patent/TWI696164B/zh active

- 2014-09-11 TW TW113128792A patent/TW202447595A/zh unknown

- 2014-09-11 TW TW111141503A patent/TWI854342B/zh active

- 2014-09-11 TW TW111115492A patent/TWI783900B/zh active

- 2014-09-11 TW TW103131369A patent/TWI652666B/zh active

- 2014-09-11 TW TW109114824A patent/TWI764142B/zh not_active IP Right Cessation

-

2017

- 2017-02-15 US US15/433,629 patent/US9852708B2/en active Active

- 2017-05-03 JP JP2017092023A patent/JP2017161925A/ja not_active Withdrawn

- 2017-12-22 US US15/852,669 patent/US10147378B2/en active Active

-

2018

- 2018-11-14 US US16/190,205 patent/US10885861B2/en active Active

-

2019

- 2019-04-29 JP JP2019086998A patent/JP2019148820A/ja not_active Withdrawn

-

2020

- 2020-12-28 US US17/134,724 patent/US11636819B2/en active Active

-

2021

- 2021-02-19 JP JP2021025370A patent/JP2021101240A/ja not_active Withdrawn

- 2021-04-13 KR KR1020210047559A patent/KR102283092B1/ko active Active

- 2021-07-09 KR KR1020210090285A patent/KR102322936B1/ko active Active

- 2021-08-02 JP JP2021126497A patent/JP2021185422A/ja not_active Withdrawn

- 2021-10-27 KR KR1020210144523A patent/KR20210134537A/ko not_active Ceased

-

2023

- 2023-02-16 KR KR1020230020572A patent/KR102737828B1/ko active Active

- 2023-04-20 US US18/137,259 patent/US12142238B2/en active Active

- 2023-05-08 JP JP2023076511A patent/JP2023103314A/ja not_active Withdrawn

-

2024

- 2024-09-05 JP JP2024153365A patent/JP2024174954A/ja not_active Withdrawn

- 2024-11-08 US US18/941,372 patent/US20250140216A1/en active Pending

- 2024-11-28 KR KR1020240173444A patent/KR20250003380A/ko active Pending

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6196952B2 (ja) | 表示装置、表示モジュール、及び電子機器 | |

| TWI584251B (zh) | 半導體裝置和顯示裝置 | |

| JP6352070B2 (ja) | 半導体装置 | |

| TW202215409A (zh) | 半導體裝置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160209 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160209 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161121 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170418 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170607 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170801 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170821 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6196952 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |