JP6133476B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6133476B2 JP6133476B2 JP2016126148A JP2016126148A JP6133476B2 JP 6133476 B2 JP6133476 B2 JP 6133476B2 JP 2016126148 A JP2016126148 A JP 2016126148A JP 2016126148 A JP2016126148 A JP 2016126148A JP 6133476 B2 JP6133476 B2 JP 6133476B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- protrusions

- pair

- semiconductor film

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0231—Manufacture or treatment of multiple TFTs using masks, e.g. half-tone masks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

Description

子および装置全般を指す。例えば、該素子の代表例はトランジスタである。該トランジス

タを含む表示装置、半導体回路および電子機器は全て半導体装置に含まれる。

晶表示装置や発光表示装置などの画素におけるスイッチング素子として用いられている。

また、トランジスタは液晶表示装置や発光表示装置などだけではなく、スイッチング特性

を利用して半導体記憶装置にも用いられている。

cess Memory)は、トランジスタとキャパシタでメモリセルが構成されている

。そして、DRAMにおいて、チップサイズの増大を抑えつつ、半導体集積回路の集積度

をより高くするためには、メモリセルの面積を縮小する目的としたトランジスタの微細化

が必要である。

い値電圧がマイナス方向へ変動するなど電気特性に変動が生じる。この現象は短チャネル

効果と呼ばれ、短チャネル効果を抑制することは、トランジスタの微細化において重要な

課題である。

チスルー現象によるリーク電流が流れやすくなり、スイッチング特性が機能しなくなるこ

ともある。該リーク電流を防ぐには、シリコン基板に高濃度の不純物をドーピングすれば

よいが、そうするとソースとシリコン基板間またはドレインとシリコン基板間に接合リー

ク電流が流れやすくなり、結局はメモリの保持特性を低下させてしまう原因となってしま

い、この問題の解決策としては適切ではなかった。

ランジスタの実効上のチャネル長を短チャネル効果が生じない程度に維持する方法が考え

られてきた。例えば、トランジスタのチャネル部が形成される領域にU字状の縦長溝を形

成し、該縦長溝の壁面に沿ってゲート絶縁膜を形成し、さらに該縦長溝にゲート電極を埋

め込んだ構造である(非特許文献1参照)。

電流が縦長溝部分を回り込む形で流れるため、上面から見たトランジスタのソース電極お

よびドレイン電極間の距離である見かけ上のチャネル長に対して、実効上のチャネル長が

長くなっている。このため、トランジスタのサイズを縮小しつつ、短チャネル効果を抑制

できるといった効果を奏する。

が、上記のように、U字状の縦長溝を設ける構造とするトランジスタは、該縦長溝を形成

する際に溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留

まりの観点で問題があった。

CVD(Chemical Vapor Deposition)法では、該縦長溝の入

り口付近に膜が堆積し、溝が塞がってしまうことがあった。そのため、被覆性の高い成膜

方法を選定する必要があった。具体的には、比較的コスト高となる原子層堆積法(ALD

:Atomic Layer Deposition)法、またはシリコンウェハなどで

しか使用できない熱酸化法などに限られることが問題であった。

実効上のチャネル長を長くすることができるトランジスタを提供することを課題の一とす

る。

ネル長を長くすることによって、トランジスタのオフ電流またはリーク電流を低減させる

ことができるが、このようにすることで、トランジスタのオン電流も低減してしまう。

とは、トランジスタを半導体記憶装置に用いる際に有用である。例えば、半導体記憶装置

に設けられる読み出し回路において、読み出すことが可能な電流値の範囲を大きくするこ

とができる。そのため、短チャネル効果を抑制するために実効上のチャネル長を長くした

トランジスタにおいて、オン電流を増大させて、トランジスタのオン・オフ比を充分に確

保することは有意なことである。

できるトランジスタ、および良好なスイッチング特性を有するトランジスタを提供するこ

とを課題とする。

ランジスタを上面から見た場合、ソース電極およびドレイン電極となる一対の電極間の距

離に相当する見かけ上のチャネル長に対して、実効上のチャネル長に相当するソースおよ

びドレイン間を流れるキャリアの経路の距離を長くするということである。

対して実効上のチャネル長を長くするための手段は、該トランジスタのゲート電極として

、半導体膜のチャネル幅方向に延伸した突起が設けられたゲート電極を用いることである

。

極として機能する一対の電極幅に相当するチャネル幅を広くすればよいが、トランジスタ

のサイズを縮小しつつ、該チャネル幅を広くする必要がある。

電極として、半導体膜のチャネル幅方向に延伸した突起と、該チャネル幅方向に延伸した

突起を介して対向した一対の突起とが設けられたゲート電極を用いることで、実効上のチ

ャネル長を長くさせつつ、さらに、トランジスタを上面から見た場合の該一対の電極幅に

相当する見かけ上のチャネル幅より、トランジスタの動作時に機能する実効上のチャネル

幅を広くすることができる。

ことから、「半導体膜のチャネル幅」は、「トランジスタのチャネル幅」と言い換えるこ

とができる。そして、「半導体膜のチャネル長」についても「トランジスタのチャネル長

」と言い換えることができる。また、「半導体膜のチャネル幅方向」または「トランジス

タのチャネル幅方向」を、単に「チャネル幅方向」と記し、「半導体膜のチャネル長方向

」または「トランジスタのチャネル長方向」を、単に「チャネル長方向」と記す場合があ

る。

起とを有するゲート電極と、ゲート電極を覆うゲート絶縁膜と、ゲート絶縁膜と接して、

且つ一対の第1の突起および第2の突起に重畳する半導体膜と、半導体膜と接して、且つ

一対の第1の突起と重畳する一対の電極と、を有し、半導体膜の側端は、半導体膜のチャ

ネル幅方向において、一対の第1の突起の頂面より外側であり、一対の電極の側端は、半

導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側である、半導体装置

である。

複数設けることで、トランジスタを上面から見た場合の該一対の電極幅に相当する見かけ

上のチャネル幅に対して、実効上のチャネル幅をさらに広くすることができる。

数設けられている半導体装置である。

ャネル幅方向における一対の電極の側端は、複数設けられた一対の突起のうち異なる一対

の突起の頂面上であってもよい。

けられる第2の突起とを有するゲート電極と、ゲート電極を覆うゲート絶縁膜と、ゲート

絶縁膜と接して、且つ複数の一対の第1の突起および第2の突起に重畳する半導体膜と、

半導体膜と接し、且つ複数の一対の第1の突起に重畳する一対の電極と、を有し、半導体

膜の側端は、半導体膜のチャネル幅方向において、複数の一対の第1の突起のうち異なる

一対の第1の突起の頂面上にあり、一対の電極の側端は、半導体膜のチャネル幅方向にお

いて、複数の一対の第1の突起のうち異なる一対の第1の突起の頂面上にある、半導体装

置である。

のチャネル長に対して、トランジスタの動作時に機能する実効上のチャネル長をさらに長

くすることができる。

れている半導体装置である。

てチャネル幅方向に延伸した突起を含む領域と、該領域以外の領域と、で構成されている

ものとみなすことができる。そこで、2つの領域は、互いに異なる導電材料によって構成

されていてもよい。その際、互いの領域を構成する導電材料の仕事関数の差は、0.6e

V以下とすることが好ましい。

含む第1の領域と、第1の領域以外の第2の領域とを有し、第1の領域と第2の領域は、

異なる導電材料によって構成されており、第1の領域を構成する導電材料と、第2の領域

を構成する導電材料との仕事関数の差は、0.6eV以下であることを特徴とする半導体

装置である。

た突起と、該チャネル幅方向に延伸した突起を介して対向した一対の突起とが設けられた

絶縁表面を有する構造物を形成することで、トップゲート構造のトランジスタにおいても

、短チャネル効果を抑制しつつ、該トランジスタのオン電流を増大させることができる。

れる第2の突起とを有し、且つ絶縁表面を有する構造物と、一対の第1の突起および第2

の突起に接する半導体膜と、半導体膜と接して、且つ一対の第1の突起と重畳する一対の

電極と、構造物、半導体膜、および一対の電極を覆うゲート絶縁膜と、ゲート絶縁膜に接

して、且つ一対の電極の間に設けられるゲート電極と、を有し、半導体膜の側端は、半導

体膜のチャネル幅方向において、一対の第1の突起の頂面より外側であり、一対の電極の

側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側である、

半導体装置である。

して対向する一対の突起を、絶縁表面を有する構造物上に複数設けることで、トランジス

タを上面から見た場合の該一対の電極幅に相当する見かけ上のチャネル幅に対して、トラ

ンジスタの動作時に機能する実効上のチャネル幅をさらに広くすることができる。

導体膜の側端およびチャネル幅方向における一対の電極の側端は、複数設けられた一対の

突起のうち異なる一対の突起の頂面上であってもよい。

起を一対の突起の間に複数設けることで、見かけ上のチャネル長に対して、実効上のチャ

ネル長をさらに長くすることができる。

シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸

化窒化アルミニウム、窒化酸化アルミニウムまたは窒化アルミニウムを含むことが好まし

い。

スタともに、見かけ上のチャネル長およびチャネル幅に対して、実効上のチャネル長およ

び実効上のチャネル幅は3倍以上であることが好ましい。

向に延伸した突起と、該チャネル幅方向に延伸した突起を介して対向した一対の突起とが

設けられたゲート電極は、2枚のフォトマスクを用いて、2回のフォトリソグラフィ工程

と2回のエッチングを行うことで形成することができる。

る領域と、チャネル幅方向に延伸した突起が形成される領域と、該チャネル幅方向に延伸

した突起を介して対向した一対の突起が形成される領域とに対応させて、厚さの異なる領

域を有するレジストマスクを形成し、該レジストマスクを用いてエッチングすることによ

り、チャネル幅方向に延伸した突起と、該チャネル幅方向に延伸した突起を介して対向し

た一対の突起とが設けられたゲート電極を形成することができる。厚さの異なる領域を有

するレジストマスクは多階調マスクを用いることで形成することができる。それゆえ、ゲ

ート電極を形成する際に、使用するフォトマスクを1枚にすることができ、さらに、フォ

トリソグラフィ工程の回数を減らせるため、フォトリソグラフィ工程の回数を増やすこと

なく該ゲート電極を作製することができる。

突起と、該チャネル幅方向に延伸した突起を介して対向した一対の突起とが設けられた絶

縁表面を有する構造物は、多階調マスクを用いる上記方法で形成することができる。

。酸化物半導体膜は、シリコン半導体膜に比べて大きなバンドギャップを有するため、該

酸化物半導体膜をトランジスタに用いることでオフ電流を低減させることができる。それ

ゆえ、トランジスタのオン・オフ比を確保することが容易になる。さらに、半導体記憶装

置のメモリセルに該トランジスタを用いる場合、該メモリセルにおいてリーク電流が流れ

ることを抑制することができる。

ズを縮小しつつ、実効上のチャネル長を長くしたトランジスタを提供することができる。

イズを縮小しつつ、高いオン電流が確保できるトランジスタ、および良好なスイッチング

特性を有するトランジスタを提供することができる。それゆえ、短チャネル効果の影響を

低減し、かつ集積度が高い半導体装置を提供することができる。

説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳

細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に

示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本

発明の構成において、同一部分または同様な機能を有する部分には、同一の符号を異なる

図面間で共通して用い、その繰り返しの説明は省略する。

明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されな

い。

またはスパッタリング法などにより、被形成面の全面に形成されたものと、該被形成面の

全面に形成されたものに対して半導体装置の作製工程に係る処理を行った後のものと、に

用いる。

したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2

の」または「第3の」などと適宜置き換えて説明することができる。

レインの間に流れる電流をいう。例えば、n型の薄膜トランジスタの場合には、ゲート電

圧がトランジスタのしきい値電圧よりも大きいときに、ソースとドレインとの間に流れる

電流が、オン電流である。また「オフ電流」とは、トランジスタが非導通状態としたとき

に、意図せずにソースとドレインの間に流れる電流をいう。例えば、n型の薄膜トランジ

スタの場合には、ゲート電圧がトランジスタのしきい値電圧よりも小さいときに、ソース

とドレインとの間に流れる電流が、オフ電流である。なお、「ゲート電圧」とは、ソース

を基準としたゲートとソースの電位差をいう。また、「オン・オフ比」とは、トランジス

タのオフ電流に対するオン電流の比をいう。

は入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の

用語は、入れ替えて用いることができるものとする。

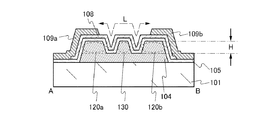

本実施の形態では、本発明の一態様であるトランジスタ100について図1を用いて説

明する。

第1の突起120a、120bの間に設けられる第2の突起130とを有するゲート電極

104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶縁膜105と接して

、且つ一対の第1の突起120a、120bおよび第2の突起130に重畳する半導体膜

108と、半導体膜108と接して、且つ一対の第1の突起120a、120bと重畳す

る一対の電極109a、109bと、を有するボトムゲート構造のトランジスタである。

なお、図1(A)において、ゲート絶縁膜105は、便宜上、図示していない。

向に延伸して設けられた第2の突起130を挟んで対向して設けられている。

対の第1の突起120a、120bの頂面より外側に位置する。

104に設けられた一対の第1の突起120a、120bの頂面より外側に位置する。

図である。

bおよび第2の突起130の形状に沿って形成される。従って、トランジスタ100は、

三次元状のチャネル領域が形成され、トランジスタ100の動作時に機能する実効上のチ

ャネル長Lは、図1(A)の一対の電極109a、109b間の距離に相当する見かけ上

のチャネル長に対して、少なくとも一対の第1の突起120a、120bおよび第2の突

起130の高さHの分は、長くなる(図1(B)参照)。

第1の突起120a、120bおよび第2の突起130頂面からゲート電極104の底面

に下ろした垂線において、該頂面から、ゲート電極104の一対の突起120a、120

bおよび第2の突起130以外の領域における上面までの距離に相当する。

図である。

0bのうちの一方である第1の突起120aを有するゲート電極104と、ゲート電極1

04を覆うゲート絶縁膜105と、ゲート絶縁膜105と接して、且つ該第1の突起12

0aと重畳する半導体膜108と、半導体膜108と接して、且つ第1の突起120aと

重畳する一対の電極109a、109bのうちの一方である電極109aと、を有する。

、トランジスタ100の半導体膜108は、ゲート電極104に設けられた一対の第1の

突起120a、120bの形状に沿って形成される。従って、トランジスタ100は、三

次元状のチャネル領域が形成され、トランジスタ100の動作時に機能する実効上のチャ

ネル幅Wは、図1(A)の一対の電極109a、109bの幅に相当する見かけ上のチャ

ネル幅に対して、少なくとも一対の第1の突起120a、120bの高さHの分は、長く

なる(図1(C)参照)。これにより、トランジスタのサイズを縮小しつつ、トランジス

タ100のオン電流を増大させることができる。

け上のチャネル長に対して、実効上のチャネル長Lが3倍以上、好ましくは5倍以上、さ

らに好ましくは10倍以上の長さとなって、且つ、見かけ上のチャネル幅に対して、実効

上のチャネル幅Wが3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さ

となることが好ましい。その好ましい長さとなるように、一対の第1の突起120a、1

20bおよび第2の突起130の高さHを選択する。なお、一対の第1の突起120a、

120bおよび第2の突起130は、同じ作製工程で形成されることから、一対の第1の

突起120a、120bの高さと第2の突起130の高さは同じになる。

対して長くなっていることから、トランジスタのサイズを縮小しつつ、しきい値電圧のマ

イナス方向への変動やオフ電流の増大など、短チャネル効果の影響を低減することができ

る。

抑制することができ、さらに実効上のチャネル幅Wも長くさせてオン電流を増大させるこ

とができるため、トランジスタのオン・オフ比を充分に確保された良好なスイッチング特

性を有するトランジスタである。

第2の突起130は角錘台状であるが、錘状でもよい。つまり、トランジスタ100の見

かけ上のチャネル長および見かけ上のチャネル幅に対して、実効上のチャネル長Lおよび

実効上のチャネル幅Wが長くなる形状であれば、特に限定はない。さらに、一対の第1の

突起120a、120bおよび第2の突起130の高さ方向に垂直な方向の断面形状は円

形(楕円形も含む。)でもよく、多角形でもよい。

びC−D断面は台形状である。このように、一対の第1の突起120a、120bおよび

第2の突起130を角錘台状とする場合、トランジスタ100の作製において形成される

膜の被覆性を向上させて該膜の断切れを防止するために、一対の第1の突起120a、1

20bおよび第2の突起130はテーパ形状とすることが好ましい。

起130について説明する。

一対の第1の突起120a、120bおよび第2の突起130の両方の形状に沿って形成

されている領域と、(2)第2の突起130のみの形状に沿って形成されている領域と、

である。この場合、(1)に形成される実効上のチャネル長よりも(2)に形成される実

効上のチャネル長のほうが短くなっている。

果の抑制は、一対の第1の突起120a、120bの形状に沿って形成されること以上に

、第2の突起130の形状に沿って形成されることに起因している。つまり、上記(1)

の領域および上記(2)の領域ともに短チャネル効果が抑制される。

する半導体膜108において、チャネル幅方向の長さを一対の第1の突起120a、12

0bのチャネル幅方向の長さに対して長くした場合でも、半導体膜108全ての領域で、

見かけ上のチャネル長に対する実効上のチャネル長を長くすることができ、短チャネル効

果を抑制できる。

08の大きさについて、その選択の範囲を広くすることができる。

スタ100は、以下の構造とすることができる。

0に重畳していればよい。つまり、図1(A)に示すトランジスタ100の半導体膜10

8の側端は、チャネル長方向において、ゲート電極104の側端より外側に位置し、チャ

ネル幅方向において、第2の突起130の側端より内側に位置しているが、このほかにチ

ャネル長方向において、半導体膜108の側端は、ゲート電極104の側端より内側に位

置してもよいし、チャネル幅方向において、半導体膜108の一方の側端は、ゲート電極

104の側端および第2の突起130の側端より外側に位置していてもよい(図25(A

)参照)。

ト電極104の側端より内側に位置しており、チャネル幅方向において、第2の突起13

0の側端もゲート電極104の側端より内側に位置しているが、一対の第1の突起120

a、120bの側端および第2の突起130の側端のそれぞれ一側端がゲート電極104

の側端の一側端となるように形成されていてもよい(図25参照(B)参照)。なお、図

1に示したトランジスタ100は、チャネル長方向において、一対の第1の突起120a

、120bの側端は、ゲート電極104の側端より内側に位置し、チャネル幅方向におい

て、第2の突起130の側端もゲート電極104の側端より内側に位置している。これは

、多階調マスクを用いて形成することにより生じることであり、多階調マスクを用いて形

成する方法については後述する。

ル幅方向における側端は、半導体膜108の側端より内側である。しかし、チャネル長方

向における一対の電極109a、109bの側端が一対の第1の突起120a、120b

に重畳し、チャネル幅方向における一対の電極109a、109bの側端が、一対の第1

の突起120a、120bの頂面より外側であれば、チャネル幅方向における一対の電極

109a、109bの側端は、半導体膜108より外側であってもよい(図25(C)参

照)。

半導体膜108の上面とが接するトップコンタクト構造であるが、一対の電極109a、

109bの上面と半導体膜108の下面とが接するボトムコンタクト構造であってもよい

。

図8に示した断面図は、図1(A)の一点鎖線A−B間および一点鎖線C−D間の断面に

相当する。

有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基

板などを、基板101として用いてもよい。また、シリコンや炭化シリコンなどの単結晶

半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI

(Silicon On Insulator)基板などを適用することも可能であり、

これらの基板上に半導体素子が設けられたものを、基板101として用いてもよい。

に直接的にトランジスタを作製する。なお、可とう性基板上にトランジスタを設ける方法

としては、基板101として非可とう性のものを用いて、この上にトランジスタを作製し

た後、トランジスタを剥離し、可とう性基板に転置する方法もある。その場合には、基板

101とトランジスタとの間に剥離層を設けるとよい。

101上に導電膜102を形成する(図2(A)参照)。導電膜102の厚さは、一対の

突起120a、120bおよび第2の突起130の高さH、ならびにトランジスタ100

の実効上のチャネル長Lを考慮して選択する。例えば、導電膜102の厚さは100nm

以上で形成すればよい。

Mo、Ag、TaおよびW、それらの窒化物、酸化物ならびに合金から一以上選択し、単

層または積層で形成することができる。また、ゲート電極104として該酸化物を用いる

場合は、5×1019cm−3以上20atomic%以下、好ましくは1×1020c

m−3以上7atomic%以下の窒素を含んでもよい。例えば、1×1020cm−3

以上7atomic%以下の窒素を含み、かつIn、GaおよびZnを含む酸化物膜を用

いるとよい。

0が設けられたゲート電極104を形成する。なお、ゲート電極104はトランジスタ1

00のゲート配線としても機能する。

は、異なるパターンを有する2枚のフォトマスクを用いて、2回のフォトリソグラフィ工

程および2回のエッチング工程で形成することができる。フォトリソグラフィ工程の代わ

りにインクジェット法または印刷法等により異なるパターンを有する2種類のマスクを形

成してもよい。ただし、トランジスタの作製工程において、フォトマスクの枚数が増える

ことは、それだけフォトリソグラフィ工程の回数が増えることになり、歩留まりの低下な

ど生産性を低下させる可能性がある。

設けられたゲート電極104を、厚さの異なる領域を有するレジストマスクを用いて形成

する方法を説明する。厚さの異なる領域を有するレジストマスクは、多階調マスクを用い

て形成することができる。多階調マスクを用いることは、1枚のフォトマスクでゲート電

極104を形成することができ、フォトリソグラフィ工程数を増やさずに一対の突起12

0a、120bおよび第2の突起130を形成できるため好ましい。

、露光領域、半露光領域および未露光領域の3段階の光量で露光を行う。多階調マスクを

用いることで、一度の露光および現像工程によって、複数(代表的には二種類)の厚さを

有するレジストマスクを形成することができる。そのため、多階調マスクを用いることで

、フォトマスクの枚数を削減することができる。

、代表的な多階調マスクの断面を示す。図3(A−1)には、グレートーンマスク304

を示し、図3(B−1)にはハーフトーンマスク314を示す。

層により形成された遮光部302、および遮光層のパターンにより設けられた回折格子部

303で構成されている。

ドットまたはメッシュ等を有することで、光の透過率を制御する。なお、回折格子部30

3に設けられるスリット、ドットまたはメッシュは周期的なものであってもよいし、非周

期的なものであってもよい。

び回折格子部303を構成する遮光層は、金属膜を用いて形成すればよく、好ましくはク

ロムまたは酸化クロム等により設けられる。

ように、遮光部302に重畳する領域における透光率は0%となり、遮光部302も回折

格子部303も設けられていない領域における透光率は100%となる。また、回折格子

部303における透光率は、概ね10%〜70%の範囲であり、回折格子のスリット、ド

ットまたはメッシュの間隔等により調節可能である。

透光層により形成された半透光部312および遮光層により形成された遮光部313で構

成されている。

層を用いて形成することができる。遮光部313は、グレートーンマスクの遮光層と同様

の金属膜を用いて形成すればよく、好ましくはクロムまたは酸化クロム等により設けられ

る。

ように、遮光部313に重畳する領域における透光率は0%となり、遮光部313も半透

光部312も設けられていない領域における透光率は100%となる。また、半透光部3

12における透光率は、概ね10%〜70%の範囲であり、形成する材料の種類または形

成する膜厚等により調整可能である。

の露光レベルのマスクを形成することができ、一度の露光および現像工程により、複数(

代表的には二種類)の厚さの領域を有するレジストマスクを形成することができる。この

ため、多階調マスクを用いることで、トランジスタ100の作製工程におけるフォトマス

クの枚数を削減することができる。

厚さの異なる領域を有するレジストマスク150を形成する。

a、および遮光層141bで構成されている。したがって、レジストマスク150は、導

電膜102において、一対の第1の突起120a、120bおよび第2の突起130が形

成される領域は厚く、それ以外の領域は薄くなるように形成する(図2(B)参照)。な

お、導電膜102において、ゲート電極104が形成されない領域には、レジストマスク

150も形成されないようにする。一対の第1の突起120a、120bと第2の突起1

30との間の距離を考慮して、レジストマスク150の薄く形成される領域の厚さを決定

する。

グ)する。このエッチングにより、島状に加工された導電膜103を形成する。なお、該

エッチングはドライエッチングで行えばよい。

120bと第2の突起130との間隔となる部分において分離されたレジストマスク15

1を形成する(図4(A)参照)。レジストマスク150の縮小(後退)には、酸素プラ

ズマによるアッシングを用いればよい。

一対の第1の突起120a、120bおよび第2の突起130を形成し、ゲート電極10

4を形成する。そして、該エッチングの後にレジストマスク151を除去する(図4(B

)参照)。該エッチングを行う時間が長くなるほど、一対の第1の突起120a、120

bおよび第2の突起130の高さHを高くすることができる。このとき、島状に加工され

た導電膜103において、一対の第1の突起120a、120bおよび第2の突起130

が形成される以外の領域が消失しないように、導電膜102のエッチングレートを考慮し

て、エッチング時間を調節する必要がある。

トマスク150を縮小(後退)させて、形成したレジストマスク151を用いることによ

り、一対の第1の突起120a、120bおよび第2の突起130のチャネル長方向およ

びチャネル幅方向における端部は、ゲート電極104のチャネル長方向およびチャネル幅

方向における端部より内側に位置するように形成される(図1(A)参照)。

する2枚のフォトマスクを用いて、2回のフォトリソグラフィ工程と2回のエッチングを

行うことで形成すれば、一対の第1の突起120a、120bの側端および第2の突起1

30の側端がゲート電極104の側端となるように形成することができる。この場合にお

いて、完成したトランジスタ100の上面図は図25(B)であり、図25(B)の一点

鎖線A−B間の断面図は図5である。

行っても構わない。このような処理を行うことによって、一対の第1の突起120a、1

20bおよび第2の突起130の角が削られ、曲面形状にでき、以降のトランジスタ10

0の作製工程において形成する膜の被覆性を高めることができる。

照)。ゲート絶縁膜105の厚さは、1nm以上300nm以下とすればよい。

窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化イットリウムまたは酸化ジルコ

ニウムなどを用いればよく、積層または単層で設ければよい。例えば、熱酸化法、プラズ

マCVD法、スパッタリング法などで形成すればよい。後に形成する半導体膜108に酸

化物半導体膜を用いる場合、ゲート絶縁膜105は、加熱処理により酸素を放出する膜を

用いると好ましい。加熱処理により酸素を放出する膜を用いることで、後に形成する半導

体膜108に生じる欠陥を修復することができ、トランジスタ100の電気特性の劣化を

抑制できる。

n Spectroscopy:昇温脱離ガス分光法)分析にて、酸素原子に換算しての

酸素の放出量が1.0×1018cm−3以上、好ましくは3.0×1020cm−3以

上であることをいう。

下に説明する。

ため、当該積分値と、標準試料の基準値に対する比とにより、気体の放出量を計算するこ

とができる。標準試料の基準値とは、所定の原子を含む試料において検出したイオン強度

の積分値に対する原子の密度の割合である。

よび絶縁膜のTDS分析結果から、絶縁膜の酸素分子の放出量(NO2)は、数式1で求

めることができる。ここで、TDS分析で得られる質量数32で検出されるイオン強度の

全てが酸素分子由来と仮定する。質量数32のものとしてほかにCH3OHがあるが、存

在する可能性が低いものとしてここでは考慮しない。また、酸素原子の同位体である質量

数17の酸素原子および質量数18の酸素原子を含む酸素分子についても、自然界におけ

る存在比率が極微量であるため考慮しない。

試料をTDS分析したときのイオン強度の積分値である。ここで、標準試料の基準値を、

NH2/SH2とする。SO2は、絶縁膜をTDS分析したときのイオン強度の積分値で

ある。αは、TDS分析におけるイオン強度に影響する係数である。数式1の詳細に関し

ては、特開平6−275697公報を参照する。なお、上記絶縁膜の酸素の放出量は、電

子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試料とし

て1×1016cm−3の水素原子を含むシリコンウェハを用いて測定した。

原子の比率は、酸素分子のイオン化率から算出することができる。なお、上述のαは酸素

分子のイオン化率を含むため、酸素分子の放出量を評価することで、酸素原子の放出量に

ついても見積もることができる。

子の放出量の2倍となる。

SiOX(X>2))膜であってもよい。酸素が過剰な酸化シリコン(SiOX(X>2

))膜とは、シリコン原子数の2倍より多い酸素原子を単位体積当たりに含むものである

。単位体積当たりのシリコン原子数および酸素原子数は、ラザフォード後方散乱法により

測定した値である。

化物半導体膜107に酸素が供給され、ゲート絶縁膜105および後述する酸化物半導体

膜107の界面準位を低減できる。従って、トランジスタ100の動作に起因して生じう

る電荷などが、該界面準位に捕獲されることを抑制でき、トランジスタ100を電気特性

の劣化の少ないトランジスタとすることができる。

。

導体膜をトランジスタ100に用いることでオフ電流を低減させることができる。それゆ

え、トランジスタのオン・オフ比を確保することが容易になる。

属酸化物材料を用いればよい。例えば、四元系金属酸化物であるIn−Sn−Ga−Zn

−O系の材料や、三元系金属酸化物であるIn−Ga−Zn−O系の材料、In−Sn−

Zn−O系の材料、In−Al−Zn−O系の材料、Sn−Ga−Zn−O系の材料、A

l−Ga−Zn−O系の材料、Sn−Al−Zn−O系の材料や、二元系金属酸化物であ

るIn−Zn−O系の材料、Sn−Zn−O系の材料、Al−Zn−O系の材料、Zn−

Mg−O系の材料、Sn−Mg−O系の材料、In−Mg−O系の材料、In−Ga−O

系の材料や、一元系金属酸化物であるIn−O系の材料、Sn−O系の材料、Zn−O系

の材料などを用いればよい。ここで、例えば、In−Ga−Zn−O系の材料とは、イン

ジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物、という意味であり、

その組成比は特に問わない。また、InとGaとZn以外の元素を含んでいてもよい。こ

のとき、酸化物半導体膜の化学量論比に対し、Oを過剰にすると好ましい。Oを過剰にす

ることで酸化物半導体膜の酸素欠損に起因するキャリアの生成を抑制することができる。

数比で、In/Zn=0.5以上50以下、好ましくはIn/Zn=1以上20以下、さ

らに好ましくはIn/Zn=3以上30以下とする。Znの原子数比を前述の範囲とする

ことで、トランジスタ100の電界効果移動度を向上させることができる。ここで、化合

物の原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとすると好ましい

。

用いてもよい。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の

金属元素を示す。例えば、Mとして、Ga、GaおよびAl、GaおよびMnまたはGa

およびCoなどを用いてもよい。

状態をとる。好ましくは、酸化物半導体膜は、CAAC−OS(C Axis Alig

ned Crystalline Oxide Semiconductor)膜とする

。

膜は、非晶質相に結晶部および非晶質部を有する結晶−非晶質混相構造の酸化物半導体膜

である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさであるこ

とが多い。また、透過型電子顕微鏡(TEM:Transmission Electr

on Microscope)による観察像では、CAAC−OS膜に含まれる非晶質部

と結晶部との境界は明確ではない。また、TEMによってCAAC−OS膜には粒界(グ

レインバウンダリーともいう。)は確認できない。そのため、CAAC−OS膜は、粒界

に起因する電子移動度の低下が抑制される。

トルまたは表面の法線ベクトルに平行な方向に揃い、かつab面に垂直な方向から見て三

角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状また

は金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸

およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、

85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、−

5°以上5°以下の範囲も含まれることとする。なお、酸化物半導体膜を構成する酸素の

一部は窒素で置換されてもよい。

AC−OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被

形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、C

AAC−OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非

晶質化することもある。

トルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC−OS膜の形状(被形

成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。

なお、結晶部のc軸の方向は、CAAC−OS膜が形成されたときの被形成面の法線ベク

トルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、ま

たは成膜後に加熱処理などの結晶化処理を行うことにより形成される。

動を低減することが可能である。よって、当該トランジスタは、信頼性が高い。

エピタキシー法、原子層堆積法またはパルスレーザー蒸着法により形成する。ここでは、

スパッタリング法により形成する。なお、酸化物半導体膜106は、厚さ1nm以上50

nm以下で形成すればよい。

物半導体膜106を形成すればよく、基板101を加熱する温度としては、150℃以上

450℃以下とすればよく、好ましくは基板温度が200℃以上350℃以下とする。な

お、酸化物半導体膜の形成時に、基板を加熱する温度を高くすることで、非晶質な部分に

対して結晶部分の占める割合の多いCAAC−OSとすることができる。

膜106に含まれる水素濃度を低減させることが好ましい。水素濃度を低減させるには、

スパッタリング装置の処理室内に供給する雰囲気ガスとして、水素、水、水酸基または水

素化物などの不純物が除去された高純度の希ガス(代表的にはアルゴン)、酸素、および

希ガスと酸素との混合ガスを適宜用いる。さらには、該処理室の排気は、水の排気能力の

高いクライオポンプおよび水素の排気能力の高いスパッタイオンポンプを組み合わせて用

いればよい。

とができる。なお、上記スパッタリング装置を用いても、酸化物半導体膜106は少なか

らず窒素を含んで形成される。例えば、二次イオン質量分析法(SIMS:Second

ary Ion Mass Spectroscopy)で測定される酸化物半導体膜1

06の窒素濃度は、5×1018cm−3未満となる。

もよい。例えば、基板101上のゲート電極104の表面に付着した水素を含む不純物を

、熱処理またはプラズマ処理で除去した後、大気に暴露することなくゲート絶縁膜105

を形成し、続けて大気に暴露することなく酸化物半導体膜106を形成してもよい。この

ようにすることで、ゲート電極104の表面に付着した水素を含む不純物を低減し、また

、ゲート絶縁膜105と酸化物半導体膜106との界面に、大気成分が付着することを抑

制できる。その結果、電気特性が良好で、信頼性の高いトランジスタ100を作製するこ

とができる。

し、該レジストマスクを用いて、酸化物半導体膜106を所望の形状にエッチングし、島

状の酸化物半導体膜107を形成する(図7(A)参照)。該エッチングは、ドライエッ

チングまたはウェットエッチングで行えばよい。

、酸化物半導体膜106を形成する際、または酸化物半導体膜107を形成する際に生じ

る。一般に酸化物半導体における酸素欠損は、酸素欠損の一部がドナーとなり、キャリア

である電子を生じる。つまり、該電子の生成は、トランジスタ100のしきい値電圧をマ

イナス方向に変動させる要因となる。そして、酸化物半導体膜107において、該電子の

生成は、酸化物半導体膜106(または酸化物半導体膜107)とゲート絶縁膜105と

の界面近傍で生じる酸素欠損おいて顕著である。

成する(図7(B)参照)。なお、酸化物半導体膜111は、図1に示したトランジスタ

100の半導体膜108に相当する。さらに、半導体膜108は、酸化物半導体膜111

のかわりに半導体特性を示す他の材料を適用してもよい。例えば、該材料としては、単結

晶シリコン膜もしくは多結晶シリコン膜に代表されるように結晶性を有するシリコン半導

体膜などがある。

)を放出させると共に、ゲート絶縁膜105に含まれる酸素の一部を放出し、酸化物半導

体膜107中、およびゲート絶縁膜105と酸化物半導体膜107との界面近傍に酸素を

拡散させる。さらに、ゲート絶縁膜105と酸化物半導体膜107と界面準位および酸化

物半導体膜107の酸素欠損を低減し、完成したトランジスタ100の酸化物半導体膜1

11とゲート絶縁膜105との界面におけるキャリア捕獲の影響を小さくすることができ

る。従って、第1の加熱処理は、トランジスタ100のしきい値電圧がマイナス方向へ変

動することを抑制することができる。

板歪み点温度未満、好ましくは250℃以上450℃以下、さらに好ましくは300℃以

上450℃以下とし、酸化性雰囲気または不活性雰囲気で行う。ここで、酸化性雰囲気は

、酸素、オゾンまたは窒化酸素などの酸化性ガスを10ppm以上含有する雰囲気をいう

。また、不活性雰囲気は、前述の酸化性ガスが10ppm未満であり、その他、窒素また

は希ガスで充填された雰囲気をいう。処理時間は3分〜24時間とする。24時間を超え

る熱処理は生産性の低下を招くため好ましくない。

らの熱伝導または熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば

、電気炉や、GRTA(Gas Rapid Thermal Anneal)装置、L

RTA(Lamp Rapid Thermal Anneal)装置等のRTA(Ra

pid Thermal Anneal)装置を用いることができる。LRTA装置は、

ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ

、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射に

より、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を

行う装置である。

第1の加熱処理によって、酸化物半導体膜107は膜中の水素濃度が低減され、高純度化

された酸化物半導体膜111となる。酸化物半導体膜111の水素濃度は、5×1018

cm−3以下、好ましくは1×1018cm−3以下、より好ましくは5×1017cm

−3未満、さらに好ましくは1×1016cm−3以下である。なお、酸化物半導体膜1

11中の水素濃度は、二次イオン質量分析法で測定されるものである。

を供給されて酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半

導体膜111を用いることで、トランジスタ100のオフ電流を低減させることができる

。具体的には、室温(25℃)でのオフ電流(ここでは、チャネル長が3μm、チャネル

幅が1μmのトランジスタにおける値)は100zA(1zA(ゼプトアンペア)は1×

10−21A)以下、望ましくは10zA以下となる。なお、LiやNaなどのアルカリ

金属は、不純物であるため含有量を少なくすることが好ましく、酸化物半導体膜111中

に2×1016cm−3以下、好ましくは、1×1015cm−3以下の濃度とことが好

ましい。さらに、アルカリ土類金属も不純物であるため含有量を少なくすることが好まし

い。

半導体膜107を形成した後だけではなく、酸化物半導体膜106を形成した後であれば

、いつ行ってもよい。さらに、第1の加熱処理は複数回行ってもよい。例えば、酸化物半

導体膜107を形成した後に1回行うだけではなく、酸化物半導体膜106を形成した後

と、酸化物半導体膜107を形成した後の2回行ってもよい。

膜は、ゲート電極104を形成する際に用いる導電膜102に適用可能な導電材料を用い

て、単層または積層して形成する。また、該導電膜の厚さは、特に限定はなく、上記導電

材料の電気抵抗や、作製工程にかかる時間を考慮し、適宜決めることができる。例えば、

10nm以上500nm以下で形成すればよい。なお、該導電膜を形成する方法は導電膜

102と同様とすればよい。

該レジストマスクを用いて該導電膜をエッチングし、一対の電極109a、109bを形

成する(図8(A)参照)。該エッチングはドライエッチングまたはウェットエッチング

で行えばよい。なお、一対の電極109a、109bはソース電極およびドレイン電極と

して機能し、ソース配線およびドレイン配線としても機能する。

工程の後に、保護絶縁膜110を形成してもよい(図8(B)参照)。保護絶縁膜110

はゲート絶縁膜105と同様とすればよい。さらに、保護絶縁膜110を形成した後に第

2の加熱処理を行ってもよい。第2の加熱処理を行うことで、ゲート絶縁膜105中の酸

素の一部および保護絶縁膜110中の酸素の一部を、酸化物半導体膜111中、およびゲ

ート絶縁膜105と酸化物半導体膜111との界面近傍、酸化物半導体膜111と保護絶

縁膜110との界面近傍に拡散させることができ、酸化物半導体膜111の酸素欠損を補

うことができるため、トランジスタ100の電気特性を向上させることができる。なお、

第2の加熱処理における装置および加熱条件は、第1の加熱処理と同様とすればよい。

20bおよび第2の突起130が設けられていることにより、上面図における一対の電極

109a、109b間の距離である見かけ上のチャネル長に対して、実効上のチャネル長

Lを3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとすることがで

きる。さらに、上面図における一対の電極109a、109b間の幅である見かけ上のチ

ャネル幅に対して、実効上のチャネル幅Wを3倍以上、好ましくは5倍以上、さらに好ま

しくは10倍以上の長さとすることができる。そのため、トランジスタのサイズを縮小し

ても短チャネル効果の影響が低減され、半導体装置の集積度を高めることが可能となる。

また、コストが低く、歩留まりの高い半導体装置を提供することができる。

る。

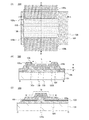

本実施の形態では、実施の形態1に示したトランジスタ100とは異なる構造のトラン

ジスタについて説明する。

ト構造のトランジスタである。そこで、本実施の形態では、ゲート電極104に一対の第

1の突起120a、120bが複数設けられている形態について説明する。また、本実施

の形態は、実施の形態1と比較して一対の第1の突起120a、120bを設ける数が異

なるだけであるため、実施の形態1の説明は、適宜参照することができる。

られているトランジスタ200を例に説明する。

20bと、該一対の第1の突起120a、120bの間に設けられた第2の突起130と

を有するゲート電極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶

縁膜105と接して、且つ該一対の第1の突起120a、120bおよび第2の突起13

0に重畳する半導体膜108と、半導体膜108と接して、且つ該一対の第1の突起12

0a、120bと重畳する一対の電極109a、109bと、を有するボトムゲート構造

のトランジスタである。なお、図9(A)において、ゲート絶縁膜105は、便宜上、図

示していない。

設けられた一対の第1の突起120a、120bのうち最も外側に配置される一対の第1

の突起120a、120bの頂面上に位置している。

104に3組設けられた一対の第1の突起120a、120bのうち最も外側に配置され

る一対の第1の突起120a、120bの頂面上に位置している。

チャネル幅方向に延伸して設けられた第2の突起130を挟んで対向して設けられている

。図9(B)は図9(A)に示した一点鎖線A−B間におけるトランジスタ200の断面

図である。図9(B)に示すように、トランジスタ200のA−B断面は、トランジスタ

100と同様である。

第1の突起120a、120bおよび第2の突起130の形状に沿って形成される。従っ

て、トランジスタ200は、三次元状のチャネル領域が形成され、トランジスタ200動

作時に機能する実効上のチャネル長Lは、図9(A)の一対の電極109a、109b間

の距離に相当する見かけ上のチャネル長に対して、少なくとも一対の第1の突起120a

、120bおよび第2の突起130の高さHの分は、長くなる(図9(B)参照)。

面図である。

第1の突起120a、120bのうちの一方である第1の突起120aが離間して3つ設

けられたゲート電極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶

縁膜105と接して、且つゲート電極104およびゲート電極104に設けられた全ての

第1の突起120aと重畳する半導体膜108と、半導体膜108と接して、且つゲート

電極104に設けられた全ての第1の突起120aと重畳する一対の電極109a、10

9bのうちの一方である電極109aと、を有する。

第1の突起120a、120bの形状に沿って形成される。従って、トランジスタ200

は、三次元状のチャネル領域が形成され、トランジスタ200の動作時に機能する実効上

のチャネル幅Wは、図9(A)の一対の電極109a、109bの幅に相当する見かけ上

のチャネル幅に対して、少なくとも形状に沿って形成された一対の第1の突起120a、

120bの高さHの分は、長くなる(図9(C)参照)。

実効上のチャネル幅Wおよび実効上のチャネル長Lが、3倍以上、好ましくは5倍以上、

さらに好ましくは10倍以上の長さとなるように、3組の一対の第1の突起120a、1

20bおよび第2の突起130の高さHを選択する。なお、一対の第1の突起120a、

120bおよび第2の突起130は、同じ作製工程で形成されることから、一対の第1の

突起120a、120bおよび第2の突起130の高さHは同じである。

するトランジスタの大きさに合わせて適宜決めればよい。なお、ゲート電極に設ける一対

の第1の突起だけでなく、後述の実施の形態3で説明するように、第2の突起を複数設け

てもよい。このように、一対の第1の突起および第2の突起を複数設けることによって、

一組一組(一つ一つ)の一対の第1の突起および第2の突起の高さを低くできるため、ト

ランジスタの作製工程において形成される膜の被覆性を高めることができる。

ャネル長Lを長くさせて短チャネル効果を抑制することができ、さらに実効上のチャネル

幅Wも長くさせてオン電流を増大させることができるため、トランジスタのオン・オフ比

を充分に確保された良好なスイッチング特性を有するトランジスタである。

。

び第2の突起130が形成される領域の厚さは厚く、それ以外の領域の厚さは薄くなるよ

うにレジストマスク150を形成する(図10(B)参照)。なお、導電膜102におい

て、ゲート電極104が形成されない領域には、レジストマスク150も形成されないよ

うにする。一対の第1の突起120a、120bと第2の突起130との間の距離を考慮

して、レジストマスク150の薄く形成される領域の厚さを決定する。

やす場合は、多階調マスクを用いて形成する厚さの異なる領域を有するレジストマスクに

おいて、設ける一対の第1の突起120a、120bの数だけ、厚さの厚い領域を形成し

、それ以外の領域の厚さは薄くなるように形成すればよい。

グ)する。このエッチングにより、島状に加工された導電膜103を形成する。なお、該

エッチングはドライエッチングで行えばよい。

、120bと第2の突起130との間隔となる部分において分離されたレジストマスク1

51を形成する(図10(C)参照)。レジストマスク150の縮小(後退)には、酸素

プラズマによるアッシングを用いればよい。

一対の第1の突起120a、120bおよび第2の突起130を形成し、ゲート電極10

4を形成する。そして、該エッチングの後にレジストマスク151を除去する(図10(

D)参照)。

ことができる(図6乃至図8参照)。

の第1の突起120a、120bおよび1つの第2の突起130を設けることで、見かけ

上のチャネル長に対して、実効上のチャネル長Lを3倍以上、好ましくは5倍以上、さら

に好ましくは10倍以上の長さとすることができる。さらに、見かけ上のチャネル幅に対

して、実効上のチャネル幅Wを3倍以上、好ましくは5倍以上、さらに好ましくは10倍

以上の長さとすることができる。そのため、トランジスタのサイズを縮小しても短チャネ

ル効果の影響が低減され、半導体装置の集積度を高めることが可能となる。また、コスト

が低く、歩留まりの高い半導体装置を提供することができる。

る。

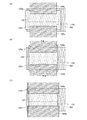

本実施の形態では、先の実施の形態に示したトランジスタとは異なる構造のトランジス

タについて説明する。

のトランジスタである。そこで、本実施の形態では、ゲート電極104に第2の突起13

0が複数設けられている形態について説明する。また、本実施の形態は、実施の形態1と

比較して第2の突起130を設ける数が異なるだけであるため、実施の形態1の説明を適

宜参照することができる。

スタ300を例に説明する。

対の第1の突起120a、120bの間に2つ設けられた第2の突起130とを有するゲ

ート電極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶縁膜105

と接して、且つ一対の第1の突起120a、120bおよび該第2の突起130に重畳す

る半導体膜108と、半導体膜108と接して、且つ該一対の第1の突起120a、12

0bと重畳する一対の電極109a、109bと、を有するボトムゲート構造のトランジ

スタである。なお、図11(A)において、ゲート絶縁膜105は、便宜上、図示してい

ない。

られた一対の第1の突起120a、120bの頂面より外側に位置する。

104に設けられた一対の第1の突起120a、120bの頂面より外側に位置する。

向に延伸して2つ設けられた第2の突起130を挟んで対向して設けられている。

断面図である。

の第1の突起120a、120bおよび一対の第1の突起120a、120bの間に設け

られた2つの第2の突起130とを有するゲート電極104と、ゲート電極104を覆う

ゲート絶縁膜105と、ゲート絶縁膜105と接して、且つゲート電極104、一対の第

1の突起120a、120b、および全ての第2の突起130に重畳する半導体膜108

と、半導体膜108と接して、且つ一対の第1の突起120a、120bと重畳する一対

の電極109a、109bと、を有する。

突起120a、120bおよび2つの第2の突起130の形状に沿って形成される。従っ

て、トランジスタ300は、三次元状のチャネル領域が形成され、トランジスタ300動

作時に機能する実効上のチャネル長Lは、図11(A)の一対の電極109a、109b

間の距離に相当する見かけ上のチャネル長に対して、少なくとも一対の第1の突起120

a、120bおよび第2の突起130の高さHの分は、長くなる(図11(B)参照)。

の断面図である。なお、図11(C)に示すように、トランジスタ300のC−D断面は

、トランジスタ100と同様である。

突起120a、120bの形状に沿って形成される。従って、トランジスタ300は、三

次元状のチャネル領域が形成され、トランジスタ300の動作時に機能する実効上のチャ

ネル幅Wは、図11(A)の一対の電極109a、109bの幅に相当する見かけ上のチ

ャネル幅に対して、少なくとも一対の第1の突起120a、120bの高さHの分は、長

くなる(図11(C)参照)。

実効上のチャネル幅Wおよび見かけ上のチャネル長Lが、3倍以上、好ましくは5倍以上

、さらに好ましくは10倍以上の長さとなるように、一対の第1の突起120a、120

bおよび2つの第2の突起130の高さHを選択する。なお、一対の第1の突起120a

、120bおよび第2の突起130は、同じ作製工程で形成されることから、一対の第1

の突起120a、120bおよび第2の突起130の高さは同じである。

スタの大きさに合わせて適宜決めればよい。なお、ゲート電極に設ける第2の突起だけで

なく、実施の形態2で説明したように、一対の第1の突起を複数設けてもよい。このよう

に、一対の第1の突起および第2の突起を複数設けることによって、一組一組(一つ一つ

)の一対の第1の突起および第2の突起の高さを低くできるため、トランジスタの作製工

程において形成される膜の被覆性を高めることができる。

ャネル長Lを長くさせて短チャネル効果を抑制することができ、さらに実効上のチャネル

幅Wも長くさせてオン電流を増大させることができるため、トランジスタのオン・オフ比

を充分に確保された良好なスイッチング特性を有するトランジスタである。

のC−D断面は、トランジスタ100と同様であるため、トランジスタ300のA−B断

面を例に説明する。

。

の第2の突起130が形成される領域の厚さは厚く、それ以外の領域の厚さは薄くなるよ

うにレジストマスク150を形成する(図12(B)参照)。なお、導電膜102におい

て、ゲート電極104が形成されない領域には、レジストマスク150も形成されないよ

うにする。一対の第1の突起120a、120bと第2の突起130との間の距離を考慮

して、レジストマスク150の薄く形成される領域の厚さを決定する。

マスクを用いて形成する厚さの異なる領域を有するレジストマスクにおいて、設ける第2

の突起130の数だけ、厚さの厚い領域を形成し、それ以外の領域の厚さは薄くなるよう

に形成すればよい。

グ)する。このエッチングにより、島状に加工された導電膜103を形成する。なお、該

エッチングはドライエッチングで行えばよい。

、120bと第2の突起130との間隔となる部分において分離されたレジストマスク1

51を形成する(図12(C)参照)。レジストマスク150の縮小(後退)には、酸素

プラズマによるアッシングを用いればよい。

一対の第1の突起120a、120bおよび第2の突起130を形成し、ゲート電極10

4を形成する。そして、該エッチングの後にレジストマスク151を除去する(図12(

D)参照)。

ことができる(図6乃至図8参照)。

の第1の突起120a、120bおよび複数の第2の突起130を設けることで、見かけ

上のチャネル長に対して、実効上のチャネル長Lを3倍以上、好ましくは5倍以上、さら

に好ましくは10倍以上の長さとすることができる。さらに、見かけ上のチャネル幅に対

して、実効上のチャネル幅Wを3倍以上、好ましくは5倍以上、さらに好ましくは10倍

以上の長さとすることができる。そのため、トランジスタのサイズを縮小しても短チャネ

ル効果の影響が低減され、半導体装置の集積度を高めることが可能となる。また、コスト

が低く、歩留まりの高い半導体装置を提供することができる。

る。

本実施の形態では、先の実施の形態に示したトランジスタとは異なる構造のトランジス

タについて説明する。

0b、および第2の突起130を含む領域と、一対の第1の突起120a、120b、お

よび第2の突起130以外の領域と、を有しているものとみなすことができる。そこで、

本実施の形態では、上記2つの異なる領域において、それぞれの領域が互いに異なる導電

材料によって構成される形態について説明する。また、本実施の形態は、実施の形態1と

比較して一対の第1の突起120a、120bおよび第2の突起130を構成する導電材

料が異なるだけであるため、実施の形態1で説明したことは、本実施の形態に適用するこ

とができる。

bおよび第2の突起130が形成されたゲート電極104を有するトランジスタ400を

例に説明する。

の第1の突起120a、120bの間に設けられる第2の突起130とを有するゲート電

極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶縁膜105と接し

て、且つ一対の第1の突起120a、120bおよび第2の突起130に重畳する半導体

膜108と、半導体膜108と接して、且つ一対の第1の突起120a、120bと重畳

する一対の電極109a、109bと、を有するボトムゲート構造のトランジスタである

。なお、図13(A)において、ゲート絶縁膜105は、便宜上、図示していない。

られた一対の第1の突起120a、120bの頂面より外側に位置する。

104に設けられた一対の第1の突起120a、120bの頂面より外側に位置する。

向に延伸して設けられた第2の突起130を挟んで対向して設けられている。

断面図である。

ト電極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶縁膜105と

接して、且つゲート電極104、該一対の第1の突起120a、120b、および該第2

の突起130に重畳する半導体膜108と、半導体膜108と接して、且つ一対の第1の

突起120a、120bと重畳する一対の電極109a、109bと、を有する。

られた一対の第1の突起120a、120bおよび第2の突起130を含む領域104b

とを有している。そして、領域104aおよび領域104bは互いに異なる導電材料から

構成されており、領域104aは第1の導電材料、領域104bは第2の導電材料で構成

されている。

る一対の第1の突起120a、120bおよび第2の突起130の形状に沿って形成され

る。従って、トランジスタ400は、三次元状のチャネル領域が形成され、トランジスタ

400動作時に機能する実効上のチャネル長Lは、図13(A)の一対の電極109a、

109b間の距離に相当する見かけ上のチャネル長に対して、少なくとも一対の第1の突

起120a、120bおよび第2の突起130の高さHの分は、長くなる(図13(B)

参照)。

断面図である。

ト電極104と、ゲート電極104を覆うゲート絶縁膜105と、ゲート絶縁膜105と

接して、且つゲート電極104、および該第1の突起120aに重畳する半導体膜108

と、半導体膜108と接して、且つ該第1の突起120aと重畳する一対の電極109a

、109bのうち一方の電極109aと、を有する。

bの一部であり、第2の導電材料で構成された一対の第1の突起120a、120bのう

ち一方である第1の突起120aを有している。

部である一対の第1の突起120a、120bの形状に沿って形成される。従って、トラ

ンジスタ400は、三次元状のチャネル領域が形成され、トランジスタ400の動作時に

機能する実効上のチャネル幅Wは、図13(A)の一対の電極109a、109bの幅に

相当する見かけ上のチャネル幅に対して、少なくとも一対の第1の突起120a、120

bの高さHの分は、長くなる(図13(C)参照。)。

実効上のチャネル幅Wおよび見かけ上のチャネル長Lが、3倍以上、好ましくは5倍以上

、さらに好ましくは10倍以上の長さとなるように、一対の第1の突起120a、120

bおよび第2の突起130の高さHを選択する。なお、一対の第1の突起120a、10

9bおよび第2の突起130は、同じ作製工程で形成されることから、一対の第1の突起

120a、120bおよび第2の突起130の高さは同じである。

形態2および実施の形態3で説明したように複数にしてもよく、作製するトランジスタの

大きさに合わせて適宜決めればよい。一対の第1の突起および第2の突起を複数設けるこ

とによって、一組一組(一つ一つ)の一対の第1の突起および第2の突起の高さを低くで

きるため、トランジスタの作製工程において形成される膜の被覆性を高めることができる

。

ャネル長Lを長くさせて短チャネル効果を抑制することができ、さらに実効上のチャネル

幅Wも長くさせてオン電流を増大させることができるため、トランジスタのオン・オフ比

を充分に確保された良好なスイッチング特性を有するトランジスタである。

のA−B断面およびC−D断面は、トランジスタ100と同様であるため、トランジスタ

400のA−B断面を例に説明する。

に第2の導電材料を用いて、導電膜102bを形成する(図14(A)参照)。導電膜1

02aおよび導電膜102b合わせて、実施の形態1に記載した導電膜102の厚さとな

るように形成すればよい。なお、導電膜102aの厚さは、導電膜102bの厚さより薄

くてもよい。

適用可能な導電材料と同様であるが、第1の導電材料に、実施の形態1で説明した金属の

酸化物を用いる場合は、該酸化物膜は金属膜と比べて抵抗が高いため、ゲート電極104

全体の抵抗を低減するために、第2の導電材料としてシート抵抗が10Ω/sq以下の低

抵抗なものを用いることが好ましい。また、第1の導電材料および第2の導電材料として

は、仕事関数差が0.6eV以内、好ましくは0.2eV以内、さらに好ましくは0.1

eV以内となるものを用いることが好ましい。

120bおよび第2の突起130が形成される領域の厚さは厚く、それ以外の領域の厚さ

は薄くなるようにレジストマスク150を形成する(図14(B)参照)。なお、導電膜

102において、ゲート電極104が形成されない領域には、レジストマスク150も形

成されないようにする。一対の第1の突起120a、120bと第2の突起130との間

の距離を考慮して、レジストマスク150の薄く形成される領域の厚さを決定する。

起130の数を複数にする場合は、多階調マスクを用いて形成する厚さの異なる領域を有

するレジストマスクにおいて、設ける一対の第1の突起120a、120bおよび第2の

突起130の数だけ、厚さの厚い領域を形成し、それ以外の領域の厚さは薄くなるように

形成すればよい。

選択的に除去(エッチング)する。このエッチングにより、島状に加工された導電膜10

3aおよび島状に加工された導電膜103bを形成する。なお、該エッチングは、導電膜

102aおよび導電膜102bの両方ともエッチングできるエッチング条件を用いて、ド

ライエッチングを行えばよい。

、120bと第2の突起130との間隔となる部分において分離されたレジストマスク1

51を形成する(図14(C)参照)。レジストマスク150の縮小(後退)には、酸素

プラズマによるアッシングを用いればよい。

、一対の第1の突起120a、120bおよび第2の突起130を形成し、領域104a

および領域104b有するゲート電極104を形成する。そして、該エッチングの後にレ

ジストマスク151を除去する(図14(D)参照)。該エッチングは、島状に加工され

た導電膜103aに対して島状に加工された導電膜103bの選択比が高いエッチング条

件を用いて、ドライエッチングを行う必要がある。

ことができる(図6乃至図8参照)。

材料で構成された領域104aと、第2の導電材料で構成された一対の第1の突起120

a、120bおよび第2の突起130を含む領域104bを設けることで、見かけ上のチ

ャネル長に対して、実効上のチャネル長Lを3倍以上、好ましくは5倍以上、さらに好ま

しくは10倍以上の長さとすることができる。さらに、見かけ上のチャネル幅に対して、

実効上のチャネル幅Wを3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の

長さとすることができる。そのため、トランジスタを縮小しても短チャネル効果の影響が

低減され、半導体装置の集積度を高めることが可能となる。また、コストが低く、歩留ま

りの高い半導体装置を提供することができる。

る。

本実施の形態では、先の実施の形態に示したトランジスタとは異なる構造のトランジス

タについて説明する。

び第2の突起が設けられた絶縁表面を有する構造物を形成するトップゲート構造のトラン

ジスタでもよい。そこで、本実施の形態では、一対の第1の突起120a、120bおよ

び第2の突起130が設けられた絶縁表面を有する構造物を有するトップゲート構造のト

ランジスタについて説明する。本実施の形態に示すトランジスタは実施の形態1に示した

トランジスタの変形例であるため、実施の形態1の説明は、適宜参照することができる。

0が形成された絶縁表面を有する構造物を有するトランジスタ500を例に説明する。

の第1の突起120a、120bの間に設けられる第2の突起130とを有して且つ絶縁

表面を有する構造物504と、一対の第1の突起120a、120bおよび第2の突起1

30に接する半導体膜108と、半導体膜108と接して、且つ一対の第1の突起120

a、120bと重畳する一対の電極109a、109bと、構造物504、半導体膜10

8、および一対の電極109a、109bを覆うゲート絶縁膜105と、ゲート絶縁膜1

05に接して、且つ一対の電極109a、109bの間に設けられるゲート電極510と

、を有するトップゲート構造のトランジスタである。なお、図15(A)において、ゲー

ト絶縁膜105は、便宜上、図示していない。

504に設けられた一対の第1の突起120a、120bの頂面より外側に位置する。

有する構造物504に設けられた一対の第1の突起120a、120bの頂面より外側に

位置する。

チャネル幅方向に延伸して設けられた第2の突起130を挟んで対向して設けられている

。

断面図である。

0a、120bおよび第2の突起130の形状に沿って形成される。従って、トランジス

タ500は、三次元状のチャネル領域が形成され、トランジスタ500動作時に機能する

実効上のチャネル長Lは、図15(A)の一対の電極109a、109b間の距離に相当

する見かけ上のチャネル長に対して、少なくとも一対の第1の突起120a、120bお

よび第2の突起130の高さHの分は、長くなる(図15(B)参照)。

第1の突起120a、120bおよび第2の突起130頂面から絶縁表面を有する構造物

504の底面に下ろした垂線において、該頂面から、絶縁表面を有する構造物504の一

対の突起120a、120bおよび第2の突起130以外の領域における上面までの距離

に相当する。

の断面図である。

の第1の突起120a、120bのうちの一方である第1の突起120aを有して且つ絶

縁表面を有する構造物504と、該第1の突起120aを覆う半導体膜108と、半導体

膜108と接して、且つ該第1の突起120aと重畳する一対の電極109a、109b

のうちの一方である電極109aと、絶縁表面を有する構造物504、半導体膜108、

電極109aを覆うゲート絶縁膜105を有する。

0a、120bの形状に沿って形成される。従って、トランジスタ500は、三次元状の

チャネル領域が形成され、トランジスタ500の動作時に機能する実効上のチャネル幅W

は、図15(A)の一対の電極109a、109bの幅に相当する見かけ上のチャネル幅

に対して、少なくとも一対の第1の突起120a、120bの高さHの分は、長くなる(

図15(C)参照)。これにより、トランジスタのサイズを縮小しつつ、トランジスタ5

00のオン電流を増大させることができる。

実効上のチャネル幅Wおよび見かけ上のチャネル長Lが、3倍以上、好ましくは5倍以上

、さらに好ましくは10倍以上の長さとなるように、一対の第1の突起120a、120

bおよび第2の突起130の高さHを選択する。

形態2および実施の形態3で説明したように複数にしてもよく、作製するトランジスタの

大きさに合わせて適宜決めればよい。一対の第1の突起および第2の突起を複数設けるこ

とによって、一組一組(一つ一つ)の一対の第1の突起および第2の突起の高さを低くで

きるため、トランジスタの作製工程において形成される膜の被覆性を高めることができる

。

ャネル長Lを長くさせて短チャネル効果を抑制することができ、さらに実効上のチャネル

幅Wも長くさせてオン電流を増大させることができるため、トランジスタのオン・オフ比

を充分に確保された良好なスイッチング特性を有するトランジスタである。

ゲート電極510とは重畳していない構成であるが、これに限定されるものではない。例

えば、一対の電極109a、109bとゲート電極510とは重畳する構成であってもよ

い。

a、109bおよびゲート電極510と重畳しない領域に、LDD領域としてドーパント

が添加された低抵抗領域を設けてもよい。LDD領域を設けることによってホットキャリ

ア劣化などのトランジスタ500の劣化が抑制され、トランジスタ500の信頼性を向上

させることができる。また、一対の電極109a、109bとゲート電極510とで形成

される寄生容量を低減することができるため、トランジスタ500の動作速度を速くする

ことができる。

に示したトランジスタ500は、一対の電極109a、109bの下面と半導体膜108

の上面とが接するトップコンタクト構造であるが、一対の電極109a、109bの上面

と半導体膜108の下面とが接するボトムコンタクト構造であってもよい。また、半導体

膜108、一対の第1の突起120a、120b、第2の突起130、および一対の電極

109a、109bのチャネル方向およびチャネル幅方向における側端の位置は、実施の

形態1と同様に、適宜選択できる。

のA−B断面を例に説明する。

膜502を形成する(図16(A)参照)。絶縁膜502の厚さは、実施の形態1で説明

した導電膜102に同様とする。

窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニ

ウム、窒化酸化アルミニウム、窒化アルミニウムなどの無機化合物またはポリイミドなど

の有機化合物を用いればよい。

縁膜502として、加熱処理により酸素を放出する膜を用いると好ましい。加熱により酸

素放出される膜を用いることで、後に形成される酸化物半導体膜107に酸素が供給され

、後に形成される絶縁表面を有する構造物504と、後に形成される酸化物半導体膜10

7との界面準位を低減できる。従って、トランジスタ500の動作に起因して生じうる電

荷などが、該界面準位に捕獲されることを抑制でき、トランジスタ500を電気特性の劣

化の少ないトランジスタとすることができる。

、基板101からの不純物(例えば、LiやNaなどのアルカリ金属など)の拡散を防止

する他に、トランジスタ500の作製工程におけるエッチング工程によって、基板101

がエッチングされることを防ぐ。それゆえ、下地絶縁膜の厚さは特に限定はないが、50

nm以上とすることが好ましい。

。アルカリ金属の侵入防止のためには、下地絶縁膜として、窒化物絶縁膜を用いることが

好ましい。

ストマスク150を形成する。レジストマスク150は、一対の第1の突起120a、1

20bおよび第2の突起130が形成される領域の厚さは厚く、それ以外の領域の厚さは

薄くなるように形成する(図16(B)参照)。なお、導電膜102において、ゲート電

極104が形成されない領域には、レジストマスク150も形成されないようにする。一

対の第1の突起120a、120bと第2の突起130との間の距離を考慮して、レジス

トマスク150の薄く形成される領域の厚さを決定すればよい。なお、ハーフトーンマス

クの代わりにグレートーンマスクのように他の多階調マスクを用いてもよい。

bおよび第2の突起130の数を複数にする場合は、多階調マスクを用いて形成する厚さ

の異なる領域を有するレジストマスクにおいて、設けられる一対の第1の突起120a、

120bおよび第2の突起130の数だけ厚さの厚い領域を形成し、それ以外の領域の厚

さは薄くなるように形成すればよい。

る。このエッチングにより、島状に加工された絶縁膜503を形成する。なお、該エッチ

ングはドライエッチングで行えばよい。

0bと第2の突起130との間隔となる部分において分離されたレジストマスク151を

形成する(図16(C)参照)。レジストマスク150の縮小(後退)には、酸素プラズ

マによるアッシングを用いればよい。

、一対の第1の突起120a、120bおよび第2の突起130を形成し、絶縁表面を有

する構造物504を形成する。そして、該エッチングの後にレジストマスク151を除去

する(図16(D)参照)。

ラズマ処理を行ってもよい。このような処理を行うことによって、一対の第1の突起12

0a、120bおよび第2の突起130の上端部の角が削られ、曲面形状にでき、以降の

トランジスタ500の作製工程において形成する膜の被覆性を高めることができる。

体膜106は実施の形態1と同様にして形成する(図17(A)参照)。

レジストマスクを用いて、酸化物半導体膜106を所望の形状にエッチングし、島状の酸

化物半導体膜107を形成する(図17(B)参照)。該エッチングは、ドライエッチン

グまたはウェットエッチングで行えばよい。

に、ゲート絶縁膜105に含まれる酸素の一部を放出し、酸化物半導体膜107中、およ

びゲート絶縁膜105と酸化物半導体膜107との界面近傍に酸素を拡散させるために、

第1の加熱処理を行い、酸化物半導体膜111を形成する(図17(C)参照)。なお、

酸化物半導体膜111は、図15に示す半導体膜108に相当する。さらに、実施の形態

1と同様に、半導体膜108は、酸化物半導体膜111のかわりに半導体特性を示す他の

材料を適用してもよい。

び酸化物半導体膜107の酸素欠損を低減し、完成したトランジスタ500の酸化物半導

体膜111とゲート絶縁膜105との界面におけるキャリア捕獲の影響を小さくすること

ができる。

態1と同様である。アルカリ金属およびアルカリ土類金属は酸化物半導体膜111にとっ

て不純物であるため、含有量は少ないことが好ましく、酸化物半導体膜111中に含まれ

るアルカリ金属の濃度は実施の形態1と同様である。

半導体膜107を形成した後だけではなく、酸化物半導体膜106を形成した後であれば

、いつ行ってもよい。さらに、第1の加熱処理は複数回行ってもよい。例えば、酸化物半

導体膜107を形成した後に1回行うだけではなく、酸化物半導体膜106を形成した後

と、酸化物半導体膜107を形成した後の2回行ってもよい。

(D)参照)。一対の電極109a、109bは実施の形態1と同様にして形成すればよ

い。なお、一対の電極109a、109bはソース電極およびドレイン電極として機能し

、ソース配線およびドレイン配線としても機能する。

09a、109bを覆うゲート絶縁膜105を形成する(図18(A)参照)。なお、ゲ

ート絶縁膜105は、実施の形態1で説明した膜種から適宜選択して形成すればよい。

10を形成する(図18(B)参照)。ゲート電極510は、実施の形態1で説明したゲ

ート電極104に適用可能な導電材料を用いて導電膜を形成し、該導電膜にフォトリソグ

ラフィ工程およびエッチング工程を行ってゲート電極510を形成する。ゲート電極51

0の厚さは、一対の電極109a、109bと同様にすればよい。

と重畳しない領域に、LDD領域としてドーパントが添加された低抵抗領域を設ける場合

は、一対の電極109a、109bおよびゲート電極510をマスクとしてドーパントを

添加することにより、セルフアラインに低抵抗領域を形成することができる。なお、ドー

パントとしては一導電性を付与できる元素として、イオンドーピング法またはイオンイン

プランテーション法を用いて添加すればよい。

工程の後に、保護絶縁膜110を形成してもよい(図18(C)参照)。保護絶縁膜11

0は、ゲート絶縁膜105と同様とすればよい。さらに、保護絶縁膜110を形成した後

に第2の加熱処理を行ってもよい。第2の加熱処理を行うことで、下地絶縁膜中の酸素の

一部、絶縁表面を有する構造物504中の酸素の一部、ゲート絶縁膜105中の酸素の一

部および保護絶縁膜110中の酸素の一部を、酸化物半導体膜111中や、下地絶縁膜お

よびゲート絶縁膜105と酸化物半導体膜111との界面近傍や、ゲート絶縁膜105と

保護絶縁膜110との界面近傍に拡散させることができるため、トランジスタ500の電

気特性を向上させることができる。なお、第2の加熱処理における装置および加熱条件は

、第1の加熱処理と同様とすればよい。

よび第2の突起130が設けられていることにより、上面図における一対の電極109a

、109b間の距離である見かけ上のチャネル長に対して、実効上のチャネル長を3倍以

上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとすることができる。さら

に、上面図における一対の電極109a、109b間の幅である見かけ上のチャネル幅に

対して、実効上のチャネル幅を3倍以上、好ましくは5倍以上、さらに好ましくは10倍

以上の長さとすることができる。そのため、トランジスタのサイズを縮小しても短チャネ

ル効果の影響が低減され、半導体装置の集積度を高めることが可能となる。また、コスト

が低く、歩留まりの高い半導体装置を提供することができる。

る。

本実施の形態では、実施の形態1乃至実施の形態5のいずれかに示したトランジスタを

用いて、半導体記憶装置を作製する例について説明する。

してキャパシタに電荷を蓄積することで、情報を記憶するDRAM、フリップフロップな

どの回路を用いて記憶内容を保持するSRAM(Static Random Acce

ss Memory)がある。

領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持する

ことで記憶を行うフラッシュメモリがある。

5のいずれかで示したトランジスタを適用することができる。

導体記憶装置であるメモリセルについて図19を用いて説明する。

スタTrと、キャパシタCと、を有する(図19(A)参照)。

ズを縮小していく必要が生じる。ところが、単にトランジスタTrのサイズを縮小してい

くと、ある程度以下のサイズとしたとき、トランジスタTrにおける短チャネル効果が無

視できなくなる。これは、短チャネル効果により、パンチスルー現象によるリーク電流が

流れやすくなり、トランジスタがスイッチング素子として機能しなくなるためである。

rの占有面積を小さくでき、かつ実効上のチャネル長を長くすることができる。そのため

、より半導体記憶装置の集積度を高めることが可能となる。

て図19(B)に示すように徐々に低減していくことが知られている。当初V0からV1

まで充電された電位は、時間が経過するとdata1を読み出す限界点であるVAまで低

減する。この期間を保持期間T_1とする。即ち、2値メモリセルの場合、保持期間T_

1の間にリフレッシュをする必要がある。

ると、酸化物半導体膜を用いたトランジスタはオフ電流が小さいため、保持期間T_1を

長くすることができる。即ち、リフレッシュ期間を長くとることが可能となるため、消費

電力を低減することができる。例えば、実施の形態1で記述したように、オフ電流が1×

10−21A以下、好ましくは1×10−24A以下となった酸化物半導体膜を用いたト

ランジスタでメモリセルを構成すると、電力を供給せずに数日間〜数十年間に渡ってデー

タを保持することが可能となる。

ジスタで構成したメモリセルの断面構造の一例を示す。なお、図19(C)および図19

(D)には、実施の形態1乃至実施の形態5で示したいずれのトランジスタも適用するこ

とができるが、例として、トランジスタ100およびトランジスタ500を適用した場合

を示す。

0およびキャパシタ190の断面構造である。なお、キャパシタ190は、トランジスタ

100のゲート電極104と同一の層かつ同一の導電材料で構成される第1の容量電極と

、一対の電極109a、109bの一方である電極109bと接続する第2の容量電極と

、第1の容量電極および第2の容量電極の間に設けられたゲート絶縁膜105と同一の層

かつ同一材料である誘電体層と、で構成される。トランジスタ100のみならず、キャパ

シタ190に対しても本発明の一態様を適用することによって、三次元のキャパシタ形状

を得ることができるため、キャパシタの占有面積も縮小することができる。

0およびキャパシタ191の断面構造である。なお、キャパシタ191は、トランジスタ

500のゲート電極510と同一の層かつ同一の導電材料で構成される第1の容量電極と

、トランジスタ500の一対の電極109a、109bの一方である電極109bと接続

する第2の容量電極と、第1の容量電極および第2の容量電極の間に設けられたトランジ

スタ500のゲート絶縁膜105と同一の層かつ同一の材料である誘電体層と、で構成さ

れる。トランジスタ500のみならず、キャパシタ191に対しても本発明の一態様を適

用することによって、三次元のキャパシタ形状を得ることができるため、キャパシタの占

有面積も縮小することができる。

示しないが、他の形態に上記キャパシタ構造を適用しても構わない。

、長期間の信頼性が高く、かつ消費電力の小さい半導体記憶装置を得ることができる。

体記憶装置であるメモリセルについて図19と異なる例について図20を用いて説明する

。

、トランジスタTr_1のゲートと接続するゲート配線GL_1と、トランジスタTr_

1のソースと接続するソース配線SL_1と、トランジスタTr_2と、トランジスタT

r_2のソースと接続するソース配線SL_2と、トランジスタTr_2のドレインと接

続するドレイン配線DL_2と、キャパシタCと、キャパシタCの一端と接続する容量配

線CLと、キャパシタCの他端、トランジスタTr_1のドレインおよびトランジスタT

r_2のゲートと接続するフローティングゲートFGと、を有する。

くと、トランジスタTr_1およびトランジスタTr_2もそれに伴いサイズを縮小して

いく必要が生じる。図20で示す半導体記憶装置は図19で示す半導体記憶装置よりも用

いるトランジスタの数が多いため、集積度を高めるためにはさらにトランジスタのサイズ

を縮小することが重要となる。

適用することで、トランジスタの占有面積は小さくでき、かつ実効上のチャネル長を長く

することができる。そのため、より半導体記憶装置の集積度を高めることが可能となる。

て、トランジスタTr_2のしきい値が変動することを利用したものである。例えば、図

20(B)は容量配線CLの電位V_CLと、トランジスタTr_2を流れるドレイン電

流Ids_2との関係を説明する図である。

ることができる。例えば、ソース配線SL_1の電位をVDDとする。このとき、ゲート

配線GL_1の電位をトランジスタTr_1のしきい値電圧VthにVDDを加えた電位

以上とすることで、フローティングゲートFGの電位をHIGHにすることができる。ま

た、ゲート配線GL_1の電位をトランジスタTr_1のしきい値電圧Vth以下とする

ことで、フローティングゲートFGの電位をLOWにすることができる。

したV_CL−Ids_2カーブのいずれかを得ることができる。即ち、FG=LOWで

は、V_CL=0VにてIds_2が小さいため、データ0となる。また、FG=HIG

Hでは、V_CL=0VにてIds_2が大きいため、データ1となる。このようにして

、データを記憶することができる。

体膜を用いたトランジスタを適用すると、該トランジスタはオフ電流を極めて小さくする

ことができるため、フローティングゲートFGに蓄積された電荷がトランジスタTr_1

を通して意図せずにリークすることを抑制できる。そのため、長期間に渡ってデータを保

持することができる。

膜を用いたトランジスタを適用してもよい。

21を用いて説明する。

ンジスタTr_1のゲートと接続するゲート配線GL_1と、トランジスタTr_1のソ

ースと接続するソース配線SL_1と、トランジスタTr_2と、トランジスタTr_2

のソースと接続するソース配線SL_2と、トランジスタTr_2のドレインと接続する

ドレイン配線DL_2と、を有し、トランジスタTr_1のドレインはトランジスタTr

_2のゲートと接続している。

いると、キャパシタを設けなくてもTr_1のドレインとTr_2のゲートの間に電荷を

保持できる。キャパシタを設けない構成であるため、小面積化が可能となり、キャパシタ

を設けた場合と比べ集積度を高めることができる。

いサイズを縮小していく必要が生じる。キャパシタを設けない構成とすることで、トラン

ジスタのサイズを縮小することがさらに重要となる。

れかに適用することで、トランジスタの占有面積は小さくした際も、実効上のチャネル長

を長くすることができる。そのため、より集積度を高めることが可能となる。

れに限定されるものではない。例えば、ソース配線SL_1とドレイン配線DL_2を共

通にする構成としても構わない。

、長期間の信頼性が高く、かつ消費電力の小さい半導体装置を得ることができる。

実施の形態1乃至実施の形態6のいずれかを一部に適用して、CPU(Central

Processing Unit)を構成することができる。

CPUは、基板1190上に、演算回路(ALU:Arithmetic logic

unit)1191、ALUコントローラ1192、インストラクションデコーダ119

3、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1

196、レジスタコントローラ1197、バスインターフェース(Bus I/F)11

98、書き換え可能なROM1199、およびROMインターフェース(ROM I/F

)1189を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを

用いる。ROM1199およびROMインターフェース1189は、別チップに設けても

よい。もちろん、図22(A)に示すCPUは、その構成を簡略化して示した一例にすぎ

ず、実際のCPUはその用途によって多種多様な構成を有している。

ンデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、イン

タラプトコントローラ1194、レジスタコントローラ1197、タイミングコントロー

ラ1195に入力される。

ーラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種

制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御す

るための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログ

ラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマス

ク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のア

ドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう

。

92、インストラクションデコーダ1193、インタラプトコントローラ1194、およ

びレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えば

タイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信

号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各

種回路に供給する。

ジスタ1196の記憶素子には、実施の形態6に記載されているいずれかの記憶素子を用

いることができる。

1からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジ

スタ1196が有する記憶素子において、位相反転素子によるデータの保持を行うか、容

量素子によるデータの保持を行うかを、選択する。位相反転素子によるデータの保持が選

択されている場合、レジスタ1196内の記憶素子への、電源電圧の供給が行われる。容

量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行

われ、レジスタ1196内の記憶素子への電源電圧の供給を停止することができる。

電源電位VDDまたは電源電位VSSの与えられているノード間に、スイッチング素子を

設けることにより行うことができる。以下に図22(B)および図22(C)の回路の説

明を行う。

チング素子に、酸化物半導体を活性層に用いたトランジスタを含む記憶回路の構成の一例

を示す。

数有する記憶素子群1143とを有している。具体的に、各記憶素子1142には、実施

の形態4に記載されている記憶素子を用いることができる。記憶素子群1143が有する

各記憶素子1142には、スイッチング素子1141を介して、ハイレベルの電源電位V

DDが供給されている。さらに、記憶素子群1143が有する各記憶素子1142には、

信号INの電位と、ローレベルの電源電位VSSの電位が与えられている。

トランジスタを用いており、該トランジスタは、そのゲート電極に与えられる信号Sig

Aによりスイッチングが制御される。

構成を示しているが、特に限定されず、トランジスタを複数有していてもよい。スイッチ

ング素子1141が、スイッチング素子として機能するトランジスタを複数有している場

合、上記複数のトランジスタは並列に接続されていてもよいし、直列に接続されていても

よいし、直列と並列が組み合わされて接続されていてもよい。

する各記憶素子1142への、ハイレベルの電源電位VDDの供給が制御されているが、

スイッチング素子1141により、ローレベルの電源電位VSSの供給が制御されていて

もよい。

チング素子1141を介して、ローレベルの電源電位VSSが供給されている、記憶装置

の一例を示す。スイッチング素子1141により、記憶素子群1143が有する各記憶素

子1142への、ローレベルの電源電位VSSの供給を制御することができる。

イッチング素子を設け、一時的にCPUの動作を停止し、電源電圧の供給を停止した場合

においてもデータを保持することが可能であり、消費電力の低減を行うことができる。例

えば、パーソナルコンピュータのユーザーが、キーボードなどの入力装置への情報の入力

を停止している間でも、CPUの動作を停止することができ、それにより消費電力を低減

することができる。

Processor)、カスタムLSI、FPGA(Field Programmab

le Gate Array)等のLSIにも応用可能である。

Uの集積度を高めることが可能となる。また、CPUの消費電力を低減することが可能と

なる。

本実施の形態では、実施の形態1乃至実施の形態5のいずれかに示したトランジスタを

用いて作製した液晶表示装置について説明する。なお、本実施の形態では液晶表示装置に

本発明の一形態を適用した例について説明するが、これに限定されるものではない。例え

ば、EL(Electro Luminescence)表示装置に本発明の一形態を適

用することも、当業者であれば容易に想到しうるものである。

は、ソース線SL_1乃至SL_a、ゲート線GL_1乃至GL_bおよび複数の画素2

000を有する。画素2000は、トランジスタ2030と、キャパシタ2020と、液

晶素子2010と、を含む。こうした画素2000が複数集まって液晶表示装置の画素部

を構成する。なお、単にソース線またはゲート線を指す場合には、ソース線SLまたはゲ

ート線GLと記載する。

スタを用いる。本発明の一態様であるトランジスタを用いることで、トランジスタの占有

面積が低減するため、開口率の高い表示装置を得ることができる。

2030のソースと接続し、トランジスタ2030のドレインは、キャパシタ2020の

一方の容量電極および液晶素子2010の一方の画素電極と接続する。キャパシタ202

0の他方の容量電極および液晶素子2010の他方の画素電極は、共通電極と接続する。

なお、共通電極はゲート線GLと同一の層かつ同一の導電材料で設けることができる。

1乃至実施の形態5のいずれかに示したトランジスタを含んでもよい。該トランジスタを

適用することで、トランジスタが縮小できるため、表示装置の額縁面積を低減することが

可能となる。また、消費電力を低減することができる。

1乃至実施の形態5のいずれかに示したトランジスタを含んでもよい。該トランジスタを

適用することで、トランジスタが縮小できるため、表示装置の額縁面積を縮小することが

可能となる。また、消費電力を低減することができる。

基板上に形成し、COG(Chip On Glass)、ワイヤボンディング、または

TAB(Tape Automated Bonding)などの方法を用いて接続して

もよい。

好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

と、ソース線SLから供給された電荷がトランジスタ2030のドレイン電流となってキ

ャパシタ2020に電荷が蓄積される。一行分の充電後、該行にあるトランジスタ203

0はオフ状態となり、ソース線SLから電圧が掛からなくなるが、キャパシタ2020に

蓄積された電荷によって必要な電圧を維持することができる。その後、次の行のキャパシ

タ2020の充電を行う。このようにして、1行〜b行の充電を行う。

いる場合、電圧を維持する期間を長くすることができる。この効果によって、動きの少な

い画像(静止画を含む。)では、表示の書き換え周波数を低減でき、消費電力の低減が可

能となる。また、キャパシタ2020の容量をさらに小さくすることが可能となるため、

充電に必要な消費電力を低減することができる。

の小さい表示装置を得ることができる。

本実施の形態では、実施の形態1乃至実施の形態8のいずれかを適用した電子機器の例

について説明する。

フォン9302と、表示部9303と、スピーカ9304と、カメラ9305と、を具備

し、携帯型電話機としての機能を有する。本発明の一態様は、表示部9303およびカメ

ラ9305に適用することができる。また、図示しないが、本体内部にある演算装置、無

線回路または記憶回路に本発明の一態様を適用することもできる。

る。本発明の一態様は、表示部9311に適用することができる。本発明の一態様を用い

ることで、表示部9311のサイズを大きくしたときにも消費電力の低いディスプレイと

することができる。

マイクロフォン9322と、表示部9323と、を具備する。本発明の一態様は、表示部

9323に適用することができる。また、図示しないが、記憶回路またはイメージセンサ

に本発明の一態様を適用することもできる。

減することができる。

101 基板

102 導電膜

102a 導電膜

102b 導電膜

103 導電膜

103a 導電膜

103b 導電膜

104 ゲート電極

104a 領域

104b 領域

105 ゲート絶縁膜

106 酸化物半導体膜

107 酸化物半導体膜

108 半導体膜

109a 電極

109b 電極

110 保護絶縁膜

111 酸化物半導体膜

120a 突起

120b 突起

130 突起

140 基板

141a 半透過層

141b 遮光層

150 レジストマスク

151 レジストマスク

190 キャパシタ

191 キャパシタ

200 トランジスタ

300 トランジスタ

301 基板

302 遮光部

303 回折格子部

304 グレートーンマスク

311 基板

312 半透光部

313 遮光部

314 ハーフトーンマスク

400 トランジスタ

500 トランジスタ

502 絶縁膜

503 絶縁膜

504 構造物

510 ゲート電極

1141 スイッチング素子

1142 記憶素子

1143 記憶素子群

1189 ROMインターフェース

1190 基板

1191 ALU

1192 ALUコントローラ

1193 インストラクションデコーダ

1194 インタラプトコントローラ

1195 タイミングコントローラ

1196 レジスタ

1197 レジスタコントローラ

1198 バスインターフェース

1199 ROM

2000 画素

2010 液晶素子

2020 キャパシタ

2030 トランジスタ

9300 筐体

9301 ボタン

9302 マイクロフォン

9303 表示部

9304 スピーカ

9305 カメラ

9310 筐体

9311 表示部

9320 筐体

9321 ボタン

9322 マイクロフォン

9323 表示部

Claims (7)

- 一対の第1の突起と、前記一対の第1の突起の間に設けられる第2の突起とを有し、且つ絶縁表面を有する構造物と、

前記一対の第1の突起および前記第2の突起に接する半導体膜と、

前記半導体膜と接して、且つ前記一対の第1の突起に重畳する一対の電極と、

前記構造物、前記半導体膜、および前記一対の電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜に接して、且つ前記一対の電極の間に設けられるゲート電極と、を有し、

チャネル幅方向における前記半導体膜の側端は、前記一対の第1の突起の頂面より外側であり、

前記チャネル幅方向における前記一対の電極の側端は、前記一対の第1の突起の頂面より外側であることを特徴とする半導体装置。 - 複数の一対の第1の突起と、前記複数の一対の第1の突起の間に設けられる第2の突起とを有し、且つ絶縁表面を有する構造物と、

前記複数の一対の第1の突起および前記第2の突起に接する半導体膜と、

前記半導体膜と接して、且つ前記複数の一対の第1の突起に重畳する一対の電極と、

前記構造物、前記半導体膜、および前記一対の電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜に接して、且つ前記一対の電極の間に設けられるゲート電極と、を有し、

チャネル幅方向における前記半導体膜の側端は、前記複数の一対の第1の突起のうち異なる一対の第1の突起の頂面上にあり、

前記チャネル幅方向における前記一対の電極の側端は、前記複数の一対の第1の突起のうち異なる前記一対の第1の突起の頂面上にあることを特徴とする半導体装置。 - 請求項1または2において、

前記第2の突起は、前記半導体膜のチャネル長方向において、複数設けられていることを特徴とする半導体装置。 - 請求項1乃至3のいずれか一において、

前記絶縁表面を有する構造物は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウムまたは窒化アルミニウムを含むことを特徴とする半導体装置。 - 請求項1乃至4のいずれか一において、

前記半導体膜に形成される実効上のチャネル長は、上面から見た前記一対の電極間の距離である見かけ上のチャネル長に対して3倍以上の長さを有することを特徴とする半導体装置。 - 請求項1乃至5のいずれか一において、

前記半導体膜に形成される実効上のチャネル幅は、上面から見た前記一対の電極の幅である見かけ上のチャネル幅に対して3倍以上の長さを有することを特徴とする半導体装置。 - 請求項1乃至6のいずれか一において、

前記半導体膜は、酸化物半導体膜であることを特徴とする半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011047759 | 2011-03-04 | ||

| JP2011047759 | 2011-03-04 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012042660A Division JP5961404B2 (ja) | 2011-03-04 | 2012-02-29 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016187048A JP2016187048A (ja) | 2016-10-27 |

| JP6133476B2 true JP6133476B2 (ja) | 2017-05-24 |

Family

ID=46752768

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012042660A Expired - Fee Related JP5961404B2 (ja) | 2011-03-04 | 2012-02-29 | 半導体装置 |

| JP2016126148A Expired - Fee Related JP6133476B2 (ja) | 2011-03-04 | 2016-06-27 | 半導体装置 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012042660A Expired - Fee Related JP5961404B2 (ja) | 2011-03-04 | 2012-02-29 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8785933B2 (ja) |

| JP (2) | JP5961404B2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014085552A (ja) * | 2012-10-24 | 2014-05-12 | Japan Display Inc | 表示装置 |

| CN103824780B (zh) * | 2014-02-28 | 2016-03-30 | 上海和辉光电有限公司 | 一种低温多晶硅tft器件及其制造方法 |

| CN104409510A (zh) * | 2014-10-28 | 2015-03-11 | 京东方科技集团股份有限公司 | 薄膜晶体管及制备方法、阵列基板及制备方法、显示装置 |

| KR102491851B1 (ko) * | 2015-07-02 | 2023-01-26 | 삼성전자주식회사 | 마이크로 구조체를 포함하는 플렉서블 바이모달 센서 |

| US11189736B2 (en) * | 2015-07-24 | 2021-11-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR102547089B1 (ko) * | 2015-12-07 | 2023-06-26 | 엘지디스플레이 주식회사 | 박막 트랜지스터 및 그 제조방법과 그를 구비한 표시장치 |

| KR102537286B1 (ko) * | 2016-07-04 | 2023-05-30 | 삼성디스플레이 주식회사 | 표시 기판 및 이의 제조 방법 |

| JP6536634B2 (ja) | 2017-07-28 | 2019-07-03 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| TWI646691B (zh) * | 2017-11-22 | 2019-01-01 | 友達光電股份有限公司 | 主動元件基板及其製造方法 |

| CN110809825A (zh) * | 2017-12-15 | 2020-02-18 | 深圳市柔宇科技有限公司 | 薄膜晶体管及制备方法、显示装置 |

| JP6732821B2 (ja) * | 2018-02-22 | 2020-07-29 | 株式会社東芝 | 半導体装置の製造方法 |

Family Cites Families (110)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62128177A (ja) * | 1985-11-29 | 1987-06-10 | Toshiba Corp | 薄膜トランジスタ |

| JPH02140980A (ja) * | 1988-11-22 | 1990-05-30 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JPH04214673A (ja) * | 1990-12-13 | 1992-08-05 | Sharp Corp | 薄膜トランジスタ及びその製造方法 |

| JPH05110098A (ja) * | 1991-10-17 | 1993-04-30 | Seiko Epson Corp | 薄膜mos型トランジスタ |

| JP3298974B2 (ja) | 1993-03-23 | 2002-07-08 | 電子科学株式会社 | 昇温脱離ガス分析装置 |

| KR970005945B1 (ko) * | 1993-08-09 | 1997-04-22 | 엘지반도체 주식회사 | 반도체 박막트랜지스터 제조방법 |

| JP3485983B2 (ja) * | 1994-12-22 | 2004-01-13 | エルジイ・セミコン・カンパニイ・リミテッド | 薄膜トランジスタの構造及びその製造方法 |

| DE69635107D1 (de) | 1995-08-03 | 2005-09-29 | Koninkl Philips Electronics Nv | Halbleiteranordnung mit einem transparenten schaltungselement |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP3173462B2 (ja) * | 1998-06-09 | 2001-06-04 | 日本電気株式会社 | 薄膜トランジスタ |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| US7071037B2 (en) * | 2001-03-06 | 2006-07-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| US6841797B2 (en) | 2002-01-17 | 2005-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device formed over a surface with a drepession portion and a projection portion |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US6884668B2 (en) | 2002-02-22 | 2005-04-26 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method therefor |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| EP2413366B1 (en) | 2004-03-12 | 2017-01-11 | Japan Science And Technology Agency | A switching element of LCDs or organic EL displays |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7868326B2 (en) | 2004-11-10 | 2011-01-11 | Canon Kabushiki Kaisha | Field effect transistor |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| CA2585063C (en) | 2004-11-10 | 2013-01-15 | Canon Kabushiki Kaisha | Light-emitting device |

| CN101057339B (zh) | 2004-11-10 | 2012-12-26 | 佳能株式会社 | 无定形氧化物和场效应晶体管 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI445178B (zh) | 2005-01-28 | 2014-07-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| JP2006245371A (ja) | 2005-03-04 | 2006-09-14 | Toppan Printing Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP4951878B2 (ja) * | 2005-05-31 | 2012-06-13 | ソニー株式会社 | 電界効果型トランジスタの製造方法 |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| US7867791B2 (en) | 2005-07-29 | 2011-01-11 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device using multiple mask layers formed through use of an exposure mask that transmits light at a plurality of intensities |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| EP3614442A3 (en) | 2005-09-29 | 2020-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device having oxide semiconductor layer and manufactoring method thereof |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| JP2007134546A (ja) * | 2005-11-11 | 2007-05-31 | Fuji Electric Holdings Co Ltd | 薄膜トランジスタ |

| KR101117948B1 (ko) | 2005-11-15 | 2012-02-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 디스플레이 장치 제조 방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| CN101663762B (zh) | 2007-04-25 | 2011-09-21 | 佳能株式会社 | 氧氮化物半导体 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP2009152487A (ja) * | 2007-12-21 | 2009-07-09 | Seiko Epson Corp | 薄膜トランジスタ、半導体装置及び電気光学装置 |

| JP5409024B2 (ja) * | 2008-02-15 | 2014-02-05 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP5543116B2 (ja) * | 2009-01-29 | 2014-07-09 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TWI485781B (zh) * | 2009-03-13 | 2015-05-21 | Semiconductor Energy Lab | 半導體裝置及該半導體裝置的製造方法 |

-

2012

- 2012-02-23 US US13/402,938 patent/US8785933B2/en active Active

- 2012-02-29 JP JP2012042660A patent/JP5961404B2/ja not_active Expired - Fee Related

-

2016

- 2016-06-27 JP JP2016126148A patent/JP6133476B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP5961404B2 (ja) | 2016-08-02 |

| US8785933B2 (en) | 2014-07-22 |

| US20120223311A1 (en) | 2012-09-06 |

| JP2016187048A (ja) | 2016-10-27 |

| JP2012199525A (ja) | 2012-10-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6133476B2 (ja) | 半導体装置 | |

| JP7717909B2 (ja) | 半導体装置 | |

| JP7406609B2 (ja) | 半導体装置 | |

| US20240222517A1 (en) | Semiconductor device and manufacturing method thereof | |

| JP6518358B2 (ja) | 半導体装置の作製方法 | |

| JP6197075B2 (ja) | 半導体装置 | |

| JP6006511B2 (ja) | 半導体装置 | |

| TWI594326B (zh) | 半導體裝置及其製造方法 | |

| CN102683386B (zh) | 半导体装置 | |

| JP6027792B2 (ja) | 半導体装置およびその作製方法 | |

| TWI553860B (zh) | 半導體裝置 | |

| JP5986392B2 (ja) | 半導体装置 | |

| US20120235137A1 (en) | Oxide semiconductor film, semiconductor device, and manufacturing method of semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170323 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170328 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170419 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6133476 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |