JP6125072B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP6125072B2 JP6125072B2 JP2016087133A JP2016087133A JP6125072B2 JP 6125072 B2 JP6125072 B2 JP 6125072B2 JP 2016087133 A JP2016087133 A JP 2016087133A JP 2016087133 A JP2016087133 A JP 2016087133A JP 6125072 B2 JP6125072 B2 JP 6125072B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- oxygen

- oxide

- oxide semiconductor

- heat treatment

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 143

- 238000000034 method Methods 0.000 title claims description 31

- 238000004519 manufacturing process Methods 0.000 title claims description 17

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 107

- 229910052760 oxygen Inorganic materials 0.000 claims description 107

- 239000001301 oxygen Substances 0.000 claims description 107

- 238000010438 heat treatment Methods 0.000 claims description 73

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 33

- 239000001257 hydrogen Substances 0.000 claims description 28

- 229910052739 hydrogen Inorganic materials 0.000 claims description 28

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 25

- 238000009792 diffusion process Methods 0.000 claims description 17

- 238000004458 analytical method Methods 0.000 claims description 10

- 239000011701 zinc Substances 0.000 claims description 8

- 229910052738 indium Inorganic materials 0.000 claims description 5

- 229910052733 gallium Inorganic materials 0.000 claims description 4

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 4

- 229910052725 zinc Inorganic materials 0.000 claims description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 2

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims 1

- 239000010408 film Substances 0.000 description 354

- 239000002585 base Substances 0.000 description 100

- 239000000758 substrate Substances 0.000 description 55

- 239000007789 gas Substances 0.000 description 39

- 229910044991 metal oxide Inorganic materials 0.000 description 33

- 150000004706 metal oxides Chemical class 0.000 description 33

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 23

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 21

- 239000000463 material Substances 0.000 description 20

- 238000003795 desorption Methods 0.000 description 19

- 125000004430 oxygen atom Chemical group O* 0.000 description 19

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical compound CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 18

- 230000001681 protective effect Effects 0.000 description 18

- 229910052814 silicon oxide Inorganic materials 0.000 description 18

- 238000004544 sputter deposition Methods 0.000 description 18

- 239000013078 crystal Substances 0.000 description 17

- 125000004429 atom Chemical group 0.000 description 15

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 239000010410 layer Substances 0.000 description 14

- 229910007541 Zn O Inorganic materials 0.000 description 13

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 11

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 11

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 10

- 229910052751 metal Inorganic materials 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- 230000001590 oxidative effect Effects 0.000 description 10

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 230000006870 function Effects 0.000 description 8

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 238000001312 dry etching Methods 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 6

- 229910052782 aluminium Inorganic materials 0.000 description 6

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 229910001882 dioxygen Inorganic materials 0.000 description 6

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 6

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 6

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 6

- 229910001928 zirconium oxide Inorganic materials 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 229910052786 argon Inorganic materials 0.000 description 5

- 229920001940 conductive polymer Polymers 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 239000002019 doping agent Substances 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 229910003437 indium oxide Inorganic materials 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910019092 Mg-O Inorganic materials 0.000 description 3

- 229910019395 Mg—O Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000010949 copper Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 150000002431 hydrogen Chemical class 0.000 description 3

- -1 hydrogen ions Chemical class 0.000 description 3

- 238000003780 insertion Methods 0.000 description 3

- 230000037431 insertion Effects 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000010453 quartz Substances 0.000 description 3

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 3

- 229920000178 Acrylic resin Polymers 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910001195 gallium oxide Inorganic materials 0.000 description 2

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 2

- 150000004678 hydrides Chemical class 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 239000001272 nitrous oxide Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920002620 polyvinyl fluoride Polymers 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 238000005477 sputtering target Methods 0.000 description 2

- 241000465531 Annea Species 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910004129 HfSiO Inorganic materials 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- 229910020994 Sn-Zn Inorganic materials 0.000 description 1

- 229910009069 Sn—Zn Inorganic materials 0.000 description 1

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 238000000231 atomic layer deposition Methods 0.000 description 1

- 229910052790 beryllium Inorganic materials 0.000 description 1

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical compound [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 description 1

- 230000002457 bidirectional effect Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910000423 chromium oxide Inorganic materials 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011777 magnesium Substances 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 230000008520 organization Effects 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 239000011112 polyethylene naphthalate Substances 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000004549 pulsed laser deposition Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229930192474 thiophene Natural products 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/0242—Crystalline insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66969—Multistep manufacturing processes of devices having semiconductor bodies not comprising group 14 or group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02422—Non-crystalline insulating materials, e.g. glass, polymers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02488—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02494—Structure

- H01L21/02496—Layer structure

- H01L21/02502—Layer structure consisting of two layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02551—Group 12/16 materials

- H01L21/02554—Oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02565—Oxide semiconducting materials not being Group 12/16 materials, e.g. ternary compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02656—Special treatments

- H01L21/02658—Pretreatments

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/517—Insulating materials associated therewith the insulating material comprising a metallic compound, e.g. metal oxide, metal silicate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78603—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the insulating substrate or support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

Description

、半導体素子自体または半導体素子を含むものをいい、このような半導体素子として、例

えばトランジスタ(薄膜トランジスタなど)が挙げられる。また、液晶表示装置などの表

示装置も半導体装置に含まれる。

例えば、特許文献1及び特許文献2)。

領域に用いた半導体装置と比較して、非常に高い電界効果移動度を有するなどの良好な電

気的特性を有する。しかし、信頼性の面において課題がある。酸化物半導体膜をチャネル

形成領域に用いた半導体装置の信頼性を低下させる要因の一つとして、酸化物半導体膜に

含まれる水及び水素が挙げられる。従って、酸化物半導体膜における水及び水素の含有量

は少なくすることが肝要である。

含まれる酸素欠損が多いと、酸素欠損の存在する領域が低抵抗化し、ソースとドレインの

間にリーク電流を生じさせる原因となる。従って、酸化物半導体膜の酸素欠損を低減する

ことが好ましく、酸素欠損を低減するためには外部から酸素を供給すればよい。

素を供給する手段の一つとして、酸化物半導体膜に接して酸素を含む下地膜が設けられた

状態で行う加熱処理が挙げられる。下地膜における水及び水素の含有量を少なくし、酸素

の含有量を多くして加熱処理すると、酸化物半導体膜への水及び水素の混入を抑制しつつ

、酸化物半導体膜に酸素を供給することができる。

ング法などにより下地膜を形成した後酸化物半導体膜を形成する前に、加熱処理を行えば

よい。しかし、単純に加熱処理を行うと、水及び水素とともに酸素も脱離してしまうとい

う問題がある。

水素の含有量を少なくし、酸素の含有量を多くすることで、酸化物半導体膜における水及

び水素の含有量を少なくし、前記下地膜から前記酸化物半導体膜に酸素欠損を低減するた

めの酸素を供給することが可能な半導体装置の作製方法を提供することを課題とする。

である。本発明の一態様である半導体装置の作製方法は、積層下地膜を形成し、第1の加

熱処理を行い、前記積層下地膜上に接して酸化物半導体膜を形成し、第2の加熱処理を行

い、前記積層下地膜では、第1の下地膜と第2の下地膜がこの順に積層されており、前記

第1の下地膜は、前記第2の加熱処理により酸素を放出する絶縁性の酸化物膜であり、前

記第2の下地膜における酸素の拡散係数は、前記第1の下地膜における酸素の拡散係数よ

りも小さいことを特徴とする。ここで、前記第1の加熱処理は、前記積層下地膜からの酸

素の脱離を抑制しつつ水及び水素を脱離させる工程であり、前記第2の加熱処理は、前記

第1の下地膜を酸素の供給源として前記第2の下地膜に酸素を供給する工程である。

第2の下地膜を形成し、前記基板に第1の加熱処理を行って前記第1の下地膜及び前記第

2の下地膜中の水及び水素を除去し、前記第2の下地膜上に酸化物半導体膜を形成し、前

記基板に第2の加熱処理を行って前記第1の下地膜から前記第2の下地膜を介して前記酸

化物半導体膜に酸素を供給し、前記酸化物半導体膜を加工することで島状の酸化物半導体

膜を形成し、前記島状の酸化物半導体膜を覆ってゲート絶縁膜を形成し、前記島状の酸化

物半導体膜の一部と重畳して前記ゲート絶縁膜上にゲート電極を形成し、前記島状の酸化

物半導体膜に接続されたソース電極及びドレイン電極を形成し、前記第2の下地膜におけ

る酸素の拡散係数が、前記第1の下地膜における酸素の拡散係数よりも小さいことを特徴

とする半導体装置の作製方法である。

第2の下地膜を形成し、前記基板に250℃以上350℃以下で第1の加熱処理を行い、

前記第2の下地膜上に酸化物半導体膜を形成し、前記基板に前記第1の加熱処理よりも高

温且つ450℃以下の温度で第2の加熱処理を行い、前記酸化物半導体膜を加工すること

で島状の酸化物半導体膜を形成し、前記島状の酸化物半導体膜を覆ってゲート絶縁膜を形

成し、前記島状の酸化物半導体膜の一部と重畳して前記ゲート絶縁膜上にゲート電極を形

成し、前記島状の酸化物半導体膜に接続されたソース電極及びドレイン電極を形成し、前

記第2の下地膜における酸素の拡散係数が、前記第1の下地膜における酸素の拡散係数よ

りも小さいことを特徴とする半導体装置の作製方法である。

10nm以下であることが好ましい。

。

ることができる。前記金属酸化物膜は、酸化イットリウム膜、酸化ジルコニウム膜、酸化

アルミニウム膜、酸化イットリウムが添加された酸化ジルコニウム膜のいずれかであるこ

とが好ましい。

物半導体膜に酸素欠損を低減するための酸素を供給することができるため、信頼性の高い

半導体装置を作製することができる。

は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及

び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発

明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

本実施の形態では、本発明の一態様である半導体装置の作製方法について説明する。

膜を形成する(図1(A))。そして、第2の下地膜104を形成した後に第1の加熱処

理を行う。第1の加熱処理は、積層下地膜からの酸素の脱離を抑制しつつ水及び水素を脱

離させる工程である。

セラミック基板またはプラスチック基板などを適宜用いることができる。または、基板1

00として、可とう性を有するガラス基板または可とう性を有するプラスチック基板を用

いることができる。プラスチック基板の材料としては、屈折率異方性の小さい材料を用い

ることが好ましい。例えば、ポリエーテルサルフォン(PES)、ポリイミドフィルム、

ポリエチレンナフタレート(PEN)、ポリビニルフルオライド(PVF)、ポリエステ

ル、ポリカーボネート(PC)、アクリル樹脂または半硬化した有機樹脂中に繊維体を含

むプリプレグなどを用いることができる。

離する絶縁性酸化物により形成する。酸素の一部が加熱処理により脱離する絶縁性酸化物

としては、化学量論比よりも多くの酸素を含むものを用いることが好ましい。これは、加

熱処理により、第1の下地膜102に接する酸化物半導体膜に酸素を拡散させることがで

きるためである。

x>2である酸化シリコンが挙げられる。ただし、これに限定されず、第1の下地膜10

2は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒

化アルミニウム、酸化ガリウム、酸化ハフニウムまたは酸化イットリウムなどで形成して

もよい。

のをいう。

のをいう。

例えば、窒化シリコン膜上に酸化シリコン膜が設けられた積層膜が挙げられる。

理により脱離しやすい。化学量論比よりも多くの酸素を含む絶縁性酸化物のTDS分析に

よる酸素の脱離量(酸素原子に換算した値)は、1.0×1018atoms/cm3以

上、好ましくは1.0×1020atoms/cm3以上、より好ましくは3.0×10

20atoms/cm3以上であるとよい。

オン強度の時間積分値に比例する。このため、絶縁性酸化物におけるこの時間積分値と、

リファレンスとなる標準試料の基準値から、気体の脱離量を計算することができる。標準

試料の基準値は、ある特定の原子を含む試料(標準試料)におけるイオン強度の時間積分

値に対する原子密度の割合である。

値と絶縁性酸化物のイオン強度の時間積分値から、絶縁性酸化物の酸素分子(O2)の脱

離量(NO2)は、以下の式(1)で求めることができる。

NO2=(NH2/SH2)×SO2×α (1)

は、標準試料の水素分子(H2)のイオン強度の時間積分値である。すなわち、NH2/

SH2を標準試料の基準値とする。SO2は、絶縁性酸化物の酸素分子(O2)のイオン

強度の時間積分値である。αは、イオン強度に影響する係数である。前記式(1)の詳細

に関しては、特開平06−275697号公報を参照されたい。

は、電子科学株式会社製の昇温脱離分析装置EMD−WA1000S/Wを用い、標準試

料として1×1016atoms/cm3の水素原子を含むシリコンウェハを用いたとき

の値である。

原子の比率は、酸素分子のイオン化率から算出することができる。なお、前記係数αは酸

素分子のイオン化率を含んでいるため、酸素分子の放出量を評価することで、酸素原子の

放出量についても算出することができる。

の脱離量は、酸素分子(O2)の脱離量の2倍である。

ればよいが、好ましくはスパッタリング法を用いる。第1の下地膜102として酸化シリ

コン膜を形成する場合には、ターゲットとして石英(好ましくは合成石英)ターゲット、

スパッタリングガスとしてアルゴンガスを用いればよい。または、ターゲットとしてシリ

コンターゲット、スパッタリングガスとして酸素を含むガスを用いてもよい。なお、酸素

を含むガスとしては、アルゴンガスと酸素ガスの混合ガスでもよいし、酸素ガスのみであ

ってもよい。

上500nm以下とするとよい。

、第2の下地膜104における酸素の拡散係数は、第1の下地膜102における酸素の拡

散係数よりも小さい。ここで、拡散係数は、第2の加熱処理時の温度における値とする。

下地膜102(後の説明では酸化シリコン膜)上に第2の加熱処理時の温度における酸素

の拡散係数が第1の下地膜102より小さい第2の下地膜104(後の説明では酸化アル

ミニウム膜)が設けられていることで、第1の下地膜102のみが設けられている場合よ

りも高温で、第2の下地膜104から酸素が放出されるようにすることができる。ここで

、仮に、第2の加熱処理時の温度において、第2の下地膜104における酸素の拡散係数

が第1の下地膜102における酸素の拡散係数よりも大きい場合には、第2の加熱処理時

の温度よりも低温で第2の下地膜104中の酸素が放出されてしまうことになる。

ム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化タンタル膜、酸化マグネシウム膜

、酸化アルミニウム膜、酸化イットリウムが添加された酸化ジルコニウム(YSZ)膜の

いずれかを挙げることができるが、酸化イットリウム膜、酸化ジルコニウム膜、酸化アル

ミニウム膜、酸化イットリウムが添加された酸化ジルコニウム膜のいずれかであることが

好ましい。

、好ましくはスパッタリング法を用いる。

m以下とすればよい。

制しつつ、水及び水素を脱離させる工程である。第1の加熱処理の温度は、250℃以上

350℃以下とするとよい。

地膜104を酸化アルミニウム膜とすることが特に好ましい。すなわち、第1の下地膜1

02と第2の下地膜104が積層して設けられた積層下地膜は、酸化シリコン膜上に酸化

アルミニウム膜が設けられた積層膜であることが特に好ましい。

積層膜について、実験データを参照しつつ説明する。

膜104として酸化アルミニウム膜を形成し、第1の加熱処理を行った。

し、基板100を400℃で10分間加熱した。

ッタリングターゲットとしては、酸化シリコンターゲットを用いた。チャンバー内にアル

ゴンガスを25sccm、酸素ガスを25sccmで導入し、チャンバー内の圧力を0.

4Paとし、電力を2.0kWとし、基板100の温度を100℃としてスパッタリング

を行い、基板100上に第1の下地膜102である酸化シリコン膜を300nmの厚さで

形成した。

スパッタリングターゲットとしては、酸化アルミニウムターゲットを用いた。チャンバー

内にアルゴンガスを25sccm、酸素ガスを25sccmで導入し、チャンバー内の圧

力を0.4Paとし、電力を1.5kWとし、基板100の温度を250℃としてスパッ

タリングを行い、基板100上に第2の下地膜104である酸化アルミニウム膜を形成し

た。

った。

した。

成した。

成した。

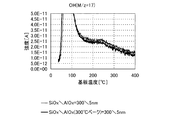

て加熱していき、TDS分析を行った。TDS分析結果を図7(A)乃至図9(B)に示

す。図7(A)乃至図9(B)では、横軸は基板温度(セルシウス温度)を示し、縦軸は

イオン強度(AはAbsoluteの略であり、絶対値を示す。)、すなわち脱離量を示

す。なお、M/z値=1を水素原子、M/z値=18を水分子、M/z値=17を水酸基

、M/z値=16を酸素原子、M/z値=32を酸素分子とする。

する。第2の試料はSiOx\AlOx=300\5nmと表記する。第3の試料はSi

Ox\AlOx=300\10nmと表記する。第4の試料はSiOx\AlOx=30

0\30nmと表記する。

。一方で、図9(A)(酸素原子のイオン強度)では、第1の試料は200〜250℃に

ピークを有し、第2の試料は約300℃にピークを有し、第3の試料は約400℃にピー

クを有し、第4の試料はピークを有していない。図9(B)(酸素分子のイオン強度)で

も同様に、第1の試料は200〜250℃にピークを有し、第2の試料は約300℃にピ

ークを有し、第3の試料は約400℃にピークを有し、第4の試料は測定範囲(400℃

まで)にピークを有していない。

子、水分子、水酸基の脱離量を変化させることなく、酸素分子及び酸素原子の脱離量を調

整することができる。例えば、第2の試料では、250〜300℃で第1の加熱処理を行

うことで、積層下地膜中の酸素の脱離を抑制しつつ水素原子、水分子、水酸基を脱離させ

ることができるといえる。第3の試料では、250〜350℃で第1の加熱処理を行うこ

とで、積層下地膜中の酸素の脱離を抑制しつつ水素原子、水分子、水酸基を脱離させるこ

とができるといえる。第4の試料では、250〜400℃で(場合によっては400℃を

越えてもよい。)第1の加熱処理を行うことで、積層下地膜中の酸素の脱離を抑制しつつ

水素原子、水分子、水酸基を脱離することができるといえる。第2の下地膜104が設け

られ、その厚さが厚くなることで、水素原子、水分子、水酸基を脱離する温度を変化させ

ずに酸素が多量に放出される温度を高温側にシフトさせることができる。

地膜から酸化物半導体膜に酸素を供給する際に、積層下地膜から酸素を引き抜くために4

00℃よりも高温にする必要があり、後の第2の加熱処理において酸化物半導体膜への酸

素の供給が困難になる。従って、第2の下地膜104である酸化アルミニウム膜の厚さは

、好ましくは試料3のように10nm以下、最も好ましくは5nm程度とする。

程度とした場合には、第1の加熱処理は250〜300℃で行うことができる。ここで、

第1の加熱処理を行わずにTDS分析を行った試料(試料Aとする。)について比較する

。TDS分析結果を図10(A)乃至図12(B)に示す。図10(A)乃至図12(B

)では、横軸は基板温度(セルシウス温度)を示し、縦軸はイオン強度(AはAbsol

uteの略であり、絶対値を示す。)、すなわち脱離量を示す。なお、M/z値=1を水

素原子、M/z値=18を水分子、M/z値=17を水酸基、M/z値=16を酸素原子

、M/z値=32を酸素分子とする。

はSiOx\AlOx=300\5nmと表記する。第1の加熱処理を300℃で行った

試料BはSiOx\AlOx(300℃ベーク)=300\5nmと表記する。

た後に第1の加熱処理を行わなかった試料である。試料Bは第2の下地膜104である酸

化アルミニウム膜を厚さ5nmで形成した後に第1の加熱処理を300℃で行った試料で

ある。

2点(第1の接点204と第2の接点206)で接する直線208を描き、曲線200と

直線208によって囲まれた閉領域202を脱離量とした(図13)。

。これは、第1の加熱処理(加熱温度300℃)によって、試料Bから水分子が予め除去

されているからである。図12(A)及び(B)(酸素原子及び酸素分子の脱離量)によ

れば、第1の加熱処理後でも試料Bの酸素原子及び酸素分子の脱離量は十分に存在する。

とができ、第2の加熱処理において供給する酸素も十分に確保することができるといえる

。本実施の形態において、最も好ましくは、第2の下地膜104である酸化アルミニウム

膜を5nmで形成し、第1の加熱処理を300℃で行う。

る(図1(B))。更には、第2の加熱処理を行う。第2の加熱処理は、第1の下地膜1

02を酸素の供給源として第2の下地膜104に酸素を供給する工程である。ただし、第

2の加熱処理を行うタイミングはこれに限定されず、酸化物半導体膜106を加工した後

に第2の加熱処理を行ってもよい。

酸化物、三元系金属酸化物であるIn−Ga−Zn−O系金属酸化物、In−Sn−Zn

−O系金属酸化物、In−Al−Zn−O系金属酸化物、Sn−Ga−Zn−O系金属酸

化物、Al−Ga−Zn−O系金属酸化物若しくはSn−Al−Zn−O系金属酸化物、

または二元系金属酸化物であるIn−Zn−O系金属酸化物、Sn−Zn−O系金属酸化

物、Al−Zn−O系金属酸化物、Zn−Mg−O系金属酸化物、Sn−Mg−O系金属

酸化物、In−Mg−O系金属酸化物若しくはIn−Ga−O系金属酸化物などを用いて

形成されていればよい。または、In−O系金属酸化物、Sn−O系金属酸化物、Zn−

O系金属酸化物などを用いて形成されていてもよい。なお、「n元系金属酸化物」はn種

類の金属酸化物で構成されるものである。ここで、例えば、In−Ga−Zn−O系金属

酸化物は、インジウム(In)、ガリウム(Ga)、亜鉛(Zn)を有する酸化物という

意味であり、その組成比は特に問わない。また、InとGaとZn以外の元素が含まれて

いてもよい。

ことが好ましい。酸素(O)を過剰に含ませると、形成される酸化物半導体膜106の酸

素欠損によるキャリアの生成を抑制することができる。

る場合には、ターゲットの組成を原子数比で、In/Zn=1〜100、好ましくはIn

/Zn=1〜20、さらに好ましくはIn/Zn=1〜10とする。Znに対するInの

原子数比を好ましい前記範囲とすることで、電界効果移動度を向上させることができる。

ここで、酸素(O)を過剰に含ませるために、化合物の原子数比In:Zn:O=X:Y

:Zを、Z>1.5X+Yとすることが好ましい。

プが2eV以上、好ましくは2.5eV以上、更に好ましくは3eV以上であるとよい。

このように、バンドギャップの広い金属酸化物を用いると、トランジスタのオフ電流を低

減することができる。

分子、水、水酸基、またはその他の水素化物として含まれる場合もある。酸化物半導体膜

106に含まれる水素は、極力少ないことが好ましい。

ことが好ましく、これらの濃度は、好ましくは1×1018atoms/cm3以下、更

に好ましくは2×1016atoms/cm3以下とする。アルカリ金属及びアルカリ土

類金属が酸化物半導体と結合すると、キャリアが生成することがあり、トランジスタのオ

フ電流を増大させる原因となるからである。

スタのサイズなどに応じて決めればよい。酸化物半導体膜106の形成方法としては、例

えば、スパッタリング法、塗布法、印刷法またはパルスレーザー蒸着法などが挙げられる

。酸化物半導体膜106の厚さは、3nm以上50nm以下とすればよい。

たスパッタリング法により酸化物半導体膜106を形成する。ここで、スパッタリングガ

スとしては、希ガス(例えばアルゴン)、酸素ガスまたは希ガスと酸素ガスの混合ガスを

用いればよい。

、水、水酸基または水素化物などが除去された高純度ガスを用いることが好ましい。また

、基板100を高温に保持した状態で酸化物半導体膜106を形成すると酸化物半導体膜

106に含まれる不純物濃度を低減することができる。ここで、基板100の温度は、1

00℃以上600℃以下、好ましくは200℃以上400℃以下とすればよい。

もよい。酸化物半導体膜106が結晶構造を有する場合には、c軸方向に配向した結晶性

の(C Axis Aligned Crystalline:CAAC)酸化物半導体

膜とすることが好ましい。酸化物半導体膜106をCAAC酸化物半導体膜とすることで

、トランジスタの信頼性を高めることができる。

の方向から見て三角形状または六角形状の原子配列を有し、c軸においては、金属原子が

層状に配列し、または金属原子と酸素原子が層状に配列し、ab面(あるいは表面または

界面)においては、a軸またはb軸の向きが異なる(c軸を中心に回転した)結晶を含む

酸化物半導体膜をいう。

な方向から見て、三角形もしくは六角形、または正三角形もしくは正六角形の原子配列を

有し、且つc軸方向に垂直な方向から見て金属原子が層状に配列した相、または金属原子

と酸素原子が層状に配列した相を含む酸化物半導体膜をいう。

のでもない。また、CAAC酸化物半導体膜は結晶化した部分(結晶部分)を含むが、一

つの結晶部分と他の結晶部分の境界を明確に判別できなくてもよい。

また、CAAC酸化物半導体膜を構成する個々の結晶部分のc軸は一定の方向(例えば、

CAAC酸化物半導体膜を支持する基板面またはCAAC酸化物半導体膜の表面、若しく

は界面などに垂直な方向)に揃えられていてもよい。または、CAAC酸化物半導体膜を

構成する個々の結晶部分のab面の法線は一定の方向(例えば、基板面、表面、若しくは

界面などに垂直な方向)であってもよい。

導体であってもよいし、絶縁体であってもよい。また、CAAC酸化物半導体膜は、その

組成などに応じて、可視光に対して透明であってもよいし、不透明であってもよい。

はパルスレーザー蒸着法によって形成する。なお、基板100を高温に保持しつつ酸化物

半導体膜の形成を行うことで、非晶質部分よりも結晶部分の占める割合を大きくすること

ができる。このとき、基板100の温度は、例えば、150℃以上450℃以下とすれば

よく、好ましくは200℃以上350℃以下とする。

よって、非晶質部分よりも結晶部分の占める割合を大きくすることができる。この加熱処

理時の基板100の温度は、例えば、200℃以上基板100の歪み点未満とすればよく

、好ましくは250℃以上450℃以下とすればよい。この加熱処理の時間は3分以上と

すればよく、24時間以下とすることが好ましい。この加熱処理の時間を長くすると非晶

質部分よりも結晶部分の占める割合を大きくすることができるが、生産性の低下を招くこ

とになるからである。なお、ここでの加熱処理は、酸化性雰囲気または不活性雰囲気で行

えばよいが、これらに限定されるものではない。また、ここでの加熱処理は減圧下で行わ

れてもよい。

としては、例えば、酸素、オゾンまたは亜酸化窒素などを例示することができる。酸化性

雰囲気からは、酸化物半導体膜に含まれないことが好ましい成分(例えば、水及び水素)

が極力除去されていることが好ましい。例えば、酸素、オゾンまたは亜酸化窒素の純度を

、8N(99.999999%)以上、好ましくは9N(99.9999999%)以上

とすればよい。

化性雰囲気には、10ppm以上の酸化性ガスが含まれているものとする。

ガスなどの反応性ガスが10ppm未満で含まれているものとする。

neal)装置を用いて行えばよい。RTA装置を用いることで、短時間であれば、基板

100の歪み点以上の温度で熱処理を行うこともできる。そのため、非晶質部分よりも結

晶部分の占める割合の大きい酸化物半導体膜を形成することができ、生産性の低下を抑制

することができる。

例えば、抵抗発熱体などからの熱伝導または熱輻射によって、被処理物を加熱する機構が

備えられた装置を用いればよい。本実施の形態における加熱処理に用いられる加熱処理装

置としては、例えば、電気炉を挙げることができる。または、GRTA(Gas Rap

id Thermal Anneal)装置、LRTA(Lamp Rapid The

rmal Anneal)装置などのRTA(Rapid Thermal Annea

l)装置などを用いることもできる。なお、LRTA装置は、ハロゲンランプ、メタルハ

ライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプま

たは高圧水銀ランプなどのランプから発せられる光(電磁波)の輻射により、被処理物を

加熱する装置である。GRTA装置は、高温のガスを熱媒体として用いて被処理物を加熱

する装置である。ここで、高温のガスは、被処理物の加熱温度よりも高いことが好ましい

。

m3以下であるIn−Ga−Zn−O系金属酸化物を用いると、c軸配向した六方晶の結

晶構造を含む金属酸化物膜が形成され、一または複数のGa及びZnを有する層が、二層

のIn−Oの結晶面(インジウムと酸素を含む結晶面)の間に配される。

合の秩序性が高い。すなわち、酸化物半導体膜が非晶質構造の場合には、隣接する金属原

子に配位する酸素原子の数が異なるが、CAAC酸化物半導体膜では金属原子に配位する

酸素原子の数はほぼ一定となる。そのため、微視的なレベルにおいても酸素欠損がほぼ見

られず、水素原子(水素イオンを含む)やアルカリ金属原子などによる電荷の移動や電気

伝導性の不安定さを抑制することができる。

製すると、トランジスタへの光照射またはバイアス−熱ストレス(BT)試験を行った後

に生じる、トランジスタのしきい値電圧の変化を抑制することができ、安定した電気的特

性を有するトランジスタを作製することができる。

))。

ず、酸化物半導体膜106を加工する際にマスクとして機能するものであればよい。

体膜110を形成し、その後第1のマスク108を除去する(図2(A))。

エッチングに用いるエッチングガスとしては、例えば、塩素ガス、または三塩化ホウ素ガ

スと塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウエットエッチン

グを用いてもよいし、酸化物半導体膜106を加工することができる他の手段を用いても

よい。

ク108はレジスト剥離液により除去すればよいが、アッシングのみで除去してもよい。

膜112上に第1の導電膜114を形成し、第1の導電膜114上に第2のマスク116

を形成する(図2(B))。

含み、酸素の一部が加熱により脱離する絶縁性酸化物により形成することが好ましい。す

なわち、第1の下地膜102の材料として例示した前記材料により形成することが好まし

い。ゲート絶縁膜112の島状の酸化物半導体膜110と接する部分を酸化シリコンによ

り形成すると、島状の酸化物半導体膜110に酸素を拡散させることができ、トランジス

タの低抵抗化を防止することができる。

加されたハフニウムシリケート(HfSixOyNz)、窒素が添加されたハフニウムア

ルミネート(HfAlxOyNz)、酸化ハフニウムまたは酸化イットリウムなどのhi

gh−k材料を用いると、ゲートリーク電流を低減することができる。ここで、ゲートリ

ーク電流とは、ゲート電極とソース電極またはドレイン電極の間に流れるリーク電流をい

う。更には、前記high−k材料により形成される層と、酸化シリコン、酸化窒化シリ

コン、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化窒化アルミニウム及び

酸化ガリウムにより形成される層が積層された積層膜であってもよい。ただし、ゲート絶

縁膜112を積層膜とする場合であっても、島状の酸化物半導体膜110に接する部分は

、絶縁性酸化物であることが好ましい。

112の厚さは、1nm以上300nm以下、好ましくは5nm以上50nm以下とすれ

ばよい。ゲート絶縁膜112の厚さを5nm以上とすると、ゲートリーク電流を特に小さ

くすることができる。

性ガスのプラズマに曝して島状の酸化物半導体膜110の表面の酸素欠損を少なくするこ

とが好ましい。

ばよい。ここで、導電性材料としては、アルミニウム、クロム、銅、タンタル、チタン、

モリブデン、タングステン、マンガン、マグネシウム、ベリリウム若しくはジルコニウム

などの金属、または前記金属の一種または複数種を成分として含む合金を挙げることがで

きる。例えば、シリコンを含むアルミニウム膜の単層膜、アルミニウム膜上にチタン膜が

設けられた二層の積層膜、窒化チタン膜上にチタン膜が設けられた二層の積層膜、窒化チ

タン膜上にタングステン膜が設けられた二層の積層膜、窒化タンタル膜上にタングステン

膜が設けられた二層の積層膜、または、アルミニウム膜をチタン膜で挟持した三層の積層

膜などが挙げられる。

される配線を低抵抗にすることができるため、好ましい。ここで、第1の導電膜114が

積層膜である場合には、第1の導電膜114のうち少なくとも一層が銅により形成されて

いればよい。

ウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウ

ム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物または酸化シリ

コンを添加したインジウム錫酸化物などの透光性を有する導電性材料により形成されてい

ていてもよい。

して形成されていてもよい。

タのサイズなどに応じて決めればよい。第1の導電膜114の形成方法としては、例えば

、スパッタリング法またはCVD法などが挙げられる。第1の導電膜114の厚さは、例

えば100nm以上300nm以下とすればよい。

ず、第1の導電膜114を加工する際にマスクとして機能するものであればよい。

形成し、その後第2のマスク116を除去する(図2(C))。

ッチングに用いるエッチングガスとしては、例えば塩素ガス、または三塩化ホウ素ガスと

塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウエットエッチングを

用いてもよいし、第1の導電膜114を加工することができる他の手段を用いてもよい。

ク116はレジスト剥離液により除去すればよいが、アッシングのみで除去してもよい。

クとして、島状の酸化物半導体膜110にドーパントを添加してソース領域及びドレイン

領域を形成することが好ましい。

法により行えばよい。または、ドーパントを含むガス雰囲気中でプラズマ処理を行うこと

でドーパントの添加を行ってもよい。また、添加するドーパントとしては、水素、希ガス

、窒素、リンまたはヒ素などを用いればよい。

し、第1の保護膜120上に第2の保護膜122を形成する(図3(A))。

同様の方法により形成すればよく、絶縁性酸化膜であることが好ましい。

保護膜120は設けられていなくてもよい。

の有機樹脂材料により形成すればよく、表面が概略平坦になる方法(例えば、スピンコー

ト法)などにより形成される膜であることが好ましい。ここで「概略平坦」とは、第2の

保護膜122上に形成される膜の形成不良を防止することができる程度のものであればよ

く、高い平坦性が要求されるわけではない。

2は設けられていなくてもよい。

膜112を加工することで開口部124a及び開口部124bを形成し、開口部124a

及び開口部124bを介して島状の酸化物半導体膜110に接続されるように第2の導電

膜126を形成し、第2の導電膜126上の所定の位置に第3のマスク128を形成する

(図3(B))。

ば、所定の位置にマスクを形成してドライエッチングを行ってもよいし、第2の保護膜1

22が感光性材料により形成されている場合には、第2の保護膜122の所定の位置を露

光して現像し、第2の保護膜122をマスクとして用いてドライエッチングを行ってもよ

い。ドライエッチングに用いるエッチングガスとしては、例えば塩素ガス、または三塩化

ホウ素ガスと塩素ガスの混合ガスを用いればよい。ただし、これに限定されず、ウエット

エッチングを用いてもよい。

ればよいし、第1の導電膜114と同程度の厚さとすればよい。

ず、第2の導電膜126を加工する際にマスクとして機能するものであればよい。

及びドレイン電極130bを形成し、その後第3のマスク128を除去する(図3(C)

)。

酸化物半導体膜に接して設けられる下地膜の水及び水素の含有量を少なくし、酸素の含有

量を多くすることで、酸化物半導体膜における水及び水素の含有量を少なくし、酸化物半

導体膜に酸素欠損を低減するための酸素を供給することができるため、信頼性の高い半導

体装置を得ることができる。

実施の形態1で説明した半導体装置(トランジスタ)は、表示装置の画素トランジスタ

として用いることができる。

適用して作製したトランジスタの少なくともソース電極130a及びドレイン電極130

bの一方と接続されるように、画素電極として機能する島状の透明導電膜を位置選択的に

形成すればよい。

続されるように、インクジェット法により島状の透明導電膜を位置選択的に形成してもよ

い。

性組成物を用いて形成することができる。導電性組成物を用いて形成された透明導電膜で

は、シート抵抗が10000Ω/□以下であり、且つ波長550nmにおける透光率が7

0%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が

0.1Ω・cm以下であることが好ましい。

る。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリ

チオフェン若しくはその誘導体、または、アニリン、ピロール及びチオフェンの2種以上

の共重合体若しくはその誘導体などがあげられる。

物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物

、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物または酸化シリコンを添

加したインジウム錫酸化物などにより形成されていればよい。

実施の形態1及び実施の形態2の半導体装置を応用した本発明の一態様である半導体装

置としては、電子ペーパーが挙げられる。電子ペーパーは、情報を表示するものであれば

あらゆる分野の電子機器に用いることが可能である。例えば、電子ペーパーを用いて、電

子書籍(電子ブック)、ポスター、デジタルサイネージ、PID(Public Inf

ormation Display)、電車などの乗り物の車内広告、クレジットカード

などの各種カードにおける表示部などに適用することができる。電子機器の一例を図4に

示す。

体303の2つの筐体で構成されている。筐体301及び筐体303は、軸部311によ

り一体とされており、該軸部311を軸として開閉動作を行うことができる。このような

構成により、紙の書籍と同様に取り扱うことが可能となる。

示部307及び光電変換装置308が組み込まれている。表示部305及び表示部307

は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。

異なる画面を表示する構成とすることで、例えば右側の表示部(図4では表示部305)

に文章を表示し、左側の表示部(図4では表示部307)に画像を表示することができる

。

1において、電源321、操作キー323、スピーカ325などを備えている。操作キー

323により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポイ

ンティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接

続用端子(イヤホン端子、USB端子、またはACアダプタ及びUSBケーブルなどの各

種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さ

らに、電子書籍300は、電子辞書としての機能を持たせた構成としてもよい。

電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすること

も可能である。

実施の形態1及び実施の形態2の半導体装置を応用した本発明の一態様である半導体装

置としては、電子ペーパー以外にもさまざまな電子機器(遊技機も含む)が挙げられる。

電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機とも

いう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ、デジタ

ルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、

携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

体401に表示部403が組み込まれている。表示部403により、映像を表示すること

が可能である。また、ここでは、スタンド405により筐体401を支持した構成を示し

ている。

ン操作機410により行うことができる。リモコン操作機410が備える操作キー409

により、チャンネルや音量の操作を行うことができ、表示部403に表示される映像を操

作することができる。また、リモコン操作機410に、当該リモコン操作機410から出

力する情報を表示する表示部407を設ける構成としてもよい。

より一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線に

よる通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向

(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

フレーム420は、筐体421に表示部423が組み込まれている。表示部423は、各

種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを

表示させることで、通常の写真立てと同様に機能させることができる。

Bケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構

成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に

備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒

体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像デー

タを取り込み、取り込んだ画像データを表示部423に表示させることができる。

。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

ユニットを閉状態として表示部443を有する上部筐体441と、キーボード444を有

する下部筐体442とを重ねた状態とすることができ、持ち運ぶことが便利であるととも

に、使用者がキーボード入力する場合には、ヒンジユニットを開状態として、表示部44

3を見て入力操作を行うことができる。

ス446を有する。また、表示部443をタッチ入力パネルとすれば、表示部の一部に触

れることで入力操作を行うこともできる。また、下部筐体442はCPUやハードディス

クなどの演算機能部を有している。また、下部筐体442は他の機器、例えばUSBの通

信規格に準拠した通信ケーブルが差し込まれる外部接続ポート445を有している。

を有しており、広い表示画面を実現することができる。また、収納可能な表示部447の

画面の向きを使用者は調節できる。また、収納可能な表示部447をタッチ入力パネルと

すれば、収納可能な表示部の一部に触れることで入力操作を行うこともできる。

無機発光素子などの発光表示パネルなどの映像表示装置を用いる。

受信して映像を表示部に表示することができる。また、上部筐体441と下部筐体442

とを接続するヒンジユニットを閉状態としたまま、表示部447をスライドさせて画面全

面を露出させ、画面角度を調節して使用者がテレビ放送を見ることもできる。この場合に

は、ヒンジユニットを閉状態として表示部443を表示させず、さらにテレビ放送を表示

するだけの回路の起動のみを行うため、最小限の消費電力とすることができ、バッテリー

容量の限られている携帯型のコンピュータにおいて有用である。

102 第1の下地膜

104 第2の下地膜

106 酸化物半導体膜

108 第1のマスク

110 島状の酸化物半導体膜

112 ゲート絶縁膜

114 第1の導電膜

116 第2のマスク

118 ゲート電極

120 第1の保護膜

122 第2の保護膜

124a 開口部

124b 開口部

126 第2の導電膜

128 第3のマスク

130a ソース電極

130b ドレイン電極

200 曲線

202 閉領域

204 第1の接点

206 第2の接点

208 直線

300 電子書籍

301 筐体

303 筐体

305 表示部

306 光電変換装置

307 表示部

308 光電変換装置

311 軸部

321 電源

323 操作キー

325 スピーカ

400 テレビジョン装置

401 筐体

403 表示部

405 スタンド

407 表示部

409 操作キー

410 リモコン操作機

420 デジタルフォトフレーム

421 筐体

423 表示部

441 上部筐体

442 下部筐体

443 表示部

444 キーボード

445 外部接続ポート

446 ポインティングデバイス

447 表示部

Claims (3)

- 酸素を含む絶縁性酸化物でなる第1の絶縁膜を形成し、

前記第1の絶縁膜上に第2の絶縁膜を形成し、

第1の加熱処理により、前記第1の絶縁膜及び前記第2の絶縁膜から水及び水素を脱離させ、

前記第1の加熱処理後、前記第2の絶縁膜上に酸化物半導体膜を形成し、

第2の加熱処理により、前記第1の絶縁膜から前記第2の絶縁膜を介して前記酸化物半導体膜に酸素を供給し、

前記第2の絶縁膜の酸素の拡散係数は、前記第1の絶縁膜の酸素の拡散係数よりも小さいことを特徴とする半導体装置の作製方法。 - 酸素を含む絶縁性酸化物でなる第1の絶縁膜を形成し、

前記第1の絶縁膜のTDS分析による酸素の脱離量は、1.0×1018atoms/cm3以上であり、

前記第1の絶縁膜上に第2の絶縁膜を形成し、

第1の加熱処理により、前記第1の絶縁膜及び前記第2の絶縁膜から水及び水素を脱離させ、

前記第1の加熱処理後、前記第2の絶縁膜上に酸化物半導体膜を形成し、

第2の加熱処理により、前記第1の絶縁膜から前記第2の絶縁膜を介して前記酸化物半導体膜に酸素を供給し、

前記第2の絶縁膜の酸素の拡散係数は、前記第1の絶縁膜の酸素の拡散係数よりも小さいことを特徴とする半導体装置の作製方法。 - 請求項1または請求項2において、

前記酸化物半導体膜は、インジウムと、ガリウムと、亜鉛とを有することを特徴とする半導体装置の作製方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011074049 | 2011-03-30 | ||

| JP2011074049 | 2011-03-30 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012064035A Division JP5926992B2 (ja) | 2011-03-30 | 2012-03-21 | 半導体装置の作製方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017074458A Division JP6357261B2 (ja) | 2011-03-30 | 2017-04-04 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016154261A JP2016154261A (ja) | 2016-08-25 |

| JP6125072B2 true JP6125072B2 (ja) | 2017-05-10 |

Family

ID=46927774

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012064035A Active JP5926992B2 (ja) | 2011-03-30 | 2012-03-21 | 半導体装置の作製方法 |

| JP2016087133A Active JP6125072B2 (ja) | 2011-03-30 | 2016-04-25 | 半導体装置の作製方法 |

| JP2017074458A Expired - Fee Related JP6357261B2 (ja) | 2011-03-30 | 2017-04-04 | 半導体装置の作製方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012064035A Active JP5926992B2 (ja) | 2011-03-30 | 2012-03-21 | 半導体装置の作製方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017074458A Expired - Fee Related JP6357261B2 (ja) | 2011-03-30 | 2017-04-04 | 半導体装置の作製方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8927329B2 (ja) |

| JP (3) | JP5926992B2 (ja) |

| KR (2) | KR101979568B1 (ja) |

| TW (3) | TWI595559B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9012905B2 (en) * | 2011-04-08 | 2015-04-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including transistor comprising oxide semiconductor and method for manufacturing the same |

| JP5871263B2 (ja) * | 2011-06-14 | 2016-03-01 | 富士フイルム株式会社 | 非晶質酸化物薄膜の製造方法 |

| US9660092B2 (en) | 2011-08-31 | 2017-05-23 | Semiconductor Energy Laboratory Co., Ltd. | Oxide semiconductor thin film transistor including oxygen release layer |

| US8999773B2 (en) | 2012-04-05 | 2015-04-07 | Semiconductor Energy Laboratory Co., Ltd. | Processing method of stacked-layer film and manufacturing method of semiconductor device |

| TWI644433B (zh) * | 2013-03-13 | 2018-12-11 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| JP6171435B2 (ja) * | 2013-03-18 | 2017-08-02 | 富士通株式会社 | 半導体装置及びその製造方法、電源装置、高周波増幅器 |

| WO2015049818A1 (ja) * | 2013-10-03 | 2015-04-09 | パナソニック株式会社 | 薄膜トランジスタ基板の製造方法 |

| CN103500710B (zh) * | 2013-10-11 | 2015-11-25 | 京东方科技集团股份有限公司 | 一种薄膜晶体管制作方法、薄膜晶体管及显示设备 |

| KR102270823B1 (ko) * | 2013-10-22 | 2021-06-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치와 그 제작 방법 |

| KR102164941B1 (ko) | 2014-01-13 | 2020-10-14 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판, 이를 포함하는 표시 장치, 및 박막 트랜지스터 기판의 제조 방법 |

| US20160163869A1 (en) * | 2014-12-08 | 2016-06-09 | Semiconductor Energy Laboratory Co., Ltd. | Transistor |

| US10205008B2 (en) * | 2016-08-03 | 2019-02-12 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| JP7086582B2 (ja) * | 2017-12-11 | 2022-06-20 | 株式会社ジャパンディスプレイ | 表示装置 |

| US11354617B1 (en) | 2018-03-12 | 2022-06-07 | Amazon Technologies, Inc. | Managing shipments based on data from a sensor-based automatic replenishment device |

| CN108766972B (zh) | 2018-05-11 | 2021-10-22 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、显示基板 |

| JP7253853B1 (ja) | 2022-05-13 | 2023-04-07 | 株式会社オーツボ | 海苔剥ぎ装置 |

Family Cites Families (134)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JP3298974B2 (ja) | 1993-03-23 | 2002-07-08 | 電子科学株式会社 | 昇温脱離ガス分析装置 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| US6656779B1 (en) | 1998-10-06 | 2003-12-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor apparatus having semiconductor circuits made of semiconductor devices, and method of manufacture thereof |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| KR100356473B1 (ko) * | 1999-12-29 | 2002-10-18 | 주식회사 하이닉스반도체 | 반도체 소자의 알루미늄 옥사이드 박막 형성 방법 |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| US7061014B2 (en) | 2001-11-05 | 2006-06-13 | Japan Science And Technology Agency | Natural-superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| CN1445821A (zh) | 2002-03-15 | 2003-10-01 | 三洋电机株式会社 | ZnO膜和ZnO半导体层的形成方法、半导体元件及其制造方法 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| CN102354658B (zh) | 2004-03-12 | 2015-04-01 | 独立行政法人科学技术振兴机构 | 薄膜晶体管的制造方法 |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| TWI382455B (zh) * | 2004-11-04 | 2013-01-11 | Semiconductor Energy Lab | 半導體裝置和其製造方法 |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| RU2358355C2 (ru) | 2004-11-10 | 2009-06-10 | Кэнон Кабусики Кайся | Полевой транзистор |

| EP1812969B1 (en) | 2004-11-10 | 2015-05-06 | Canon Kabushiki Kaisha | Field effect transistor comprising an amorphous oxide |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI505473B (zh) | 2005-01-28 | 2015-10-21 | Semiconductor Energy Lab | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| TWI569441B (zh) | 2005-01-28 | 2017-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| US7544967B2 (en) | 2005-03-28 | 2009-06-09 | Massachusetts Institute Of Technology | Low voltage flexible organic/transparent transistor for selective gas sensing, photodetecting and CMOS device applications |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP5216201B2 (ja) * | 2005-09-27 | 2013-06-19 | 株式会社半導体エネルギー研究所 | 半導体装置、半導体装置の作製方法、液晶表示装置、rfidタグ、発光装置及び電子機器 |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101117948B1 (ko) | 2005-11-15 | 2012-02-15 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 액정 디스플레이 장치 제조 방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101146574B1 (ko) | 2006-12-05 | 2012-05-16 | 캐논 가부시끼가이샤 | 산화물 반도체를 이용한 박막 트랜지스터의 제조방법 및 표시장치 |

| WO2008069255A1 (en) | 2006-12-05 | 2008-06-12 | Canon Kabushiki Kaisha | Method for manufacturing thin film transistor using oxide semiconductor and display apparatus |

| JP5305630B2 (ja) | 2006-12-05 | 2013-10-02 | キヤノン株式会社 | ボトムゲート型薄膜トランジスタの製造方法及び表示装置の製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| JP5320746B2 (ja) | 2007-03-28 | 2013-10-23 | 凸版印刷株式会社 | 薄膜トランジスタ |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| KR101334182B1 (ko) * | 2007-05-28 | 2013-11-28 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터의 제조방법 |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5406449B2 (ja) | 2007-05-30 | 2014-02-05 | キヤノン株式会社 | 酸化物半導体を用いた薄膜トランジスタの製造方法および表示装置 |

| JP5193542B2 (ja) * | 2007-09-20 | 2013-05-08 | パナソニック株式会社 | 半導体装置の製造方法 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP5704790B2 (ja) * | 2008-05-07 | 2015-04-22 | キヤノン株式会社 | 薄膜トランジスタ、および、表示装置 |

| JP5250321B2 (ja) * | 2008-07-04 | 2013-07-31 | 昭和電工株式会社 | 炭化珪素単結晶成長用種結晶の製造方法並びに炭化珪素単結晶の製造方法 |

| JP2010056541A (ja) | 2008-07-31 | 2010-03-11 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| TWI413260B (zh) | 2008-07-31 | 2013-10-21 | Semiconductor Energy Lab | 半導體裝置及其製造方法 |

| TWI637444B (zh) | 2008-08-08 | 2018-10-01 | 半導體能源研究所股份有限公司 | 半導體裝置的製造方法 |

| JP2010045263A (ja) * | 2008-08-15 | 2010-02-25 | Idemitsu Kosan Co Ltd | 酸化物半導体、スパッタリングターゲット、及び薄膜トランジスタ |

| JP5602390B2 (ja) * | 2008-08-19 | 2014-10-08 | 富士フイルム株式会社 | 薄膜トランジスタ、アクティブマトリクス基板、及び撮像装置 |

| JP5627071B2 (ja) | 2008-09-01 | 2014-11-19 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2010029865A1 (en) * | 2008-09-12 | 2010-03-18 | Semiconductor Energy Laboratory Co., Ltd. | Display device |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5552753B2 (ja) | 2008-10-08 | 2014-07-16 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| CN101911269B (zh) * | 2008-11-18 | 2013-05-01 | 松下电器产业株式会社 | 柔性半导体装置及其制造方法 |

| JP2010205987A (ja) | 2009-03-04 | 2010-09-16 | Sony Corp | 薄膜トランジスタおよびその製造方法並びに表示装置 |

| JP5760298B2 (ja) * | 2009-05-21 | 2015-08-05 | ソニー株式会社 | 薄膜トランジスタ、表示装置、および電子機器 |

| KR101213708B1 (ko) * | 2009-06-03 | 2012-12-18 | 엘지디스플레이 주식회사 | 어레이 기판 및 이의 제조방법 |

| JP5499529B2 (ja) * | 2009-06-25 | 2014-05-21 | 大日本印刷株式会社 | 薄膜トランジスタ搭載基板、その製造方法及び画像表示装置 |

| KR101968855B1 (ko) | 2009-06-30 | 2019-04-12 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 제조 방법 |

| WO2011002046A1 (en) | 2009-06-30 | 2011-01-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| KR101476817B1 (ko) | 2009-07-03 | 2014-12-26 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 트랜지스터를 갖는 표시 장치 및 그 제작 방법 |

| JP5663214B2 (ja) | 2009-07-03 | 2015-02-04 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| WO2011004723A1 (en) | 2009-07-10 | 2011-01-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method the same |

-

2012

- 2012-03-20 US US13/424,681 patent/US8927329B2/en active Active

- 2012-03-21 JP JP2012064035A patent/JP5926992B2/ja active Active

- 2012-03-26 TW TW105114131A patent/TWI595559B/zh not_active IP Right Cessation

- 2012-03-26 TW TW101110391A patent/TWI543258B/zh active

- 2012-03-26 TW TW106117663A patent/TWI626691B/zh not_active IP Right Cessation

- 2012-03-27 KR KR1020120030996A patent/KR101979568B1/ko active IP Right Grant

-

2014

- 2014-12-26 US US14/583,416 patent/US10008588B2/en not_active Expired - Fee Related

-

2016

- 2016-04-25 JP JP2016087133A patent/JP6125072B2/ja active Active

-

2017

- 2017-04-04 JP JP2017074458A patent/JP6357261B2/ja not_active Expired - Fee Related

-

2019

- 2019-05-10 KR KR1020190054929A patent/KR102113027B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| TW201732933A (zh) | 2017-09-16 |

| US20150162421A1 (en) | 2015-06-11 |

| TWI595559B (zh) | 2017-08-11 |

| US10008588B2 (en) | 2018-06-26 |

| TWI626691B (zh) | 2018-06-11 |

| JP2017120935A (ja) | 2017-07-06 |

| KR102113027B1 (ko) | 2020-05-20 |

| JP6357261B2 (ja) | 2018-07-11 |

| US20120252173A1 (en) | 2012-10-04 |

| TWI543258B (zh) | 2016-07-21 |

| KR101979568B1 (ko) | 2019-05-17 |

| TW201631662A (zh) | 2016-09-01 |

| JP5926992B2 (ja) | 2016-05-25 |

| KR20120112098A (ko) | 2012-10-11 |

| US8927329B2 (en) | 2015-01-06 |

| KR20190053165A (ko) | 2019-05-17 |

| JP2016154261A (ja) | 2016-08-25 |

| JP2012216796A (ja) | 2012-11-08 |

| TW201306129A (zh) | 2013-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6357261B2 (ja) | 半導体装置の作製方法 | |

| KR102660906B1 (ko) | 반도체 장치 | |

| JP6630779B2 (ja) | 半導体装置の作製方法 | |

| JP2012009845A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170404 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6125072 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |