JP6114577B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6114577B2 JP6114577B2 JP2013044393A JP2013044393A JP6114577B2 JP 6114577 B2 JP6114577 B2 JP 6114577B2 JP 2013044393 A JP2013044393 A JP 2013044393A JP 2013044393 A JP2013044393 A JP 2013044393A JP 6114577 B2 JP6114577 B2 JP 6114577B2

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- layer

- wiring layer

- wirings

- lands

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49822—Multilayer substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/025—Impedance arrangements, e.g. impedance matching, reduction of parasitic impedance

- H05K1/0251—Impedance arrangements, e.g. impedance matching, reduction of parasitic impedance related to vias or transitions between vias and transmission lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

- H05K1/116—Lands, clearance holes or other lay-out details concerning the surrounding of a via

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05147—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/05155—Nickel [Ni] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/05001—Internal layers

- H01L2224/05099—Material

- H01L2224/051—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/05163—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than 1550°C

- H01L2224/05166—Titanium [Ti] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16227—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/2919—Material with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29199—Material of the matrix

- H01L2224/2929—Material of the matrix with a principal constituent of the material being a polymer, e.g. polyester, phenolic based polymer, epoxy

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/29198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/29298—Fillers

- H01L2224/29299—Base material

- H01L2224/29386—Base material with a principal constituent of the material being a non metallic, non metalloid inorganic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

- H01L2224/331—Disposition

- H01L2224/3318—Disposition being disposed on at least two different sides of the body, e.g. dual array

- H01L2224/33181—On opposite sides of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/36—Selection of materials, or shaping, to facilitate cooling or heating, e.g. heatsinks

- H01L23/367—Cooling facilitated by shape of device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L24/33—Structure, shape, material or disposition of the layer connectors after the connecting process of a plurality of layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

- H01L2924/3511—Warping

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/0245—Lay-out of balanced signal pairs, e.g. differential lines or twisted lines

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0213—Electrical arrangements not otherwise provided for

- H05K1/0237—High frequency adaptations

- H05K1/025—Impedance arrangements, e.g. impedance matching, reduction of parasitic impedance

- H05K1/0253—Impedance adaptations of transmission lines by special lay-out of power planes, e.g. providing openings

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/0929—Conductive planes

- H05K2201/09309—Core having two or more power planes; Capacitive laminate of two power planes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09718—Clearance holes

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electromagnetism (AREA)

Description

本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクション等に分けて記載するが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、記載の前後を問わず、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しの説明を省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

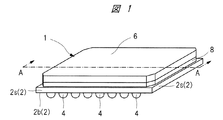

図1は本実施の形態の半導体装置の斜視図、図2は、図1に示す半導体装置の下面図である。また、図3は、図1に示す放熱板を取り除いた状態で配線基板上の半導体装置の内部構造を示す透視平面図である。また、図4は図1のA−A線に沿った断面図である。なお、図1〜図4では、見易さのため、端子数を少なくして示している。また、図4では、見易さのため、図2に示す例よりも半田ボール4の数を少なくして示している。端子(ボンディングパッド2PD、ランド2LD、半田ボール4)の数は、図1〜図4に示す態様には限定されない。例えば、ボンディングパッド2PD、ランド2LD、半田ボール4などの端子数が、それぞれ100個〜10,000個程度の半導体装置に適用することができる。

まず、本実施の形態の半導体装置1の概要構成について、図1〜図4を用いて説明する。本実施の形態の半導体装置1は、配線基板2、および配線基板2上に搭載された半導体チップ3(図4参照)を備えている。

次に、図1〜図4に示す配線基板2の詳細について説明する。図5は、図4に示す配線基板のチップ搭載面側(第1層目)の配線層のレイアウトを示す平面図である。また、図6は、図5に示す配線基板の一部を拡大して示す拡大平面図である。また、図7は図5に示す配線基板の他の一部を拡大して示す拡大平面図である。また、図8は図7のA−A線に沿った拡大断面図である。また、図9は、ストリップラインの配線構造例を示す拡大断面図である。また図10は、マイクロストリップラインの配線構造例を示す拡大断面図である。また、図11は、図5に示す配線層の一つ下層(第2層目)の配線層のレイアウトを示す平面図である。また、図12は、図11に示す配線層の一部を拡大して示す拡大平面図である。また、図13は、図11に示す配線層の他の一部を拡大して示す拡大平面図である。また、図14は、図11に示す配線層の一つ下層(第3層目)の配線層のレイアウトを示す平面図である。また、図15は、図14に示す配線層の一部を拡大して示す拡大平面図である。また、図16は図15のA−A線に沿った拡大断面図である。また、図17は図14に示す配線層(第4層目)の一つ下層の配線層のレイアウトを示す平面図である。また、図18は図17に示す配線層の一つ下層(第5層目)の配線層のレイアウトを示す平面図である。また、図19は図4に示す配線基板の実装面側(第6層目)の配線層のレイアウトを示す平面図である。

図5に示すように、配線基板2のチップ搭載面である上面2aを持つ配線層(第1配線層)WL1は、複数のボンディングパッド2PDを備えている。複数のボンディングパッド2PDには、上記第1の伝送速度で第1信号電流が流れる複数のボンディングパッド(第2ボンディングパッド)2PDaが含まれる。また、複数のボンディングパッド2PDには、上記第1の伝送速度よりも早い、上記第2の伝送速度で第2信号電流が流れる複数のボンディングパッド(第1ボンディングパッド)2PDbが含まれる。本実施の形態では、複数のボンディングパッド2PDbには、例えば、10Gbps〜25Gbps程度の伝送速度で、差動信号が伝送される。また、図示は省略するが、複数のボンディングパッド2PDには、図4に示す半導体チップ3に形成された回路に、電源電位または基準電位を供給する複数のボンディングパッド(電源用ボンディングパッド)2PDが含まれる。また、複数のボンディングパッド2PDには、信号伝送経路のリファレンス用の基準電位が供給されるボンディングパッド2PDが含まれる。

次に、図11に示す第2層目の配線層(第2配線層)WL2は、複数のビア配線2V1と電気的に接続されている複数の配線(第2層配線)2d2、および複数の配線2d2と電気的に接続されている複数のビア配線2V2を備えている。複数のビア配線2V2には、図12に示すように、配線層WL1(図6参照)に形成された複数のビア配線2V1aと電気的に接続されている複数のビア配線2V2aが含まれる。複数のビア配線2V2aは、上記した低速伝送経路を構成する。また、複数のビア配線2V2には、図13に示すように、複数の配線2d2(配線2d2b)を介して複数のビア配線2V1bとそれぞれ電気的に接続される、複数のビア配線2V2bが含まれる。複数の配線2d2bおよび複数のビア配線2V2bは、上記した高速伝送経路を構成する。

次に、図14に示す第3層目の配線層(第3配線層)WL3は、複数のビア配線2V2と電気的に接続されている複数のスルーホールランド(第1スルーホールランド)2TL1を備えている。複数のスルーホールランド2TL1には、図14に示すように、配線層WL2(図12参照)に形成された複数のビア配線2V2aと電気的に接続されている複数のスルーホールランド2TL1aが含まれる。複数のスルーホールランド2TL1aは、上記した低速伝送経路を構成する。また、複数のスルーホールランド2TL1には、図15に示すように、配線層WL2(図13参照)に形成された複数のビア配線2V2bと電気的に接続されている複数のスルーホールランド2TL1bが含まれる。複数のスルーホールランド2TL1bは、上記した高速伝送経路を構成する。図15および図16に示すように、複数のスルーホールランド2TL1bには、高速伝送経路を構成するスルーホール配線2TWbが、それぞれ接続されている。

図16に示すように、配線層WL3は、絶縁層2CRの上面2Ca上に形成されている。絶縁層2CRは、配線層WL3が形成されている上面(第1面)2Ca、上面2Caの反対側に位置する下面(第2面)2Cbを有している。また、絶縁層2CRは、上面2Caまたは下面2Cbのうち、一方から他方に向かって貫通するように形成されている複数のスルーホール2TH(図15参照)を有している。また、絶縁層2CRは、スルーホール2THの内壁のそれぞれを覆うように形成されるスルーホール配線2TWを有している。スルーホール配線2TWは、絶縁層2CRの上面2Caに形成されたスルーホールランド2TL1、および絶縁層2CRの下面2Cbに形成されたスルーホールランド2TL2と一体に形成されている。

次に、絶縁層2CRの下面2Cbには、第4層目の配線層(第4配線層)WL4が形成されている。図17に示すように、配線層WL4は、複数のスルーホールランド(第2スルーホールランド)2TL2を備えている。複数のスルーホールランド2TL2のそれぞれは、図16に例示するスルーホール2THと一体に形成されている。複数のスルーホールランド2TL2には、図14に示す複数のスルーホールランド2TL1aと電気的に接続されている複数のスルーホールランド2TL2aが含まれる。複数のスルーホールランド2TL2aは、上記した低速伝送経路を構成する。また、複数のスルーホールランド2TL2には、図14に示す複数のスルーホールランド2TL1bと電気的に接続されている複数のスルーホールランド2TL2bが含まれる。複数のスルーホールランド2TL2bは、上記した高速伝送経路を構成する。

次に、配線層WL4のさらに下層には、図18に示す第5層目の配線層(第5配線層)WL5が形成されている。第5層目の配線層WL5は、図17に示す複数のスルーホールランド2TL2と電気的に接続されている複数のビア配線(第3ビア配線)2V3、および複数のビア配線2V3と電気的に接続されている複数の配線(第5層配線)2d3を備えている。複数のビア配線2V3には、図17に示す配線層WL4に形成された複数のスルーホールランド2TL2aと電気的に接続されている複数のビア配線2V3aが含まれる。また、複数の配線2d3には、複数のビア配線2V3aと電気的に接続されている複数の配線2d3aが含まれる。複数の配線2d3aおよび複数のビア配線2V3aは、上記した低速伝送経路を構成する。

次に、配線層WL5のさらに下層には、図19に示す第6層目の配線層(第6配線層)WL6が形成されている。第6層目の配線層WL6は、図18に示す複数のビア配線2V3と電気的に接続されている複数のビア配線(第4ビア配線)2V4、および複数のビア配線2V4と電気的に接続されている複数のランド2LDを備えている。複数のビア配線2V4には、図18に示す配線層WL5に形成された複数のビア配線2V3aと電気的に接続されている複数のビア配線2V4aが含まれる。複数のビア配線2V4aおよびビア配線2V4aと電気的に接続される複数のランド2LDaは、上記した低速伝送経路を構成する。

次に、高速伝送経路のインピーダンス整合について、更に詳しく説明する。図21は、図16に示す高速伝送経路の接続構造を模式的に示す説明図である。また、図22は、図21に対する検討例を示す説明図である。また、図23は、図15に示す拡大平面における第1層目の配線層の導体のパターニングを示す拡大平面図である。また、図24は、図15に示す拡大平面における第2層目の配線層の導体のパターニングを示す拡大平面図である。また、図25は図21に対する他の検討例を示す説明図である。

上記では、スルーホールランド2TL1bの周辺に形成される寄生容量について説明した。しかし、高速伝送経路におけるインピーダンス整合を容易に行う観点からは、絶縁層2CRの実装面側(図16に示す下面2Cb側)に形成される寄生容量も低減することが好ましい。以下では、絶縁層2CRの実装面側(図16に示す下面2Cb側)に形成される寄生容量も低減する構成について詳しく説明する。

次に、図21に示す配線基板2の構成を適用することによるノイズ耐性の改善効果について本願発明者が検討した結果について説明する。図29は、図21に示す配線基板と図22に示す配線基板について、電気的特性の評価を行った結果を示す説明図である。図29に示す評価では、図21に示す配線基板2の構成、および図22に示す配線基板2Aの構成について、それぞれ差動インピーダンスZdiff[Ω]、差動反射特性Sdd11[dB]、および差動伝送特性Sdd21[dB]について評価を行った。

上記では図16では、スルーホールランド2TL1、2TL2がランド2LD上に配置されている場合の実施態様について説明した。本実施の形態に対する変形例としては、全ての高速伝送経路を、例えば図11に示す配線層WL2においてランド2LD(図19参照)上まで引き回すこともできる。この場合、図18に示す配線層WL5は省力することができる。

次に、図1〜図40を用いて説明した半導体装置1の製造方法(組立工程)について、図41に示すフロー図を用いて説明する。図41は、図1〜図40を用いて説明した半導体装置の組立工程のフローを示す説明図である。なお、以下の製造方法の説明においては、予め製品サイズに形成された配線基板2を準備して、一つの半導体装置1を製造する方法について説明する。しかし、変形例としては、複数の製品形成領域に区画された、所謂、多数個取り基板を準備して、複数の製品形成領域のそれぞれについて組立を行ったあと、製品形成領域毎に分割して複数の半導体装置を取得する、多数個取り方式にも適用できる。このため、図41では、多数個取り方式の時に適用する個片化工程について、括弧書きで記載している。

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

2、2A、2B 配線基板

2a 上面(面、主面、第1面、チップ搭載面)

2b 下面(面、主面、第2面、実装面)

2Ca 上面(第1面)

2Cb 下面(第2面)

2CR 絶縁層(コア材、コア絶縁層)

2d 配線

2d1、2d1a 配線(第1層配線)

2d2、2d2b 配線(第2層配線)

2d3、2d3a、2d3b 配線(第5層配線)

2e 絶縁層

2e1 絶縁層(第1絶縁層、ソルダレジスト膜)

2e2 絶縁層(第2絶縁層)

2e3 絶縁層(第3絶縁層)

2e4 絶縁層(第4絶縁層)

2e5 絶縁層(第5絶縁層)

2e6 絶縁層(第6絶縁層、ソルダレジスト膜)

2ek1、2ek2 開口部(ソルダレジスト開口部)

2FL 導体パターン

2K1、2K1a、2K1b 開口部

2K1c 開口部(第1開口部)

2K2、2K2a 開口部

2K2b 開口部(第2開口部)

2K3、2K4、2K5 開口部

2K4A 開口部(第3開口部)

2K4B 開口部(第5開口部)

2K5A 開口部(第4開口部)

2K6B 開口部(第6開口部)

2LD、2LDa、2LDb ランド

2Lg 基準電位用ランド

2Lv 電源電位用ランド

2Li 入力用ランド

2Lo 出力用ランド

2PD ボンディングパッド(ボンディングリード、半導体チップ接続用端子)

2PDa ボンディングパッド(第2ボンディングパッド)

2PDb ボンディングパッド(第1ボンディングパッド)

2Pg 基準電位用ボンディングパッド

2Pr ボンディングパッド

2Pv 電源電位用ボンディングパッド

2Pi 入力用ボンディングパッド

2Po 出力用ボンディングパッド

2PL 導体プレーン

2PL1 導体プレーン(第1導体プレーン)

2PL2 導体プレーン(第2導体プレーン)

2PL3 導体プレーン(第3導体プレーン)

2PL4 導体プレーン(第4導体プレーン)

2PL5 導体プレーン(第5導体プレーン)

2PL6 導体プレーン(第6導体プレーン)

2PLg 基準電位用導体プレーン

2PLv 電源電位用導体プレーン

2s 側面

2s1、2s2、2s3、2s4 辺

2TH スルーホール

2TL1 スルーホールランド(第1スルーホールランド)

2TL1a、2TL1b スルーホールランド

2TL2 スルーホールランド(第2スルーホールランド)

2TL2a、2TL2b スルーホールランド

2TW、2TWb、2TWb1、2TWb2、2TWr、2TWr1、2TWr2 スルーホール配線

2V1、2V1a、2V1b ビア配線(第1ビア配線)

2V2、2V2a、2V2b ビア配線(第2ビア配線)

2V2r、2V4r ビア配線

2V3、2V3a、2V3b ビア配線(第3ビア配線)

2V4、2V4a、2V4b ビア配線(第4ビア配線)

3 半導体チップ

3a 表面(主面、上面)

3b 裏面(主面、下面)

3BP 突起電極

3PD パッド(ボンディングパッド)

3s 側面

4、4b1、4b2、4r1、4r2 半田ボール(半田材、外部端子、電極、外部電極)

5 アンダフィル樹脂(絶縁性樹脂)

6 放熱板(ヒートスプレッダ)

7 接着材(放熱樹脂)

8 支持枠(スティフナリング)

10 実装基板

Cp、Ct 寄生容量

WL1 配線層(第1配線層)

WL2 配線層(第2配線層)

WL3 配線層(第3配線層)

WL4 配線層(第4配線層)

WL5 配線層(第5配線層)

WL6 配線層(第6配線層)

Sdd11 差動反射特性

Sdd21 差動伝送特性

Zdiff 差動インピーダンス

Claims (18)

- 複数の電極パッドが形成された表面、および前記表面の反対側に位置する裏面を有する半導体チップと、

前記半導体チップが搭載されているチップ搭載面、前記チップ搭載面の反対側に位置する実装面、前記チップ搭載面に配置され、前記半導体チップの前記複数の電極パッドと電気的に接続されている複数のボンディングパッド、前記実装面に配置され、前記複数のボンディングパッドと電気的に接続される複数の第1ランド、および前記複数のボンディングパッドと前記複数の第1ランドを電気的に接続する複数層の配線層を有する配線基板と、

を有し、

前記配線基板は、

前記複数のボンディングパッドと電気的に接続される複数の第1ビア配線、前記複数の第1ビア配線の周囲に、前記複数の第1ビア配線と離間して設けられている第1導体プレーン、および前記複数の第1ビア配線および前記第1導体プレーンを覆う第1絶縁層を備える第1配線層と、

前記複数の第1ビア配線と電気的に接続されている複数の第2層配線、前記複数の第2層配線と電気的に接続されている複数の第2ビア配線、前記複数の第2層配線および前記複数の第2ビア配線の周囲に、前記複数の第2層配線および前記複数の第2ビア配線と離間して設けられている第2導体プレーン、および、前記複数の第2層配線、前記複数の第2ビア配線、および前記第2導体プレーンを覆う第2絶縁層を備え、前記第1配線層よりも前記実装面側に位置している第2配線層と、

前記複数の第2ビア配線と電気的に接続されている複数の第1スルーホールランド、前記複数の第1スルーホールランドの周囲に、前記複数の第1スルーホールランドと離間して設けられている第3導体プレーン、および、前記複数の第1スルーホールランドおよび前記第3導体プレーンを覆う第3絶縁層を備え、前記第2配線層よりも前記実装面側に位置している第3配線層と、

前記第3配線層が形成されている第1面、前記第1面の反対側に位置する第2面、前記第1または第2面のうち、一方から他方に向かって貫通するように形成されている複数のスルーホール、および、前記複数のスルーホールの内壁のそれぞれを覆うように形成され、かつ、前記複数の第1スルーホールランドのそれぞれと一体に形成されている複数のスルーホール配線、を備えているコア絶縁層と、

を有し、

前記配線基板の厚さ方向の断面視において、前記複数の第2層配線は前記第1配線層の前記第1導体プレーンと前記第3配線層の前記第3導体プレーンに挟まれており、

前記第1配線層の前記第1導体プレーンには、前記第3配線層の前記複数の第1スルーホールランドと厚さ方向に重なる位置に、前記複数の第1スルーホールランドのそれぞれの平面積よりも大きい開口面積を有し、前記第1絶縁層が開口部内全体に埋め込まれている複数の第1開口部が形成されており、

前記第2配線層の前記第2導体プレーンには、前記第1配線層の前記複数の第1開口部のそれぞれと厚さ方向に重なる位置に、前記複数の第1スルーホールランドのそれぞれの平面積よりも大きい開口面積を有している複数の第2開口部が形成されており、

平面視において、前記複数の第2ビア配線のそれぞれは、前記複数の第1および第2開口部内に形成され、かつ、前記複数の第2ビア配線のそれぞれは、前記第1配線層の前記第1導体プレーンと重ならず、

前記複数の第2ビア配線のそれぞれは、平面視において前記複数の第1スルーホールランドに重なり、かつ、前記複数のスルーホールには重ならない半導体装置。 - 請求項1において、

前記配線基板は、

前記コア絶縁層の前記第2面に形成され、かつ前記複数のスルーホール配線のそれぞれと一体に形成される複数の第2スルーホールランド、前記複数の第2スルーホールランドの周囲に、前記複数の第2スルーホールランドと離間して設けられている第4導体プレーン、および、前記複数の第2スルーホールランドおよび前記第4導体プレーンを覆う第4絶縁層を備え、前記コア絶縁層よりも前記実装面側に位置している第4配線層と、

前記複数の第2スルーホールランドと電気的に接続されている複数の第3ビア配線、前記複数の第3ビア配線の周囲に、前記複数の第3ビア配線と離間して設けられている第5導体プレーン、および、前記複数の第3ビア配線および前記第5導体プレーンを覆う第5絶縁層を備え、前記第4配線層よりも前記実装面側に位置している第5配線層と、

前記複数の第3ビア配線と電気的に接続されている複数の第4ビア配線、前記複数の第4ビア配線と電気的に接続されている前記複数の第1ランド、前記複数の第1ランドおよび前記複数の第4ビア配線の周囲に、前記複数の第1ランドおよび前記複数の第4ビア配線と離間して設けられている第6導体プレーン、および前記複数の第4ビア配線および前記第6導体プレーンを覆う第6絶縁層を備える第6配線層と、

を有し、

前記複数の第1ランドのそれぞれの平面積は、前記複数の第2スルーホールランドのそれぞれの平面積よりも大きく、

前記第4配線層の前記第4導体プレーンには、前記第6配線層の前記複数の第1ランドと厚さ方向に重なる位置に、前記複数の第1ランドのそれぞれの平面積よりも大きい開口面積を有する複数の第3開口部が形成されており、

前記第5配線層の前記第5導体プレーンには、前記第4配線層の前記複数の第3開口部のそれぞれと厚さ方向に重なる位置に、前記複数の第1ランドのそれぞれの平面積よりも大きい開口面積を有する複数の第4開口部が形成されており、

平面視において、前記複数の第4ビア配線のそれぞれは、前記複数の第3および第4開口部内に形成され、かつ、前記複数の第4ビア配線のそれぞれは、前記第4配線層の前記第4導体プレーンおよび前記第5配線層の前記第5導体プレーンと重ならない半導体装置。 - 請求項2において、

前記第1配線層に形成される前記複数の第1開口部のそれぞれの開口面積は、

前記第5配線層に形成される前記複数の第4開口部のそれぞれの開口面積よりも小さい半導体装置。 - 請求項3において、

前記第4配線層に形成された前記複数の第2スルーホールランドと、前記第6絶縁層に形成された前記複数の第1ランドとは、厚さ方向に重なっている半導体装置。 - 請求項4において、

前記第1配線層に形成される前記複数の第1開口部のそれぞれの開口面積は、

前記第4配線層に形成される前記複数の第3開口部のそれぞれの開口面積よりも小さい半導体装置。 - 請求項5において、

前記第1配線層に形成される前記複数の第1開口部、前記第2配線層に形成される前記複数の第2開口部のそれぞれの開口形状および開口面積は同じであり、

平面視において、前記複数の第1開口部の輪郭と前記複数の第2開口部の輪郭は重なる半導体装置。 - 請求項6において、

前記第4配線層に形成される前記複数の第3開口部、前記第5配線層に形成される前記複数の第4開口部のそれぞれの開口形状および開口面積は同じであり、

平面視において、前記複数の第3開口部の輪郭と前記複数の第4開口部の輪郭は重なる半導体装置。 - 請求項3において、

前記第4配線層に形成された前記複数の第2スルーホールランドと、前記第6絶縁層に形成された前記複数の第1ランドとは、厚さ方向に重なっていない半導体装置。 - 請求項8において、

前記第5配線層には、前記複数の第3ビア配線と電気的に接続されている複数の第5層配線が形成されており、

前記第6配線層の前記複数の第4ビア配線は、前記複数の第5層配線のそれぞれを介して前記複数の第3ビア配線と電気的に接続されており、

前記配線基板の厚さ方向の断面視において、前記複数の第5層配線は前記第4配線層の前記第4導体プレーンと前記第6配線層の前記第6導体プレーンに挟まれている半導体装置。 - 請求項9において、

前記第4配線層に形成される前記複数の第3開口部のそれぞれの開口面積は、

前記第5配線層に形成される前記複数の第4開口部のそれぞれの開口面積よりも小さい半導体装置。 - 請求項10において、

前記第5配線層の前記第5導体プレーンには、前記第4配線層の前記複数の第2スルーホールランドと厚さ方向に重なる位置に、前記複数の第2スルーホールランドのそれぞれの平面積よりも大きい開口面積を有し、前記第5絶縁層が開口部内全体に埋め込まれている複数の第5開口部が形成されており、

前記第6配線層の前記第6導体プレーンには、前記第5配線層の前記複数の第5開口部のそれぞれと厚さ方向に重なる位置に、前記複数の第2スルーホールランドのそれぞれの平面積よりも大きい開口面積を有している複数の第6開口部が形成されており、

平面視において、前記複数の第3ビア配線のそれぞれは、前記複数の第5および第6開口部内に形成され、かつ、前記複数の第3ビア配線のそれぞれは、前記第4配線層の前記第4導体プレーンおよび前記第5配線層の前記第5導体プレーンと重ならない半導体装置。 - 請求項8において、

前記配線基板の前記チップ搭載面側において、前記複数のボンディングパッドは、前記配線基板の前記複数の第2層配線を介して前記半導体チップへの入力信号が伝送される複数の入力用ボンディングパッドと、前記配線基板の前記複数の第2層配線に対して前記半導体チップからの出力信号が伝送される複数の出力用ボンディングパッドと、の対がそれぞれまとまって配置されており、

前記配線基板の前記実装面において、前記複数の第1ランドのうち、前記複数の入力用ボンディングパッドと電気的に接続される複数の入力用ランドと、前記複数の出力用ボンディングパッドと電気的に接続される複数の出力用ランドとは、異なる位置にそれぞれまとまって配置されている半導体装置。 - 請求項1において、

前記複数の第1ランドの平面積は、前記複数の第1スルーホールランドの平面積よりも大きく、

前記複数の第1開口部、および前記複数の第2開口部の開口面積は、前記複数の第1ランドの平面積よりも小さい半導体装置。 - 請求項1において、

前記複数の第2層配線のそれぞれは、差動信号が流れる一対の信号配線から成る半導体装置。 - 請求項1において、

前記第1配線層には、前記複数のボンディングパッドのうちの第2ボンディングパッドと電気的に接続され、かつ、前記複数の第2層配線とは電気的に分離されている第1層配線が形成されており、

前記複数の第2層配線に流れる電気信号の伝送速度は、前記第1層配線に流れる電気信号の伝送速度よりも大きい半導体装置。 - 請求項1において、

前記第1配線層には、前記複数のボンディングパッドのうちの第2ボンディングパッドと電気的に接続され、かつ、前記複数の第2層配線とは電気的に分離されている第1層配線が形成されており、

平面視において、前記第1層配線と前記複数の第2層配線は重ならないように配置されている半導体装置。 - 請求項1において、

前記第1、第2および第3導体プレーンには、接地電位が供給されている半導体装置。 - 複数の電極パッドが形成された表面、および前記表面の反対側に位置する裏面を有する半導体チップと、

前記半導体チップが搭載されているチップ搭載面、前記チップ搭載面の反対側に位置する実装面、前記チップ搭載面に配置され、前記半導体チップの前記複数の電極パッドと電気的に接続されている複数のボンディングパッド、前記実装面に配置され、前記複数のボンディングパッドと電気的に接続される複数の第1ランド、および前記複数のボンディングパッドと前記複数の第1ランドを電気的に接続する複数層の配線層を有する配線基板と、

を有し、

前記配線基板は、

前記複数の第1ランド、前記複数の第1ランドと電気的に接続される複数の第1ビア配線、前記複数の第1ランドおよび前記複数の第1ビア配線の周囲に、前記複数の第1ランドおよび前記複数の第1ビア配線と離間して設けられている第1導体プレーン、および前記複数の第1ビア配線および前記第1導体プレーンを覆う第1絶縁層を備える第1配線層と、

前記複数の第1ビア配線と電気的に接続されている複数の第2層配線、前記複数の第2層配線と電気的に接続されている複数の第2ビア配線、前記複数の第2層配線および前記複数の第2ビア配線の周囲に、前記複数の第2層配線および前記複数の第2ビア配線と離間して設けられている第2導体プレーン、および、前記複数の第2層配線、前記複数の第2ビア配線、および前記第2導体プレーンを覆う第2絶縁層を備え、前記第1配線層よりも前記チップ搭載面側に位置している第2配線層と、

前記複数の第2ビア配線と電気的に接続されている複数の第1スルーホールランド、前記複数の第1スルーホールランドの周囲に、前記複数の第1スルーホールランドと離間して設けられている第3導体プレーン、および、前記複数の第1スルーホールランドおよび前記第3導体プレーンを覆う第3絶縁層を備え、前記第2配線層よりも前記チップ搭載面側に位置している第3配線層と、

前記第3配線層が形成されている第1面、前記第1面の反対側に位置する第2面、前記第1または第2面のうち、一方から他方に向かって貫通するように形成されている複数のスルーホール、および、前記複数のスルーホールの内壁のそれぞれを覆うように形成され、かつ、前記複数の第1スルーホールランドのそれぞれと一体に形成されている複数のスルーホール配線、を備えている第4絶縁層と、

を有し、

前記配線基板の厚さ方向の断面視において、前記複数の第2層配線は前記第1配線層の前記第1導体プレーンと前記第3配線層の前記第3導体プレーンに挟まれており、

平面視において、前記複数の第1スルーホールランドと前記複数の第1ランドは、それぞれ厚さ方向に重ならない位置に配置され、

前記第2配線層の前記第2導体プレーンには、前記第3配線層の前記複数の第1スルーホールランドと厚さ方向に重なる位置に、前記複数の第1スルーホールランドのそれぞれの平面積よりも大きい開口面積を有している複数の第1開口部が形成されており、

前記第1配線層の前記第1導体プレーンには、前記第2配線層の前記複数の第1開口部のそれぞれと厚さ方向に重なる位置に、前記複数の第1スルーホールランドのそれぞれの平面積よりも大きい開口面積を有し、第1絶縁層が開口部内全体に埋め込まれている複数の第2開口部が形成されており、

平面視において、前記複数の第2ビア配線のそれぞれは、前記複数の第1および第2開口部内に形成され、かつ、前記複数の第2ビア配線のそれぞれは、前記第1配線層の前記第1導体プレーンおよび前記第2配線層の前記第2導体プレーンと重ならず、

前記複数の第2ビア配線のそれぞれは、平面視において前記複数の第1スルーホールランドに重なり、かつ、前記複数のスルーホールには重ならない半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013044393A JP6114577B2 (ja) | 2013-03-06 | 2013-03-06 | 半導体装置 |

| US14/196,736 US9330992B2 (en) | 2013-03-06 | 2014-03-04 | Wiring substrate for a semiconductor device having differential signal paths |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013044393A JP6114577B2 (ja) | 2013-03-06 | 2013-03-06 | 半導体装置 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016243454A Division JP6258460B2 (ja) | 2016-12-15 | 2016-12-15 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014175356A JP2014175356A (ja) | 2014-09-22 |

| JP2014175356A5 JP2014175356A5 (ja) | 2015-09-17 |

| JP6114577B2 true JP6114577B2 (ja) | 2017-04-12 |

Family

ID=51486860

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013044393A Active JP6114577B2 (ja) | 2013-03-06 | 2013-03-06 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9330992B2 (ja) |

| JP (1) | JP6114577B2 (ja) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2775806B1 (en) * | 2013-03-07 | 2015-03-04 | Tyco Electronics Svenska Holdings AB | Optical receiver and transceiver using the same |

| USD758372S1 (en) | 2013-03-13 | 2016-06-07 | Nagrastar Llc | Smart card interface |

| USD759022S1 (en) * | 2013-03-13 | 2016-06-14 | Nagrastar Llc | Smart card interface |

| JP5967071B2 (ja) * | 2013-12-26 | 2016-08-10 | 株式会社デンソー | 電子制御装置、および、これを用いた電動パワーステアリング装置 |

| JP2015170770A (ja) * | 2014-03-07 | 2015-09-28 | イビデン株式会社 | プリント配線板 |

| US9589946B2 (en) * | 2015-04-28 | 2017-03-07 | Kabushiki Kaisha Toshiba | Chip with a bump connected to a plurality of wirings |

| USD864968S1 (en) | 2015-04-30 | 2019-10-29 | Echostar Technologies L.L.C. | Smart card interface |

| US9666544B2 (en) | 2015-06-02 | 2017-05-30 | Sarcina Technology LLC | Package substrate differential impedance optimization for 25 GBPS and beyond |

| US10276519B2 (en) | 2015-06-02 | 2019-04-30 | Sarcina Technology LLC | Package substrate differential impedance optimization for 25 to 60 Gbps and beyond |

| US10410984B1 (en) | 2015-06-02 | 2019-09-10 | Sarcina Technology LLC | Package substrate differential impedance optimization for 25 to 60 GBPS and beyond |

| JP6534312B2 (ja) * | 2015-07-31 | 2019-06-26 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US9974174B1 (en) * | 2016-10-26 | 2018-05-15 | Nxp Usa, Inc. | Package to board interconnect structure with built-in reference plane structure |

| JP2019009319A (ja) | 2017-06-26 | 2019-01-17 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6867268B2 (ja) * | 2017-10-13 | 2021-04-28 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6853774B2 (ja) * | 2017-12-21 | 2021-03-31 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP7001530B2 (ja) * | 2018-04-16 | 2022-01-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| CN111508901B (zh) * | 2019-10-01 | 2022-01-25 | 威锋电子股份有限公司 | 集成电路芯片、封装基板及电子总成 |

| US11342307B2 (en) * | 2019-10-14 | 2022-05-24 | Nanya Technology Corporation | Semiconductor structure and manufacturing method thereof |

| JP2021085709A (ja) * | 2019-11-26 | 2021-06-03 | 日本電気株式会社 | 電子回路装置 |

| US20220069489A1 (en) * | 2020-08-28 | 2022-03-03 | Unimicron Technology Corp. | Circuit board structure and manufacturing method thereof |

| JP2024041144A (ja) * | 2022-09-14 | 2024-03-27 | 京セラドキュメントソリューションズ株式会社 | 信号処理基板、画像形成装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6587008B2 (en) | 2000-09-22 | 2003-07-01 | Kyocera Corporation | Piezoelectric oscillator and a method for manufacturing the same |

| KR100917081B1 (ko) * | 2001-03-14 | 2009-09-15 | 이비덴 가부시키가이샤 | 다층 프린트 배선판 |

| JP2003168864A (ja) * | 2001-09-20 | 2003-06-13 | Kyocera Corp | 多層配線基板 |

| JP2003124633A (ja) * | 2001-10-19 | 2003-04-25 | Kyocera Corp | 多層配線基板 |

| JP3872413B2 (ja) * | 2002-11-05 | 2007-01-24 | 三菱電機株式会社 | 半導体装置 |

| WO2005076683A1 (ja) * | 2004-02-04 | 2005-08-18 | Ibiden Co., Ltd. | 多層プリント配線板 |

| JP4606776B2 (ja) | 2004-05-28 | 2011-01-05 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2006049645A (ja) * | 2004-08-05 | 2006-02-16 | Ngk Spark Plug Co Ltd | 配線基板 |

| JP2010219498A (ja) | 2009-02-20 | 2010-09-30 | Elpida Memory Inc | 半導体装置 |

| WO2011018938A1 (ja) * | 2009-08-12 | 2011-02-17 | 日本電気株式会社 | 多層プリント配線板 |

| JP2011138846A (ja) * | 2009-12-27 | 2011-07-14 | Kyocer Slc Technologies Corp | 配線基板 |

-

2013

- 2013-03-06 JP JP2013044393A patent/JP6114577B2/ja active Active

-

2014

- 2014-03-04 US US14/196,736 patent/US9330992B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9330992B2 (en) | 2016-05-03 |

| JP2014175356A (ja) | 2014-09-22 |

| US20140252612A1 (en) | 2014-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6114577B2 (ja) | 半導体装置 | |

| JP6342994B2 (ja) | 半導体装置およびその製造方法 | |

| JP6609633B2 (ja) | 半導体装置 | |

| JP6324738B2 (ja) | 半導体装置 | |

| JP6207422B2 (ja) | 電子装置 | |

| US10446531B2 (en) | Electronic device and semiconductor device | |

| JP6317855B2 (ja) | 電子装置 | |

| US11784173B2 (en) | Semiconductor device including a circuit for transmitting a signal | |

| JP2019186479A (ja) | 半導体装置 | |

| JP2019114601A (ja) | 半導体装置 | |

| JP6258460B2 (ja) | 半導体装置 | |

| US20200168540A1 (en) | Semiconductor device and electronic device | |

| TWI770287B (zh) | 半導體裝置 | |

| KR100671808B1 (ko) | 반도체 장치 | |

| JP2023034619A (ja) | 半導体装置 | |

| JP2022191691A (ja) | 半導体装置 | |

| KR20240067812A (ko) | 반도체 장치 | |

| JP2012174998A (ja) | 半導体装置 | |

| JP2010123608A (ja) | 半導体装置及び半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150724 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150724 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160526 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160531 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160728 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20160920 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161215 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20161226 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170317 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6114577 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |