JP6082037B2 - トランジスタの作製方法 - Google Patents

トランジスタの作製方法 Download PDFInfo

- Publication number

- JP6082037B2 JP6082037B2 JP2015004136A JP2015004136A JP6082037B2 JP 6082037 B2 JP6082037 B2 JP 6082037B2 JP 2015004136 A JP2015004136 A JP 2015004136A JP 2015004136 A JP2015004136 A JP 2015004136A JP 6082037 B2 JP6082037 B2 JP 6082037B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide semiconductor

- transistor

- insulating layer

- semiconductor layer

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10P14/22—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D99/00—Subject matter not provided for in other groups of this subclass

-

- H10P14/3426—

-

- H10P14/3434—

Landscapes

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

- Physical Deposition Of Substances That Are Components Of Semiconductor Devices (AREA)

- Physical Vapour Deposition (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Dram (AREA)

Description

半導体特性を利用することで機能する素子および装置全般を指すものである。

装置を半導体集積回路や電子デバイスに応用する技術が注目されている。例えば、半導体

材料として酸化亜鉛、In−Ga−Zn−O系酸化物半導体を用いてトランジスタを作製

し、画像表示装置のスイッチング素子などに用いる技術が特許文献1及び特許文献2で開

示されている。

モルファスシリコンを用いたトランジスタよりも高い移動度が得られている。さらに、酸

化物半導体膜はスパッタリング法(スパッタ法ともいう)などによって比較的低温で膜形

成が可能であり、多結晶シリコンを用いたトランジスタよりも製造工程が容易である。例

えば、特許文献3では、対向して配置された一組のターゲットを用いたスパッタリング法

により形成した酸化亜鉛薄膜をチャネル形成領域に用いた薄膜トランジスタが開示されて

いる。

えない。例えば、酸化物半導体層を用いたトランジスタには、制御された閾値電圧、高い

動作速度等の電気的特性、または十分な信頼性が求められている。

を提供することを目的の一とする。または、高い信頼性を有する半導体装置、若しくはそ

の作製方法を提供することを目的の一とする。

メージが混入すると、ゲート絶縁層と酸化物半導体層との界面に欠陥(界面トラップ)を

生じる。更には、ゲート絶縁層中及び酸化物半導体層中の一方または双方にプラズマダメ

ージが混入すると、欠陥(膜中トラップ)を生じる。これらの欠陥は、トランジスタの閾

値電圧がシフトする原因となる。

リア密度(キャリア濃度ともいう)にも影響される。また、酸化物半導体膜に含まれるキ

ャリアは、酸化物半導体膜に含まれる不純物により発生する。例えば、成膜された酸化物

半導体膜に含まれるH2Oに代表される水素原子を含む化合物や炭素原子を含む化合物、

もしくは水素原子や炭素原子等の不純物は、酸化物半導体膜のキャリア密度を高める。

導体膜を用いて作製したトランジスタは、閾値電圧のシフトなどの経時劣化を制御するこ

とが困難である。

層中、またはその界面の少なくとも一へのプラズマダメージを抑制し、且つ、酸化物半導

体膜に含まれるキャリア密度に影響する不純物、例えば、H2Oに代表される水素原子を

含む化合物、もしくは水素原子等の不純物を排除すればよい。

半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、ゲート電極と酸化

物半導体層との間に設けられたゲート絶縁層と、を有し、酸化物半導体層は、対向ターゲ

ット方式を用いたスパッタリング法により成膜され、且つ酸化物半導体層に含まれるキャ

リア濃度が、1×1012/cm3未満である半導体装置である。

導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、ゲート電極と酸化物

半導体層との間に設けられたゲート絶縁層と、を有し、酸化物半導体層に含まれるキャリ

ア濃度は、1×1012/cm3未満であり、ゲート絶縁層は、対向ターゲット方式を用

いたスパッタリング法により成膜される半導体装置である。

ッタリング法により成膜されるのが好ましい。

さらに有し、絶縁層は、対向ターゲット方式を用いたスパッタリング法により成膜される

のが好ましい。

縁層を形成し、ゲート絶縁層上に酸化物半導体層を形成し、酸化物半導体層と電気的に接

続するソース電極及びドレイン電極を形成する半導体装置の作製方法であって、酸化物半

導体層は、対向させて配置した一組のターゲットを用いたスパッタリング法により成膜さ

れ、酸化物半導体層形成後に、第1の加熱処理により、酸化物半導体層に含まれる水素濃

度を低減し、第2の加熱処理により、酸化物半導体層に酸素を供給する半導体装置の作製

方法である。

的に接続するソース電極及びドレイン電極を形成し、酸化物半導体層の少なくともチャネ

ル形成領域と接するゲート絶縁層を形成し、ゲート絶縁層上に、ゲート電極を形成する半

導体装置の作製方法であって、酸化物半導体層は、対向させて配置した一組のターゲット

を用いたスパッタリング法により成膜され、酸化物半導体層形成後に、第1の加熱処理に

より、酸化物半導体層に含まれる水素濃度を低減し、第2の加熱処理により、酸化物半導

体層に酸素を供給する半導体装置の作製方法である。

のターゲットを用いたスパッタリング法により形成するのが好ましい。

置した一組のターゲットを用いたスパッタリング法により絶縁層を形成するのが好ましい

。

下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表

現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

ものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆

もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が

一体となって形成されている場合をなどをも含む。

動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明

細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるも

のとする。

して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、

接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば

、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどの

スイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子

などが含まれる。

ある。

することができる。

ことができる。

の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および

詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下

に示す実施の形態の記載内容に限定して解釈されるものではない。

際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必

ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

同を避けるために付すものであり、数的に限定するものではないことを付記する。

本実施の形態では、開示する発明の一態様に係る半導体装置の構成およびその作製工程の

例について、図1乃至図4を参照して説明する。

図1(A)乃至図1(D)に、半導体装置の例として、トランジスタの断面構造を示す。

基板100上に、酸化物半導体層144と、酸化物半導体層144に接して設けられたソ

ース電極142a及びドレイン電極142bと、酸化物半導体層144の少なくともチャ

ネル形成領域、ソース電極142a及びドレイン電極142bを覆うゲート絶縁層146

と、ゲート絶縁層146上に設けられ、酸化物半導体層144のチャネル形成領域と重な

るゲート電極148と、を有している。

り、図1(A)に示すトランジスタ160との相違の一は、ソース電極142a及びドレ

イン電極142bと、酸化物半導体層144との積層順である。すなわち、図1(B)に

示すトランジスタ170は、基板100上に、ソース電極142a及びドレイン電極14

2bと、ソース電極142a及びドレイン電極142bの一端面に少なくとも接する酸化

物半導体層144と、酸化物半導体層144上に設けられたゲート絶縁層146と、ゲー

ト絶縁層146上に設けられ、酸化物半導体層144のチャネル形成領域と重なるゲート

電極148と、を有している。

基板100上に、ゲート電極148と、ゲート電極148を覆うゲート絶縁層146と、

ゲート絶縁層146上に設けられたソース電極142a及びドレイン電極142bと、ソ

ース電極142a及びドレイン電極142bの一端面に少なくとも接する酸化物半導体層

144と、酸化物半導体層144上に設けられた絶縁層150と、を有している。なお、

絶縁層150は、必ずしも設けなくとも良い。

り、図1(C)に示すトランジスタ180との相違の一は、ソース電極142a及びドレ

イン電極142bと、酸化物半導体層144との積層順である。すなわち、図1(D)に

示すトランジスタ190は、基板100上に、ゲート電極148と、ゲート電極148を

覆うゲート絶縁層146と、ゲート絶縁層146上に設けられた酸化物半導体層144と

、酸化物半導体層144に接して設けられたソース電極142a及びドレイン電極142

bと、酸化物半導体層144の少なくともチャネル形成領域、ソース電極142a及びド

レイン電極142bを覆う絶縁層150と、を有している。なお、絶縁層150は、必ず

しも設けなくとも良い。

素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることに

より、高純度化された酸化物半導体層である。具体的には、例えば、酸化物半導体層14

4の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atom

s/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上

述の酸化物半導体層144中の水素濃度は、二次イオン質量分析法(SIMS:Seco

ndary Ion Mass Spectroscopy)で測定されるものである。

このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠

乏に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体層144では、

水素や酸素欠陥等に由来するキャリア濃度が1×1012/cm3未満、望ましくは、1

×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。酸化

物半導体層144を有するトランジスタでは、オフ電流を十分に小さくすることが可能で

ある。例えば、酸化物半導体層144の膜厚が30nmで、チャネル長が2μmのトラン

ジスタの、室温(25℃)でのチャネル幅1μmあたりのオフ電流(ゲートバイアスは−

3V)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは

10zA以下となる。このように、高純度化された酸化物半導体(以下、本明細書では、

I型化(真性化)または実質的にI型化された酸化物半導体ともいう)を用いることで、

極めて優れたオフ電流特性のトランジスタを得ることができる。

4、またはゲート絶縁層146の少なくとも一、好ましくは双方が、図2に示す対向ター

ゲット方式のスパッタリング装置を用いて成膜されており、成膜時に生じるプラズマ等の

電界の影響が低減されている。

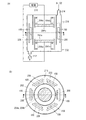

図2に示すスパッタリング装置は、真空容器202内に、対向して配置された一組のター

ゲット204a及びターゲット204bと、ターゲット204a及びターゲット204b

のスパッタ面に対して垂直な方向に磁界を発生させる永久磁石等の磁界発生手段206a

〜206dと、基板100を載置するための基板ホルダー208と、を有している。図2

において、ターゲットは、電源210と接続された電極(図示せず)にそれぞれ固定され

ている。基板ホルダー208は、基板100面内における膜厚分布を抑制するために、基

板100を図2の左から右(あるいはその逆)へ移動可能であるのが好ましい。

02内を減圧または真空状態とし、ガス供給手段(図示せず)と連結された供給管214

よりスパッタガスとして酸素(O2)ガスとアルゴン(Ar)ガスの混合ガス、またはA

rガスを導入する。その後、ターゲット204a及びターゲット204bに電圧を印加す

ることによりスパッタガスを励起し、励起されたイオンによりターゲット204a及びタ

ーゲット204bをスパッタリングする。スパッタリングに用いる電源は、DC(直流)

電源またはRF(交流)電源のいずれを用いても良いが、酸化物半導体層を成膜する場合

には、DC電源を用いるのが好ましく、ゲート絶縁層(絶縁層)を成膜する場合には、R

F電源を用いるのが好ましい。

垂直な方向に発生した磁界によって、プラズマがターゲット204a及びターゲット20

4b間に閉じこめられ、基板100に直接作用しないため、成膜される膜及びその下地と

なる膜にプラズマによるダメージを与えずに成膜することが可能である。なお、成膜速度

が安定するまでシャッター216によって基板100への被膜形成を停止しておき、成膜

時にシャッター216を開けて成膜を開始するのが好ましい。シャッター216の形状は

図2に限定されない。

もよい。基板ホルダー208のヒータを用いて、減圧状態に保持された真空容器202内

に基板100を保持し、基板100の温度が100℃以上550℃未満、好ましくは20

0℃以上400℃以下となるように基板100上の膜を熱することもできる。そして、真

空容器202内の水分を除去しつつ、水素や水などが除去されたスパッタガス(酸素また

はアルゴン)を導入し、上記ターゲット204a、204bを用いて成膜を行う。基板ホ

ルダー208のヒータを用いて、基板100を熱しながら成膜することにより、スパッタ

による損傷をより軽減することもできる。

い。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用い

ることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。

クライオポンプなどを用いて排気することで、真空容器202から水素や水などを除去す

ることができる。

、特に限定されず、基板ホルダー208で基板100の被成膜面が真空容器202底面に

対して斜め、または垂直になるように配置してもよい。

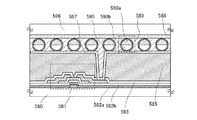

3に示すように、真空容器202内に基板を複数枚(図3では6枚)配置することができ

る。なお、図3(A)は真空容器202の断面模式図であり、図3(B)は、図3(A)

における鎖線A−Bの断面を上方からみた上面模式図である。

とターゲット204bとが対向して配置され、該空間に表面が面するように、6枚の基板

100が円状に配置されている。また、円筒状のシャッター216を装置上方または下方

から伸縮させることで、成膜速度が安定するまでシャッター216によって基板100へ

の被膜形成を停止しておき、成膜時にシャッター216を開けて成膜を開始するのが好ま

しい。シャッター216の形状は図3に限定されない。

とが可能となるため、半導体装置の製造工程におけるスループットを向上させることがで

きる。

において、絶縁層150を図2または図3に示すスパッタリング装置を用いて成膜すると

より好ましい。

以下、図4及び図5を用いて、図1に示すトランジスタの作製工程の例について説明する

。

まず、図4(A)乃至図4(C)を用いて、図1(A)に示すトランジスタ160の作製

工程の一例について説明する。

て島状の酸化物半導体層144を形成する(図4(A)参照)。酸化物半導体層の成膜に

は、図2または図3に示した対向ターゲット方式のスパッタリング法を用いるのが好まし

い。酸化物半導体層の成膜に対向ターゲット方式のスパッタリング法を用いることで、被

成膜面、及び、形成される酸化物半導体層へのプラズマによる損傷(プラズマダメージ)

を抑制することができ、膜質の良い酸化物半導体層とすることができる。

に耐えうる程度の耐熱性を有していることが必要となる。例えば、ガラス基板、セラミッ

ク基板、石英基板、サファイア基板など基板を用いることができる。また、少なくとも酸

化物半導体層144の形成面に絶縁表面を有していれば、シリコンや炭化シリコンなどの

単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、

SOI基板などを適用することも可能であり、これらの基板上に半導体素子が設けられて

いてもよい。また、基板100上に下地膜が設けられていても良い。

属酸化物であるIn−Ga−Zn−O系、In−Sn−Zn−O系、In−Al−Zn−

O系、Sn−Ga−Zn−O系、Al−Ga−Zn−O系、Sn−Al−Zn−O系や、

二元系金属酸化物であるIn−Zn−O系、Sn−Zn−O系、Al−Zn−O系、Zn

−Mg−O系、Sn−Mg−O系、In−Mg−O系や、In−O系、Sn−O系、Zn

−O系などを用いて形成することができる。

フ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体

装置に用いる半導体材料としては好適である。

m(m>0)で表記されるものがある。また、Gaに代えてMを用い、InMO3(Zn

O)m(m>0)のように表記される酸化物半導体材料がある。ここで、Mは、ガリウム

(Ga)、アルミニウム(Al)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、

コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、

Mとしては、Ga、GaおよびAl、GaおよびFe、GaおよびNi、GaおよびMn

、GaおよびCoなどを適用することができる。なお、上述の組成は結晶構造から導き出

されるものであり、あくまでも一例に過ぎないことを付記する。

1:x:y(xは0以上、yは0.5以上5以下)の組成式で表されるものを用いるのが

好適である。例えば、In:Ga:Zn=1:1:1[atom比](x=1、y=1)

、(すなわち、In2O3:Ga2O3:ZnO=1:1:2[mol数比])の組成比

を有するターゲットなどを用いることができる。また、In:Ga:Zn=1:1:0.

5[atom比](x=1、y=0.5)の組成比を有するターゲットや、In:Ga:

Zn=1:1:2[atom比](x=1、y=2)の組成比を有するターゲットや、I

n:Ga:Zn=1:0:1[atom比](x=0、y=1)の組成比を有するターゲ

ットを用いることもできる。

成比は、原子数比で、In:Zn=50:1〜1:2(モル数比に換算するとIn2O3

:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(モル数比に

換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=1

5:1〜1.5:1(モル数比に換算するとIn2O3:ZnO=15:2〜3:4)と

する。例えば、In−Zn−O系酸化物半導体の形成に用いるターゲットは、原子数比が

In:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

物ターゲットを用いる対向ターゲット方式のスパッタリング法により形成することとする

。

さらに好ましくは99.9%以上である。相対密度の高い金属酸化物ターゲットを用いる

ことにより、緻密な構造の酸化物半導体層を形成することが可能である。

たは、希ガス(代表的にはアルゴン)と酸素との混合雰囲気とするのが好適である。具体

的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度1ppm以下(望ま

しくは濃度10ppb以下)にまで除去された高純度ガス雰囲気を用いるのが好適である

。

持し、被処理物の温度が100℃以上550℃未満、好ましくは200℃以上400℃以

下となるように被処理物を熱する。または、酸化物半導体層の形成の際の被処理物の温度

は、室温(25℃±10℃)としてもよい。そして、処理室内の水分を除去しつつ、水素

や水などが除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体層を

形成する。被処理物を熱しながら酸化物半導体層を形成することにより、酸化物半導体層

に含まれる不純物を低減することができる。また、スパッタによる損傷を軽減することが

できる。処理室内の水分を除去するためには、吸着型の真空ポンプを用いることが好まし

い。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用い

ることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。

クライオポンプなどを用いて排気することで、処理室から水素や水などを除去することが

できるため、酸化物半導体層中の不純物濃度を低減できる。

される粉状の物質など)を低減でき、膜厚分布も均一となるため好ましい。酸化物半導体

層の厚さは、1nm以上50nm以下、好ましくは1nm以上30nm以下、より好まし

くは1nm以上10nm以下とする。このような厚さの酸化物半導体層を用いることで、

微細化に伴う短チャネル効果を抑制することが可能である。ただし、適用する酸化物半導

体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用いる材

料や用途などに応じて選択することもできる。

第1の熱処理によって酸化物半導体層中の、過剰な水素(水や水酸基を含む)を除去し、

酸化物半導体層の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる

。第1の熱処理の温度は、例えば、300℃以上550℃未満、または400℃以上50

0℃以下とする。

る場合、平行平板のスパッタリング装置と比較して成膜時の気相状態が長いため、形成さ

れた酸化物半導体層中には、平行平板のスパッタリング装置で成膜した酸化物半導体層よ

りも高い濃度で水素(水や水酸基を含む)が含有されていることがある。したがって、該

対向ターゲット方式のスパッタリング法を用いて形成された酸化物半導体層144に対し

て脱水・脱水素の効果を奏する第1の熱処理を施すことは、特に効果的である。

450℃、1時間の条件で行うことができる。この間、酸化物半導体層は大気に触れさせ

ず、水や水素の混入が生じないようにする。

によって、被処理物を加熱する装置を用いても良い。例えば、GRTA(Gas Rap

id Thermal Anneal)装置、LRTA(Lamp Rapid The

rmal Anneal)装置等のRTA(Rapid Thermal Anneal

)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ

、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ラン

プなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。

GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴン

などの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が

用いられる。

間熱した後、当該不活性ガス雰囲気から被処理物を取り出すGRTA処理を行ってもよい

。GRTA処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温

度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素

を含むガスに切り替えても良い。酸素を含む雰囲気において第1の熱処理を行うことで、

酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである

。

)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ま

しい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの

純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(

すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

に限りなく近い酸化物半導体層を形成することで、極めて優れた特性のトランジスタを実

現することができる。

当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や

、脱水素化処理は、酸化物半導体層の形成後やゲート絶縁層の形成後、ゲート電極の形成

後、などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱

水素化処理は、一回に限らず複数回行っても良い。

て行っても良い。また、素子の微細化という観点からはドライエッチングを用いるのが好

適であるが、ウェットエッチングを用いても良い。エッチングガスやエッチング液につい

ては被エッチング材料に応じて適宜選択することができる。なお、素子におけるリーク電

流などが問題とならない場合には、酸化物半導体層を島状に加工しないで用いても良い。

ソース電極142a、ドレイン電極142bを形成する(図4(B)参照)。

いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、

タンタル、チタン、モリブデン、タングステンから選ばれた元素や、上述した元素を成分

とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウ

ム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いて

もよい。

ン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウ

ム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構

造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。な

お、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有す

るソース電極142a、およびドレイン電極142bへの加工が容易であるというメリッ

トがある。

ては酸化インジウム、酸化錫、酸化亜鉛、インジウム錫酸化物(ITOと略記する場合が

ある)、酸化インジウム酸化亜鉛、または、これらの金属酸化物材料にシリコン若しくは

酸化シリコンを含有させたものを用いることができる。

部が、テーパー形状となるように行うことが好ましい。ここで、テーパー角は、例えば、

30°以上60°以下であることが好ましい。ソース電極142a、ドレイン電極142

bの端部をテーパー形状となるようにエッチングすることにより、後に形成されるゲート

絶縁層146の被覆性を向上し、段切れを防止することができる。

極142bの下端部の間隔によって決定される。なお、チャネル長(L)が25nm未満

のトランジスタを形成する場合に用いるマスク形成の露光を行う際には、数nm〜数10

nmと波長の短い超紫外線(Extreme Ultraviolet)を用いるのが望

ましい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成され

るトランジスタのチャネル長(L)を、10nm以上1000nm(1μm)以下とする

ことも可能であり、回路の動作速度を高めることが可能である。また、微細化によって、

半導体装置の消費電力を低減することも可能である。

なくともチャネル形成領域に接するゲート絶縁層146を形成し、その後、ゲート絶縁層

146上において酸化物半導体層144と重畳する領域にゲート電極148を形成する(

図4(C)参照)。

ゲート絶縁層146は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウ

ム、酸化タンタル、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート(HfS

ixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSixO

y(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(

x>0、y>0))、などを含むように形成するのが好適である。ゲート絶縁層146は

、単層構造としても良いし、積層構造としても良い。また、その厚さは特に限定されない

が、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くするの

が望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ま

しくは10nm以上50nm以下とすることができる。

パッタリング法を用いるのが好ましい。ゲート絶縁層146の成膜に対向ターゲット方式

のスパッタリング法を用いることで、被成膜面(具体的には、ソース電極142a、ドレ

イン電極142bまたは酸化物半導体層144と、ゲート絶縁層146との界面)、及び

形成されるゲート絶縁層146に対するプラズマによる損傷(プラズマダメージ)を抑制

することができ、膜質の良いゲート絶縁層146とすることができる。また、ゲート絶縁

層146の被覆性を向上し、ゲートリーク電流などの発生を抑制することができる。

問題となる。ゲートリークの問題を解消するには、ゲート絶縁層146に、酸化ハフニウ

ム、酸化タンタル、酸化イットリウム、ハフニウムシリケート(HfSixOy(x>0

、y>0))、窒素が添加されたハフニウムシリケート(HfSixOy(x>0、y>

0))、窒素が添加されたハフニウムアルミネート(HfAlxOy(x>0、y>0)

)、などの高誘電率(high−k)材料を用いると良い。high−k材料をゲート絶

縁層146に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜

厚を大きくすることが可能になる。なお、high−k材料を含む膜と、酸化シリコン、

窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれか

を含む膜との積層構造としてもよい。

処理を行うのが望ましい。熱処理の温度は、200℃以上450℃以下、望ましくは25

0℃以上350℃以下である。例えば、窒素雰囲気下で250℃、1時間の熱処理を行え

ばよい。第2の熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減

することができる。また、ゲート絶縁層146が酸素を含む場合、酸化物半導体層144

に酸素を供給し、該酸化物半導体層144の酸素欠損を補填して、I型(真性半導体)ま

たはI型に限りなく近い酸化物半導体層を形成することもできる。

第2の熱処理のタイミングはこれに限定されない。例えば、ゲート電極の形成後に第2の

熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良いし、第

1の熱処理に第2の熱処理を兼ねさせても良いし、第2の熱処理に第1の熱処理を兼ねさ

せても良い。

半導体層144を、その主成分以外の不純物が極力含まれないように高純度化することが

できる。

的にエッチングすることによって形成することができる。ゲート電極148となる導電層

は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形

成することができる。詳細は、ソース電極142a及びドレイン電極142b上などの場

合と同様であり、これらの記載を参酌できる。

い。例えば、保護絶縁層として酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、

窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができ

る。また、保護絶縁層の成膜に対向ターゲット方式のスパッタリング法を用いることもで

きる。

、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他

に、低誘電率材料(low−k材料)、シロキサン系樹脂、PSG(リンガラス)、BP

SG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶

縁膜を複数積層させることで、平坦化絶縁層を形成してもよい。

42bと、酸化物半導体層144の成膜順以外は、図4に示すトランジスタ160の作製

工程と同様の工程によって作製することが可能である。すなわち、基板100上に、導電

層を形成し、該導電層を選択的にエッチングすることによってソース電極142a及びド

レイン電極142bを形成し、ソース電極142a及びドレイン電極142b上に酸化物

半導体層144を形成した後、酸化物半導体層144に接するゲート絶縁層146を形成

し、その後、ゲート絶縁層146上において酸化物半導体層144と重畳する領域にゲー

ト電極148を形成することで、トランジスタ170を形成することができる。酸化物半

導体層144成膜後には、第1の熱処理及び第2の熱処理を施すのが好ましい。これらの

詳細は図4を参酌することができるため、記載を省略する。

次いで、図5(A)乃至図5(C)を用いて、図1(C)に示すトランジスタ180の作

製工程の一例について説明する。なお、特に記載がない限り、図4に示したトランジスタ

160と同じ符号を付した構成には、同様の材料及び同様の成膜方法を採用することがで

きる。

ゲート電極148を形成する。次いで、ゲート電極148を覆うようにゲート絶縁層14

6を成膜する。その後、ゲート絶縁層146上に導電層を形成し、該導電層を選択的にエ

ッチングしてソース電極142a及びドレイン電極142bを形成する(図5(A)参照

)。

層146としているが、島状に加工されていない構成を採用しても良い。ゲート絶縁層1

46を島状に加工しない場合には、加工の際のエッチングによるゲート絶縁層146の汚

染を防止することができる。

リング法を用いるのが好ましい。ゲート絶縁層146の成膜に対向ターゲット方式のスパ

ッタリング法を用いることで、被成膜面(具体的には、ゲート電極148とゲート絶縁層

146との界面)、及び形成されるゲート絶縁層146に対するプラズマによる損傷(プ

ラズマダメージ)を抑制することができ、膜質の良いゲート絶縁層146とすることがで

きる。また、ゲート絶縁層146の被覆性を向上し、ゲートリーク電流などの発生を抑制

することができる。

物半導体層を成膜し、選択的にエッチングして島状の酸化物半導体層144を形成する(

図5(B)参照)。酸化物半導体層の成膜には、図2または図3に示した対向ターゲット

方式のスパッタリング法を用いるのが好ましい。酸化物半導体層の成膜に対向ターゲット

方式のスパッタリング法を用いることで、被成膜面(具体的には、ソース電極142a、

ドレイン電極142bまたはゲート絶縁層146と、酸化物半導体層との界面)、及び形

成される酸化物半導体層へのプラズマによる損傷(プラズマダメージ)を抑制することが

でき、膜質の良い酸化物半導体層とすることができる。また、酸化物半導体層の被覆性を

向上し、接続不良などの発生を抑制することができる。また、酸化物半導体層144に対

しては、熱処理(第1の熱処理)を行うことが望ましい。

うに絶縁層150を形成する(図5(C)参照)。

、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁層150

に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体

層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化(N型化)し

てしまい、寄生チャネルが形成されるおそれがある。よって、絶縁層150はできるだけ

水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

リング法を用いるのが好ましい。絶縁層150の成膜に対向ターゲット方式のスパッタリ

ング法を用いることで、被成膜面(具体的には、ソース電極142a、ドレイン電極14

2bまたは酸化物半導体層144と、絶縁層150との界面)、及び形成される絶縁層1

50へのプラズマによる損傷(プラズマダメージ)を抑制することができ、膜質の良い絶

縁層とすることができる。また、絶縁層の被覆性を向上し、段切れなどの発生を抑制する

ことができる。

0℃以上400℃以下、例えば250℃以上350℃以下)を行う。例えば、窒素雰囲気

下で250℃、1時間の第2の熱処理を行う。第2の熱処理を行うと、酸化物半導体層1

44が絶縁層150と接した状態で加熱される。

のための熱処理を行って低抵抗化した後、酸化物半導体層の酸素欠損を補填することがで

きる。その結果、高抵抗化(I型化)した酸化物半導体層144が形成される。以上の工

程でトランジスタ180が形成される。

窒化珪素膜を形成することができる。また、保護絶縁層の成膜に対向ターゲット方式のス

パッタリング法を用いることもできる。また、保護絶縁層上に平坦化のための平坦化絶縁

層を設けてもよい。

42bと、酸化物半導体層144の成膜順以外は、図5に示すトランジスタ180の作製

工程と同様の工程によって作製することが可能である。すなわち、基板100上に、ゲー

ト電極148を形成し、ゲート電極148上にゲート絶縁層146を形成し、ゲート絶縁

層146上に酸化物半導体層144を形成した後、酸化物半導体層144に接するソース

電極142a及びドレイン電極142bを形成し、その後、酸化物半導体層144の少な

くともチャネル形成領域、ソース電極142a及びドレイン電極142bを覆う絶縁層1

50を形成することで、トランジスタ190を形成することができる。酸化物半導体層1

44成膜後には、第1の熱処理及び第2の熱処理を施すのが好ましい。これらの詳細は図

5を参酌することができるため、記載を省略する。

を、対向ターゲット方式を用いたスパッタリング法により形成しているため、ゲート絶縁

層と酸化物半導体層との界面、ゲート絶縁層中、または、酸化物半導体層中の少なくとも

いずれかへのプラズマダメージの混入を防ぎ、界面トラップ、膜中トラップ等の欠陥の発

生を抑制することができる。よって、閾値電圧のシフトが制御された信頼性の高いトラン

ジスタを形成することができる。

を酸化物半導体から除去し、第2の熱処理により、欠損部に酸素を導入することで、酸化

物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性化(

I型化)、又は実質的に真性化している。酸化物半導体膜を高純度化することにより、ト

ランジスタのしきい値電圧値をプラスとすることができ、所謂ノーマリーオフのトランジ

スタを実現できる。

1×1012/cm3未満、さらに望ましくは、1.45×1010/cm3未満)を用

いることで、極めて優れたオフ電流特性のトランジスタを得ることが可能である。また、

閾値電圧のばらつきの少ない、信頼性の高いトランジスタとすることが可能である。

、形成された酸化物半導体層中には、平行平板のスパッタリング装置で成膜した酸化物半

導体層よりも高い濃度で水素(水や水酸基を含む)が含有されていることがあるため、脱

水・脱水素の効果を奏する第1の熱処理を施すことは、効果的である。

いたスパッタリング法により形成することで、ゲート絶縁層または酸化物半導体層を薄膜

化した場合でも被覆性の良い膜を、安定した膜質で成膜することが可能であるため、半導

体装置の微細化を実現することができる。半導体装置を十分に微細化することで、一基板

あたりの半導体装置の取り数が増大し、半導体装置を低コストで製造可能となる。また、

チャネル長の縮小による、動作の高速化、低消費電力化などの効果を得ることもできる。

宜組み合わせて用いることができる。

本実施の形態では、半導体装置の一形態に相当する液晶表示パネルの外観及び断面につい

て、図6を用いて説明する。図6に示す液晶表示パネルは、実施の形態1で示したトラン

ジスタを含む。図6(A)及び図6(C)は、トランジスタ4010、4011、及び液

晶素子4013を、第2の基板4006との間にシール材4005によって封止した、パ

ネルの平面図であり、図6(B)は、図6(A)または図6(C)のM−Nにおける断面

図に相当する。

ようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回

路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査

線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006

とによって、液晶層4008と共に封止されている。また第1の基板4001上のシール

材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶

半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003が実装されている。

ワイヤボンディング方法、或いはTAB方法などを用いることができる。図6(A)は、

COG方法により信号線駆動回路4003を実装する例であり、図6(C)は、TAB方

法により信号線駆動回路4003を実装する例である。

トランジスタを複数有しており、図6(B)では、画素部4002に含まれるトランジス

タ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示してい

る。図6(B)において、トランジスタ4010、4011は、第1のゲート絶縁層40

20a、第2のゲート絶縁層4020bを有する。なお、ゲート絶縁層を単層としても良

い。トランジスタ4010、4011上には絶縁層4041、4042、4021が設け

られている。

ることができる。もちろん、実施の形態1で示したトランジスタ160、170、180

のいずれかを用いてもよい。また、これらを組み合わせて用いることもできる。本実施の

形態において、トランジスタ4010、4011はnチャネル型トランジスタである。

ネル形成領域と重なる位置に導電層4040が設けられている。導電層4040を酸化物

半導体層のチャネル形成領域と重なる位置に設けることによって、トランジスタの信頼性

が向上し、例えばバイアス−熱ストレス試験(BT試験)において、BT試験前後におけ

るトランジスタ4011のしきい値電圧の変化量を低減することができる。また、導電層

4040の電位はトランジスタ4011のゲート電極の電位と同じでもよいし、異なって

いても良く、第2のゲート電極として機能させることもできる。また、導電層4040の

電位がGND、0V、或いはフローティング状態であってもよい。

に接続されている。そして液晶素子4013の対向電極層4031は第2の基板4006

上に形成されている。画素電極層4030と対向電極層4031と液晶層4008とが重

なっている部分が、液晶素子4013に相当する。なお、画素電極層4030、対向電極

層4031はそれぞれ配向膜として機能する絶縁層4032、4033が設けられ、絶縁

層4032、4033を介して液晶層4008を挟持している。

き、ポリエステルフィルム、またはアクリル樹脂フィルムなどのプラスチックや、ガラス

や、セラミックスなどを用いることができる。

画素電極層4030と対向電極層4031との間の距離(セルギャップ)を制御するため

に設けられている。なお球状のスペーサを用いていても良い。また、対向電極層4031

は、トランジスタ4010と同一基板上に設けられる共通電位線と電気的に接続される。

共通接続部を用いて、一対の基板間に配置される導電性粒子を介して対向電極層4031

と共通電位線とを電気的に接続することができる。なお、導電性粒子はシール材4005

に含有させる。

するため、図6に示す電極配置と異なる配置とする。例えば、同一絶縁層上に画素電極層

と共通電極層とを並べて配置し、液晶層に横電界を印加する。ブルー相は液晶相の一つで

あり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直

前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善

するために5重量%以上のカイラル剤を混合させた液晶組成物を用いて液晶層4008に

用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が1msec

以下と短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。

子に用いる電極層という順に設ける例を示すが、偏光板は基板の内側に設けてもよい。ま

た、偏光板と着色層の積層構造も本実施の形態に限定されず、偏光板及び着色層の材料や

作製工程条件によって適宜設定すればよい。また、表示部以外にブラックマトリクスとし

て機能する遮光膜を設けてもよい。

されている。絶縁層4041は実施の形態1で示した絶縁層150と同様な材料及び方法

で形成すればよい。ここでは、絶縁層4041として、図2または図3の成膜装置を用い

たスパッタ法により酸化珪素膜を形成する。また、絶縁層4041上に接して保護絶縁層

4042を形成する。また、保護絶縁層4042は実施の形態1で示した保護絶縁層と同

様な材料及び方法で形成すればよい。また、トランジスタの表面凹凸を低減するために、

保護絶縁層4042を平坦化絶縁膜として機能する絶縁層4021で覆う構成となってい

る。

ミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機

材料を用いることができる。また上記有機材料の他に、低誘電率材料(low−k材料)

、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いる

ことができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層

4021を形成してもよい。

、スピンコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン

印刷、オフセット印刷等)、ドクターナイフ、ロールコーター、カーテンコーター、ナイ

フコーター等を用いることができる。絶縁層4021の焼成工程と半導体層の加熱処理を

兼ねることで効率よく半導体装置を作製することが可能となる。

、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、

酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、酸化インジウム酸化亜鉛、

酸化シリコンを含むインジウム錫酸化物などの透光性を有する透光性の導電性材料を用い

ることができる。

002に与えられる各種信号及び電位は、FPC4018から供給されている。

ら形成され、端子電極4016は、トランジスタ4010、4011のソース電極及びド

レイン電極と同じ導電膜で形成されている。

て電気的に接続されている。

している例を示しているがこの構成に限定されない。走査線駆動回路を別途形成して実装

しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実

装しても良い。

性の高いトランジスタを用いて構成されているため、良好な品質を有する液晶表示パネル

とすることが可能である。

宜組み合わせて用いることができる。

本実施の形態では、半導体装置の一形態として電子ペーパーの例を示す。

て電子インクを駆動させる電子ペーパーに用いてもよい。電子ペーパーは、電気泳動表示

装置(電気泳動ディスプレイ)とも呼ばれており、紙と同じ読みやすさ、他の表示装置に

比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒または溶質に

複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロ

カプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示す

るものである。なお、第1の粒子または第2の粒子は染料を含み、電界がない場合におい

て移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの(無色を

含む)とする。

いわゆる誘電泳動的効果を利用したディスプレイである。

の電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また

、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

ロカプセルを複数配置すればアクティブマトリクス型の表示装置が完成し、マイクロカプ

セルに電界を印加すれば表示を行うことができる。例えば、実施の形態1のトランジスタ

によって得られるアクティブマトリクス基板を用いることができる。

半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレク

トロクロミック材料、磁気泳動材料から選ばれた一種の材料、またはこれらの複合材料を

用いればよい。

置に用いられるトランジスタ581としては、実施の形態1で示すトランジスタと同様に

作製でき、電気的特性が良好で、信頼性の高いトランジスタである。

ボール表示方式とは、白と黒に塗り分けられた球形粒子を表示素子に用いる電極層である

第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を

生じさせての球形粒子の向きを制御することにより、表示を行う方法である。

態1で示したトランジスタ190を用いることができる。もちろん、実施の形態1で示し

たトランジスタ160、170、180のいずれかを用いてもよい。また、これらを組み

合わせて用いることもできる。トランジスタ581は、第1のゲート絶縁層582a、第

2のゲート絶縁層582bの積層上に接して酸化物半導体層を有し、該酸化物半導体層と

接する絶縁層583に覆われている。なお、第1のゲート絶縁層582aはハフニウムを

含む絶縁膜とするのが好ましく、第2のゲート絶縁層582bよりも比誘電率の高い膜を

用いているのが好ましい。ただし、ゲート絶縁層を単層で形成しても良い。

る開口で、第1の電極層587と接して電気的に接続している。第1の電極層587と第

2の電極層588との間には黒色領域590a及び白色領域590bを有し、周りに液体

で満たされている球形粒子589が一対の基板580、596の間に設けられており、球

形粒子589の周囲は樹脂等の充填材595で充填されている。

る。第2の電極層588は、トランジスタ581と同一基板上に設けられる共通電位線と

電気的に接続される。共通接続部を用いて、一対の基板580、596間に配置される導

電性粒子を介して第2の電極層588と共通電位線とを電気的に接続することができる。

と、正に帯電した白い微粒子と負に帯電した黒い微粒子とを封入した直径10μm〜20

0μm程度のマイクロカプセルを用いる。第1の電極層と第2の電極層との間に設けられ

るマイクロカプセルは、第1の電極層と第2の電極層によって、電場が与えられると、白

い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この

原理を応用した表示素子が電気泳動表示素子であり、一般的に電子ペーパーとよばれてい

る。電気泳動表示素子は、液晶素子に比べて反射率が高いため、補助ライトは不要であり

、また消費電力が小さく、薄暗い場所でも表示部を認識することが可能である。また、表

示部に電源が供給されない場合であっても、一度表示した像を保持することが可能である

ため、電波発信源から表示機能付き半導体装置(単に表示装置、又は表示装置を具備する

半導体装置ともいう)を遠ざけた場合であっても、表示された像を保存しておくことが可

能となる。

とができる。本実施の形態で示す電子ペーパーは、実施の形態1で示した電気的特性が良

好で、信頼性の高いトランジスタを用いて構成されているため、良好な品質を有する電子

ペーパーとすることが可能である。

である。

本実施の形態では、半導体装置の一例として、記憶媒体(メモリ素子)を示す。本実施の

形態では、実施の形態1で示す酸化物半導体を用いたトランジスタと、酸化物半導体以外

の材料を用いたトランジスタとを同一基板上に形成する。

B)には、半導体装置の平面を、それぞれ示す。ここで、図8(A)は、図8(B)のC

1−C2およびD1−D2における断面に相当する。また、図8(C)には、上記半導体

装置をメモリ素子として用いる場合の回路図の一例を示す。図8(A)および図8(B)

に示される半導体装置は、下部に第1の半導体材料を用いたトランジスタ140を有し、

上部に第2の半導体材料を用いたトランジスタ162を有する。本実施の形態では、第1

の半導体材料を酸化物半導体以外の半導体材料とし、第2の半導体材料を酸化物半導体と

する。酸化物半導体以外の半導体材料としては、例えば、シリコン、ゲルマニウム、シリ

コンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半

導体を用いるのが好ましい。他に、有機半導体材料などを用いてもよい。このような半導

体材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いた

トランジスタは、その特性により長時間の電荷保持を可能とする。

00に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設け

られた不純物領域120と、不純物領域120に接する金属化合物領域124と、チャネ

ル形成領域116上に設けられたゲート絶縁層108と、ゲート絶縁層108上に設けら

れたゲート電極110と、を有する。

晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用す

ることができる。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体層が設け

られた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料か

らなる半導体層が設けられた構成の基板も含む。つまり、「SOI基板」が有する半導体

層は、シリコン半導体層に限定されない。また、SOI基板には、ガラス基板などの絶縁

基板上に絶縁層を介して半導体層が設けられた構成のものが含まれるものとする。

り、トランジスタ140を覆うように絶縁層128および絶縁層130が設けられている

。なお、高集積化を実現するためには、図8に示すようにトランジスタ140がサイドウ

ォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ140の特性

を重視する場合には、ゲート電極110の側面にサイドウォール絶縁層を設け、不純物濃

度が異なる領域を含む不純物領域120を設けても良い。

タ140は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを

読み出し用のトランジスタとして用いることで、情報の読み出しを高速に行うことができ

る。

処理として、絶縁層128や絶縁層130にCMP処理を施して、ゲート電極110の上

面を露出させる。ゲート電極110の上面を露出させる処理としては、CMP処理の他に

エッチング処理などを適用することも可能であるが、トランジスタ162の特性を向上さ

せるために、絶縁層128や絶縁層130の表面は可能な限り平坦にしておくことが望ま

しい。

電層を選択的にエッチングして、ソース電極またはドレイン電極142c、ソース電極ま

たはドレイン電極142dを形成する。

いて形成することができる。また、導電層の材料としては、Al、Cr、Cu、Ta、T

i、Mo、Wからから選ばれた元素や、上述した元素を成分とする合金等を用いることが

できる。Mn、Mg、Zr、Be、Nd、Scのいずれか、またはこれらを複数組み合わ

せた材料を用いてもよい。

ン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウ

ム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構

造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。な

お、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有す

るソース電極またはドレイン電極142c、およびソース電極またはドレイン電極142

dへの加工が容易であるというメリットがある。

c、およびソース電極またはドレイン電極142dの下端部の間隔によって決定される。

なお、チャネル長(L)が25nm未満のトランジスタを形成する場合に用いるマスク形

成の露光を行う際には、数nm〜数10nmと波長の短い超紫外線を用いるのが望ましい

。

はドレイン電極142dの上に絶縁層143bを、それぞれ形成する。絶縁層143aお

よび絶縁層143bは、ソース電極またはドレイン電極142cや、ソース電極またはド

レイン電極142dを覆う絶縁層を形成した後、当該絶縁層を選択的にエッチングするこ

とにより形成できる。また、絶縁層143aおよび絶縁層143bは、後に形成されるゲ

ート電極の一部と重畳するように形成する。このような絶縁層を設けることにより、ゲー

ト電極と、ソース電極またはドレイン電極との間の容量を低減することが可能である。

化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。

では、絶縁層143aおよび絶縁層143bを形成するのが好適であるが、当該絶縁層を

設けない構成とすることも可能である。

42dを覆うように酸化物半導体層を形成した後、当該酸化物半導体層を選択的にエッチ

ングして酸化物半導体層144を形成する。

導体層の成膜には、図2または図3に示す対向ターゲット方式のスパッタリング装置を用

いるのが好ましい。

第1の熱処理によって酸化物半導体層中の、過剰な水素(水や水酸基を含む)を除去し、

酸化物半導体層の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる

。第1の熱処理の温度は、例えば、300℃以上550℃未満、または400℃以上50

0℃以下とする。特に、対向ターゲット方式のスパッタリング装置を用いて酸化物半導体

層を形成する場合、形成された酸化物半導体層中には、平行平板のスパッタリング装置で

成膜した酸化物半導体層よりも高い濃度で水素(水や水酸基を含む)が含有されているこ

とがあるため、脱水・脱水素の効果を奏する第1の熱処理を施すことは、効果的である。

450℃、1時間の条件で行うことができる。この間、酸化物半導体層は大気に触れさせ

ず、水や水素の混入が生じないようにする。第1の熱処理によって不純物を低減し、I型

(真性)またはI型に限りなく近い酸化物半導体層を形成することで、極めて優れた特性

のトランジスタを実現することができる。

6は、実施の形態1に示す材料及び形成プロセスを用いる。なお、ゲート絶縁層146の

成膜には、図2または図3に示す対向ターゲット方式のスパッタリング装置を用いるのが

好ましい。

148aを形成し、ソース電極またはドレイン電極142cと重畳する領域に電極148

bを形成する。

処理を行うのが望ましい。熱処理の温度は、200℃以上450℃以下、望ましくは25

0℃以上350℃以下である。例えば、窒素雰囲気下で250℃、1時間の熱処理を行え

ばよい。第2の熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減

することができる。また、ゲート絶縁層146が酸素を含む場合、酸化物半導体層144

に酸素を供給し、該酸化物半導体層144の酸素欠損を補填して、I型(真性)またはI

型に限りなく近い酸化物半導体層を形成することもできる。

第2の熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良い

し、第1の熱処理に第2の熱処理を兼ねさせても良いし、第2の熱処理に第1の熱処理を

兼ねさせても良い。

半導体層144を、その主成分以外の不純物が極力含まれないように高純度化することが

できる。

に、当該導電層を選択的にエッチングすることによって形成することができる。

0および絶縁層152を形成する。絶縁層150および絶縁層152は、スパッタ法やC

VD法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化

シリコン、酸化ハフニウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成

することができる。なお、絶縁層150および絶縁層152の成膜には、図2または図3

に示す対向ターゲット方式のスパッタリング装置を用いるのが好ましい。

イン電極142dにまで達する開口を形成する。当該開口の形成は、マスクなどを用いた

選択的なエッチングにより行われる。

6を形成する。

した後、エッチング処理やCMPといった方法を用いて、上記導電層の一部を除去するこ

とにより形成することができる。

を用いて導電層を形成した後、当該導電層をパターニングすることによって形成される。

また、導電層の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元

素や、上述した元素を成分とする合金等を用いることができる。Mn、Mg、Zr、Be

、Nd、Scのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は

、ソース電極またはドレイン電極142cなどと同様である。

容量素子164が完成する。容量素子164は、ソース電極またはドレイン電極142c

、酸化物半導体層144、ゲート絶縁層146、および電極148b、で構成される。

せることにより、ソース電極またはドレイン電極142cと、電極148bとの間の絶縁

性を十分に確保することができる。もちろん、十分な容量を確保するために、酸化物半導

体層144を有しない構成の容量素子164を採用しても良い。また、絶縁層143aと

同様に形成される絶縁層を有する構成の容量素子164を採用しても良い。さらに、容量

が不要の場合は、容量素子164を設けない構成とすることも可能である。

図8(C)において、トランジスタ162のソース電極またはドレイン電極の一方と、容

量素子164の電極の一方と、トランジスタ140のゲート電極と、は電気的に接続され

ている。また、第1の配線(1st Line:ソース線とも呼ぶ)とトランジスタ14

0のソース電極とは、電気的に接続され、第2の配線(2nd Line:ビット線とも

呼ぶ)とトランジスタ140のドレイン電極とは、電気的に接続されている。また、第3

の配線(3rd Line:第1の信号線とも呼ぶ)とトランジスタ162のソース電極

またはドレイン電極の他方とは、電気的に接続され、第4の配線(4th Line:第

2の信号線とも呼ぶ)と、トランジスタ162のゲート電極とは、電気的に接続されてい

る。そして、第5の配線(5th Line:ワード線とも呼ぶ)と、容量素子164の

電極の他方は電気的に接続されている。

ているため、トランジスタ162をオフ状態とすることで、トランジスタ162のソース

電極またはドレイン電極の一方と、容量素子164の電極の一方と、トランジスタ140

のゲート電極とが電気的に接続されたノード(以下、ノードFG)の電位を極めて長時間

にわたって保持することが可能である。そして、容量素子164を有することにより、ノ

ードFGに与えられた電荷の保持が容易になり、また、保持された情報の読み出しが容易

になる。

ジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これ

により、第3の配線の電位が、ノードFGに供給され、ノードFGに所定量の電荷が蓄積

される。ここでは、異なる二つの電位レベルを与える電荷(以下、ロー(Low)レベル

電荷、ハイ(High)レベル電荷という)のいずれかが与えられるものとする。その後

、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ

162をオフ状態とすることにより、ノードFGが浮遊状態となるため、ノードFGには

所定の電荷が保持されたままの状態となる。以上のように、ノードFGに所定量の電荷を

蓄積及び保持させることで、メモリセルに情報を記憶させることができる。

間にわたって保持される。したがって、リフレッシュ動作が不要となるか、または、リフ

レッシュ動作の頻度を極めて低くすることが可能となり、消費電力を十分に低減すること

ができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持する

ことが可能である。

えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、ノードFGに保持さ

れた電荷量に応じて、トランジスタ140は異なる状態をとる。一般に、トランジスタ1

40をnチャネル型とすると、ノードFGにHighレベル電荷が保持されている場合の

トランジスタ140の見かけのしきい値Vth_Hは、ノードFGにLowレベル電荷が

保持されている場合のトランジスタ140の見かけのしきい値Vth_Lより低くなるた

めである。ここで、見かけのしきい値とは、トランジスタ140を「オン状態」とするた

めに必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位をVth

_HとVth_Lの中間の電位V0とすることにより、ノードFGに保持された電荷を判

別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、

第5の配線の電位がV0(>Vth_H)となれば、トランジスタ140は「オン状態」

となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位がV0(<Vt

h_L)となっても、トランジスタ140は「オフ状態」のままである。このため、第5

の配線の電位を制御して、トランジスタ140のオン状態またはオフ状態を読み出す(第

2の配線の電位を読み出す)ことで、記憶された情報を読み出すことができる。

荷を保持したノードFGに、新たな電位を供給することで、ノードFGに新たな情報に係

る電荷を保持させる。具体的には、第4の配線の電位を、トランジスタ162がオン状態

となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電

位(新たな情報に係る電位)が、ノードFGに供給され、ノードFGに所定量の電荷が蓄

積される。その後、第4の配線の電位をトランジスタ162がオフ状態となる電位にして

、トランジスタ162をオフ状態とすることにより、ノードFGには、新たな情報に係る

電荷が保持された状態となる。すなわち、ノードFGに第1の書き込みによって所定量の

電荷が保持された状態で、第1の書き込みと同様の動作(第2の書き込み)を行うことで

、記憶させた情報を上書きすることが可能である。

も一方を、対向ターゲット方式を用いたスパッタリング法により形成しているため、ゲー

ト絶縁層と酸化物半導体層との界面、ゲート絶縁層中、または、酸化物半導体層中の少な

くともいずれかへのプラズマダメージの混入を防ぎ、界面トラップ、膜中トラップ等の欠

陥の発生を抑制することができる。さらに、高純度化され、真性化された酸化物半導体層

144を用いることで、トランジスタ162のオフ電流を十分に低減することができる。

そして、このようなトランジスタを用いることで、極めて長期にわたり記憶内容を保持す

ることが可能な半導体装置が得られる。

62を重畳させることで、集積度が十分に高められた半導体装置が実現される。

宜組み合わせて用いることができる。

本明細書に開示する半導体装置は、さまざまな電子機器(遊技機も含む)に適用すること

ができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン

受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメ

ラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型

ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられ

る。

の高いトランジスタを搭載した電子機器の例について図9を用いて説明する。

、表示部3003、キーボード3004などによって構成されている。なお、ノート型の

パーソナルコンピュータは、上記実施の形態で示すトランジスタを含んでいる。そのため

、良好な品質を有し、信頼性の高いノート型のパーソナルコンピュータが実現される。

部インターフェイス3025と、操作ボタン3024等が設けられている。また操作用の

付属品としてスタイラス3022がある。なお、携帯情報端末(PDA)は、上記実施の

形態で示すトランジスタを含んでいる。そのため、良好な品質を有し、信頼性の高い携帯

情報端末(PDA)が実現される。

書籍である。図9(C)は、電子書籍の一例を示している。例えば、電子書籍2700は

、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および

筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉

動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可

能となる。

込まれている。表示部2705および表示部2707は、続き画面を表示する構成として

もよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とするこ

とで、例えば右側の表示部(図9(C)では表示部2705)に文章を表示し、左側の表

示部(図9(C)では表示部2707)に画像を表示することができる。

体2701において、電源2721、操作キー2723、スピーカー2725などを備え

ている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面

にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏

面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびU

SBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える

構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成

としてもよい。

電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすること

も可能である。

ている。筐体2801には、表示パネル2802、スピーカー2803、マイクロフォン

2804、ポインティングデバイス2806、カメラ用レンズ2807、外部接続端子2

808などを備えている。また、筐体2801には、携帯型情報端末の充電を行う太陽電

池セル2810、外部メモリスロット2811などを備えている。また、アンテナは筐体

2801内部に内蔵されている。なお、携帯電話は、上記実施の形態で示すトランジスタ

を少なくとも一部品として含んでいる。

いる複数の操作キー2805を点線で示している。なお、太陽電池セル2810で出力さ

れる電圧を各回路に必要な電圧に昇圧するための昇圧回路も実装している。

2802と同一面上にカメラ用レンズ2807を備えているため、テレビ電話が可能であ

る。スピーカー2803及びマイクロフォン2804は音声通話に限らず、テレビ電話、

録音、再生などが可能である。さらに、筐体2800と筐体2801は、スライドし、図

9(D)のように展開している状態から重なり合った状態とすることができ、携帯に適し

た小型化が可能である。

であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部

メモリスロット2811に記録媒体を挿入し、より大量のデータ保存及び移動に対応でき

る。記録媒体として、実施の形態4に示す半導体装置を用いることができる。実施の形態

4によれば、オフ電流を十分に低減することができるトランジスタを用いることで、極め

て長期にわたり記憶内容を保持することが可能な半導体装置が得られる。

よい。

053、操作スイッチ3054、表示部(B)3055、バッテリー3056などによっ

て構成されている。なお、デジタルカメラは、上記実施の形態で示すトランジスタを含ん

でいる。そのため、良好な品質を有し、信頼性の高いデジタルカメラが実現される。

載されている。このため、良好な品質を有する電子機器が実現される。

106 素子分離絶縁層

108 ゲート絶縁層

110 ゲート電極

116 チャネル形成領域

120 不純物領域

124 金属化合物領域

128 絶縁層

130 絶縁層

140 トランジスタ

142a ソース電極

142b ドレイン電極

142c ドレイン電極

142d ドレイン電極

143a 絶縁層

143b 絶縁層

144 酸化物半導体層

146 ゲート絶縁層

148 ゲート電極

148a ゲート電極

148b 電極

150 絶縁層

152 絶縁層

154 電極

156 配線

160 トランジスタ

162 トランジスタ

164 容量素子

170 トランジスタ

180 トランジスタ

190 トランジスタ

200 基板

202 真空容器

204a ターゲット

204b ターゲット

206a 磁界発生手段

206b 磁界発生手段

206c 磁界発生手段

206d 磁界発生手段

208 基板ホルダー

210 電源

212 排気管

214 供給管

216 シャッター

Claims (6)

- 基板上に、対向して配置された一組のターゲットを用いたスパッタリング法により酸化物半導体層を形成し、

前記酸化物半導体層に、前記酸化物半導体層中の水素を低減するための第1の熱処理を行い、

前記酸化物半導体層上にソース電極及びドレイン電極を形成し、

前記酸化物半導体層上、前記ソース電極上、及び前記ドレイン電極上に、ゲート絶縁層を形成し、

前記ゲート絶縁層形成後に、不活性ガス雰囲気下で第2の熱処理を行い、

前記第2の熱処理後に、前記ゲート絶縁層上にゲート電極を形成し、

前記第1の熱処理は、不活性ガス雰囲気での熱処理を行った後、前記不活性ガスを酸素を含むガスに切り替えて熱処理を行い、

前記トランジスタのチャネル長は、10nm以上1000nm以下であるトランジスタの作製方法。 - 基板上に、前記基板を室温とした状態で、対向して配置された一組のターゲットを用いたスパッタリング法により酸化物半導体層を形成し、

前記酸化物半導体層に、前記酸化物半導体層中の水素を低減するための第1の熱処理を行い、

前記酸化物半導体層上にソース電極及びドレイン電極を形成し、

前記酸化物半導体層上、前記ソース電極上、及び前記ドレイン電極−上に、ゲート絶縁層を形成し、

前記ゲート絶縁層形成後に、不活性ガス雰囲気下で第2の熱処理を行い、

前記第2の熱処理後に、前記ゲート絶縁層上にゲート電極を形成し、

前記第1の熱処理は、不活性ガス雰囲気での熱処理を行った後、前記不活性ガスを酸素を含むガスに切り替えて熱処理を行い、

前記トランジスタのチャネル長は、10nm以上1000nm以下であるトランジスタの作製方法。 - 請求項2において、

前記室温は、25℃±10℃であるトランジスタの作製方法。 - 請求項1乃至請求項3のいずれか一において、

前記酸化物半導体層は、インジウムと亜鉛と元素Mとを有し、

前記元素Mは、ガリウム、スズ、又はアルミニウムであるトランジスタの作製方法。 - 請求項1乃至請求項4のいずれか一において、

前記酸化物半導体層は非晶質であるトランジスタの作製方法。 - 請求項1乃至請求項5のいずれか一において、

前記酸化物半導体層のキャリア濃度は、1×1012/cm3であるトランジスタの作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015004136A JP6082037B2 (ja) | 2010-02-12 | 2015-01-13 | トランジスタの作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010028598 | 2010-02-12 | ||

| JP2010028598 | 2010-02-12 | ||

| JP2015004136A JP6082037B2 (ja) | 2010-02-12 | 2015-01-13 | トランジスタの作製方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011027296A Division JP5723172B2 (ja) | 2010-02-12 | 2011-02-10 | 半導体装置の作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015111705A JP2015111705A (ja) | 2015-06-18 |

| JP6082037B2 true JP6082037B2 (ja) | 2017-02-15 |

Family

ID=44369011

Family Applications (9)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011027296A Expired - Fee Related JP5723172B2 (ja) | 2010-02-12 | 2011-02-10 | 半導体装置の作製方法 |

| JP2015004149A Withdrawn JP2015128162A (ja) | 2010-02-12 | 2015-01-13 | 成膜方法 |

| JP2015004131A Expired - Fee Related JP6149049B2 (ja) | 2010-02-12 | 2015-01-13 | 半導体装置の作製方法 |

| JP2015004138A Withdrawn JP2015119190A (ja) | 2010-02-12 | 2015-01-13 | 半導体装置の作製方法 |

| JP2015004136A Expired - Fee Related JP6082037B2 (ja) | 2010-02-12 | 2015-01-13 | トランジスタの作製方法 |

| JP2015004130A Withdrawn JP2015122512A (ja) | 2010-02-12 | 2015-01-13 | 半導体装置 |

| JP2017100504A Expired - Fee Related JP6420868B2 (ja) | 2010-02-12 | 2017-05-22 | 半導体装置の作製方法 |

| JP2018193068A Withdrawn JP2019033276A (ja) | 2010-02-12 | 2018-10-12 | 半導体装置の作製方法 |

| JP2020104371A Withdrawn JP2020167431A (ja) | 2010-02-12 | 2020-06-17 | 半導体装置の作製方法 |

Family Applications Before (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011027296A Expired - Fee Related JP5723172B2 (ja) | 2010-02-12 | 2011-02-10 | 半導体装置の作製方法 |

| JP2015004149A Withdrawn JP2015128162A (ja) | 2010-02-12 | 2015-01-13 | 成膜方法 |

| JP2015004131A Expired - Fee Related JP6149049B2 (ja) | 2010-02-12 | 2015-01-13 | 半導体装置の作製方法 |

| JP2015004138A Withdrawn JP2015119190A (ja) | 2010-02-12 | 2015-01-13 | 半導体装置の作製方法 |

Family Applications After (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015004130A Withdrawn JP2015122512A (ja) | 2010-02-12 | 2015-01-13 | 半導体装置 |

| JP2017100504A Expired - Fee Related JP6420868B2 (ja) | 2010-02-12 | 2017-05-22 | 半導体装置の作製方法 |

| JP2018193068A Withdrawn JP2019033276A (ja) | 2010-02-12 | 2018-10-12 | 半導体装置の作製方法 |

| JP2020104371A Withdrawn JP2020167431A (ja) | 2010-02-12 | 2020-06-17 | 半導体装置の作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8617920B2 (ja) |

| JP (9) | JP5723172B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9722212B2 (en) | 2011-02-14 | 2017-08-01 | Semiconductor Energy Laboratory Co., Ltd. | Lighting device, light-emitting device, and manufacturing method and manufacturing apparatus thereof |

| KR102124557B1 (ko) | 2011-06-08 | 2020-06-18 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 스퍼터링 타겟, 스퍼터링 타겟의 제조 방법 및 박막의 형성 방법 |

| US20130087784A1 (en) * | 2011-10-05 | 2013-04-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9117916B2 (en) | 2011-10-13 | 2015-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising oxide semiconductor film |

| KR20130040706A (ko) * | 2011-10-14 | 2013-04-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 반도체 장치의 제작 방법 |

| KR20130046357A (ko) * | 2011-10-27 | 2013-05-07 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP2013149953A (ja) * | 2011-12-20 | 2013-08-01 | Semiconductor Energy Lab Co Ltd | 半導体装置及び半導体装置の作製方法 |

| JP6175740B2 (ja) * | 2012-03-30 | 2017-08-09 | 株式会社Joled | 薄膜トランジスタおよびその製造方法並びに表示装置および電子機器 |

| US9885108B2 (en) | 2012-08-07 | 2018-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Method for forming sputtering target |

| JP6141777B2 (ja) | 2013-02-28 | 2017-06-07 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| CN117690933A (zh) | 2013-12-27 | 2024-03-12 | 株式会社半导体能源研究所 | 发光装置 |

| KR102426711B1 (ko) * | 2015-11-18 | 2022-07-29 | 삼성디스플레이 주식회사 | 플렉서블 디스플레이 장치 |

| US10475869B2 (en) * | 2016-08-23 | 2019-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Display device including display element and transistor |

| US10002762B2 (en) * | 2016-09-09 | 2018-06-19 | International Business Machines Corporation | Multi-angled deposition and masking for custom spacer trim and selected spacer removal |

| JP7233964B2 (ja) | 2019-02-26 | 2023-03-07 | 三菱重工業株式会社 | 運転指標提示装置、運転指標提示方法、およびプログラム |

Family Cites Families (130)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02255504A (ja) * | 1989-03-30 | 1990-10-16 | Nippon Steel Corp | 酸化物超電導薄膜の製造方法 |

| JPH04317408A (ja) * | 1991-04-01 | 1992-11-09 | Semiconductor Energy Lab Co Ltd | 酸化物超伝導材料 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP2003273133A (ja) * | 2002-03-15 | 2003-09-26 | Sanyo Electric Co Ltd | 酸化物半導体層およびその形成方法ならびに半導体装置 |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) * | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4135540B2 (ja) * | 2003-03-25 | 2008-08-20 | 株式会社ジェイテクト | 電動パワーステアリング装置 |

| JP2004335572A (ja) * | 2003-05-01 | 2004-11-25 | Seiko Epson Corp | 塗布装置、薄膜形成装置、半導体装置の製造方法、電気光学装置、並びに電子機器 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| JP2005179716A (ja) * | 2003-12-17 | 2005-07-07 | Sony Corp | スパッタリング装置 |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| KR20070116889A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 박막의 기상성막방법 |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP2006005515A (ja) * | 2004-06-16 | 2006-01-05 | Altia Hashimoto Co Ltd | 電波等の透過装置 |

| JP4660124B2 (ja) * | 2004-06-17 | 2011-03-30 | カシオ計算機株式会社 | 薄膜トランジスタの製造方法 |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| AU2005302964B2 (en) | 2004-11-10 | 2010-11-04 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| JP2006144053A (ja) * | 2004-11-17 | 2006-06-08 | Bridgestone Corp | NドープZnO膜の成膜方法。 |

| JP2006188733A (ja) * | 2005-01-06 | 2006-07-20 | Osaka Vacuum Ltd | 対向ターゲット式スパッタ装置及び対向ターゲット式スパッタ方法 |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP4560502B2 (ja) * | 2005-09-06 | 2010-10-13 | キヤノン株式会社 | 電界効果型トランジスタ |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP5064747B2 (ja) | 2005-09-29 | 2012-10-31 | 株式会社半導体エネルギー研究所 | 半導体装置、電気泳動表示装置、表示モジュール、電子機器、及び半導体装置の作製方法 |

| JP5078246B2 (ja) | 2005-09-29 | 2012-11-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の作製方法 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101397571B1 (ko) | 2005-11-15 | 2014-05-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제조방법 |

| JP5395994B2 (ja) * | 2005-11-18 | 2014-01-22 | 出光興産株式会社 | 半導体薄膜、及びその製造方法、並びに薄膜トランジスタ |

| WO2007058248A1 (ja) | 2005-11-18 | 2007-05-24 | Idemitsu Kosan Co., Ltd. | 半導体薄膜、及びその製造方法、並びに薄膜トランジスタ |

| US7998372B2 (en) * | 2005-11-18 | 2011-08-16 | Idemitsu Kosan Co., Ltd. | Semiconductor thin film, method for manufacturing the same, thin film transistor, and active-matrix-driven display panel |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| JP5110803B2 (ja) * | 2006-03-17 | 2012-12-26 | キヤノン株式会社 | 酸化物膜をチャネルに用いた電界効果型トランジスタ及びその製造方法 |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP2007311404A (ja) * | 2006-05-16 | 2007-11-29 | Fuji Electric Holdings Co Ltd | 薄膜トランジスタの製造方法 |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP5007792B2 (ja) * | 2006-08-24 | 2012-08-22 | 株式会社ブリヂストン | p型In−Ga−Zn−O膜の成膜方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| JP5105842B2 (ja) * | 2006-12-05 | 2012-12-26 | キヤノン株式会社 | 酸化物半導体を用いた表示装置及びその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| TWI478347B (zh) * | 2007-02-09 | 2015-03-21 | 出光興產股份有限公司 | A thin film transistor, a thin film transistor substrate, and an image display device, and an image display device, and a semiconductor device |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| JP5466939B2 (ja) * | 2007-03-23 | 2014-04-09 | 出光興産株式会社 | 半導体デバイス、多結晶半導体薄膜、多結晶半導体薄膜の製造方法、電界効果型トランジスタ、及び、電界効果型トランジスタの製造方法 |

| JP5465825B2 (ja) * | 2007-03-26 | 2014-04-09 | 出光興産株式会社 | 半導体装置、半導体装置の製造方法及び表示装置 |

| JP5244331B2 (ja) * | 2007-03-26 | 2013-07-24 | 出光興産株式会社 | 非晶質酸化物半導体薄膜、その製造方法、薄膜トランジスタの製造方法、電界効果型トランジスタ、発光装置、表示装置及びスパッタリングターゲット |

| JP5372337B2 (ja) * | 2007-03-27 | 2013-12-18 | 住友化学株式会社 | 有機薄膜トランジスタ基板及びその製造方法、並びに、画像表示パネル及びその製造方法 |

| JP5197058B2 (ja) * | 2007-04-09 | 2013-05-15 | キヤノン株式会社 | 発光装置とその作製方法 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP2009030133A (ja) * | 2007-07-30 | 2009-02-12 | Panasonic Corp | 薄膜形成装置並びに薄膜形成方法 |

| TWI453915B (zh) * | 2007-09-10 | 2014-09-21 | Idemitsu Kosan Co | Thin film transistor |

| JP2009099847A (ja) * | 2007-10-18 | 2009-05-07 | Canon Inc | 薄膜トランジスタとその製造方法及び表示装置 |

| JP5213422B2 (ja) | 2007-12-04 | 2013-06-19 | キヤノン株式会社 | 絶縁層を有する酸化物半導体素子およびそれを用いた表示装置 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| WO2009093625A1 (ja) * | 2008-01-23 | 2009-07-30 | Idemitsu Kosan Co., Ltd. | 電界効果型トランジスタ及びその製造方法、それを用いた表示装置、並びに半導体装置 |

| JP5088792B2 (ja) * | 2008-04-02 | 2012-12-05 | 富士フイルム株式会社 | Zn含有複合酸化物膜の成膜方法 |

| JP5202094B2 (ja) * | 2008-05-12 | 2013-06-05 | キヤノン株式会社 | 半導体装置 |

| JP5555848B2 (ja) * | 2008-05-15 | 2014-07-23 | 国立大学法人山口大学 | 薄膜作製用スパッタ装置及び薄膜作製方法 |

| JP5510767B2 (ja) * | 2008-06-19 | 2014-06-04 | 出光興産株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5584960B2 (ja) * | 2008-07-03 | 2014-09-10 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| JP5608347B2 (ja) * | 2008-08-08 | 2014-10-15 | 株式会社半導体エネルギー研究所 | 半導体装置及び半導体装置の作製方法 |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

| JP5564331B2 (ja) * | 2009-05-29 | 2014-07-30 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR20130008037A (ko) * | 2010-03-05 | 2013-01-21 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 제작하는 방법 |

-

2011

- 2011-02-08 US US13/022,865 patent/US8617920B2/en not_active Expired - Fee Related

- 2011-02-10 JP JP2011027296A patent/JP5723172B2/ja not_active Expired - Fee Related

-

2015

- 2015-01-13 JP JP2015004149A patent/JP2015128162A/ja not_active Withdrawn

- 2015-01-13 JP JP2015004131A patent/JP6149049B2/ja not_active Expired - Fee Related

- 2015-01-13 JP JP2015004138A patent/JP2015119190A/ja not_active Withdrawn

- 2015-01-13 JP JP2015004136A patent/JP6082037B2/ja not_active Expired - Fee Related

- 2015-01-13 JP JP2015004130A patent/JP2015122512A/ja not_active Withdrawn

-

2017

- 2017-05-22 JP JP2017100504A patent/JP6420868B2/ja not_active Expired - Fee Related

-

2018

- 2018-10-12 JP JP2018193068A patent/JP2019033276A/ja not_active Withdrawn

-

2020

- 2020-06-17 JP JP2020104371A patent/JP2020167431A/ja not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| US20110198594A1 (en) | 2011-08-18 |

| JP2019033276A (ja) | 2019-02-28 |

| JP2015119190A (ja) | 2015-06-25 |

| JP6420868B2 (ja) | 2018-11-07 |

| JP2011187952A (ja) | 2011-09-22 |

| JP5723172B2 (ja) | 2015-05-27 |

| JP2015111705A (ja) | 2015-06-18 |

| JP2020167431A (ja) | 2020-10-08 |

| JP2015119189A (ja) | 2015-06-25 |

| JP2015128162A (ja) | 2015-07-09 |

| JP2017152740A (ja) | 2017-08-31 |

| JP6149049B2 (ja) | 2017-06-14 |

| US8617920B2 (en) | 2013-12-31 |

| JP2015122512A (ja) | 2015-07-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6420868B2 (ja) | 半導体装置の作製方法 | |

| JP7592128B2 (ja) | 半導体装置 | |

| JP6957668B2 (ja) | 半導体装置の作製方法 | |

| JP5844583B2 (ja) | 半導体装置の作製方法、及び、半導体装置 | |

| TW201207955A (en) | Deposition method and method for manufacturing semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160223 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160705 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170117 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170119 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6082037 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |