JP5983999B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5983999B2 JP5983999B2 JP2012147538A JP2012147538A JP5983999B2 JP 5983999 B2 JP5983999 B2 JP 5983999B2 JP 2012147538 A JP2012147538 A JP 2012147538A JP 2012147538 A JP2012147538 A JP 2012147538A JP 5983999 B2 JP5983999 B2 JP 5983999B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating film

- opening

- forming

- metal pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 69

- 238000004519 manufacturing process Methods 0.000 title claims description 16

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 144

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 claims description 76

- 239000010931 gold Substances 0.000 claims description 57

- 238000000034 method Methods 0.000 claims description 52

- 229910052751 metal Inorganic materials 0.000 claims description 49

- 239000002184 metal Substances 0.000 claims description 49

- 150000004767 nitrides Chemical class 0.000 claims description 39

- 238000007772 electroless plating Methods 0.000 claims description 23

- 230000004888 barrier function Effects 0.000 claims description 20

- 238000001771 vacuum deposition Methods 0.000 claims description 17

- 229910052759 nickel Inorganic materials 0.000 claims description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 claims description 5

- 239000010949 copper Substances 0.000 claims description 3

- 229910052737 gold Inorganic materials 0.000 claims description 3

- 229910052763 palladium Inorganic materials 0.000 claims description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 2

- 229910052802 copper Inorganic materials 0.000 claims description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims description 2

- 239000000463 material Substances 0.000 claims description 2

- 229910052697 platinum Inorganic materials 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 337

- 239000000758 substrate Substances 0.000 description 17

- 230000004048 modification Effects 0.000 description 9

- 238000012986 modification Methods 0.000 description 9

- 230000008569 process Effects 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- 238000009713 electroplating Methods 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 229910002601 GaN Inorganic materials 0.000 description 7

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical group [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 7

- 238000009792 diffusion process Methods 0.000 description 7

- 238000007747 plating Methods 0.000 description 7

- 238000000151 deposition Methods 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical group Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 238000007738 vacuum evaporation Methods 0.000 description 3

- 238000001994 activation Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000006073 displacement reaction Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- RNQKDQAVIXDKAG-UHFFFAOYSA-N aluminum gallium Chemical compound [Al].[Ga] RNQKDQAVIXDKAG-UHFFFAOYSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005868 electrolysis reaction Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7786—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT

- H01L29/7787—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT with wide bandgap charge-carrier supplying layer, e.g. direct single heterostructure MODFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/201—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys

- H01L29/205—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys in different semiconductor regions, e.g. heterojunctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/47—Schottky barrier electrodes

- H01L29/475—Schottky barrier electrodes on AIII-BV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66446—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET]

- H01L29/66462—Unipolar field-effect transistors with an active layer made of a group 13/15 material, e.g. group 13/15 velocity modulation transistor [VMT], group 13/15 negative resistance FET [NERFET] with a heterojunction interface channel or gate, e.g. HFET, HIGFET, SISFET, HJFET, HEMT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28575—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising AIIIBV compounds

- H01L21/28587—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising AIIIBV compounds characterised by the sectional shape, e.g. T, inverted T

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/80—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier

- H01L29/812—Field effect transistors with field effect produced by a PN or other rectifying junction gate, i.e. potential-jump barrier with a Schottky gate

Description

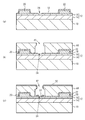

12 窒化物半導体層

14 チャネル層

16 電子供給層

18 第1絶縁膜

20 ソース電極

22 ドレイン電極

24 開口

26、50 ゲート電極

28、52 Ni層

30、54 Pd層

32、56 Au層

34 第2絶縁膜

36 ソース配線

38 ドレイン配線

40、80 フィールドプレート

42 第1開口

44 第1レジスト層

46 第2開口

48 第2レジスト層

82 ソースウォール

Claims (7)

- 窒化物半導体層上に、上面および外側面を有し、ニッケルを含有する金属パターンを形成する工程と、

前記金属パターンの前記上面および前記外側面を含む露出面に対して無電解めっきによってバリア層を形成し、前記金属パターンの前記上面および前記外側面を前記バリア層で被覆する工程と、

前記バリア層上に、無電解めっきによって導電層を形成する工程と、

前記窒化物半導体層上に、前記導電層を覆う絶縁膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。 - 前記窒化物半導体層上に、開口を有する他の絶縁膜を形成する工程を有し、

前記金属パターンは、前記他の絶縁膜および前記開口に接して形成され、

前記金属パターンの前記外側面に形成された前記バリア層と前記窒化物半導体層との間は、前記他の絶縁膜によって隔離されてなることを特徴とする請求項1記載の半導体装置の製造方法。 - 前記バリア層の形成は、前記金属パターンよりも大きい幅を有する開口が前記金属パターンに対応して形成されたマスクを設ける工程と、前記無電解めっきによって、前記マスクの開口内に前記バリア層を構成する材料を充填して成長させる工程と、によりなされることを特徴とする請求項1または2記載の半導体装置の製造方法。

- 前記導電層が、前記マスクの開口内を充填して形成されることを特徴とする請求項3記載の半導体装置の製造方法。

- 前記絶縁膜は、前記バリア層および前記導電層の段差の形状を反映した段差を有し、

前記絶縁膜の前記段差の位置に金属層を形成する工程を有することを特徴とする請求項1から4のいずれか一項記載の半導体装置の製造方法。 - 前記金属パターンを形成する工程は、前記窒化物半導体層上に、開口を有するマスクを形成する工程と、前記マスクを用いて前記金属パターンを真空蒸着法およびリフトオフ法により形成する工程と、を含むことを特徴とする請求項1から5のいずれか一項記載の半導体装置の製造方法。

- 前記金属パターンはニッケル層を含み、前記バリア層はパラジウム層またはプラチナ層を含み、前記導電層は金層または銅層を含むことを特徴とする請求項1から6のいずれか一項記載の半導体装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012147538A JP5983999B2 (ja) | 2012-06-29 | 2012-06-29 | 半導体装置の製造方法 |

| US13/930,904 US9412829B2 (en) | 2012-06-29 | 2013-06-28 | Method for fabricating semiconductor device and semiconductor device |

| US15/204,199 US9653592B2 (en) | 2012-06-29 | 2016-07-07 | Method for fabricating semiconductor device and semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012147538A JP5983999B2 (ja) | 2012-06-29 | 2012-06-29 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014011350A JP2014011350A (ja) | 2014-01-20 |

| JP2014011350A5 JP2014011350A5 (ja) | 2015-05-21 |

| JP5983999B2 true JP5983999B2 (ja) | 2016-09-06 |

Family

ID=49777263

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012147538A Active JP5983999B2 (ja) | 2012-06-29 | 2012-06-29 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9412829B2 (ja) |

| JP (1) | JP5983999B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9178016B2 (en) * | 2013-03-01 | 2015-11-03 | Infineon Technologies Austria Ag | Charge protection for III-nitride devices |

| JP2015204335A (ja) * | 2014-04-11 | 2015-11-16 | 豊田合成株式会社 | 半導体装置および半導体装置の製造方法 |

| JP6179445B2 (ja) * | 2014-04-11 | 2017-08-16 | 豊田合成株式会社 | 縦型ショットキーバリアダイオード、縦型ショットキーバリアダイオードの製造方法 |

| EP2942815B1 (en) * | 2014-05-08 | 2020-11-18 | Nexperia B.V. | Semiconductor device and manufacturing method |

| CN104332498B (zh) * | 2014-09-01 | 2018-01-05 | 苏州捷芯威半导体有限公司 | 一种斜场板功率器件及斜场板功率器件的制备方法 |

| JP6292104B2 (ja) * | 2014-11-17 | 2018-03-14 | 三菱電機株式会社 | 窒化物半導体装置の製造方法 |

| JP2017107942A (ja) * | 2015-12-08 | 2017-06-15 | 株式会社東芝 | 半導体装置 |

| WO2018188649A1 (zh) * | 2017-04-14 | 2018-10-18 | 苏州能讯高能半导体有限公司 | 半导体器件及其制造方法 |

| JP6344531B1 (ja) * | 2017-06-07 | 2018-06-20 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JP6997002B2 (ja) * | 2018-02-19 | 2022-01-17 | 住友電気工業株式会社 | 半導体装置及びその製造方法 |

| JP7047615B2 (ja) * | 2018-06-13 | 2022-04-05 | 住友電工デバイス・イノベーション株式会社 | 半導体デバイスの製造方法 |

| CN109449211B (zh) * | 2018-11-01 | 2022-06-07 | 合肥鑫晟光电科技有限公司 | 薄膜晶体管及其制作方法、阵列基板及其制作方法 |

| US11955522B2 (en) * | 2020-02-13 | 2024-04-09 | Vanguard International Semiconductor Corporation | Semiconductor structure and method of forming the same |

| JP7464152B2 (ja) | 2021-01-27 | 2024-04-09 | 三菱電機株式会社 | 半導体装置及びその製造方法 |

| JP2022145319A (ja) * | 2021-03-19 | 2022-10-04 | 株式会社東芝 | 半導体装置 |

| CN113725283A (zh) * | 2021-11-04 | 2021-11-30 | 深圳市时代速信科技有限公司 | 半导体器件及其制备方法 |

| CN113793867B (zh) * | 2021-11-16 | 2022-03-01 | 深圳市时代速信科技有限公司 | 一种电极结构及其制作方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5014018A (en) * | 1987-10-06 | 1991-05-07 | Stanford University | Nonlinear transmission line for generation of picosecond electrical transients |

| JP2643812B2 (ja) * | 1993-12-24 | 1997-08-20 | 日本電気株式会社 | 電界効果型トランジスタのゲート電極形成方法 |

| JPH0897234A (ja) * | 1994-09-22 | 1996-04-12 | Mitsubishi Electric Corp | 半導体装置の電極,及びその製造方法 |

| JPH11121471A (ja) * | 1997-10-21 | 1999-04-30 | Nec Corp | 半導体装置及びその製造方法 |

| JP2003179057A (ja) * | 2001-12-12 | 2003-06-27 | Sony Corp | 半導体装置及びその製造方法 |

| JP2003273129A (ja) * | 2002-03-14 | 2003-09-26 | Fujitsu Quantum Devices Ltd | 半導体装置及びその製造方法 |

| JP2006261252A (ja) | 2005-03-15 | 2006-09-28 | Eudyna Devices Inc | 半導体装置及びその製造方法 |

| US8212290B2 (en) * | 2007-03-23 | 2012-07-03 | Cree, Inc. | High temperature performance capable gallium nitride transistor |

| US7935620B2 (en) * | 2007-12-05 | 2011-05-03 | Freescale Semiconductor, Inc. | Method for forming semiconductor devices with low leakage Schottky contacts |

| JP2011238805A (ja) * | 2010-05-11 | 2011-11-24 | Nec Corp | 電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置 |

| US20120156843A1 (en) * | 2010-12-17 | 2012-06-21 | Green Bruce M | Dielectric layer for gallium nitride transistor |

-

2012

- 2012-06-29 JP JP2012147538A patent/JP5983999B2/ja active Active

-

2013

- 2013-06-28 US US13/930,904 patent/US9412829B2/en active Active

-

2016

- 2016-07-07 US US15/204,199 patent/US9653592B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20140001640A1 (en) | 2014-01-02 |

| US9412829B2 (en) | 2016-08-09 |

| US20160315181A1 (en) | 2016-10-27 |

| JP2014011350A (ja) | 2014-01-20 |

| US9653592B2 (en) | 2017-05-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5983999B2 (ja) | 半導体装置の製造方法 | |

| JP6335444B2 (ja) | 再成長構造を用いたiii族窒化物トランジスタ | |

| US11222969B2 (en) | Normally-off transistor with reduced on-state resistance and manufacturing method | |

| TWI431770B (zh) | 半導體裝置及製造其之方法 | |

| TWI512993B (zh) | 電晶體與其形成方法與半導體元件 | |

| US11316038B2 (en) | HEMT transistor with adjusted gate-source distance, and manufacturing method thereof | |

| JP2012231109A (ja) | 窒化物半導体素子及びその製造方法 | |

| JP2011155221A (ja) | 半導体装置およびその製造方法 | |

| US11335797B2 (en) | Semiconductor devices and methods for fabricating the same | |

| US9564503B2 (en) | Semiconductor device and method of manufacturing semiconductor device | |

| JP2012069978A (ja) | 化合物半導体装置 | |

| TW201933490A (zh) | 半導體裝置及其製造方法 | |

| JP5504660B2 (ja) | 化合物半導体装置及びその製造方法 | |

| WO2023141749A1 (en) | GaN-BASED SEMICONDUCTOR DEVICE WITH REDUCED LEAKAGE CURRENT AND METHOD FOR MANUFACTURING THE SAME | |

| JP6166508B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2019047055A (ja) | トランジスタ | |

| KR20150030283A (ko) | 전력 반도체 소자 | |

| US10903350B2 (en) | Semiconductor devices and methods for forming the same | |

| US20100117186A1 (en) | Semiconductor device and method of producing the same | |

| US20240047554A1 (en) | Semiconductor device and manufacturing method thereof | |

| CN117981087A (zh) | 降低漏电流的氮化镓半导体装置及其制造方法 | |

| JP2013211484A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150330 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150330 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160315 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160705 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160720 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5983999 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |