JP5908030B2 - 貫通電極を有する半導体パッケージ及びその製造方法 - Google Patents

貫通電極を有する半導体パッケージ及びその製造方法 Download PDFInfo

- Publication number

- JP5908030B2 JP5908030B2 JP2014125069A JP2014125069A JP5908030B2 JP 5908030 B2 JP5908030 B2 JP 5908030B2 JP 2014125069 A JP2014125069 A JP 2014125069A JP 2014125069 A JP2014125069 A JP 2014125069A JP 5908030 B2 JP5908030 B2 JP 5908030B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- mold layer

- chip

- manufacturing

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/01—Manufacture or treatment

- H10W74/014—Manufacture or treatment using batch processing

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/7402—Wafer tapes, e.g. grinding or dicing support tapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/111—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed

- H10W74/121—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed by multiple encapsulations, e.g. by a thin protective coating and a thick encapsulation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/7416—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support used during dicing or grinding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P72/00—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof

- H10P72/70—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping

- H10P72/74—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support

- H10P72/7422—Handling or holding of wafers, substrates or devices during manufacture or treatment thereof for supporting or gripping using temporarily an auxiliary support used to protect an active side of a device or wafer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/012—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps

- H10W72/01231—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition

- H10W72/01233—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating

- H10W72/01235—Manufacture or treatment of bump connectors, dummy bumps or thermal bumps using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating by plating, e.g. electroless plating or electroplating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/019—Manufacture or treatment of bond pads

- H10W72/01931—Manufacture or treatment of bond pads using blanket deposition

- H10W72/01933—Manufacture or treatment of bond pads using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating

- H10W72/01935—Manufacture or treatment of bond pads using blanket deposition in liquid form, e.g. spin coating, spray coating or immersion coating by plating, e.g. electroless plating or electroplating

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/019—Manufacture or treatment of bond pads

- H10W72/01931—Manufacture or treatment of bond pads using blanket deposition

- H10W72/01938—Manufacture or treatment of bond pads using blanket deposition in gaseous form, e.g. by CVD or PVD

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/0198—Manufacture or treatment batch processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07202—Connecting or disconnecting of bump connectors using auxiliary members

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07202—Connecting or disconnecting of bump connectors using auxiliary members

- H10W72/07204—Connecting or disconnecting of bump connectors using auxiliary members using temporary auxiliary members, e.g. sacrificial coatings

- H10W72/07207—Temporary substrates, e.g. removable substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07251—Connecting or disconnecting of bump connectors characterised by changes in properties of the bump connectors during connecting

- H10W72/07253—Connecting or disconnecting of bump connectors characterised by changes in properties of the bump connectors during connecting changes in shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07251—Connecting or disconnecting of bump connectors characterised by changes in properties of the bump connectors during connecting

- H10W72/07254—Connecting or disconnecting of bump connectors characterised by changes in properties of the bump connectors during connecting changes in dispositions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/221—Structures or relative sizes

- H10W72/222—Multilayered bumps, e.g. a coating on top and side surfaces of a bump core

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/231—Shapes

- H10W72/234—Cross-sectional shape, i.e. in side view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/231—Shapes

- H10W72/237—Multiple bump connectors having different shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/241—Dispositions, e.g. layouts

- H10W72/242—Dispositions, e.g. layouts relative to the surface, e.g. recessed, protruding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/241—Dispositions, e.g. layouts

- H10W72/247—Dispositions of multiple bumps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/851—Dispositions of multiple connectors or interconnections

- H10W72/874—On different surfaces

- H10W72/879—Bump connectors and bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/922—Bond pads being integral with underlying chip-level interconnections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/922—Bond pads being integral with underlying chip-level interconnections

- H10W72/9226—Bond pads being integral with underlying chip-level interconnections with via interconnections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/921—Structures or relative sizes of bond pads

- H10W72/923—Bond pads having multiple stacked layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/9415—Dispositions of bond pads relative to the surface, e.g. recessed, protruding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/942—Dispositions of bond pads relative to underlying supporting features, e.g. bond pads, RDLs or vias

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/111—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed

- H10W74/114—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed by a substrate and the encapsulations

- H10W74/117—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being completely enclosed by a substrate and the encapsulations the substrate having spherical bumps for external connection

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/131—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed

- H10W74/142—Encapsulations, e.g. protective coatings characterised by their shape or disposition the semiconductor body being only partially enclosed the encapsulations exposing the passive side of the semiconductor body

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/10—Encapsulations, e.g. protective coatings characterised by their shape or disposition

- H10W74/15—Encapsulations, e.g. protective coatings characterised by their shape or disposition on active surfaces of flip-chip devices, e.g. underfills

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/28—Configurations of stacked chips the stacked chips having different sizes, e.g. chip stacks having a pyramidal shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/20—Configurations of stacked chips

- H10W90/297—Configurations of stacked chips characterised by the through-semiconductor vias [TSVs] in the stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/722—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/731—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors

- H10W90/732—Package configurations characterised by the relative positions of pads or connectors relative to package parts of die-attach connectors between stacked chips

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/754—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between a chip and a stacked insulating package substrate, interposer or RDL

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W99/00—Subject matter not provided for in other groups of this subclass

Landscapes

- Mechanical Treatment Of Semiconductor (AREA)

- Dicing (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Engineering & Computer Science (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Manufacturing & Machinery (AREA)

- Power Engineering (AREA)

Description

前記半導体パッケージの第1モールド層の幅、前記半導体パッケージの第2モールド層の幅、及び前記半導体パッケージの基板の幅の中でいずれか1つは、前記チップの幅に比べて大きくなり得る。

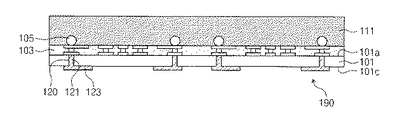

前記第1活性層上にポリマー物質を含む第1モールド層を形成して前記基板に剛性を付し、前記第1モールド層を形成した後に、前記基板の第1後面を除去して前記基板を薄型化し、第2後面を露出させ、前記薄型化された基板内に前記第1活性層と電気的に連結される貫通電極を形成し、前記薄型化された基板上に前記基板内に提供された前記貫通電極と電気的に連結されるパッドを形成することを包含することができる。

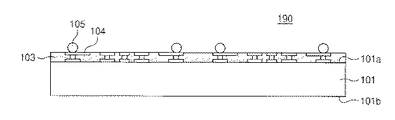

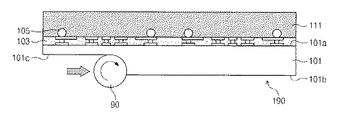

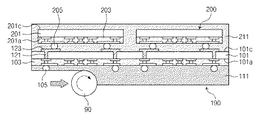

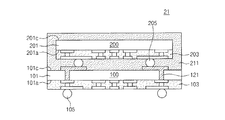

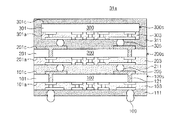

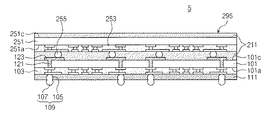

図1A乃至図1Jは本発明の一実施形態による半導体パッケージの製造方法を示した断面図である。図1Dは図1Bの変形形態を示した断面図である。

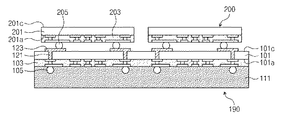

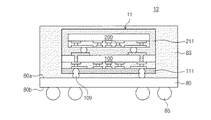

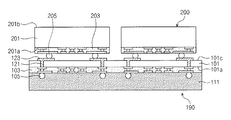

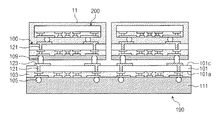

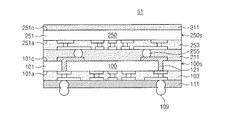

図2A乃至図2Dは本発明の他の実施形態による半導体パッケージの製造方法を示した断面図である。以下には第1実施形態と異なる点に対して詳説し、同一な点に対しては省略するか、或いは概説する。

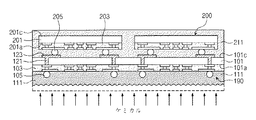

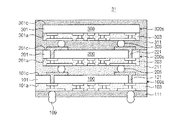

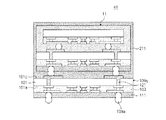

図3A乃至図3Hは本発明のその他の実施形態による半導体パッケージの製造方法を示した断面図である。図3Iは図3Aの変形形態を示した断面図である。図3Jは図3Gの変形形態を示した断面図である。

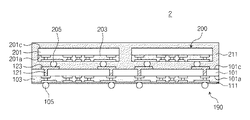

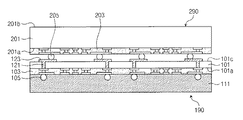

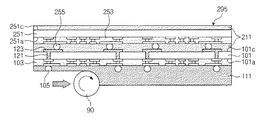

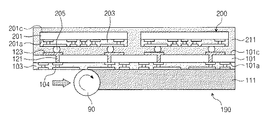

図4A乃至図4Eは本発明のその他の実施形態による半導体パッケージの製造方法を示した断面図である。以下には第1実施形態と異なる点に対して詳説し、同一な点に対しては省略するか、或いは概説する。

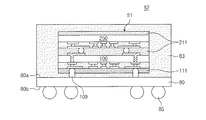

図5A乃至図5Eは本発明のその他の実施形態による半導体パッケージの製造方法を示した断面図である。以下には第1実施形態と異なる点に対して詳説し、同一な点に対しては省略するか、或いは概説する。

図6A乃至図6Dは本発明のその他の実施形態による半導体パッケージの製造方法を示した断面図である。以下には第1実施形態と異なる点に対して詳説し、同一な点に対しては省略するか、或いは概説する。

図7Aは本発明の実施形態による半導体パッケージを具備するメモリカードを示したブロック図である。図7Bは本発明の実施形態による半導体パッケージを応用した情報処理システムを示したブロック図である。

100・・・マスターチップ

101・・・下部ウエハー

101a・・・前面、活性面

101b・・・第1後面、非活性面

101c・・・第2後面

103・・・回路層

104・・・前面パッド

105・・・バンプ

109・・・外部端子

111・・・前面モールド層

120・・・垂直ホール

121・・・貫通電極

123・・・後面パッド

200・・・スレーブチップ

Claims (20)

- ウエハーの前面上に第1活性層を含む基板を提供し、

前記第1活性層上にポリマー物質を含む第1モールド層を形成して前記基板に剛性を提供し、

前記第1モールド層を形成した後に、接着剤の使用無しで前記第1モールド層に装置を付着して前記基板が支持された状態で、前記基板の第1後面を除去して前記基板を薄型化し、第2後面を露出させ、

前記薄型化された基板に前記基板に提供された貫通電極と電気的に連結されるパッドを形成することを含み、

前記第1モールド層は、前記基板が薄型化の間に曲がらないように、基板に剛性を提供するための所定の厚さを有する、半導体素子の製造方法。 - 前記装置は、前記装置が前記第1モールド層に接着されないまま、前記第1モールド層に付着される請求項1に記載の半導体素子の製造方法。

- 前記装置は、前記装置と前記第1モールド層との間に接着剤を使用せずに、前記第1モールド層に付着される請求項1に記載の半導体素子の製造方法。

- 前記基板の第1後面を薄型化することは、

機械的な工程を使用して前記第1後面を除去することを含む請求項1に記載の半導体素子の製造方法。 - 前記基板の第1後面を薄型化することは、

前記基板の第1後面をグラインディングすることを含む請求項1に記載の半導体素子の製造方法。 - 前記薄型化された基板内に前記貫通電極を形成することをさらに含む請求項4に記載の半導体素子の製造方法。

- 前記薄型化された基板の第2後面上にチップを積層することをさらに含み、

前記チップの活性面は、前記薄型化された基板の第2後面に向かう請求項6に記載の半導体素子の製造方法。 - 前記チップ上に前記チップをモールディングする第2モールド層を形成して前記基板に剛性を付し、

前記第2モールド層を形成した後に前記第1モールド層の少なくとも一部を除去して滑らかで平坦な面を形成することをさらに含む請求項7に記載の半導体素子の製造方法。 - 前記第1及び第2モールド層と前記基板とをカッティングして半導体パッケージを形成することをさらに含み、

前記半導体パッケージの第1モールド層の幅、前記半導体パッケージの第2モールド層の幅、及び前記半導体パッケージの基板の幅の中でいずれか1つは、前記チップの幅に比べて大きい請求項8に記載の半導体素子の製造方法。 - 前記半導体パッケージの第1モールド層の幅、前記半導体パッケージの第2モールド層の幅、及び前記半導体パッケージの基板の幅は、同一である請求項9に記載の半導体素子の製造方法。

- 前記第2モールド層は、前記チップと前記基板との間に配置されない請求項9に記載の半導体素子の製造方法。

- 前記基板を薄型化する時、前記装置は、前記第1モールド層と直接接触して支持する真空チャックである請求項1に記載の半導体素子の製造方法。

- 前記第1モールド層の少なくとも一部を除去する時、前記第2モールド層は、真空チャックに直接接触して支持される請求項8に記載の半導体素子の製造方法。

- 前記第1モールド層の熱膨張係数CTEと前記基板の熱膨張係数CTEとは、1つの桁程度(an order of magnitude)の範囲である請求項1に記載の半導体素子の製造方法。

- 前記第1モールド層の熱膨張係数CTEと前記基板の熱膨張係数CTEとの比は、3乃至1である請求項1に記載の半導体素子の製造方法。

- 前記第1活性層は、回路層である請求項1に記載の半導体素子の製造方法。

- ウエハーの前面上に提供された第1活性層を含む基板を提供し、

前記第1活性層上にポリマー物質を含む第1モールド層を形成して前記基板に剛性を付し、

前記第1モールド層を形成した後に、前記基板の第1後面を除去して前記基板を薄型化し、第2後面を露出させ、

前記薄型化された基板内に前記第1活性層と電気的に連結される貫通電極を形成し、

前記薄型化された基板上に前記基板内に提供された前記貫通電極と電気的に連結されるパッドを形成することを

含み、

前記第1モールド層の熱膨張係数CTEと前記基板の熱膨張係数CTEとは、1つの桁程度(an order of magnitude)の範囲である、半導体素子の製造方法。 - 前記第1モールド層は、装置が前記第1モールド層に接着されないまま、前記装置に付着される、請求項17に記載の半導体素子の製造方法。

- 前記第1モールド層は、装置と前記第1モールド層との間に接着剤を使用せずに、前記装置に付着される、請求項17に記載の半導体素子の製造方法。

- 前面上に第1活性層を含む基板を提供し、

前記第1活性層上に第1モールド層を形成して前記基板に剛性を提供し、

前記第1モールド層を形成した後に、前記基板の第1後面を除去して前記基板を薄型化し、第2後面を露出させ、

前記薄型化された基板内に前記第1活性層と電気的に連結される貫通電極を形成し、

前記薄型化された基板に前記基板内に提供された前記貫通電極と電気的に連結されるパッドを形成し、

前記薄型化された基板の第2後面上に、チップの活性面が前記薄型化された基板の第2後面に向かう前記チップを積層すること含み、

前記基板が薄型化されるときに接着剤の使用無しで装置に前記第1モールド層を付着して、前記基板が支持され、

前記第1モールド層の幅、及び前記基板の幅は、同一である、半導体素子の製造方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2013-0071775 | 2013-06-21 | ||

| KR1020130071775A KR102077153B1 (ko) | 2013-06-21 | 2013-06-21 | 관통전극을 갖는 반도체 패키지 및 그 제조방법 |

| US14/264,120 US9245771B2 (en) | 2013-06-21 | 2014-04-29 | Semiconductor packages having through electrodes and methods for fabricating the same |

| US14/264,120 | 2014-04-29 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015005748A JP2015005748A (ja) | 2015-01-08 |

| JP2015005748A5 JP2015005748A5 (ja) | 2016-02-25 |

| JP5908030B2 true JP5908030B2 (ja) | 2016-04-26 |

Family

ID=52111252

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014125069A Active JP5908030B2 (ja) | 2013-06-21 | 2014-06-18 | 貫通電極を有する半導体パッケージ及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9245771B2 (ja) |

| JP (1) | JP5908030B2 (ja) |

| KR (1) | KR102077153B1 (ja) |

| CN (1) | CN104241229B (ja) |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102174336B1 (ko) * | 2014-07-08 | 2020-11-04 | 삼성전자주식회사 | 반도체 패키지 및 그 제조 방법 |

| US9899285B2 (en) * | 2015-07-30 | 2018-02-20 | Semtech Corporation | Semiconductor device and method of forming small Z semiconductor package |

| US20170062240A1 (en) * | 2015-08-25 | 2017-03-02 | Inotera Memories, Inc. | Method for manufacturing a wafer level package |

| JP2017069397A (ja) * | 2015-09-30 | 2017-04-06 | 日立化成株式会社 | 半導体装置及びその製造方法 |

| JP2017073472A (ja) * | 2015-10-07 | 2017-04-13 | 株式会社ディスコ | 半導体装置の製造方法 |

| KR101712288B1 (ko) * | 2015-11-12 | 2017-03-03 | 앰코 테크놀로지 코리아 주식회사 | 반도체 패키지 및 그 제조 방법 |

| US10872879B2 (en) | 2015-11-12 | 2020-12-22 | Amkor Technology Singapore Holding Pte. Ltd. | Semiconductor package and manufacturing method thereof |

| KR102506697B1 (ko) * | 2016-05-18 | 2023-03-08 | 에스케이하이닉스 주식회사 | 관통 몰드 볼 커넥터를 포함하는 반도체 패키지 |

| US10204893B2 (en) | 2016-05-19 | 2019-02-12 | Invensas Bonding Technologies, Inc. | Stacked dies and methods for forming bonded structures |

| US9922845B1 (en) * | 2016-11-03 | 2018-03-20 | Micron Technology, Inc. | Semiconductor package and fabrication method thereof |

| US10879212B2 (en) | 2017-05-11 | 2020-12-29 | Invensas Bonding Technologies, Inc. | Processed stacked dies |

| CN109087897A (zh) * | 2017-06-13 | 2018-12-25 | 精材科技股份有限公司 | 晶片封装体及其制作方法 |

| US10217720B2 (en) | 2017-06-15 | 2019-02-26 | Invensas Corporation | Multi-chip modules formed using wafer-level processing of a reconstitute wafer |

| US12068246B2 (en) * | 2017-11-30 | 2024-08-20 | Taiwan Semiconductor Manufacturing Company, Ltd. | Redistribution layer layouts on integrated circuits and methods for manufacturing the same |

| KR102085654B1 (ko) * | 2017-12-07 | 2020-03-06 | 주식회사 아모텍 | 다이오드 복합소자 및 그의 제조 방법 |

| US11276676B2 (en) | 2018-05-15 | 2022-03-15 | Invensas Bonding Technologies, Inc. | Stacked devices and methods of fabrication |

| US10727204B2 (en) | 2018-05-29 | 2020-07-28 | Advances Micro Devices, Inc. | Die stacking for multi-tier 3D integration |

| WO2020010265A1 (en) | 2018-07-06 | 2020-01-09 | Invensas Bonding Technologies, Inc. | Microelectronic assemblies |

| US11158606B2 (en) | 2018-07-06 | 2021-10-26 | Invensas Bonding Technologies, Inc. | Molded direct bonded and interconnected stack |

| CN108831861A (zh) * | 2018-08-09 | 2018-11-16 | 苏州晶方半导体科技股份有限公司 | 堆叠式芯片封装方法及封装结构 |

| US10950529B2 (en) * | 2018-08-30 | 2021-03-16 | Advanced Semiconductor Engineering Korea, Inc. | Semiconductor device package |

| US20220406765A9 (en) * | 2018-10-02 | 2022-12-22 | Micron Technology, Inc. | Semiconductor device packages having stacked semiconductor dice |

| WO2020085715A1 (ko) * | 2018-10-26 | 2020-04-30 | 주식회사 네패스 | 반도체 패키지 |

| CN113330557A (zh) | 2019-01-14 | 2021-08-31 | 伊文萨思粘合技术公司 | 键合结构 |

| US11296053B2 (en) | 2019-06-26 | 2022-04-05 | Invensas Bonding Technologies, Inc. | Direct bonded stack structures for increased reliability and improved yield in microelectronics |

| KR102722905B1 (ko) | 2019-07-25 | 2024-10-30 | 삼성전자주식회사 | 반도체 패키지 및 그의 제조 방법 |

| US12080672B2 (en) | 2019-09-26 | 2024-09-03 | Adeia Semiconductor Bonding Technologies Inc. | Direct gang bonding methods including directly bonding first element to second element to form bonded structure without adhesive |

| JP7488116B2 (ja) * | 2020-06-03 | 2024-05-21 | 株式会社ディスコ | 電極形成方法 |

| US11631647B2 (en) | 2020-06-30 | 2023-04-18 | Adeia Semiconductor Bonding Technologies Inc. | Integrated device packages with integrated device die and dummy element |

| KR102805365B1 (ko) | 2020-07-15 | 2025-05-12 | 삼성전자주식회사 | 반도체 패키지, 및 이를 가지는 패키지 온 패키지 |

| US11764177B2 (en) | 2020-09-04 | 2023-09-19 | Adeia Semiconductor Bonding Technologies Inc. | Bonded structure with interconnect structure |

| US11728273B2 (en) | 2020-09-04 | 2023-08-15 | Adeia Semiconductor Bonding Technologies Inc. | Bonded structure with interconnect structure |

| US20220165669A1 (en) * | 2020-11-25 | 2022-05-26 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device structure, stacked semiconductor device structure and method of manufacturing semiconductor device structure |

| CN113035825A (zh) * | 2021-02-02 | 2021-06-25 | 日月光半导体制造股份有限公司 | 半导体封装结构及其形成方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3525808B2 (ja) | 1999-06-28 | 2004-05-10 | 松下電器産業株式会社 | 半導体装置の製造方法および半導体装置 |

| JP2001237205A (ja) * | 2000-02-24 | 2001-08-31 | Sumitomo Metal Ind Ltd | 化学機械的研磨装置、ダマシン配線形成装置及びダマシン配線形成方法 |

| US6841883B1 (en) * | 2003-03-31 | 2005-01-11 | Micron Technology, Inc. | Multi-dice chip scale semiconductor components and wafer level methods of fabrication |

| JP4390775B2 (ja) | 2006-02-08 | 2009-12-24 | Okiセミコンダクタ株式会社 | 半導体パッケージの製造方法 |

| US8409920B2 (en) * | 2007-04-23 | 2013-04-02 | Stats Chippac Ltd. | Integrated circuit package system for package stacking and method of manufacture therefor |

| US7948095B2 (en) | 2008-02-12 | 2011-05-24 | United Test And Assembly Center Ltd. | Semiconductor package and method of making the same |

| US7955895B2 (en) * | 2008-11-07 | 2011-06-07 | Taiwan Semiconductor Manufacturing Co., Ltd. | Structure and method for stacked wafer fabrication |

| US8487444B2 (en) | 2009-03-06 | 2013-07-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Three-dimensional system-in-package architecture |

| US8531015B2 (en) | 2009-03-26 | 2013-09-10 | Stats Chippac, Ltd. | Semiconductor device and method of forming a thin wafer without a carrier |

| KR20100109241A (ko) | 2009-03-31 | 2010-10-08 | 삼성전자주식회사 | 칩 적층 패키지 및 그 제조방법 |

| US8143097B2 (en) | 2009-09-23 | 2012-03-27 | Stats Chippac, Ltd. | Semiconductor device and method of forming open cavity in TSV interposer to contain semiconductor die in WLCSMP |

| KR20110105159A (ko) | 2010-03-18 | 2011-09-26 | 주식회사 하이닉스반도체 | 적층 반도체 패키지 및 그 형성방법 |

| KR101667656B1 (ko) | 2010-03-24 | 2016-10-20 | 삼성전자주식회사 | 패키지-온-패키지 형성방법 |

| KR101142339B1 (ko) * | 2010-06-17 | 2012-05-17 | 에스케이하이닉스 주식회사 | 반도체 칩 |

| US8338939B2 (en) | 2010-07-12 | 2012-12-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | TSV formation processes using TSV-last approach |

| KR101678539B1 (ko) * | 2010-07-21 | 2016-11-23 | 삼성전자 주식회사 | 적층 패키지, 반도체 패키지 및 적층 패키지의 제조 방법 |

| KR20120045402A (ko) | 2010-10-29 | 2012-05-09 | 에스케이하이닉스 주식회사 | 반도체 집적회로 및 그의 제조 방법 |

| KR20120053332A (ko) | 2010-11-17 | 2012-05-25 | 삼성전자주식회사 | 반도체 패키지 및 이의 제조 방법 |

| JP2012209545A (ja) | 2011-03-17 | 2012-10-25 | Sekisui Chem Co Ltd | 半導体積層体の製造方法 |

| KR20120123919A (ko) | 2011-05-02 | 2012-11-12 | 삼성전자주식회사 | 칩 적층 반도체 패키지 제조 방법 및 이에 의해 제조된 칩 적층 반도체 패키지 |

| US8642385B2 (en) | 2011-08-09 | 2014-02-04 | Alpha & Omega Semiconductor, Inc. | Wafer level package structure and the fabrication method thereof |

| US8853003B2 (en) * | 2011-08-09 | 2014-10-07 | Alpha & Omega Semiconductor, Inc. | Wafer level chip scale package with thick bottom metal exposed and preparation method thereof |

| US8779599B2 (en) * | 2011-11-16 | 2014-07-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Packages including active dies and dummy dies and methods for forming the same |

| KR101784507B1 (ko) * | 2011-12-14 | 2017-10-12 | 에스케이하이닉스 주식회사 | 반도체 적층 패키지 및 제조 방법, 이를 포함하는 전자 시스템 |

| US9006004B2 (en) * | 2012-03-23 | 2015-04-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Probing chips during package formation |

| JP5399542B2 (ja) * | 2012-08-08 | 2014-01-29 | 富士通株式会社 | 半導体装置の製造方法 |

-

2013

- 2013-06-21 KR KR1020130071775A patent/KR102077153B1/ko active Active

-

2014

- 2014-04-29 US US14/264,120 patent/US9245771B2/en active Active

- 2014-06-18 JP JP2014125069A patent/JP5908030B2/ja active Active

- 2014-06-20 CN CN201410279831.7A patent/CN104241229B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| KR20150000064A (ko) | 2015-01-02 |

| JP2015005748A (ja) | 2015-01-08 |

| CN104241229B (zh) | 2017-10-13 |

| US9245771B2 (en) | 2016-01-26 |

| KR102077153B1 (ko) | 2020-02-14 |

| CN104241229A (zh) | 2014-12-24 |

| US20140377909A1 (en) | 2014-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5908030B2 (ja) | 貫通電極を有する半導体パッケージ及びその製造方法 | |

| US12362343B2 (en) | Semiconductor device using EMC wafer support system and fabricating method thereof | |

| KR102094924B1 (ko) | 관통전극을 갖는 반도체 패키지 및 그 제조방법 | |

| US10867897B2 (en) | PoP device | |

| TWI710079B (zh) | 使用導線接合之混合式添加結構之可堆疊記憶體晶粒 | |

| US11705436B2 (en) | Semiconductor device and method for manufacturing the same | |

| JP2013526066A (ja) | 低減されたダイ歪みアッセンブリのためのパッケージ基板のためのcte補償 | |

| US8691625B2 (en) | Method for making a chip package | |

| KR20140141927A (ko) | 접합신뢰성이 우수한 연결단자를 갖는 반도체 장치 및 그의 제조방법 | |

| US10991597B2 (en) | Method of fabricating a semiconductor device using an adhesive layer | |

| US10825783B2 (en) | Semiconductor packages and devices | |

| KR101958831B1 (ko) | 양면 접착성 테이프, 반도체 패키지 및 그 제조 방법 | |

| CN108321128A (zh) | 封装结构及其制造方法 | |

| KR102777068B1 (ko) | 반도체 패키지 | |

| KR100577015B1 (ko) | 반도체 소자의 적층 칩 패키지 및 그 제조 방법 | |

| CN116313844A (zh) | 基于面板形态的芯片封装方法和芯片封装件 | |

| JP2005340483A (ja) | 半導体チップ、半導体装置、およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20141226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160108 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160108 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20160108 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20160126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160222 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160322 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5908030 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |