JP5500907B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP5500907B2 JP5500907B2 JP2009191589A JP2009191589A JP5500907B2 JP 5500907 B2 JP5500907 B2 JP 5500907B2 JP 2009191589 A JP2009191589 A JP 2009191589A JP 2009191589 A JP2009191589 A JP 2009191589A JP 5500907 B2 JP5500907 B2 JP 5500907B2

- Authority

- JP

- Japan

- Prior art keywords

- manufacturing

- film

- wiring

- semiconductor device

- conductive film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 116

- 238000004519 manufacturing process Methods 0.000 title claims description 75

- 229920002120 photoresistant polymer Polymers 0.000 claims description 67

- 238000000034 method Methods 0.000 claims description 47

- 239000000758 substrate Substances 0.000 claims description 47

- 229910052751 metal Inorganic materials 0.000 claims description 37

- 239000002184 metal Substances 0.000 claims description 37

- 238000005530 etching Methods 0.000 claims description 24

- 229910007541 Zn O Inorganic materials 0.000 claims description 13

- 229910052760 oxygen Inorganic materials 0.000 claims description 12

- 229910020923 Sn-O Inorganic materials 0.000 claims description 10

- 239000002985 plastic film Substances 0.000 claims description 9

- 229920006255 plastic film Polymers 0.000 claims description 9

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 claims description 6

- 229910052753 mercury Inorganic materials 0.000 claims description 6

- 229910018516 Al—O Inorganic materials 0.000 claims description 3

- 229910018557 Si O Inorganic materials 0.000 claims description 3

- 229910007991 Si-N Inorganic materials 0.000 claims description 3

- 229910006294 Si—N Inorganic materials 0.000 claims description 3

- 229910007604 Zn—Sn—O Inorganic materials 0.000 claims description 3

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Inorganic materials [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 claims description 3

- 239000010408 film Substances 0.000 description 97

- 208000033365 congenital hypomelinating neuropathy Diseases 0.000 description 41

- 238000012545 processing Methods 0.000 description 27

- 238000001312 dry etching Methods 0.000 description 25

- 238000010586 diagram Methods 0.000 description 21

- 238000000206 photolithography Methods 0.000 description 19

- 238000001039 wet etching Methods 0.000 description 19

- 238000004544 sputter deposition Methods 0.000 description 17

- 238000000926 separation method Methods 0.000 description 15

- 239000000463 material Substances 0.000 description 14

- 230000003071 parasitic effect Effects 0.000 description 13

- 238000005516 engineering process Methods 0.000 description 11

- 208000009989 Posterior Leukoencephalopathy Syndrome Diseases 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 239000013256 coordination polymer Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 229910044991 metal oxide Inorganic materials 0.000 description 6

- 150000004706 metal oxides Chemical class 0.000 description 6

- 229910021417 amorphous silicon Inorganic materials 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 229910052725 zinc Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 238000002835 absorbance Methods 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 208000035196 congenital hypomyelinating 2 neuropathy Diseases 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 150000002736 metal compounds Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000012827 research and development Methods 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

Description

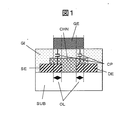

図2に、酸化物半導体を用い作成したトップゲート、ボトムコンタクト型のTFTを示す。ここでいうトップゲートとは、チャネル層CHNよりも上層にゲート電極GEが形成されている構造のことであり、ボトムコンタクトとは、チャネル層CHNよりも下層にソース電極SEおよびドレイン電極DEが形成されている構造のことである。

導電層CLを形成する。導電層CLの成膜はCVD法やスパッタ法などにより行ない、加工は一般的なフォトリソグラフィー技術とドライエッチングとの組み合わせにより行なう。

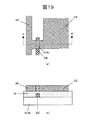

図11は、本実施の形態2における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるトップゲート/トップコンタクト型酸化物TFTを挙げている。ここでいうトップゲートとは、チャネル層CHNよりも上層にゲート電極GEが形成されている構造のことであり、トップコンタクトとは、チャネル層CHNよりも上層にソース電極SEおよびドレイン電極DEが形成されている構造のことを示している。

図12は、本実施の形態3における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるボトムゲート/トップコンタクト型酸化物TFTを挙げている。ここでいうボトムゲートとは、チャネル層CHNよりも下層にゲート電極GEが形成されている構造のことであり、トップコンタクトとは、チャネル層CHNよりも上層にソース電極SEおよびドレイン電極DEが形成されている構造のことを示している。

図17は、本実施の形態4における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるボトムゲート/ボトムコンタクト型酸化物TFTを挙げている。ここでいうボトムゲートとは、チャネル層CHNよりも下層にゲート電極GEが形成されている構造のことであり、ボトムコンタクトとは、チャネル層CHNよりも下層にソース電極SEおよびドレイン電極DEが形成されている構造のことを示している。

図18は、本実施の形態5における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるボトムゲート型酸化物TFTを挙げている。ここでいうボトムゲートとは、チャネル層CHNよりも下層にゲート電極GEが形成されている構造のことを示している。

図20は、本実施の形態6における半導体装置の構成および製造方法を示す図である。半導体装置としていわゆるボトムゲート型酸化物TFTを挙げている。ここでいうボトムゲートとは、チャネル層CHNよりも下層にゲート電極GEが形成されている構造のことを示している。

図21は本実施の形態5における半導体装置の構成を示す図である。実施の形態1〜6に示す構造の酸化物TFTを用いてアンテナ共振回路AR、整流器RCT、変調器MOD、デジタル回路DGCなどを構成し、無線タグを形成している。無線タグはリーダRDまたはライタWRと無線で通信を行うことができるようになっている。無線タグでは、リーダRDやライタWRとの無線通信を行なうが、高周波での動作が要求される。このとき、前記実施の形態1〜6に示す自己整合型酸化物TFTでは、寄生容量が小さいため高周波での動作が可能になる。これにより、前記実施の形態1〜6における自己整合型酸化物TFTを使用した回路の高速化を図ることができる。このことから、前記実施の形態1〜6に示す自己整合型酸化物TFTは、高周波動作が必要とされる無線タグの使用に適しているといえる。

図22は本実施の形態8における半導体装置の構成を示す図である。本実施の形態8では、前記実施の形態1〜6の構造を有する酸化物TFTを構成要素とする素子が基板SUB上にアレイ状に配置されている。前記実施の形態1〜6に示す酸化物TFTを、アレイ内の各素子のスイッチングや駆動用のトランジスタに用いることはもちろん、この酸化物TFTのゲート電極GEと接続されるゲート線GLに信号を送るゲート線駆動回路GDCや、この酸化物TFTのソース電極SEあるいはドレイン電極DEと接続されるデータ線DLに信号を送るデータ線駆動回路DDCを構成するトランジスタに用いてもよい。この場合、各素子の酸化物TFTとゲート線駆動回路GDCあるいはデータ線駆動回路DDC内の酸化物TFTを並行して形成することができる。

CE 容量電極

CHN チャネル層

CHN2 チャネル層

CP 寄生容量

DDC データ線駆動回路

DE ドレイン電極

DE2 ドレイン電極

DGC デジタル回路

DL データ線

GDC ゲート線駆動回路

GE ゲート電極

GE2 ゲート電極

GI ゲート絶縁膜

GL ゲート線

IF 絶縁膜

LWI 下層配線

MOD 変調器

NRES ネガレジスト

OL オーバラップ

PE 画素電極

PM フォトマスク

PRES ポジレジスト

RCT 整流器

RD リーダ

SE ソース電極

SE2 ソース電極

SUB 基板

TCL 透明導電膜

TFT 酸化物TFT

UWI 上層配線

WI 配線

WR ライタ

Claims (16)

- 基板上に金属膜によりソース電極とドレイン電極と共に第1配線を形成し、酸化物半導体によりチャネル膜を形成し、

前記ソース電極と前記ドレイン電極と前記チャネル膜の上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、導電膜を形成し、

前記導電膜上にネガレジストを塗布し、

前記ソース電極と前記ドレイン電極と共に前記第1配線をマスクとして、前記基板の裏面側から前記ネガレジストを露光し、

前記ネガレジストの露光部分を残し前記ネガレジストを除去し、

前記露光部分をエッチングマスクとして前記導電膜をエッチングし、

前記導電膜上にレジストを塗布し、

前記基板の表面側から前記レジストを露光し、

露光後の前記レジストをエッチングマスクとして前記導電膜を再度エッチングすることで、ゲート電極と共に第2配線を形成し、

前記第1配線直上の前記第2配線の分断部分に第3配線を形成し接続することを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記裏面露光の光源として、水銀ランプのi線を用いることを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記基板は、プラスチックフィルムからなることを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記チャネル膜は、Zn−O、In-O、Ga-O、Sn-O、In−Ga−Zn−O、Zn−Sn−O、In−Sn−O、In−Zn−O、Ga−Zn−O、In−Ga−Oの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記ゲート絶縁膜は、Si−O、Al−O、Si−Nの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記導電膜は、In-Sn-O、Al−Zn-O、Sn−Oの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項1記載の製造方法において、

前記基板と、チャネル膜と、ゲート絶縁膜と、導電膜は透明であり、

前記金属膜は不透明であることを特徴とする半導体装置の製造方法。 - 基板上に金属膜によりゲート電極と共に第1配線を形成し、

前記ゲート電極と前記基板の上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に酸化物半導体によりチャネル膜を形成し、

前記チャネル膜上に導電膜を形成し、

前記導電膜上にネガレジストを塗布し、

前記ゲート電極と共に前記第1配線をマスクとして、前記基板の裏面側から前記ネガレジストを露光し、

前記ネガレジストの露光部分を残し前記ネガレジストを除去し、

前記露光部分をエッチングマスクとして前記導電膜をエッチングし、

前記導電膜上にレジストを塗布し、

前記基板の表面側から前記レジストを露光し、

露光後の前記レジストをエッチングマスクとして前記導電膜を再度エッチングすることで、ソース電極とドレイン電極と共に第2配線を形成し、

前記第1配線直上の前記第2配線の分断部分に第3配線を形成し接続することを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記裏面露光の光源として、水銀ランプのi線を用いることを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記基板は、プラスチックフィルムからなることを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記チャネル膜は、Zn−O、In-O、Ga-O、Sn-O、In−Ga−Zn−O、Zn−Sn−O、In−Sn−O、In−Zn−O、Ga−Zn−O、In−Ga−Oの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記ゲート絶縁膜は、Si−O、Al−O、Si−Nの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記導電膜は、In-Sn-O、Al−Zn-O、Sn−Oの何れか一つから成ることを特徴とする半導体装置の製造方法。 - 請求項8記載の製造方法において、

前記基板と、チャネル膜と、ゲート絶縁膜と、導電膜は透明であり、

前記金属膜は不透明であることを特徴とする半導体装置の製造方法。 - 基板上に金属膜によりソース電極とドレイン電極と共に第1配線を形成し、酸化物半導体によりチャネル膜を形成し、

前記ソース電極と前記ドレイン電極と前記チャネル膜の上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に、導電膜を形成し、

前記導電膜上にネガレジストを塗布し、

前記ソース電極と前記ドレイン電極と共に前記第1配線をマスクとして、前記基板の裏面側から前記ネガレジストを露光し、

前記ネガレジストの露光部分を残し前記ネガレジストを除去し、

前記露光部分をエッチングマスクとして前記導電膜をエッチングし、

前記導電膜上にレジストを塗布し、

前記基板の表面側から前記レジストを露光し、

露光後の前記レジストをエッチングマスクとする前記導電膜のエッチングにより、ゲート電極と共に第2配線を形成し、

前記第1配線直上の前記第2配線の分断部分に第3配線を形成し接続することにより製造された半導体装置。 - 基板上に金属膜によりゲート電極と共に第1配線を形成し、

前記ゲート電極と前記基板の上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上に酸化物半導体によりチャネル膜を形成し、

前記チャネル膜上に導電膜を形成し、

前記導電膜上にネガレジストを塗布し、

前記ゲート電極と共に前記第1配線をマスクとして、前記基板の裏面側から前記ネガレジストを露光し、

前記ネガレジストの露光部分を残し前記ネガレジストを除去し、

前記露光部分をエッチングマスクとして前記導電膜をエッチングし、

前記導電膜上にレジストを塗布し、

前記基板の表面側から前記レジストを露光し、

露光後の前記レジストをエッチングマスクとして前記導電膜を再度エッチングすることで、ソース電極とドレイン電極と共に第2配線を形成し、

前記第1配線直上の前記第2配線の分断部分に第3配線を形成し接続することにより製造された半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009191589A JP5500907B2 (ja) | 2009-08-21 | 2009-08-21 | 半導体装置およびその製造方法 |

| US12/838,451 US8314032B2 (en) | 2009-08-21 | 2010-07-17 | Semiconductor device and method for manufacturing the same |

| KR1020100073549A KR101126798B1 (ko) | 2009-08-21 | 2010-07-29 | 반도체 장치 및 그 제조 방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009191589A JP5500907B2 (ja) | 2009-08-21 | 2009-08-21 | 半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011044575A JP2011044575A (ja) | 2011-03-03 |

| JP2011044575A5 JP2011044575A5 (ja) | 2012-04-26 |

| JP5500907B2 true JP5500907B2 (ja) | 2014-05-21 |

Family

ID=43604593

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009191589A Expired - Fee Related JP5500907B2 (ja) | 2009-08-21 | 2009-08-21 | 半導体装置およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8314032B2 (ja) |

| JP (1) | JP5500907B2 (ja) |

| KR (1) | KR101126798B1 (ja) |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011074407A1 (en) | 2009-12-18 | 2011-06-23 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9209314B2 (en) | 2010-06-16 | 2015-12-08 | Semiconductor Energy Laboratory Co., Ltd. | Field effect transistor |

| WO2012002186A1 (en) | 2010-07-02 | 2012-01-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| WO2012014786A1 (en) * | 2010-07-30 | 2012-02-02 | Semiconductor Energy Laboratory Co., Ltd. | Semicondcutor device and manufacturing method thereof |

| US8704230B2 (en) | 2010-08-26 | 2014-04-22 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2012256821A (ja) | 2010-09-13 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 記憶装置 |

| US9443984B2 (en) | 2010-12-28 | 2016-09-13 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US8829512B2 (en) | 2010-12-28 | 2014-09-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| GB2489682B (en) | 2011-03-30 | 2015-11-04 | Pragmatic Printing Ltd | Electronic device and its method of manufacture |

| GB2492442B (en) | 2011-06-27 | 2015-11-04 | Pragmatic Printing Ltd | Transistor and its method of manufacture |

| GB201202544D0 (en) | 2012-02-14 | 2012-03-28 | Pragmatic Printing Ltd | Electronic devices |

| JP2013012610A (ja) * | 2011-06-29 | 2013-01-17 | Dainippon Printing Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US9082663B2 (en) | 2011-09-16 | 2015-07-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| SG11201505088UA (en) | 2011-09-29 | 2015-08-28 | Semiconductor Energy Lab | Semiconductor device |

| JP6026839B2 (ja) * | 2011-10-13 | 2016-11-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN107068765B (zh) | 2011-10-14 | 2021-03-09 | 株式会社半导体能源研究所 | 半导体装置 |

| US8796682B2 (en) * | 2011-11-11 | 2014-08-05 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a semiconductor device |

| US8981367B2 (en) | 2011-12-01 | 2015-03-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6081171B2 (ja) | 2011-12-09 | 2017-02-15 | 株式会社半導体エネルギー研究所 | 記憶装置 |

| US10002968B2 (en) | 2011-12-14 | 2018-06-19 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and display device including the same |

| TWI613824B (zh) | 2011-12-23 | 2018-02-01 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| US9006024B2 (en) * | 2012-04-25 | 2015-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| TWI511200B (zh) * | 2013-07-25 | 2015-12-01 | Ye Xin Technology Consulting Co Ltd | 顯示面板製作方法 |

| TWI678740B (zh) * | 2013-09-23 | 2019-12-01 | 日商半導體能源研究所股份有限公司 | 半導體裝置 |

| JP2016076541A (ja) | 2014-10-03 | 2016-05-12 | ソニー株式会社 | 薄膜トランジスタ、薄膜トランジスタの製造方法および表示装置 |

| US9991394B2 (en) * | 2015-02-20 | 2018-06-05 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and fabrication method thereof |

| JP6583812B2 (ja) * | 2015-06-24 | 2019-10-02 | 国立研究開発法人物質・材料研究機構 | 多層構成の薄膜トランジスタの製造方法 |

| US11024744B2 (en) * | 2016-12-12 | 2021-06-01 | Sumitomo Electric Industries, Ltd. | Semiconductor device and method for manufacturing the same |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2913300B2 (ja) * | 1985-09-26 | 1999-06-28 | セイコーインスツルメンツ株式会社 | 薄膜トランジスタ装置の製造方法 |

| JPS62152174A (ja) | 1985-12-25 | 1987-07-07 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタの製造方法 |

| JPH02128432A (ja) * | 1988-11-08 | 1990-05-16 | Fuji Xerox Co Ltd | 薄膜トランジスタの製造方法 |

| JPH02211635A (ja) * | 1989-02-13 | 1990-08-22 | Seiko Epson Corp | 電界効果トランジスターの製造方法 |

| JPH02273935A (ja) * | 1989-04-14 | 1990-11-08 | Sanyo Electric Co Ltd | 薄膜トランジスタの製造方法 |

| GB9114018D0 (en) | 1991-06-28 | 1991-08-14 | Philips Electronic Associated | Thin-film transistor manufacture |

| US5441905A (en) * | 1993-04-29 | 1995-08-15 | Industrial Technology Research Institute | Process of making self-aligned amorphous-silicon thin film transistors |

| JPH06333949A (ja) | 1993-05-21 | 1994-12-02 | Kyocera Corp | 薄膜トランジスタの製造方法 |

| JPH07211914A (ja) * | 1994-01-13 | 1995-08-11 | Dainippon Printing Co Ltd | 薄膜トランジスタおよびその製造方法 |

| JPH08228011A (ja) * | 1994-12-14 | 1996-09-03 | Toshiba Corp | 半導体装置およびその製造方法 |

| GB9907019D0 (en) * | 1999-03-27 | 1999-05-19 | Koninkl Philips Electronics Nv | Thin film transistors and their manufacture |

| JP3447619B2 (ja) * | 1999-06-25 | 2003-09-16 | 株式会社東芝 | アクティブマトリクス基板の製造方法、中間転写基板 |

| GB9919913D0 (en) * | 1999-08-24 | 1999-10-27 | Koninkl Philips Electronics Nv | Thin-film transistors and method for producing the same |

| GB9929615D0 (en) * | 1999-12-15 | 2000-02-09 | Koninkl Philips Electronics Nv | Method of manufacturing an active matrix device |

| JP2003168645A (ja) * | 2001-12-03 | 2003-06-13 | Hitachi Ltd | 半導体薄膜装置、その製造方法及び画像表示装置 |

| US7211825B2 (en) * | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| TWI294689B (en) * | 2005-09-14 | 2008-03-11 | Ind Tech Res Inst | Method of tft manufacturing and a base-board substrate structure |

| JP2008171989A (ja) * | 2007-01-11 | 2008-07-24 | Toppan Printing Co Ltd | 電界効果型トランジスタ及びその製造方法 |

| KR100857455B1 (ko) * | 2007-04-17 | 2008-09-08 | 한국전자통신연구원 | 산화물 반도체막상에 보호막을 형성하여 패터닝하는 박막트랜지스터의 제조방법 |

| JP5213421B2 (ja) | 2007-12-04 | 2013-06-19 | キヤノン株式会社 | 酸化物半導体薄膜トランジスタ |

| JP5405850B2 (ja) * | 2009-02-17 | 2014-02-05 | 株式会社日立製作所 | 酸化物半導体を有する電界効果トランジスタの製造方法 |

| JP2010199457A (ja) * | 2009-02-27 | 2010-09-09 | Dainippon Printing Co Ltd | トランジスタ素子の製造方法 |

| JP2010199458A (ja) * | 2009-02-27 | 2010-09-09 | Dainippon Printing Co Ltd | トランジスタ素子の製造方法 |

-

2009

- 2009-08-21 JP JP2009191589A patent/JP5500907B2/ja not_active Expired - Fee Related

-

2010

- 2010-07-17 US US12/838,451 patent/US8314032B2/en not_active Expired - Fee Related

- 2010-07-29 KR KR1020100073549A patent/KR101126798B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US20110042667A1 (en) | 2011-02-24 |

| US8314032B2 (en) | 2012-11-20 |

| JP2011044575A (ja) | 2011-03-03 |

| KR20110020172A (ko) | 2011-03-02 |

| KR101126798B1 (ko) | 2012-03-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5500907B2 (ja) | 半導体装置およびその製造方法 | |

| US10403757B2 (en) | Top-gate self-aligned metal oxide semiconductor TFT and method of making the same | |

| US10109647B2 (en) | MOTFT with un-patterned etch-stop | |

| JP5325446B2 (ja) | 半導体装置及びその製造方法 | |

| US7550772B2 (en) | Image display device and manufacturing method thereof | |

| US8202770B2 (en) | Semiconductor structure of a display device and method for fabricating the same | |

| JP2010021170A (ja) | 半導体装置およびその製造方法 | |

| US10209558B2 (en) | Array substrate and manufacturing method thereof, display panel and display device | |

| JP2003273361A (ja) | 半導体装置およびその製造方法 | |

| WO2016123974A1 (zh) | 薄膜晶体管、像素结构及其制作方法、阵列基板、显示装置 | |

| US20100117155A1 (en) | Semiconductor device and production method thereof | |

| WO2016115824A1 (zh) | 薄膜晶体管、阵列基板及其制作方法 | |

| KR102586938B1 (ko) | 박막 트랜지스터 표시판 및 그 제조 방법 | |

| TWI495110B (zh) | 顯示面板及其製作方法 | |

| US8227302B2 (en) | Semiconductor device, electronic device, and manufacturing method thereof | |

| CN111710725A (zh) | 双栅电极金属氧化物薄膜晶体管及其制备方法 | |

| TWI528564B (zh) | 薄膜電晶體及其製作方法 | |

| US20130146864A1 (en) | Thin film transistor display panel and manufacturing method thereof | |

| TWI814369B (zh) | 感光元件基板及其製造方法 | |

| JP2009206388A (ja) | 薄膜トランジスタとその製造方法 | |

| US11502115B2 (en) | Active matrix substrate and method for manufacturing same | |

| US20230187555A1 (en) | Semiconductor device and manufacturing method thereof | |

| WO2023097728A1 (zh) | 阵列基板及显示面板 | |

| JP2010114160A (ja) | 半導体素子およびその製造方法並びに表示装置 | |

| JP2023033960A (ja) | アクティブマトリクス基板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120308 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140311 |

|

| LAPS | Cancellation because of no payment of annual fees |