JP5431777B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5431777B2 JP5431777B2 JP2009101679A JP2009101679A JP5431777B2 JP 5431777 B2 JP5431777 B2 JP 5431777B2 JP 2009101679 A JP2009101679 A JP 2009101679A JP 2009101679 A JP2009101679 A JP 2009101679A JP 5431777 B2 JP5431777 B2 JP 5431777B2

- Authority

- JP

- Japan

- Prior art keywords

- wafer

- insulating film

- film pattern

- thickness

- back surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 77

- 238000004519 manufacturing process Methods 0.000 title claims description 38

- 238000000034 method Methods 0.000 claims description 96

- 230000008569 process Effects 0.000 claims description 70

- 229910052751 metal Inorganic materials 0.000 claims description 52

- 239000002184 metal Substances 0.000 claims description 52

- 238000000227 grinding Methods 0.000 claims description 12

- 239000000853 adhesive Substances 0.000 claims description 4

- 230000001070 adhesive effect Effects 0.000 claims description 4

- 239000010408 film Substances 0.000 description 173

- 235000012431 wafers Nutrition 0.000 description 150

- 230000015572 biosynthetic process Effects 0.000 description 21

- 238000004544 sputter deposition Methods 0.000 description 20

- 229910052581 Si3N4 Inorganic materials 0.000 description 17

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 17

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 17

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 14

- 239000000758 substrate Substances 0.000 description 14

- 238000005530 etching Methods 0.000 description 13

- 230000003014 reinforcing effect Effects 0.000 description 13

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 12

- 229910052710 silicon Inorganic materials 0.000 description 12

- 239000010703 silicon Substances 0.000 description 12

- 229910052814 silicon oxide Inorganic materials 0.000 description 12

- 238000010586 diagram Methods 0.000 description 9

- 238000005468 ion implantation Methods 0.000 description 9

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 8

- 230000001681 protective effect Effects 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 230000000116 mitigating effect Effects 0.000 description 7

- 230000002093 peripheral effect Effects 0.000 description 7

- 238000001179 sorption measurement Methods 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 6

- 239000012790 adhesive layer Substances 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 239000000523 sample Substances 0.000 description 5

- 238000000137 annealing Methods 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- 239000002131 composite material Substances 0.000 description 3

- 229910001873 dinitrogen Inorganic materials 0.000 description 3

- 239000010410 layer Substances 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 239000000377 silicon dioxide Substances 0.000 description 3

- 239000010409 thin film Substances 0.000 description 3

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 3

- 229910052721 tungsten Inorganic materials 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 239000005380 borophosphosilicate glass Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000011229 interlayer Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000005453 pelletization Methods 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 230000002787 reinforcement Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 238000004381 surface treatment Methods 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229940104869 fluorosilicate Drugs 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000011800 void material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3083—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their size, orientation, disposition, behaviour, shape, in horizontal or vertical plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L22/00—Testing or measuring during manufacture or treatment; Reliability measurements, i.e. testing of parts without further processing to modify the parts as such; Structural arrangements therefor

- H01L22/10—Measuring as part of the manufacturing process

- H01L22/14—Measuring as part of the manufacturing process for electrical parameters, e.g. resistance, deep-levels, CV, diffusions by electrical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2221/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof covered by H01L21/00

- H01L2221/67—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere

- H01L2221/683—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L2221/68304—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

- H01L2221/6834—Apparatus for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support used to protect an active side of a device or wafer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electrodes Of Semiconductors (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

- Formation Of Insulating Films (AREA)

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。

(a)第1の厚さを有する半導体ウエハの第1の主面上に、第1の金属膜を形成する工程;

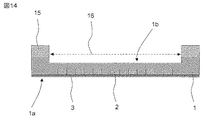

(b)前記工程(a)の後、前記半導体ウエハの第2の主面側に対して、バック・グラインディング処理を実行することにより、前記第1の厚さよりも薄い第2の厚さとする工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面上に、その周辺に沿って、第1の絶縁膜からなり、前記第2の主面の周辺に沿う円環状絶縁膜パターンを含む絶縁膜パターンを形成する工程;

(d)前記絶縁膜パターンがある状態で、前記円環状絶縁膜パターンの開口部の厚さを前記第2の厚さよりも薄い第3の厚さとする工程;

(e)前記工程(d)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハに対して、電気的テストを実行する工程;

(f)前記工程(e)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面を粘着シートに貼り付けることにより、前記粘着シートを介してダイシング・フレームに保持させる工程;

(g)前記工程(f)の後、ダイシング・フレームに保持された状態で、前記半導体ウエハを個々のチップに分割する工程。

(h)前記工程(e)の前であって前記工程(d)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面上に、第2の金属膜を形成する工程。

(i)前記工程(h)の前であって前記工程(d)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面に、不純物イオンを注入する工程。

(j)前記工程(h)の前であって前記工程(i)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面に対して、前記不純物イオンの活性化アニールを実行する工程。

(k)前記工程(h)の前であって前記工程(j)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面の前記開口部の酸化膜を除去する工程。

1.本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクションに分けて記載する場合もあるが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しを省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

実施の形態について更に詳述する。各図中において、同一または同様の部分は同一または類似の記号または参照番号で示し、説明は原則として繰り返さない。

図1は、本願の一実施の形態の半導体装置の製造方法の対象デバイスの一例であるノン・パンチスルー(Non−Punch−Through)型IGBT素子のセル部の拡大断面図である(なお、パンチスルー型IGBT素子にも適用できることは言うまでもない)。図2は、図1のIGBT素子の等価回路図である。図1および図2に基づいて、ウエハ1の反りとウエハ1の表面1aおよび裏面1bに形成された種々の金属膜との関係を説明するのに必要な範囲でセル部の縦構造を説明する。セル部は、一般にパワー・デバイスのチップ領域2(図4)の大半を占めるので、多数の単位セルからなるセル部分の単位部分の縦構造を見れば、ウエハ1の反りに寄与する種々の膜の関係を理解することができる。

図10は、本願の一実施の形態の半導体装置の製造方法における補強用環状絶縁膜パターンの形成に使用するスパッタリング装置の模式正断面図である。図11は、本願の一実施の形態の半導体装置の製造方法における補強用環状絶縁膜パターンの元となる絶縁膜の形成に使用するプラズマCVD装置の模式正断面図である。

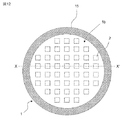

図3は、本願の一実施の形態の半導体装置の製造方法の主要プロセス・ブロック・フロー図である。図12は図3に対応するデバイス裏面図であり、図19は、図3に対応するデバイス表面(表側面)図(ダイシング工程)である。図4から図9、図13から図18、および図20は、図3に対応するデバイス断面プロセス・フロー図である。図12は、図3に対応するデバイス裏面図(補強用環状絶縁膜パターン形成完了時点)である。図19は、図3に対応するデバイス表面(表側面)図(ダイシング工程)である。これらのうち図13は図12のX−X’に対応するデバイス断面図であり、図20は図19のX−X’に対応するデバイス断面図である。以下では、ウエハの反りという観点から製造プロセスの要部等を説明する。ここでは、200φウエハを例にとり説明する。

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

1a ウエハ(またはチップ)の表面又は表側(第1の主面又はデバイス面)

1b ウエハ(またはチップ)の裏面(第2の主面)

1s N型単結晶シリコン基板部

2 半導体素子領域(チップ領域)

3 表面金属膜(第1の金属膜)

4 裏面金属膜(第2の金属膜)

5 ゲート・ポリシリコン膜

6p 裏面側P+領域

6n 裏面側N+領域(埋め込みN+領域)

7 N型ドリフト領域

8 チャネル領域

9 P型ベース領域

10 IGBT素子

10b IGBT素子のバイポーラ・トランジスタ部分

10m IGBT素子のMOSFET部分

11 N+エミッタ領域

12 ディープP+領域

14 ゲート周辺絶縁膜(ゲート絶縁膜および層間絶縁膜)

15 第1の絶縁膜(絶縁膜パターン)

16 円環状絶縁膜パターンの中央部の円形開口(またはその部分に対応するウエハ)

31 BG保護テープ(ウエハ表面保護テープ)

31a BG保護テープの基体

31b BG保護テープの粘着層

51 スパッタ成膜装置

52 スパッタ成膜チャンバ

53 スパッタ成膜装置の下部電極(ウエハ・ステージ)

54 スパッタ成膜装置の上部電極(ターゲット・バッキング・プレート)

55 ターゲット

56 シャッタ

57 シャドー・マスク

58 円環状開口

59 回転軸

61 BGホイール

62 BGウエハ吸着回転テーブル

63 ストレス・リリーフ用エッチング回転ステージ

64 ストレス・リリーフ用エッチング薬液ノズル

65 剥離装置のウエハ吸着ステージ

67 直流電源

68 ガス導入口

69 排気口

71 プラズマCVD装置

72 プラズマCVD装置の下部電極(ウエハ・ステージ)

73 プラズマCVD装置の上部電極

74 高周波電源(13.56MHz)

75 低周波電源(250kHz)

76 プラズマCVD装置の処理チャンバ

77 シャワー・ヘッド

78 ガス導入口

79 排気口

81 イオン注入装置のウエハ吸着ステージ

85 ウエハ・プローバ

86 表面プローブ針

87 裏面プローブ針

88 ウエハ・プローバのウエハ吸着ステージ

90 ダイシング装置

91 ダイシング・ウエハ保持フレーム

92 ダイシング・テープ

92a ダイシング・テープの基材部

92b ダイシング・テープの粘着剤層

94 ダイシング・ブレード

95 真空吸着ウエハ・ステージ

101 ウエハ表面処理工程群(第1の主面処理工程群)

101a ウエハ表面金属膜形成工程(第1の金属膜形成工程)

102 バック・グラインディング工程群

102a ウエハ表面への研削保護テープ貼り付け工程

102b バック・グラインディング工程

102c ストレス・リリーフ工程

102d BGテープ剥離工程

103 ウエハ補強膜成膜工程(ウエハ補強膜パターン形成工程)

104 ウエハ裏面エッチング工程

105 ウエハ裏面イオン注入工程群

105a ウエハ裏面イオン注入工程

105b ウエハ裏面活性化アニール工程

106 ウエハ裏面酸化膜除去

107 ウエハ裏面メタル膜成膜工程(第2の金属膜形成工程)

108 ウエハ・テスト工程

109 ダイシング工程(ペレタイズ工程)

C コレクタ端子(コレクタ電極)

E エミッタ端子(エミッタ電極)

G ゲート端子(ゲート電極)

Claims (1)

- 以下の工程を含む半導体装置の製造方法:

(a)第1の厚さを有する半導体ウエハの第1の主面上に、第1の金属膜を形成する工程;

(b)前記工程(a)の後、前記半導体ウエハの第2の主面側に対して、バック・グラインディング処理を実行することにより、前記第1の厚さよりも薄い第2の厚さとする工程;

(c)前記工程(b)の後、前記半導体ウエハの前記第2の主面上に、その周辺に沿って、第1の絶縁膜からなり、前記第2の主面の周辺に沿う円環状絶縁膜パターンを含む絶縁膜パターンを形成する工程;

(d)前記絶縁膜パターンがある状態で、前記円環状絶縁膜パターンの開口部の厚さを前記第2の厚さよりも薄い第3の厚さとする工程;

(e)前記工程(d)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハに対して、電気的テストを実行する工程;

(f)前記工程(e)の後、前記絶縁膜パターンがある状態で、前記半導体ウエハの前記第2の主面を粘着シートに貼り付けることにより、前記粘着シートを介してダイシング・フレームに保持させる工程;

(g)前記工程(f)の後、ダイシング・フレームに保持された状態で、前記半導体ウエハを個々のチップに分割する工程。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009101679A JP5431777B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置の製造方法 |

| US12/719,067 US8039276B2 (en) | 2009-04-20 | 2010-03-08 | Manufacturing method of semiconductor device |

| US13/237,235 US8153452B2 (en) | 2009-04-20 | 2011-09-20 | Manufacturing method of semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009101679A JP5431777B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010251632A JP2010251632A (ja) | 2010-11-04 |

| JP2010251632A5 JP2010251632A5 (ja) | 2012-04-12 |

| JP5431777B2 true JP5431777B2 (ja) | 2014-03-05 |

Family

ID=42981301

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009101679A Active JP5431777B2 (ja) | 2009-04-20 | 2009-04-20 | 半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8039276B2 (ja) |

| JP (1) | JP5431777B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11081344B2 (en) | 2018-01-25 | 2021-08-03 | Fujifilm Business Innovation Corp. | Method for manufacturing semiconductor substrate |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2953064B1 (fr) * | 2009-11-20 | 2011-12-16 | St Microelectronics Tours Sas | Procede d'encapsulation de composants electroniques sur tranche |

| WO2012165551A1 (ja) * | 2011-06-02 | 2012-12-06 | 電気化学工業株式会社 | 粘着テープおよび半導体ウエハ加工方法 |

| JP5755043B2 (ja) * | 2011-06-20 | 2015-07-29 | 株式会社ディスコ | 半導体ウエーハの加工方法 |

| JP5846060B2 (ja) | 2011-07-27 | 2016-01-20 | 信越化学工業株式会社 | ウエハ加工体、ウエハ加工用部材、ウエハ加工用仮接着材、及び薄型ウエハの製造方法 |

| JP5464192B2 (ja) * | 2011-09-29 | 2014-04-09 | 株式会社デンソー | 半導体装置の製造方法 |

| JP5893887B2 (ja) * | 2011-10-11 | 2016-03-23 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP5687647B2 (ja) * | 2012-03-14 | 2015-03-18 | 株式会社東芝 | 半導体装置の製造方法、半導体製造装置 |

| JP5591852B2 (ja) * | 2012-03-19 | 2014-09-17 | 株式会社東芝 | 半導体装置の検査方法、半導体装置の製造方法、検査用治具 |

| US9318446B2 (en) | 2013-03-15 | 2016-04-19 | Infineon Technologies Austria Ag | Metal deposition on substrates |

| CN107078061B (zh) * | 2015-03-16 | 2020-07-10 | 富士电机株式会社 | 半导体装置的制造方法 |

| EP3164890B1 (en) * | 2015-04-24 | 2017-11-01 | ABB Schweiz AG | Method for manufacturing a power semiconductor device with thick top-metal-design |

| DE102015112649B4 (de) * | 2015-07-31 | 2021-02-04 | Infineon Technologies Ag | Verfahren zum bilden eines halbleiterbauelements und halbleiterbauelement |

| JP6658171B2 (ja) | 2016-03-22 | 2020-03-04 | 富士電機株式会社 | 半導体装置の製造方法 |

| EP3640973A4 (en) * | 2018-01-17 | 2021-03-17 | SPP Technologies Co., Ltd. | WIDE GAP SEMICONDUCTOR SUBSTRATE, APPARATUS FOR MANUFACTURING A WIDE GAP SEMICONDUCTOR SUBSTRATE AND METHOD FOR MANUFACTURING A WIDE GAP SEMICONDUCTOR SUBSTRATE |

| JP7200537B2 (ja) * | 2018-08-21 | 2023-01-10 | 富士フイルムビジネスイノベーション株式会社 | 半導体基板の製造方法 |

| US20200321236A1 (en) * | 2019-04-02 | 2020-10-08 | Semiconductor Components Industries, Llc | Edge ring removal methods |

| CN110676207B (zh) * | 2019-09-27 | 2021-11-16 | 云谷(固安)科技有限公司 | 分离装置以及分离方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3184493B2 (ja) * | 1997-10-01 | 2001-07-09 | 松下電子工業株式会社 | 電子装置の製造方法 |

| US6162702A (en) * | 1999-06-17 | 2000-12-19 | Intersil Corporation | Self-supported ultra thin silicon wafer process |

| JP3834589B2 (ja) * | 2001-06-27 | 2006-10-18 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| DE10256985B4 (de) * | 2001-12-12 | 2013-01-10 | Denso Corporation | Verfahren zur Herstellung eines Leistungshalbleiterbauelements |

| JP3620528B2 (ja) | 2001-12-12 | 2005-02-16 | 株式会社デンソー | 半導体装置の製造方法 |

| US6884717B1 (en) * | 2002-01-03 | 2005-04-26 | The United States Of America As Represented By The Secretary Of The Air Force | Stiffened backside fabrication for microwave radio frequency wafers |

| JP2004186522A (ja) * | 2002-12-05 | 2004-07-02 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP4570896B2 (ja) * | 2004-04-06 | 2010-10-27 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2005303218A (ja) * | 2004-04-16 | 2005-10-27 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP4020097B2 (ja) | 2004-05-11 | 2007-12-12 | セイコーエプソン株式会社 | 半導体チップ、半導体装置及びその製造方法、並びに電子機器 |

| CN101002307A (zh) * | 2004-07-16 | 2007-07-18 | 株式会社瑞萨科技 | 制造半导体集成电路器件的方法 |

| JP4904922B2 (ja) | 2006-05-26 | 2012-03-28 | トヨタ自動車株式会社 | 半導体基板製造方法及び半導体基板 |

| JP4816278B2 (ja) * | 2006-06-15 | 2011-11-16 | 富士電機株式会社 | 半導体装置の製造方法 |

| JP2008053595A (ja) | 2006-08-28 | 2008-03-06 | Toyota Motor Corp | 半導体ウエハとその製造方法 |

| JP5007179B2 (ja) * | 2007-08-29 | 2012-08-22 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

-

2009

- 2009-04-20 JP JP2009101679A patent/JP5431777B2/ja active Active

-

2010

- 2010-03-08 US US12/719,067 patent/US8039276B2/en active Active

-

2011

- 2011-09-20 US US13/237,235 patent/US8153452B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11081344B2 (en) | 2018-01-25 | 2021-08-03 | Fujifilm Business Innovation Corp. | Method for manufacturing semiconductor substrate |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100267175A1 (en) | 2010-10-21 |

| JP2010251632A (ja) | 2010-11-04 |

| US8153452B2 (en) | 2012-04-10 |

| US8039276B2 (en) | 2011-10-18 |

| US20120009695A1 (en) | 2012-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5431777B2 (ja) | 半導体装置の製造方法 | |

| JP4185704B2 (ja) | 半導体装置の製造方法 | |

| US8507362B2 (en) | Process of forming ultra thin wafers having an edge support ring | |

| JP5712058B2 (ja) | 半導体装置の製造方法 | |

| PH12013000169A1 (en) | Semiconductor die singulation method | |

| US7737531B2 (en) | Wafer including a reinforcing flange formed upright at a periphery and method for manufacturing the same | |

| US20140134828A1 (en) | Semiconductor die singulation method | |

| US10032670B2 (en) | Plasma dicing of silicon carbide | |

| JP2014007351A (ja) | 半導体装置の製造方法 | |

| JP3620528B2 (ja) | 半導体装置の製造方法 | |

| US20220336265A1 (en) | Method of forming semiconductor-on-insulator (soi) substrate | |

| CN107968048A (zh) | 一种降低半导体器件背面金属接触电阻的方法 | |

| US20200321236A1 (en) | Edge ring removal methods | |

| JP6028325B2 (ja) | 半導体装置の製造方法 | |

| JP4724729B2 (ja) | 半導体装置の製造方法 | |

| US11710656B2 (en) | Method of forming semiconductor-on-insulator (SOI) substrate | |

| JP2002100773A (ja) | 半導体装置及びその製造方法 | |

| JP2013093442A (ja) | 半導体装置の製造方法 | |

| JP2013041919A (ja) | 半導体装置の製造方法 | |

| JP2010272676A (ja) | 半導体装置の製造方法 | |

| JP2011249721A (ja) | 半導体装置 | |

| JP2007266347A (ja) | 半導体装置の製造方法 | |

| TW202435455A (zh) | 用於矽上gan晶圓之單粒化的系統及方法 | |

| JP2011138976A (ja) | 半導体装置の製造方法 | |

| JP2009260041A (ja) | 半導体装置の製造方法および成膜装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120229 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120229 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131007 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131125 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131205 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5431777 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |