JP5049467B2 - 薄膜トランジスタと薄膜トランジスタ基板とそれらの製造方法 - Google Patents

薄膜トランジスタと薄膜トランジスタ基板とそれらの製造方法 Download PDFInfo

- Publication number

- JP5049467B2 JP5049467B2 JP2005087085A JP2005087085A JP5049467B2 JP 5049467 B2 JP5049467 B2 JP 5049467B2 JP 2005087085 A JP2005087085 A JP 2005087085A JP 2005087085 A JP2005087085 A JP 2005087085A JP 5049467 B2 JP5049467 B2 JP 5049467B2

- Authority

- JP

- Japan

- Prior art keywords

- channel layer

- region

- crystal

- insulating layer

- temperature gradient

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010409 thin film Substances 0.000 title claims description 61

- 239000000758 substrate Substances 0.000 title claims description 42

- 238000004519 manufacturing process Methods 0.000 title claims description 27

- 239000013078 crystal Substances 0.000 claims description 79

- 238000010899 nucleation Methods 0.000 claims description 67

- 230000006911 nucleation Effects 0.000 claims description 67

- 238000000034 method Methods 0.000 claims description 34

- 239000004973 liquid crystal related substance Substances 0.000 claims description 13

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 7

- 238000000137 annealing Methods 0.000 claims description 6

- 150000002500 ions Chemical class 0.000 claims description 5

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 5

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 4

- 230000000149 penetrating effect Effects 0.000 claims 2

- 238000000059 patterning Methods 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 19

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 14

- 230000008569 process Effects 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 14

- 239000010703 silicon Substances 0.000 description 14

- 229910021417 amorphous silicon Inorganic materials 0.000 description 9

- 239000002245 particle Substances 0.000 description 9

- 238000005530 etching Methods 0.000 description 7

- 238000000206 photolithography Methods 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 230000017525 heat dissipation Effects 0.000 description 5

- 230000000295 complement effect Effects 0.000 description 4

- 238000005224 laser annealing Methods 0.000 description 4

- 230000003197 catalytic effect Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000002210 silicon-based material Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 230000004931 aggregating effect Effects 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000005247 gettering Methods 0.000 description 1

- 229910021478 group 5 element Inorganic materials 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 230000001737 promoting effect Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 238000001953 recrystallisation Methods 0.000 description 1

- 230000007261 regionalization Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

Images

Classifications

-

- A—HUMAN NECESSITIES

- A47—FURNITURE; DOMESTIC ARTICLES OR APPLIANCES; COFFEE MILLS; SPICE MILLS; SUCTION CLEANERS IN GENERAL

- A47G—HOUSEHOLD OR TABLE EQUIPMENT

- A47G19/00—Table service

- A47G19/22—Drinking vessels or saucers used for table service

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78675—Polycrystalline or microcrystalline silicon transistor with normal-type structure, e.g. with top gate

-

- A—HUMAN NECESSITIES

- A47—FURNITURE; DOMESTIC ARTICLES OR APPLIANCES; COFFEE MILLS; SPICE MILLS; SUCTION CLEANERS IN GENERAL

- A47G—HOUSEHOLD OR TABLE EQUIPMENT

- A47G19/00—Table service

- A47G19/22—Drinking vessels or saucers used for table service

- A47G2019/2277—Drinking vessels or saucers used for table service collapsible

-

- A—HUMAN NECESSITIES

- A47—FURNITURE; DOMESTIC ARTICLES OR APPLIANCES; COFFEE MILLS; SPICE MILLS; SUCTION CLEANERS IN GENERAL

- A47G—HOUSEHOLD OR TABLE EQUIPMENT

- A47G2400/00—Details not otherwise provided for in A47G19/00-A47G23/16

- A47G2400/02—Hygiene

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Recrystallisation Techniques (AREA)

Description

多くのTFTでは、チャネル層用の半導体に、非晶質シリコン(以下、a−Siという)や多結晶シリコン(以下、p−Siという)を利用している。a−Siは、特定の結晶方向を有しない複数のシリコン結晶粒子によって構成される高純度のシリコン物質である。一方、p−Siは、種々の結晶方向を有する複数の単結晶シリコン小粒子によって構成される高純度のシリコン物質である。即ち、p−Siは、単結晶シリコンとa−Siの中間の高純度なシリコンといえる。電子移動度については、a−Siよりもp−Siの方が大きくなる。

図1aと図1bに示すような従来のチャネル層14では、核生成がチャネル層14の多数箇所において生じることがある。核生成が多多数箇所において生じると、多くの結晶粒子が形成されることとなり、結晶粒子のサイズは小さくなってしまう。多くの結晶粒子が形成されることは、多くの粒子境界が存在することとなり、電子移動度を減少させてしまうことになる。

上記のことから、結晶粒子径が大きく、電子移動度が高い薄膜トランジスタが必要とされている。

この製造方法によると、温度勾配誘導体によって、有形チャネル層の核生成領域の方が、結晶端領域よりも、熱をより速く放散する。

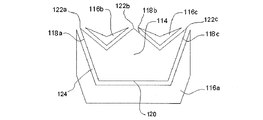

図2bに示すように、チャネル層114は水滴のような形状をしており、核生成領域118と、核生成領域118の略反対側に位置している結晶端領域120を備えている。結晶端領域120は、核生成領域118に比べて広い。核生成領域118は、核生成点122を備えている。以下で詳細に説明するように、チャネル層では、アニール処理が施されることによって、核生成領域118の核生成点122又はその近傍において再結晶化が生じる。その結晶粒子は、結晶端領域120に向けて成長する。チャネル層114は、例えば水滴形状や、三角形状や、扇形状や、台形状等に形成することができる。

チャネル層114は、ソース領域128と、中間領域130と、ドレイン領域132を備えている。さらに、TFT100は、ゲート絶縁層134と、ゲート電極136と、第1の中間絶縁層138と、ソース電極140と、ドレイン電極142を備えている。ゲート絶縁層134は、基板112上に形成されており、チャネル層114と温度勾配誘導体116を覆っている。ゲート電極136は、ゲート絶縁層134上に形成されている。第1の中間絶縁層138は、ゲート絶縁層134上に形成されており、ゲート電極136を覆っている。ソース電極140とドレイン電極142は、第1の中間絶縁層138上に形成されているとともに、ゲート絶縁層134を貫通してソース領域128とドレイン領域132へそれぞれ電気的に接続している。本実施形態においては、温度勾配誘導体116が単一であることに限定されない。複数の温度勾配誘導体を形成することが可能であることは、いわゆる当業者にとって明らかである。

図3に示すように、プラズマ化学気相成長工程によって、高い反応温度、例えば、略575℃〜650℃により、初期チャネル層110を基板112上に蒸着形成する。プラズマ化学気相成長工程では、プラズマによって、気体分子が原子やイオンや原子群に分解される。

図4aに示すように、フォトリソグラフィとエッチング工程によって、初期チャネル層110にパターン形成を行い、チャネル層114と温度勾配誘導体116とチャネル層114および温度勾配誘導体116との間に位置する不定距離間隙124を形成する。チャネル層114では、核生成領域118と結晶端領域120が規定されている。結晶端領域120は、核生成領域118の核生成点122に対して略反対側に位置している。

チャネル層114の形状は、水滴形状(図4bに示される)や、三角形状(図4cに示される)や、扇形状(図4dに示される)や、台形形状(図4eに示される)等とすることができる。説明を明瞭にするために、ここでは水滴形状に形成する実施形態について詳細に説明する。

典型的には、初期チャネル層110の一部を除去し、基板層112に向けて下方へと伸びる間隙124を形成することによって、チャネル層114が温度勾配誘導体116から独立し、チャネル層114が温度勾配誘導体116に接続することがないようになっている。不定距離間隙124では、温度勾配誘導体116の広幅部分144とチャネル層114の結晶端領域120との間において第1間隙距離124aを有しており、温度勾配誘導体116の狭幅部分146とチャネル層114の核生成領域118との間において第2間隙距離124bを有している。第1間隙距離124aは、第2間隙距離124bよりも短く設定されている。

温度勾配誘導体116における温度勾配や、チャネル層114の形状や、不定距離間隙124等によって、チャネル層114内に温度勾配が誘導される。具体的には、チャネル層114の結晶領域120における温度は、核生成領域118の温度よりも高くなる。それにより、チャネル層114における結晶成長は、核生成領域118の核生成点122から結晶端領域120へ向けて進むこととなる。

図5dに示すように、実施形態の一例として、初期チャネル層110にパターン形成を行うことによって、略王冠状のチャネル層114と、複数の温度勾配誘導体116a、116b、116cを形成することができる。王冠状のチャネル層114は、複数の核生成領域118a、118b、118cを備えており、それぞれに核生成点122a、122b、122cが規定される。温度勾配誘導体116bは、王冠状チャネル層114の形状に対して相補的な形状をしており、核生成点122aと核生成点122bとの間に位置している。温度勾配誘導体116cは、王冠状チャネル層114の形状に対して相補的な形状をしており、核生成点122bと核生成点122cとの間に位置している。特許文献1の技術と比較すると、本開示技術による薄膜トランジスタの製造方法では、少ないレーザエネルギーを利用して、粒子径の大きい多結晶シリコン層を形成することができる。

図7に示すように、イオン注入工程によって、チャネル層114にP型イオン(P−)又はN型イオン(N+)をイオン注入し、ソース領域128、中間領域130、ドレイン領域132を形成する。

図8に示すように、第1の中間絶縁層138を、ゲート絶縁層134とゲート電極136上に形成する。次いで、フォトリソグラフィとエッチング工程によって、2つのコンタクトホール152、154を、第1の中間絶縁層138とゲート絶縁層134に形成する。コンタクトホール152、154は、ソース領域128とドレイン領域132の一部を露出する。

図9に示すように、第1の中間絶縁層138上に、第2の金属薄層156を、2つのコンタクトホール152、154を充填するように形成する。フォトリソグラフィとエッチング工程によって第2の金属薄層156にパターン形成を行い、ソース電極140とドレイン電極142を形成する。

チャネル層114は、いくつかの実施形態において、結晶粒子径の大きい多結晶シリコン層や、単結晶シリコン層で形成することができる。それにより、チャネル層114は高い電子移動度を有することができる。

第2の中間絶縁層158上とコンタクトホール160内に、透明導電性薄膜162が形成されている。透明導電性薄膜162は、ドレイン電極142と電気的に接続している。透明導電性薄膜162は、フォトリソグラフィとエッチング工程によって、パターン形成される。透明導電性薄膜162を、対応する薄膜トランジスタ100に電気的に接続することによって、本開示技術による薄膜トランジスタ基板200を形成することができる。

Claims (18)

- 基板上に設けられている薄膜トランジスタであって、

前記基板上に形成され、結晶端領域と少なくとも1つの核生成領域が規定され、前記核生成領域では第1の横幅を有するとともに前記結晶端領域では第2の横幅を有し、前記第1の横幅は前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記基板上に形成され、前記チャネル層を取り囲んでおり、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層との間に間隙を形成する少なくとも1つの温度勾配誘導体と、

前記基板上に形成されているとともに前記チャネル層を覆っているゲート絶縁層と、

前記ゲート絶縁層上に形成されているゲート電極と、

前記ゲート絶縁層上に形成されているとともに前記ゲート電極を覆っている第1の中間絶縁層と、

前記第1の中間絶縁層上に形成されているとともに前記ゲート絶縁層と前記第1の中間絶縁層を貫通して前記チャネル層に電気的に接続しているソース電極およびドレイン電極と、

を備える薄膜トランジスタ。 - 前記チャネル層は、多結晶シリコンおよび単結晶シリコンの少なくとも一方から形成されていることを特徴とする請求項1の薄膜トランジスタ。

- 前記チャネル層は、水滴の形状、三角形状、扇形状、台形形状、王冠形状のいずれかであることを特徴とする請求項1又は2の薄膜トランジスタ。

- 前記温度勾配誘導体と前記チャネル層との間の間隙では、前記広幅部分における前記間隙の距離は、前記狭幅部分における前記間隙の距離よりも、短くなっていることを特徴とする請求項1から3のいずれか一項の薄膜トランジスタ。

- 前記温度勾配誘導体の前記狭幅部分に、鋸歯状の縁部が形成されていることを特徴とする請求項1から4のいずれか一項の薄膜トランジスタ。

- 前記第1の中間絶縁層上に形成されており、前記ゲート絶縁層および前記第1の中間絶縁層を貫通して前記チャネル層と電気的に接続しているソース電極およびドレイン電極と、

前記第1の中間絶縁層上に配設されており、前記ソース電極と前記ドレイン電極を覆っており、コンタクトホールが形成されている第2の中間絶縁層と、

前記第2の中間絶縁層上に形成されており、前記コンタクトホールに蒸着されている画素電極と、

が付加されている請求項1から5のいずれか一項の薄膜トランジスタ。 - 薄膜トランジスタを製造する方法であって、

基板上に初期チャネル層を形成する工程と、

前記初期チャネル層にパターン形成を行うことによって、有形チャネル層と少なくとも1つの温度勾配誘導体を形成する工程と、

前記有形チャネル層と前記温度勾配誘導体をアニールする工程と、

前記基板上に、前記有形チャネル層と前記温度勾配誘導体を覆うゲート絶縁層を形成する工程と、

前記ゲート絶縁層上にゲート電極を形成する工程と、

前記有形チャネル層に、P型イオン(P−)およびN型イオン(N+)の少なくとも一方をイオン注入することによって、ソース領域と中間領域とドレイン領域を形成する工程と、

前記ゲート絶縁層上に、前記ゲート電極を覆う第1の中間絶縁層を形成する工程と、

前記ゲート絶縁層と前記第1の中間絶縁層を貫通する2つのコンタクトホールを形成することによって、前記ソース領域と前記ドレイン領域を露出させる工程と、

前記第1の中間絶縁層上に、前記2つのコンタクトホールの少なくとも一部を充填するソース電極とドレイン電極を形成する工程とを備え、

前記有形チャネル層は、結晶端領域と核生成領域が規定され、前記核生成領域で第1の横幅を有するとともに前記結晶端領域で第2の横幅を有し、前記第1の横幅が前記第2の横幅よりも狭いものであり、

前記温度勾配誘導体は、前記有形チャネル層の周囲の少なくとも一部に隣接し、前記有形チャネル層の前記結晶端領域に対応して位置する広幅部分および前記核生成領域に対応して位置する狭幅部分を備え、前記有形チャネル層との間に間隙を形成するものであり、

前記アニールする工程では、前記有形チャネル層における結晶粒子の成長が、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする製造方法。 - 前記有形チャネル層の前記狭幅部分は尖部を備えており、

前記有形チャネル層における結晶粒子の成長は、前記核生成領域で開始し、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする請求項7の製造方法。 - 前記第1の中間絶縁層上に、前記ソース電極と前記ドレイン電極を覆う第2の中間絶縁層を形成する工程と、

前記第2の中間絶縁層に、コンタクトホールを形成する工程と、

前記第2の中間絶縁層上および前記コンタクトホール内に画素電極を形成する工程と、

が付加されている請求項7の製造方法。 - 薄膜トランジスタであって、

基板と、

前記基板上に形成され、核生成領域と結晶端領域が規定され、前記核生成領域では第1の横幅を有するとともに前記結晶端領域では第2の横幅を有し、前記第1の横幅が前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記基板上に形成され、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層との間に間隙を形成して隣接している温度勾配誘導体と、

を備える薄膜トランジスタ。 - 前記チャネル層と前記温度勾配誘導体との間の間隙は、前記結晶端領域に隣接する位置において第1の距離を有しているとともに前記核生成領域に隣接する位置において第2の距離を有しており、

前記第1の距離は、前記第2の距離よりも短いことを特徴とする請求項10の薄膜トランジスタ。 - 前記核生成領域は尖部を備えており、

前記狭幅部分には、前記尖部に対応して位置している開口部が形成されていることを特徴とする請求項10の薄膜トランジスタ。 - 液晶表示装置を製造する方法であって、

基板を準備する工程と、

前記基板上に初期チャネル層を形成する工程と、

前記初期チャネル層の少なくとも一部を、有形チャネル層と、有形チャネル層に隣接する温度勾配誘導体に成形する工程と、

前記有形チャネル層と前記温度勾配誘導体をアニールする工程とを備え、

前記有形チャネル層は、第1の横幅を有する核生成領域と第2の横幅を有する結晶端領域が規定され、前記第1の横幅は前記第2の横幅よりも狭いものであり、

前記温度勾配誘導体は、前記有形チャネル層の前記結晶端領域に対応して位置する広幅部分および前記核生成領域に対応して位置する狭幅部分を備え、前記有形チャネル層との間に間隙を形成するものであり、

前記アニールする工程では、前記有形チャネル層における結晶粒子の成長が、前記核生成領域から前記結晶端領域に向けて進むことを特徴とする製造方法。 - 前記温度勾配誘導体は、前記初期チャネル層の少なくとも一部を除去することによって、前記初期チャネル層から形成することを特徴とする請求項13の製造方法。

- 前記温度勾配誘導体と前記有形チャネル層との間の間隙は、前記核生成領域に隣接する位置において第1の距離であるとともに前記結晶端領域に隣接する位置において第2の距離であり、前記第1の距離は前記第2の距離よりも長いことを特徴とする請求項13又は14の製造方法。

- 液晶表示装置であって、

第1の基板と、

第2の基板と、

第1の基板と第2の基板との間に挟持されている液晶層と、

前記第2の基板上に形成され、核生成領域および結晶端領域を備え、前記核生成領域で第1の横幅を有するとともに前記結晶端領域で第2の横幅を有し、前記第1の横幅は前記第2の横幅よりも狭く、結晶粒子の成長方向が前記核生成領域から前記結晶端領域に向かう構造を有するチャネル層と、

前記第2の基板上に形成され、広幅部分と狭幅部分を備え、前記広幅部分が前記結晶端領域に隣接するとともに前記狭幅部分が前記核生成領域に隣接し、前記チャネル層の周囲に間隙を形成して隣接している温度勾配誘導体と、

を備える液晶表示装置。 - 前記チャネル層と前記温度勾配誘導体との間の間隙は、前記結晶端領域に隣接する位置において第1の距離を有しているとともに前記核生成領域に隣接する位置において第2の距離を有しており、前記第1の距離は前記第2の距離よりも短いことを特徴とする請求項16の液晶表示装置。

- 前記核生成領域は尖部を備えており、

前記狭幅部分には、前記尖部に対応して位置する開口部が形成されていることを特徴とする請求項16又は17の液晶表示装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW093108422A TWI240950B (en) | 2004-03-26 | 2004-03-26 | Thin film transistor, thin film transistor substrate, and methods for manufacturing the same |

| TW093108422 | 2004-03-26 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005286330A JP2005286330A (ja) | 2005-10-13 |

| JP2005286330A5 JP2005286330A5 (ja) | 2008-04-24 |

| JP5049467B2 true JP5049467B2 (ja) | 2012-10-17 |

Family

ID=34988722

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005087085A Expired - Fee Related JP5049467B2 (ja) | 2004-03-26 | 2005-03-24 | 薄膜トランジスタと薄膜トランジスタ基板とそれらの製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US7199399B2 (ja) |

| JP (1) | JP5049467B2 (ja) |

| KR (1) | KR101126282B1 (ja) |

| TW (1) | TWI240950B (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009146432A1 (en) | 2008-05-30 | 2009-12-03 | Colorado State University Research Foundation | Plasma-based chemical source device and method of use thereof |

| US8994270B2 (en) | 2008-05-30 | 2015-03-31 | Colorado State University Research Foundation | System and methods for plasma application |

| WO2009146439A1 (en) | 2008-05-30 | 2009-12-03 | Colorado State University Research Foundation | System, method and apparatus for generating plasma |

| TWI361492B (en) | 2008-07-25 | 2012-04-01 | Au Optronics Corp | Thin film transistor substrate, electric apparatus, and method for fabricating the same |

| US8222822B2 (en) | 2009-10-27 | 2012-07-17 | Tyco Healthcare Group Lp | Inductively-coupled plasma device |

| EP2552340A4 (en) | 2010-03-31 | 2015-10-14 | Univ Colorado State Res Found | PLASMA DEVICE WITH LIQUID GAS INTERFACE |

| EP2554028B1 (en) | 2010-03-31 | 2016-11-23 | Colorado State University Research Foundation | Liquid-gas interface plasma device |

| US8735207B2 (en) * | 2011-04-05 | 2014-05-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method to avoid fixed pattern noise within backside illuminated (BSI) complementary metal-oxide-semiconductor (CMOS) sensor array |

| US9532826B2 (en) | 2013-03-06 | 2017-01-03 | Covidien Lp | System and method for sinus surgery |

| US9555145B2 (en) | 2013-03-13 | 2017-01-31 | Covidien Lp | System and method for biofilm remediation |

| WO2016140670A1 (en) * | 2015-03-05 | 2016-09-09 | Hewlett-Packard Development Company, L.P. | Generating three-dimensional objects |

| CN104900713B (zh) * | 2015-06-15 | 2017-12-08 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、显示基板、显示装置 |

| KR102526615B1 (ko) * | 2018-09-18 | 2023-04-27 | 엘지디스플레이 주식회사 | 박막 트랜지스터와, 이를 포함하는 기판 내장형 드라이버 및 표시 장치 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6066416A (ja) * | 1983-09-22 | 1985-04-16 | Matsushita Electric Ind Co Ltd | 半導体集積回路基体の製造方法 |

| JPH081892B2 (ja) * | 1987-06-03 | 1996-01-10 | 松下電子工業株式会社 | 半導体装置の製造方法 |

| JP3472401B2 (ja) * | 1996-01-17 | 2003-12-02 | 三菱電機株式会社 | 半導体装置の製造方法 |

| JP3969510B2 (ja) * | 1998-08-31 | 2007-09-05 | エルジー フィリップス エルシーディー カンパニー リミテッド | 薄膜トランジスタアレイ基板および液晶表示装置 |

| JP2000208771A (ja) * | 1999-01-11 | 2000-07-28 | Hitachi Ltd | 半導体装置、液晶表示装置およびこれらの製造方法 |

| JP2001135573A (ja) * | 1999-11-02 | 2001-05-18 | Sharp Corp | 半導体装置の製造方法およびその半導体装置 |

| JP2002270507A (ja) * | 2001-03-14 | 2002-09-20 | Hitachi Cable Ltd | 結晶シリコン層の形成方法および結晶シリコン半導体装置 |

| JP2003008024A (ja) * | 2001-06-21 | 2003-01-10 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ及び半導体装置及び表示装置 |

| JP2004063478A (ja) * | 2002-04-11 | 2004-02-26 | Fumimasa Yo | 薄膜トランジスタ及びその製造方法 |

| AU2003302834A1 (en) * | 2002-12-09 | 2004-06-30 | Samsung Electronics Co., Ltd. | Display pixel, display apparatus having an image pixel and method of manufacturing display device |

| JP4593094B2 (ja) * | 2003-08-21 | 2010-12-08 | 日本電気株式会社 | 液晶表示装置及びその製造方法 |

-

2004

- 2004-03-26 TW TW093108422A patent/TWI240950B/zh not_active IP Right Cessation

-

2005

- 2005-03-21 US US11/085,420 patent/US7199399B2/en not_active Expired - Fee Related

- 2005-03-24 JP JP2005087085A patent/JP5049467B2/ja not_active Expired - Fee Related

- 2005-03-24 KR KR1020050024638A patent/KR101126282B1/ko not_active IP Right Cessation

-

2007

- 2007-01-15 US US11/623,214 patent/US7432140B2/en not_active Expired - Fee Related

-

2008

- 2008-08-25 US US12/197,416 patent/US8139175B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20070114535A1 (en) | 2007-05-24 |

| KR20060044702A (ko) | 2006-05-16 |

| US7199399B2 (en) | 2007-04-03 |

| TW200532744A (en) | 2005-10-01 |

| US20080316386A1 (en) | 2008-12-25 |

| US20050211985A1 (en) | 2005-09-29 |

| KR101126282B1 (ko) | 2012-03-19 |

| JP2005286330A (ja) | 2005-10-13 |

| US8139175B2 (en) | 2012-03-20 |

| TWI240950B (en) | 2005-10-01 |

| US7432140B2 (en) | 2008-10-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5049467B2 (ja) | 薄膜トランジスタと薄膜トランジスタ基板とそれらの製造方法 | |

| JP4263609B2 (ja) | 多結晶シリコン用マスク及びこれを利用した薄膜トランジスタの製造方法 | |

| US6531348B2 (en) | Method for crystallizing amorphous silicon and fabricating thin film transistor using crystallized silicon | |

| JP2008252108A (ja) | 半導体装置 | |

| KR101146995B1 (ko) | 다결정 실리콘층의 형성 방법 및 이를 이용한 박막 트랜지스터의 형성방법 | |

| TWI527087B (zh) | 多晶矽層、備製多晶矽層之方法、使用多晶矽層之薄膜電晶體及包含該薄膜電晶體之有機發光顯示裝置 | |

| TW200423407A (en) | Fabricating method of low temperature poly-silicon film and low temperature poly-silicon thin film transistor | |

| JP2005354028A (ja) | 薄膜トランジスタ及びその製造方法 | |

| JP2001345451A (ja) | 薄膜半導体集積回路装置、それを用いた画像表示装置、及びその製造方法 | |

| JP2008072093A (ja) | 薄膜トランジスタ及びその製造方法 | |

| KR100721957B1 (ko) | 다결정 실리콘층, 상기 다결정 실리콘층을 이용한 평판표시 장치 및 이들을 제조하는 방법 | |

| KR100504538B1 (ko) | 비정질 실리콘의 결정화 방법 및 이를 이용한액정표시장치의제조방법 | |

| KR100678739B1 (ko) | 탑 게이트 구조의 나노결정-실리콘 박막트랜지스터형성방법 | |

| KR100721956B1 (ko) | 다결정 실리콘층, 상기 다결정 실리콘층을 이용한 평판표시 장치 및 이들을 제조하는 방법 | |

| JP4115590B2 (ja) | 半導体装置の作製方法 | |

| KR100751315B1 (ko) | 박막 트랜지스터, 박막 트랜지스터 제조 방법 및 이를구비한 평판 디스플레이 소자 | |

| JP3433903B2 (ja) | 半導体装置の製造方法 | |

| JPH0786601A (ja) | 多結晶シリコンmosトランジスタ及びその製造方法 | |

| JP2004128345A (ja) | 半導体装置の製造方法および表示装置の製造方法 | |

| JP4322969B2 (ja) | 結晶性珪素膜の作製方法 | |

| JP3977063B2 (ja) | 半導体薄膜とその製造方法 | |

| JP2000260713A (ja) | 多結晶シリコン膜の形成方法 | |

| KR100788993B1 (ko) | 다결정 실리콘 박막 트랜지스터의 제조 방법 | |

| JP2000260707A (ja) | 多結晶シリコン膜の形成方法 | |

| KR101088449B1 (ko) | 금속 촉매를 이용한 폴리 게이트 전극을 구비하는 반도체 소자 및 그 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080311 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080311 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120417 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120605 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20120605 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120710 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120723 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150727 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |