JP4931277B2 - フレキシブル基板上の相互接続用金属にダイを位置合せするための装置及び方法 - Google Patents

フレキシブル基板上の相互接続用金属にダイを位置合せするための装置及び方法 Download PDFInfo

- Publication number

- JP4931277B2 JP4931277B2 JP2000388006A JP2000388006A JP4931277B2 JP 4931277 B2 JP4931277 B2 JP 4931277B2 JP 2000388006 A JP2000388006 A JP 2000388006A JP 2000388006 A JP2000388006 A JP 2000388006A JP 4931277 B2 JP4931277 B2 JP 4931277B2

- Authority

- JP

- Japan

- Prior art keywords

- die

- flexible substrate

- bond pad

- reference point

- camera

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/76—Apparatus for connecting with build-up interconnects

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5389—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates the chips being integrally enclosed by the interconnect and support structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/82—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/544—Marks applied to semiconductor devices or parts

- H01L2223/54426—Marks applied to semiconductor devices or parts for alignment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04105—Bonding areas formed on an encapsulation of the semiconductor or solid-state body, e.g. bonding areas on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8312—Aligning

- H01L2224/83136—Aligning involving guiding structures, e.g. spacers or supporting members

- H01L2224/83138—Aligning involving guiding structures, e.g. spacers or supporting members the guiding structures being at least partially left in the finished device

- H01L2224/8314—Guiding structures outside the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/91—Methods for connecting semiconductor or solid state bodies including different methods provided for in two or more of groups H01L2224/80 - H01L2224/90

- H01L2224/92—Specific sequence of method steps

- H01L2224/921—Connecting a surface with connectors of different types

- H01L2224/9212—Sequential connecting processes

- H01L2224/92142—Sequential connecting processes the first connecting process involving a layer connector

- H01L2224/92144—Sequential connecting processes the first connecting process involving a layer connector the second connecting process involving a build-up interconnect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01018—Argon [Ar]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01027—Cobalt [Co]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01039—Yttrium [Y]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01074—Tungsten [W]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01075—Rhenium [Re]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01087—Francium [Fr]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

- H01L2924/141—Analog devices

- H01L2924/1423—Monolithic Microwave Integrated Circuit [MMIC]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/4913—Assembling to base an electrical component, e.g., capacitor, etc.

- Y10T29/49131—Assembling to base an electrical component, e.g., capacitor, etc. by utilizing optical sighting device

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Laser Beam Processing (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Manufacturing Of Printed Wiring (AREA)

- Drying Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の分野】

本発明はダイ配置の分野に関するものであって、更に詳しく言えば、ポリイミドフレックスのごときフレキシブル基板上にダイを配置する際の精度を向上させることに関する。

【0002】

【発明の背景】

ダイ配置のための適応性リソグラフィーの技術は、指定された既存の標識(たとえば、以前の金属層上に存在するダイボンドパッド又は基準マーク)の位置狂いを測定し、そしてこれらの位置狂いに対応するように金属線及びバイアのルーティングを変更するというものである。もし通常のリソグラフィー装置を使用するのであれば、これは各々の個別部品上に焼付けられる各々のアートワーク層用のカスタムマスクを製作することに類似している。仮想マスク(すなわち、コンピュータメモリから部品上に直接に書込まれるマスク)の使用及びアートワークの自動化されたカスタマイズにより、コスト面の制約は解消されている。

【0003】

とは言え、この方法にはまだ欠点が存在している。それは、ダイの位置狂い及び以前のルーティング層のゆがみに対処するための相互接続アートワークのカスタマイズを自動化するための特注装置を必要とする点で資本集約的である。それはまた、線の再ルーティングに際して線の幅及びピッチを最小にするための設計規則に従わなければならず、かつ各々のアートワークはそれが表わす部品に特有のものであるために計算集約的でもある。最後に、最も重要なのは、現在実施されているこの方法がなお極めて労働集約的であるという点である。各々のダイの位置狂い及びフレキシブル基板のゆがみを正確に測定することは、完全には自動化されていない。フレキシブル基板のゆがみを一般化して測定の回数を低減させる技術は開発されており、また特注の「コンポーネント・マッピング・システム(CMC)」を使用すれば、各々の個別部品用のアートワークを正確にカスタマイズするために必要なデータを収集するために要求される工数を低減させることもできる。しかしながら、設定、(CMCの自動化された視覚認識システムに対して補足又は拒絶を行うための)判断、及び正確なアートワークを各々の対応する部品上に確実に焼付けるためのトラッキングについてはオペレータの多大の関与がなおも必要である。

【0004】

ある種類の高密度相互接続(HDI)回路モジュールにおいては、チップウェル内に集積回路チップを支持し得る基板上に接着剤で被覆された重合体フィルムオーバレイが設置される。次いで、バイア開口を形成することによって集積回路チップのチップパッドが露出させられる。重合体フィルムは、バイアを通して基板の金属被膜及び(又は)個々の回路チップを相互接続するために役立つ金属被膜パターンを蒸着するための絶縁層を提供する。オーバレイを用いてHDI操作を実行するための方法は、アイヘルベルガー(Eichelberger)等の米国特許第4783695号及びアイヘルベルガー(Eichelberger)等の米国特許第4933042号の明細書中に一層詳しく記載されている。一般に、複数の重合体フィルムオーバレイ及び金属被膜パターンが使用される。

【0005】

本発明の場合と同じ譲受人に譲渡されたコール(Cole)等の米国特許第5527741号明細書中に記載されているような別の種類の回路モジュール(本明細書中においては「チップ・オン・フレックス」と呼ぶ)の場合、回路モジュールの製造方法は金属被覆された基礎絶縁層及び外部絶縁層を有するフレキシブルな相互接続層の使用を含んでいる。チップパッドを有する少なくとも1個の回路チップが基礎絶縁層に結合され、そして外部絶縁層及び基礎絶縁層中にバイアを形成することによって基礎絶縁層の金属被膜及びチップパッドの特定部分が露出させられる。結合されたチップの周囲に基板が成形される。外部絶縁層上には、特定のバイアを通って延びるようにパターン形成された外部金属層が設置され、それによって特定のチップパッドと基礎絶縁層の金属被膜の特定部分とが相互接続される。

【0006】

前述のコール(Cole)等の米国特許第5527741号明細書中に開示されているもののごとき標準的なチップ・オン・フレックス法においては、通例はモジュールレイアウトの外周部に位置する金属中にパターン形成された「大域」基準点に対して補間的に位置合せすることにより、ダイがポリイミドフレックスのごときフレキシブル基板上に配置される。25μのターゲットの範囲内におけるダイ配置の精度は1.79σのZstを有している(図6参照)。なお、Zstは「短期シグマ」として定義される。Zstは、欠陥(この場合にはダイの位置狂い)の起こり易さの頻度を表わす統計的尺度である。シグマ値が大きくなるほど、その方法が欠陥を生じる可能性は低くなる。その結果、バイアを通してダイボンドパッドに達するフレキシブル基板上の相互接続用金属の位置合せは、アイヘルベルガー(Eichelberger)等の米国特許第4835704号明細書中に記載のごとき「適応性リソグラフィー」の使用によって実施されるのが普通である。適応性リソグラフィーは、レーザで穴あけされるバイアの位置に関する「特注」の直接書込みアートワークを作成し、次いで相互接続用金属のパターニングを行うことによってダイ配置誤差に対処し得る方法である。この方法は有効に働くが、それは高価で保守の比較的困難な特注の装置を必要とする。それはまた、処理すべき各々のモジュールに関する固有のアートワークを保存するため非常に大きいデータファイルを必要とする。こうして得られる「適応性」のアートワークはまた、ダイの近傍における相互接続レイアウトの設計規則を制限する。これは、ダイ及びダイボンドパッドの寸法が小さくなるに従って益々重要となる。2007年までには、ダイボンドパッドの寸法は55μのピッチで40μにまで小さくなると推定される。従って、適応性リソグラフィーを用いた相互接続ルーティングは極めて困難になるはずである。

【0007】

1999年9月20日に提出された「加工を低減させるためのHDIチップ結合方法」と称するイー・ダブリュー・バルチ(E.W. Balch)等の米国特許出願明細書中には、接着剤で被覆されたフレキシブル基板中にバイアを予め形成する方法が開示されている。次いで、予め形成されたバイアにダイが位置合せされ、そして接着剤中に配置される。この方法は、ダイ結合用接着剤の流動性に大きく依存する。ボイドの無い結合部を得るためには、チップ・オン・フレックス用として最適のダイ結合用接着剤は硬化時に流れるものである。この方法においては、硬化工程に際して予め形成されたバイア中に接着剤も流れ込み、しかもそれは除去することができない。バイアが開いていなければ、ダイボンドパッドへの接触を達成することができない。ポリイミド中に予め形成されたバイアもまた、ダイ配置時の位置合せにとって最適の構造ではない。

【0008】

更にまた、鋭いバイアかど部を回避することは、信頼性を向上させ、応力を低減させ、かつより能率的な相互接続ルーティング設計を可能にする点で通例有利である。

【0009】

このようなわけで、適応性リソグラフィー及び高価な特注装置の使用を排除しながら、商業的に入手し得る装置を用いてフレキシブル基板上の相互接続用金属にダイを位置合せするための代替方法が得られれば望ましいのである。これの利益の1つは、次世代のダイに対して必要なマルチチップモジュール(MCM)の相互接続ルーティングに対処し得ることである。

【0010】

また、金属パターンやエッチング技術によって決定されるバイア形状を変化させ得るような、矩形以外のバイアを形成するための方法を得ることも望ましい。たとえば、丸いバイアは応力点を持たないので信頼性を向上させることができ、しかもより能率的な相互接続ルーティング設計を可能にする。

【0011】

更にまた、小さなバイアだけではなく大きな領域において電気的性能又は機械的機能を向上させるため、MMIC又はMEMSダイの表面から誘電体を除去する能力を得ることも望ましい。

【0012】

更にまた、各種の方法〔たとえば、RIE(反応イオンエッチング)、プラズマエッチング及びエキシマアブレーション)のうちの任意のものを用いてボンドパッドに達するバイアを形成し得ることも望ましい。

【0013】

【発明の概要】

本発明に実施の一態様に従って簡単に述べれば、フレキシブル基板上に設けられた相互接続用金属にダイを位置合せすることによって少なくとも1個の電子チップパッケージを製造するための方法が提供される。かかる方法は、フレキシブル基板の下面上に設けられたバイアマスク層のパターニングによってバイア形成用のマスクを作成する工程と、バイアマスク層の局所基準点に対して少なくとも1個のダイの少なくとも1個のボンドパッドを適応可能に位置合せする工程とを含むものである。

【0014】

このような方法に従えば、「適応性リソグラフィー」を使用しながら各々のダイの位置狂いに対してフレキシブルな金属アートワークをカスタマイズする必要がなくなる。また、以前のダイ配置状態に合わせて相互接続アートワークを調整するのではなく、相互接続アートワークの局所的な細部に基づいてダイが配置される。更にまた、商業的に入手し得る安価なリソグラフィー装置を加工用として使用することができるため、資本設備及び加工費を低減させることができる。かかる方法は、寸法が40μm程度のボンドパッドを有する次世代のダイの計画的な設計にも適合性を有している。

【0015】

新規であると考えられる本発明の特徴は、前記特許請求の範囲中に明記されている。とは言え、本発明の内容並びにそれの追加の目的及び利点は、添付の図面を参照しながら以下の説明を考察することによって最も良く理解できよう。

【0016】

【好適な実施の態様の詳細な説明】

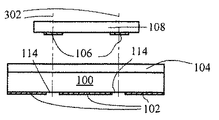

上から下に向かって本発明の実施の一態様に係わるダイ位置合せ方法を図示する図1について説明すれば、先ず最初に工程11においてポリイミドフレックスのごときフレキシブル基板100が用意される。フレキシブル基板100の下面上に金属のバイアマスク層102を蒸着してからパターニングを施すことにより、バイア形成用のマスクが作成される(工程12)。重要なのは、かかるパターンがフレーム上に配置される各々のダイ上に存在する構成要素に正確に対応した局所基準標識を含むことである。詳しく述べれば、ダイドロップ位置のごとき局所基準点114がバイアマスク層102中に直接にパターン形成されている。ダイが配置された後、適応性リソグラフィーを用いてバイアマスク層102を変更する必要は全くない。なぜなら、バイアマスク層が以後に全てのダイ配置や相互接続パターン形成を行うための基準となるからである。

【0017】

次に、ダイ結合用接着剤のごときダイ結合手段104がフレキシブル基板100の上面に塗布される(工程13)。次いで、本発明に係わる新規な「適応性ダイ配置」装置及び方法を使用することにより、ダイ108上に設けられたボンドパッド106が金属のバイアマスク層102中にパターン形成された局所基準点114に対して局所的に位置合せされ、そして(接着剤104のごときダイ結合手段を用いて)高い精度でフレキシブル基板100に結合される(工程14)。なお、本明細書中に開示される適応性ダイ配置方法は図2〜5に関連して一層詳細に説明される。所望ならば、この時点においてかかるモジュールを材料111で封入成形することもできる。そのためには、たとえば、前述の米国特許第5527741号明細書中に記載の方法と同様な方法を使用すればよい。

【0018】

次に、フレキシブル基板100上に存在する位置合せされた金属のバイアマスク層102を通して各種の方法から選ばれた任意の方法(たとえば、プラズマエッチング又はエキシマレーザアブレーション)を実施することにより、ダイボンドパッド106にまで達するバイア110が形成される(工程15)。実際、適応性ダイ配置のためにバイアマスク層102を使用することは、バイア形成のために広範囲の技術を使用し得るという副次的な利益をも有している。

【0019】

最後に、相互接続用金属112が付着され(工程16)、そしてパターニング及びエッチングが施される(工程17)。その結果、工程17後にはフルチップスケールパッケージ又はマルチチップモジュール1が得られることになる。

【0020】

図1中の工程はいずれも同じ方位を有するものとして示されているが、通例、工程12及び15〜17は構造物を逆転することによって一層容易に実施される。更にまた、本明細書中で使用される「上」及び「下」という用語は例示を目的として使用されるものに過ぎない。

【0021】

図2〜5には、工程14の構成を生み出すような適応性ダイ配置方法が示されている。一般に、ダイ配置時の位置狂いには3つの主たる原因が存在する。ダイ配置用フレームの作製は、フレーム上におけるフレキシブル基板100のゆがみを導入することがある。また、ダイ取付ステーション内におけるフレームの配置状態の変動は、フレーム全体に関する並進誤差及び回転誤差を導入することがある。更にまた、それの作業区域を横切るロボット動作の較正及び補間に関する誤差は、ロボット動作の補間に使用される基準点に対するダイの位置狂いをもたらすことがある。

【0022】

適応性ダイ配置方法を使用すれば、これらの誤差に対処して工程14の構成を生み出すことができる。詳しく述べれば、図2に示されるごとく、ダイ108の特定の1対のダイボンドパッド106と、バイアマスク層102中に直接にパターン形成された対応する特定の1対の局所基準標識114(たとえば、図示されたバイアドロップ開口)との間における正確な位置合せ302を達成することが所望される。

【0023】

これを達成するためには、ダイ108が活性表面を下方に向けて装填される。下向きのカメラの焦点がフレーム上の参照標識に合わされる。視覚認識システムにより、フレーム上の参照標識が3段階の階層構造で(すなわち、「大域」基準点、「モジュール」基準点及び「局所」基準点を用いて)決定される。これらの基準点はいずれも、工程12において、バイアマスク層102の一部として形成される。大域基準点は、システムがフレーム全体の大きな位置狂い及び回転を補正することを可能にする荒調整用の標識である。下向きの第1の低倍率カメラが1対の標準化された座標に移動し、そしてそれの視野内において大域基準点を探知する。これら2つの大域基準点により、フレームの位置及び回転が確認される。また、各対のモジュール基準点に関する座標の上方には下方を向いた第2の高倍率カメラ500が配置される。この高倍率カメラによって各対のモジュール基準点が探知される結果、フレームを横切るフレキシブルパターンのゆがみが部分的に補正される。これらの基準点がバイアマスク層102中に形成されたパターンの一部として作成されていることを別にすれば、上記のごとき2つの位置合せ工程はチップ・オン・フレックスモジュールの作製のための標準的な従来技術である。

【0024】

この時点において、本発明に基づく追加の新規な位置合せ工程が実施される。配置すべき各々のダイに関するバイアマスク層102の局所基準点114の上方に下向きの高倍率カメラ500が配置され、そして視覚認識システムがそれらの局所基準点114を与えるそれぞれの標識の位置を探知する(図3参照)。この工程の利点は、各々のダイの配置点をモジュール基準点に基づく補間によって計算する代りに、ダイ配置位置に対応する局所基準点114の標識の実際の位置を使用することにある。それの実例としては、ダイ108上のダイボンドパッド106の所望の配置位置に対応(302)する局所基準点114として役立つ開口(たとえば、バイアドロップ開口)を有する金属層が挙げられる。これらの開口の2つ以上について位置合せを行えば、遠隔の基準点からの補間よりも正確にダイの位置決めを行うことができる。較正誤差、フレキシブルフィルムの局所的なゆがみ、及びその他の微小な誤差原因は排除される。次に、ダイが真空エンドエフェクタ610によって「拾い上げ」られ、そして上向きのカメラ600の上方に配置される(図4参照)。上向きのカメラ600は、局所基準点を探知するために使用された下向きの高倍率カメラ500とほぼ同じ倍率を有している。局所基準点114を表わす探知された標識(たとえば、フレキシブル基板100上のバイアドロップ開口)に対応するダイ108上のボンドパッド106の位置が捕捉される。その結果、真空エンドエフェクタ610に対するダイ108及びダイボンドパッド106の位置及び回転方位が正確に決定される。次いで、ダイ108がフレキシブル基板100上の所望の位置に整合するように並進及び回転され、そしてフレキシブル基板100上のダイ結合手段104に圧着される。

【0025】

詳しく述べれば、図3中に詳細に示されるごとく、下向きのカメラ500は付属の光源から(いずれも半透明である)ダイ結合手段104及びフレキシブル基板100を通して光510を投射する。金属のバイアマスク層102に当った光線は反射されて下向きのカメラ500に戻る一方、局所基準点114(すなわち、バイアドロップ開口)に向かった光線はフレキシブル基板100を通過して戻ることはない。従って、下向きのカメラ500はバイアドロップ開口を検出することができる。模式的に示されているごとく、制御装置502は下向きのカメラ500から視覚認識データを受取り(506)、そして局所基準点114で標識された光線510に対して垂直な平面内におけるバイアドロップ開口の正確な位置及び角方位を決定して記録する。また、好適な実施の態様に従えば、局所基準点114はバイアドロップ開口であって、それらは金属のバイアマスク層102中に直接にパターン形成されていることを強調しておくことが重要である。下向きのカメラ500及びフレキシブル基板100の相対的な位置及び角方位を正確に調整するためのアクチュエータ504は、制御装置502によって制御される(508)。アクチュエータ504は、当業界において公知の数値制御ロボット動作技術を使用するのが通例である。好適な実施の態様に従えば、フレキシブル基板100は固定された位置を占め、そして下向きのカメラ500がそれに対して移動させられる。とは言え実際には、本発明の別の実施の態様に従えば、下向きのカメラ500及びフレキシブル基板100の一方又は両方を絶対運動目盛に基づいて移動させることによって両者間における所望の相対運動を達成し得ることは言うまでもない。また、このような相対運動を達成するための様々な変更態様が当業者にとって自明であり、そしてそれらは本発明の範囲内に含まれると考えられることも勿論である。

【0026】

この時点において、バイアドロップ開口(局所基準点114)に関して確認されかつ制御装置502中に記録された適当な座標を使用しながらダイボンドパッド106を経験的に配置しさえすれば、それらをフレキシブル基板100上のどこに配置すべきかがわかることになる。図4には、実際に上向きのカメラ600を用いてダイボンドパッド106を経験的に配置する方法が示されている。真空エンドエフェクタ610又は適当な代用品若しくは同等品により、ダイボンドパッド106を有するダイ108が拾い上げられる。真空エンドエフェクタ610及び上向きのカメラ600の相対的な位置及び角方位を正確に調整するための追加のアクチュエータ604もまた、制御装置502によって制御される(608)。追加のアクチュエータ604はロボット動作技術を使用するのが通例であって、アクチュエータ504に関して前述したものと同じ考察事項がこの場合にも適用される。上向きのカメラ600もまた、付属の光源から光610を投射する。ダイボンドパッド106から反射された光を使用することにより、真空エンドエフェクタ610の既知の位置及び方位に対するダイボンドパッド106の位置及び角方位が検出される。その結果、制御装置502はバイアドロップ開口(局所基準点114)をダイボンドパッド106と正確に位置合せする(図2参照)ために必要な全ての情報を得たことになる。

【0027】

そこで、図5に示されるごとく、制御装置502は下向きのカメラ500及び上向きのカメラ600によって以前に得られた情報を使用しながら数値制御ロボット動作技術に従ってダイ108及びフレキシブル基板100を作動し(すなわち、移動させ)(508、608)、それによってダイボンドパッド106をフレキシブル基板100上のバイアドロップ開口に位置合せする。次いで、ダイボンドパッド106をフレキシブル基板100(詳しくはダイ結合手段104)に圧着することにより、適応性ダイ配置が完了する。(随意の)封入成形111を施せば、図1中の工程14に示された構造物が得られることになる。

【0028】

本発明は、金属アートワークパターン上の「基準点」に対してダイを配置した後、その位置からフレキシブル基板上にダイを支持すべき位置まで一定のX及びY距離だけ移動させるという非適応性のダイ配置技術に比べて改良されている。移動用のステージが較正されていなかったり、あるいはフレキシブル基板が何らかのゆがみを有していたりすれば、ダイの位置狂いが生じることになる。本発明はまた、誤って配置されたダイボンドパッドが存在する位置を探知し、そしてその位置に合わせてバイアのレーザ穴あけを行うことによって位置狂いのダイを補正する上記のごとき適応性リソグラフィー技術に比べても改良されている。適応性リソグラフィー技術においては、相互接続用金属もまたバイアに合わせて調整されるから、それぞれのアートワークは異なっている。

【0029】

図1〜5に示されるごとく、フレキシブル基板100の下面上に金属のバイアマスク層102を蒸着してからパターニングを施すことによってフレキシブルフィルム上にダイ固有の位置合せ標識を形成し、そしてこれらの標識に対してダイを位置合せしかつ配置するという方法は、本明細書中に開示される適応性のダイ配置を構成するものである。適応性リソグラフィーは全く必要ないのであって、実際に適応性リソグラフィーの排除が本発明の有用な利益の1つであることに注意すべきである。その上、ダイの配置状態を基準として相互接続パターンが補正されるのとは異なり、相互接続パターンを基準としてダイが配置されるのである。

【0030】

ダイ位置合せ標識が実際にはダイボンドパッド106に対するバイアドロップ開口として役立つ局所基準点114を有する連続した金属層(バイアマスク層102)から成るような上記のごとき実施の態様においては、本発明の方法の第2の新規な利益を実現することができる。従来の穴あけ方法においては、351nmのアルゴンイオンレーザを使用することにより、フレキシブルフィルムを貫通してダイボンドパッドにまで達するバイアが逐次操作で形成される。これは長い時間のかかる作業である場合が多く、しかも特にピン数の多い複数のデバイスを組込んだ複合モジュールの場合にそれは顕著となる。この工程はまた、上記のごとく、各々のダイに対する位置合せや各々のダイの位置の記録が必要であることによっても複雑化される。それに対し、上記のごとき適応性ダイ配置用の金属層を用いて製作された同じモジュールは、フレキシブル基板100の下面上に一体化された相似マスク(バイアマスク層102)を既に有している。このマスクを使用することにより、広範囲の方法(たとえば、RIE、プラズマエッチング及びエキシマアブレーション)のうちの任意のものを用いてダイボンドパッドに対する全てのバイアを形成する(工程15)ことができる。これらはいずれも並行方法であるから、バイアを形成するために必要な時間はモジュール上のバイアの数に無関係である。要するに、以後に適応性リソグラフィーによって配置状態を補正する必要なしにダイ108の配置を可能にするものと同じバイアマスク層102が、本来ならばかかる目的のために使用できない(並行方法を含む)広範囲の方法を用いてバイア110を形成することを可能にする相似マスクとしても役立つのである。

【0031】

バイア穴あけ工程に続いて適応性リソグラフィーが必要となるのは、もっぱらフレキシブル基板のゆがみに依存している。なぜなら、ダイ及びバイアがフレキシブル基板上に予め存在する位置合せパターンに対して配置されるからである。

【0032】

フレキシブル基板上にダイを正確に配置するために局所位置合せ標識を使用することの利点は、後続のバイア形成工程用の相似的なバイアマスク層102に対して位置合せを行うことにより、パッドに対するバイアの正確な位置合せが保証されることである。しかも、その際には、(1) 追加の位置合せ/適応操作を繰返す必要がなく、(2) レーザによる逐次のバイア穴あけ操作を行う必要がなく、かつ(3) ダイ結合用接着剤の流動性に依存することがない。本明細書中に開示された相似的な位置合せマスク(バイアマスク層102)は、前述のごとき従来技術の数多い制約を克服するものである。

【0033】

本発明の実験的な実施例として、キャプトン(KAPTON)(デュポン社の登録商標である)から成るポリイミドフレックス(厚さ0.5ミル)の両面を金属被覆し〔上層は厚さ120AのTiから成り、また下層は厚さ4.3μのブライト(Brite) Cuから成る〕、そしてパターニング及びエッチングを施した。上側(ダイ側)には試験用の相互接続パターンをパターン形成し、また下側にはバイア開口をパターン形成した。金属のエッチングを行った後、ダイ結合用接着剤を塗布した。次いで、適応性ダイ配置方法を使用しながら、パターン形成されたバイア開口と整列するようにしてダイを結合した。こうして得られた位置合せの精度を図7に示す。適応性ダイ配置方法は25μのターゲットの範囲内においてZst=5.98σで実施することができるが、これは図6に示される非適応性の方法についてはZst=1.79σであるのに比べて顕著な改善を示している。

【0034】

配置後、ダイ結合用接着剤を硬化させた。次いで、2つの方法を使用しながら、既に位置合せされた金属のバイアマスク中の開口を通してバイアを形成した。2つの方法とは、エキシマレーザアブレーション(248nmのKrFIエキシマ、130mJ、300レプ)及び反応イオンエッチング(36sccmCF4/4sccmO2、155ミリトル、500W)であった。

【0035】

反応イオンエッチングを用いて形成されたバイアは、エキシマアブレーションによって形成されたバイアよりも大きい。これは、使用したRIE条件下では横方向のエッチングが起こるためであった。異方性のより大きいエッチングも可能であるが、それはとりわけ鋭いバイアかど部を回避し得るという利点をもたらす。

【0036】

本発明の好適な実施の態様においては、フレキシブル基板100及びダイ108の特定の方位に関連して下向きのカメラ500及び上向きのカメラ600が使用されているが、それほど好適ではないものの、逆転された方位又はその他の方位を有する実施の態様もやはり本発明の範囲内に含まれることは言うまでもない。従って、下向きのカメラ500は第1のカメラ500として一般化されるのであって、これは下方を向いているのが好ましいが、他の実施の態様に従って異なる方位を有していてもよい。また、上向きのカメラ600は第2のカメラ600として一般化されるのであって、これは上方を向いているのが好ましいが、他の実施の態様に従って異なる方位を有していてもよい。

【0037】

以上、特定の好適な実施の態様のみに関連して本発明を説明したが、当業者には数多くの変更例、変形例及び置換例が想起されるであろう。それ故、本発明の精神に反しない限り、前記特許請求の範囲はかかる変更例及び変形例の全てを包括するように意図されていることを理解すべきである。

【図面の簡単な説明】

【図1】本発明の実施の一態様に従ってフレキシブル基板上の相互接続用金属にダイを位置合せするための方法の様々な工程を示す一連の平面図である。

【図2】フレキシブル基板の金属マスク層中にパターン形成されたバイアドロップ開口に対するダイ及びそれのダイボンドパッドの所望の位置合せ状態を示す平面図である。

【図3】下向きのカメラを用いてダイボンドパッドと位置合せすべきバイアドロップ開口を正確に位置決めする方法を示す平面図と模式図との混成図である。

【図4】上向きのカメラを用いることにより、図3において位置決めされたバイアドロップ開口と位置合せすべきダイボンドパッドの位置を正確に決定する方法を示す平面図と模式図との混成図である。

【図5】図4及び5の工程に続き、ダイボンドパッドをバイアドロップ開口と位置合せしかつそれに圧着する方法を示す平面図と模式図との混成図である。

【図6】従来の方法によって得られるダイ配置の精度を示すグラフである。

【図7】本発明の実験的な実施例によって得られるダイ配置の精度の向上を示すグラフである。

【符号の説明】

1 電子チップパッケージ

100 フレキシブル基板

102 バイアマスク層

104 ダイ結合手段

106 ボンドパッド

108 ダイ

110 バイア

112 相互接続用金属

114 局所基準点

500 第1のカメラ

502 制御装置

508 アクチュエータ

600 第2のカメラ

608 アクチュエータ

Claims (6)

- フレキシブル基板(100)上のバイアマスク層(102)にダイ(108)を位置合せする(302)ことによって少なくとも1個の電子チップパッケージ(1)を製造するための方法において、

前記フレキシブル基板(100)の下面上に設けられた前記バイアマスク層(102)のパターニングによってバイア形成用のマスクを作成する(12)工程と、

前記バイアマスク層(102)のバイアドロップ開口となる少なくとも1つの局所基準点(114)に対して少なくとも1個の前記ダイ(108)の少なくとも1個のボンドパッド(106)を位置合せする(302)工程と、

前記フレキシブル基板(100)の上面に前記少なくとも1個のボンドパッド(106)を結合する(13、14、104)工程と、

前記バイアドロップ開口の位置において前記フレキシブル基板(100)の前記下面から前記ボンドパッド(106)にまで達するバイア(110)を形成する(15)工程と、

を含むことを特徴とする方法。 - 前記フレキシブル基板(100)の前記下面上に相互接続用金属(112)を付着し(16)かつパターニング及びエッチングを施す(17)工程を更に含む請求項1記載の方法。

- 前記バイア(110)を形成する(15)前記工程が、エキシマレーザアブレーション又はプラズマエッチングによって前記バイア(110)を形成することから成る請求項1又は2に記載の方法。

- 前記ボンドパッド(106)を結合する前記工程が、接着剤を使用する、請求項1乃至3のいずれかに記載の方法。

- 前記局所基準点(114)に対して前記ボンドパッド(106)を適応可能に位置合せする(302)前記工程が、第1のカメラ(500)を用いて前記局所基準点(114)の位置を前記フレキシブル基板(100)を通して探知し、第2のカメラ(600)を用いて前記ボンドパッド(106)の位置を探知し、そして制御装置(502)及びアクチュエータ(508、608)を使用しながら前記第1のカメラ(500)によって探知された前記局所基準点(114)の位置及び前記第2のカメラ(600)によって探知された前記ボンドパッド(106)の位置に基づいて前記ボンドパッド(106)及び前記局所基準点(114)を互いに適応可能に位置合せする(302)ことから成る請求項1乃至4のいずれかに記載の方法。

- フレキシブル基板(100)の下面上のバイアマスク層(102)にダイ(108)を位置合せする(302)ことによって少なくとも1個の電子チップ(1)を製造するための装置において、

前記フレキシブル基板(100)の下面上に設けられた前記バイアマスク層(102)のパターニングによってバイアドロップ開口となる局所基準点(114)を有するバイア形成用のマスクを作成する手段と、

前記バイアマスク層(102)の局所基準点(114)の位置を探知するための第1のカメラ(500)と、前記ダイ(108)のボンドパッド(106)の位置を探知するための第2のカメラ(600)と、前記第1のカメラ(500)によって探知された前記局所基準点(114)の位置及び前記第2のカメラ(600)によって探知された前記ボンドパッド(106)の位置に基づいて前記ボンドパッド(106)及び前記局所基準点(114)を位置合せする(302)ための制御装置(502)及びアクチュエータ(508、608)とを含み、

前記制御装置(502)及び前記アクチュエータ(508、608)が前記フレキシブル基板(100)の上面に前記少なくとも1個のボンドパッド(106)を結合する(13、14、104)ための位置合せを行い、

前記バイアドロップ開口の位置において前記フレキシブル基板(100)の前記下面から前記ボンドパッド(106)にまで達するバイア(110)が形成される、装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/469749 | 1999-12-22 | ||

| US09/469,749 US6475877B1 (en) | 1999-12-22 | 1999-12-22 | Method for aligning die to interconnect metal on flex substrate |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001250888A JP2001250888A (ja) | 2001-09-14 |

| JP2001250888A5 JP2001250888A5 (ja) | 2008-02-14 |

| JP4931277B2 true JP4931277B2 (ja) | 2012-05-16 |

Family

ID=23864927

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000388006A Expired - Lifetime JP4931277B2 (ja) | 1999-12-22 | 2000-12-21 | フレキシブル基板上の相互接続用金属にダイを位置合せするための装置及び方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6475877B1 (ja) |

| EP (1) | EP1111662B1 (ja) |

| JP (1) | JP4931277B2 (ja) |

| CN (1) | CN1199250C (ja) |

| TW (1) | TW490716B (ja) |

Families Citing this family (63)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6888240B2 (en) | 2001-04-30 | 2005-05-03 | Intel Corporation | High performance, low cost microelectronic circuit package with interposer |

| US6894399B2 (en) | 2001-04-30 | 2005-05-17 | Intel Corporation | Microelectronic device having signal distribution functionality on an interfacial layer thereof |

| US7071024B2 (en) | 2001-05-21 | 2006-07-04 | Intel Corporation | Method for packaging a microelectronic device using on-die bond pad expansion |

| US7183658B2 (en) * | 2001-09-05 | 2007-02-27 | Intel Corporation | Low cost microelectronic circuit package |

| JP3645511B2 (ja) * | 2001-10-09 | 2005-05-11 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| FI115285B (fi) * | 2002-01-31 | 2005-03-31 | Imbera Electronics Oy | Menetelmä komponentin upottamiseksi alustaan ja kontaktin muodostamiseksi |

| FI119215B (fi) * | 2002-01-31 | 2008-08-29 | Imbera Electronics Oy | Menetelmä komponentin upottamiseksi alustaan ja elektroniikkamoduuli |

| US8455994B2 (en) * | 2002-01-31 | 2013-06-04 | Imbera Electronics Oy | Electronic module with feed through conductor between wiring patterns |

| US6964881B2 (en) * | 2002-08-27 | 2005-11-15 | Micron Technology, Inc. | Multi-chip wafer level system packages and methods of forming same |

| US6855953B2 (en) * | 2002-12-20 | 2005-02-15 | Itt Manufacturing Enterprises, Inc. | Electronic circuit assembly having high contrast fiducial |

| US7263677B1 (en) * | 2002-12-31 | 2007-08-28 | Cadence Design Systems, Inc. | Method and apparatus for creating efficient vias between metal layers in semiconductor designs and layouts |

| US8222723B2 (en) | 2003-04-01 | 2012-07-17 | Imbera Electronics Oy | Electric module having a conductive pattern layer |

| FI115601B (fi) * | 2003-04-01 | 2005-05-31 | Imbera Electronics Oy | Menetelmä elektroniikkamoduulin valmistamiseksi ja elektroniikkamoduuli |

| US8704359B2 (en) | 2003-04-01 | 2014-04-22 | Ge Embedded Electronics Oy | Method for manufacturing an electronic module and an electronic module |

| CN1302541C (zh) * | 2003-07-08 | 2007-02-28 | 敦南科技股份有限公司 | 具有柔性电路板的芯片封装基板及其制造方法 |

| FI20031201A (fi) * | 2003-08-26 | 2005-02-27 | Imbera Electronics Oy | Menetelmä elektroniikkamoduulin valmistamiseksi ja elektroniikkamoduuli |

| FI20031341A (fi) | 2003-09-18 | 2005-03-19 | Imbera Electronics Oy | Menetelmä elektroniikkamoduulin valmistamiseksi |

| TWI237883B (en) * | 2004-05-11 | 2005-08-11 | Via Tech Inc | Chip embedded package structure and process thereof |

| FI117814B (fi) * | 2004-06-15 | 2007-02-28 | Imbera Electronics Oy | Menetelmä elektroniikkamoduulin valmistamiseksi |

| TWI250596B (en) * | 2004-07-23 | 2006-03-01 | Ind Tech Res Inst | Wafer-level chip scale packaging method |

| US8487194B2 (en) * | 2004-08-05 | 2013-07-16 | Imbera Electronics Oy | Circuit board including an embedded component |

| FI117812B (fi) * | 2004-08-05 | 2007-02-28 | Imbera Electronics Oy | Komponentin sisältävän kerroksen valmistaminen |

| FI117369B (fi) | 2004-11-26 | 2006-09-15 | Imbera Electronics Oy | Menetelmä elektroniikkamoduulin valmistamiseksi |

| CN100541767C (zh) * | 2005-01-28 | 2009-09-16 | 松下电器产业株式会社 | 电子元件封装的制造方法以及电子元件封装 |

| FI122128B (fi) * | 2005-06-16 | 2011-08-31 | Imbera Electronics Oy | Menetelmä piirilevyrakenteen valmistamiseksi |

| WO2006134220A1 (en) | 2005-06-16 | 2006-12-21 | Imbera Electronics Oy | Method for manufacturing a circuit board structure, and a circuit board structure |

| FI119714B (fi) | 2005-06-16 | 2009-02-13 | Imbera Electronics Oy | Piirilevyrakenne ja menetelmä piirilevyrakenteen valmistamiseksi |

| US20070012965A1 (en) * | 2005-07-15 | 2007-01-18 | General Electric Company | Photodetection system and module |

| JP4487875B2 (ja) * | 2005-07-20 | 2010-06-23 | セイコーエプソン株式会社 | 電子基板の製造方法及び電気光学装置の製造方法並びに電子機器の製造方法 |

| US9601474B2 (en) * | 2005-07-22 | 2017-03-21 | Invensas Corporation | Electrically stackable semiconductor wafer and chip packages |

| KR100785014B1 (ko) * | 2006-04-14 | 2007-12-12 | 삼성전자주식회사 | Soi웨이퍼를 이용한 mems 디바이스 및 그 제조방법 |

| JP5091600B2 (ja) * | 2006-09-29 | 2012-12-05 | 三洋電機株式会社 | 半導体モジュール、半導体モジュールの製造方法および携帯機器 |

| US7579215B2 (en) * | 2007-03-30 | 2009-08-25 | Motorola, Inc. | Method for fabricating a low cost integrated circuit (IC) package |

| US20080318413A1 (en) * | 2007-06-21 | 2008-12-25 | General Electric Company | Method for making an interconnect structure and interconnect component recovery process |

| US20080318055A1 (en) * | 2007-06-21 | 2008-12-25 | General Electric Company | Recoverable electronic component |

| US20080318054A1 (en) * | 2007-06-21 | 2008-12-25 | General Electric Company | Low-temperature recoverable electronic component |

| US20080313894A1 (en) * | 2007-06-21 | 2008-12-25 | General Electric Company | Method for making an interconnect structure and low-temperature interconnect component recovery process |

| US9610758B2 (en) * | 2007-06-21 | 2017-04-04 | General Electric Company | Method of making demountable interconnect structure |

| US9953910B2 (en) * | 2007-06-21 | 2018-04-24 | General Electric Company | Demountable interconnect structure |

| US20090028491A1 (en) | 2007-07-26 | 2009-01-29 | General Electric Company | Interconnect structure |

| CN101373748B (zh) * | 2007-08-20 | 2011-06-15 | 宏茂微电子(上海)有限公司 | 晶圆级封装结构及其制作方法 |

| JP4966156B2 (ja) * | 2007-10-23 | 2012-07-04 | ソニーケミカル&インフォメーションデバイス株式会社 | 配線基板の受台及びこれを用いた配線基板の接続装置、接続方法 |

| WO2009081746A1 (ja) * | 2007-12-21 | 2009-07-02 | Tokyo Seimitsu Co., Ltd. | ダイシング装置及びダイシング方法 |

| JP4840373B2 (ja) * | 2008-01-31 | 2011-12-21 | カシオ計算機株式会社 | 半導体装置およびその製造方法 |

| FI123205B (fi) | 2008-05-12 | 2012-12-31 | Imbera Electronics Oy | Piirimoduuli ja menetelmä piirimoduulin valmistamiseksi |

| CN102204418B (zh) | 2008-10-30 | 2016-05-18 | At&S奥地利科技及系统技术股份公司 | 用于将电子部件集成到印制电路板中的方法 |

| US7964974B2 (en) | 2008-12-02 | 2011-06-21 | General Electric Company | Electronic chip package with reduced contact pad pitch |

| US8008781B2 (en) | 2008-12-02 | 2011-08-30 | General Electric Company | Apparatus and method for reducing pitch in an integrated circuit |

| US7897481B2 (en) * | 2008-12-05 | 2011-03-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | High throughput die-to-wafer bonding using pre-alignment |

| WO2011065062A1 (ja) * | 2009-11-30 | 2011-06-03 | シャープ株式会社 | フレキシブル回路基板およびその製造方法 |

| US8623689B2 (en) * | 2010-07-07 | 2014-01-07 | Ineffable Cellular Limited Liability Company | Package process of backside illumination image sensor |

| JP5399542B2 (ja) * | 2012-08-08 | 2014-01-29 | 富士通株式会社 | 半導体装置の製造方法 |

| JP5554380B2 (ja) * | 2012-08-08 | 2014-07-23 | 富士通株式会社 | 半導体装置 |

| JP5624699B1 (ja) * | 2012-12-21 | 2014-11-12 | パナソニック株式会社 | 電子部品パッケージおよびその製造方法 |

| US9595651B2 (en) | 2012-12-21 | 2017-03-14 | Panasonic Intellectual Property Management Co., Ltd. | Electronic component package and method for manufacturing same |

| WO2014097641A1 (ja) * | 2012-12-21 | 2014-06-26 | パナソニック株式会社 | 電子部品パッケージおよびその製造方法 |

| WO2014097642A1 (ja) * | 2012-12-21 | 2014-06-26 | パナソニック株式会社 | 電子部品パッケージおよびその製造方法 |

| JP5624698B1 (ja) * | 2012-12-21 | 2015-11-12 | パナソニック株式会社 | 電子部品パッケージおよびその製造方法 |

| DE102015214219A1 (de) * | 2015-07-28 | 2017-02-02 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines Bauelements und ein Bauelement |

| JP2017073472A (ja) * | 2015-10-07 | 2017-04-13 | 株式会社ディスコ | 半導体装置の製造方法 |

| US10867959B2 (en) * | 2016-11-30 | 2020-12-15 | Shenzhen Xiuyuan Electronic Technology Co., Ltd | Integrated circuit packaging method and integrated packaged circuit |

| EP3557608A1 (en) | 2018-04-19 | 2019-10-23 | AT & S Austria Technologie & Systemtechnik Aktiengesellschaft | Packaged integrated circuit with interposing functionality and method for manufacturing such a packaged integrated circuit |

| EP3833164A1 (en) | 2019-12-05 | 2021-06-09 | AT & S Austria Technologie & Systemtechnik Aktiengesellschaft | Compensating misalignment of component carrier feature by modifying target design concerning correlated component carrier feature |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4933042A (en) | 1986-09-26 | 1990-06-12 | General Electric Company | Method for packaging integrated circuit chips employing a polymer film overlay layer |

| US4783695A (en) | 1986-09-26 | 1988-11-08 | General Electric Company | Multichip integrated circuit packaging configuration and method |

| US4835704A (en) | 1986-12-29 | 1989-05-30 | General Electric Company | Adaptive lithography system to provide high density interconnect |

| US5192716A (en) | 1989-01-25 | 1993-03-09 | Polylithics, Inc. | Method of making a extended integration semiconductor structure |

| US5055907A (en) * | 1989-01-25 | 1991-10-08 | Mosaic, Inc. | Extended integration semiconductor structure with wiring layers |

| JP2803221B2 (ja) | 1989-09-19 | 1998-09-24 | 松下電器産業株式会社 | Ic実装装置及びその方法 |

| US5194948A (en) * | 1991-04-26 | 1993-03-16 | At&T Bell Laboratories | Article alignment method and apparatus |

| JPH05152794A (ja) * | 1991-11-29 | 1993-06-18 | Sharp Corp | Icチツプ実装装置 |

| JPH06338538A (ja) * | 1993-05-28 | 1994-12-06 | Nippon Chemicon Corp | 半導体素子の接続方法 |

| US5527741A (en) * | 1994-10-11 | 1996-06-18 | Martin Marietta Corporation | Fabrication and structures of circuit modules with flexible interconnect layers |

| JPH09232363A (ja) * | 1996-02-23 | 1997-09-05 | Toshiba Corp | 半導体チップの位置合せ方法およびボンディング装置 |

| GB9610689D0 (en) * | 1996-05-22 | 1996-07-31 | Int Computers Ltd | Flip chip attachment |

| US5920123A (en) | 1997-01-24 | 1999-07-06 | Micron Technology, Inc. | Multichip module assembly having via contacts and method of making the same |

| JP3160252B2 (ja) * | 1997-12-11 | 2001-04-25 | イビデン株式会社 | 多層プリント配線板の製造方法 |

| JP3919972B2 (ja) * | 1998-07-31 | 2007-05-30 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| US6246010B1 (en) * | 1998-11-25 | 2001-06-12 | 3M Innovative Properties Company | High density electronic package |

| US6284564B1 (en) | 1999-09-20 | 2001-09-04 | Lockheed Martin Corp. | HDI chip attachment method for reduced processing |

| US6242282B1 (en) * | 1999-10-04 | 2001-06-05 | General Electric Company | Circuit chip package and fabrication method |

| US6271469B1 (en) * | 1999-11-12 | 2001-08-07 | Intel Corporation | Direct build-up layer on an encapsulated die package |

-

1999

- 1999-12-22 US US09/469,749 patent/US6475877B1/en not_active Expired - Lifetime

-

2000

- 2000-12-11 TW TW089126381A patent/TW490716B/zh not_active IP Right Cessation

- 2000-12-21 EP EP00311553A patent/EP1111662B1/en not_active Expired - Lifetime

- 2000-12-21 JP JP2000388006A patent/JP4931277B2/ja not_active Expired - Lifetime

- 2000-12-22 CN CNB001364499A patent/CN1199250C/zh not_active Expired - Lifetime

-

2002

- 2002-07-22 US US10/199,296 patent/US6790703B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6475877B1 (en) | 2002-11-05 |

| CN1301039A (zh) | 2001-06-27 |

| US6790703B2 (en) | 2004-09-14 |

| TW490716B (en) | 2002-06-11 |

| EP1111662A3 (en) | 2003-10-01 |

| EP1111662B1 (en) | 2012-12-12 |

| EP1111662A2 (en) | 2001-06-27 |

| JP2001250888A (ja) | 2001-09-14 |

| US20020197767A1 (en) | 2002-12-26 |

| CN1199250C (zh) | 2005-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4931277B2 (ja) | フレキシブル基板上の相互接続用金属にダイを位置合せするための装置及び方法 | |

| US6255726B1 (en) | Vertical interconnect process for silicon segments with dielectric isolation | |

| US6188126B1 (en) | Vertical interconnect process for silicon segments | |

| US7019223B2 (en) | Solder resist opening to define a combination pin one indicator and fiducial | |

| US6080596A (en) | Method for forming vertical interconnect process for silicon segments with dielectric isolation | |

| US6177296B1 (en) | Method for forming vertical interconnect process for silicon segments with thermally conductive epoxy preform | |

| US5923539A (en) | Multilayer circuit substrate with circuit repairing function, and electronic circuit device | |

| EP1029360A2 (en) | Vertical interconnect process for silicon segments with dielectric isolation | |

| US6975040B2 (en) | Fabricating semiconductor chips | |

| US7030508B2 (en) | Substrate for semiconductor package and wire bonding method using thereof | |

| US6954272B2 (en) | Apparatus and method for die placement using transparent plate with fiducials | |

| JP4100728B2 (ja) | 電気的相互接続を行う適応方法及び装置 | |

| JPH11154694A (ja) | ウェハ一括型測定検査用アライメント方法およびプローブカードの製造方法 | |

| JP3301112B2 (ja) | マルチチップパッケージ型半導体装置の製造方法 | |

| JPH10160793A (ja) | ベアチップ検査用プローブ基板及びその製造方法、及びベアチップ検査システム | |

| JP2001332677A (ja) | 半導体装置の製造方法 | |

| JPS60110128A (ja) | 多層基板および多層基板のワイヤボンディング方法 | |

| JPH04106967A (ja) | 高密度相互接続回路及び製造方法 | |

| JPH088281B2 (ja) | フィルムキャリア製造用のフィルム材 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071220 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071220 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100201 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101013 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101019 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111101 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120124 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120214 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4931277 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150224 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |