JP4636461B2 - 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 - Google Patents

電源電圧監視回路、および該電源電圧監視回路を備える電子回路 Download PDFInfo

- Publication number

- JP4636461B2 JP4636461B2 JP2009005214A JP2009005214A JP4636461B2 JP 4636461 B2 JP4636461 B2 JP 4636461B2 JP 2009005214 A JP2009005214 A JP 2009005214A JP 2009005214 A JP2009005214 A JP 2009005214A JP 4636461 B2 JP4636461 B2 JP 4636461B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- circuit

- signal

- voltage

- supply voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000012544 monitoring process Methods 0.000 title claims description 100

- 238000001514 detection method Methods 0.000 claims description 185

- 230000007704 transition Effects 0.000 claims description 47

- 239000003990 capacitor Substances 0.000 claims description 11

- 230000001747 exhibiting effect Effects 0.000 claims description 2

- 238000010586 diagram Methods 0.000 description 29

- 230000008859 change Effects 0.000 description 16

- 238000005513 bias potential Methods 0.000 description 15

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical group [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 12

- 230000009471 action Effects 0.000 description 8

- 230000000630 rising effect Effects 0.000 description 8

- 238000000034 method Methods 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 230000007423 decrease Effects 0.000 description 4

- 230000004044 response Effects 0.000 description 3

- 230000001052 transient effect Effects 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 238000003780 insertion Methods 0.000 description 1

- 230000037431 insertion Effects 0.000 description 1

- 238000009434 installation Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

Description

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができる。このため、例えば、IC等の最低動作電源電圧仕様を低電圧化することが可能になる。

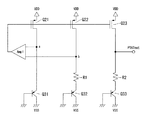

図1は、本発明の第1の実施形態による電源電圧監視回路を示す概略構成図である。

電源電圧監視回路50は、信号出力回路1と、信号電圧監視回路4とで構成される。また、電源電圧監視回路50の出力信号は、後続するアプリケーション回路6に出力される。また、信号出力回路1の出力信号もアプリケーション回路6において使用される場合もある。

また、PMOSトランジスタQ21のドレインにエミッタが接続されると共に、コレクタとベースが基準電位VSSに共通接続されるバイポーラ型のPNPトランジスタQ31と、PMOSトランジスタQ22のドレインに抵抗R1を介してエミッタが接続されると共に、コレクタとベースが基準電位VSSに共通接続されるバイポーラトランジスタQ32を有している。

ここで、「Vt=KT/q、K:ボルツマン定数、T:絶対温度、q:電子の電荷量」

で表され、出力電圧PTAToutは絶対温度Tに比例する電圧として出力される。

時刻t1において、信号出力回路1および信号電圧監視回路4に電源が投入される。その後、電源電圧VDDが徐々に上昇する。同じ電源から電力が供給される信号出力回路1の出力である信号電圧Vsigは、電源電圧VDDが低い状態では、電流源回路2の働きにより出力電圧は電源電圧VDDになる。すなわち、信号電圧Vsigは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができる。また、電源電圧VDDが所定の電圧になることを持つことなく、例え、定格動作電圧よりもかなり低い電圧であっても、この電源電圧において回路動作を許可することが可能になる。

これにより、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

これにより、例えば、温度検出用のダイオード等の温度センサの検出信号を信号電圧Vsigとし、この信号電圧Vsigを電源電圧VDDと比較して、信号電圧Vsigが正常であること示す信号Voutを出力することができる。

これにより、電子化路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

これにより、信号出力回路からの信号とオフセット電位とを基に、電子回路における最低動作電源電圧を容易に検出することができる。

これにより、例えば、インピーダンス回路として順方向にバイアスされたダイード等を使用して信号出力回路1を容易に構成することができる。また、インピーダンス回路を温度センサ等で構成することができる。

これにより、センサからの出力信号を検出対象として、センサが安定して動作できる電源電圧のレベルを検出することができる。このため、センサが安定して動作できる電圧を電子回路の最低動作電源電圧とすることができ、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

これにより、温度センサからの出力信号を検出対象として、この温度センサが安定して動作できる電源電圧のレベルを検出することができる。このため、温度センサが安定して動作できる電圧を電子回路の最低動作電源電圧とすることができ、電子回路における最低動作電源電圧の低電圧化を図り、電源電圧を効率的に利用することができるようになる。

図7は、第2実施形態による検出回路を示す概略構成図である。この第2の実施の形態では、図1に示す第1の実施の形態の電源電圧監視回路の応用例であり、温度センサ等の信号を検出する検出回路の例を示したものである。

検出回路100における割込条件生成回路10aは、2つの入力端子(Tip、Tin)と出力端子Toを有する。割込条件生成回路10aは、入力される2つの信号の電位を比較し、その電位差が所定の値以上であるか否かを検出し、検出結果を2値化された論理信号によって出力する。

オフセットコンパレータ11では、入力端子Tinがバイアス電圧源11bを介してコンパレータ11cの反転入力端に接続され、入力端子Tipがコンパレータ11cの非反転入力端に接続され、コンパレータ11cの出力端が出力端子Toに接続される。

入力端子Tinに入力される信号は、バイアス電圧源11bによりバイアス電位Vb分だけ高い電位に変換され、コンパレータ11cに入力される。

このような構成をとることにより、オフセットコンパレータ11は、入力端子Tipに入力された信号の電圧が、入力端子Tinに入力された信号の電圧より、所定の電圧(バイアス電位Vb)分だけ高くなった閾値電圧により比較される。入力端子Tipに入力される信号の電位が、入力端子Tinに入力される信号の電位にバイアス電位Vbを加算した電圧より低い状態から高い状態に遷移すると出力信号が反転する。その出力信号は、前者の状態(バイアス電位Vbを加算した電圧より低い状態)では、ローレベルを示す。

割込条件生成回路10aからは、オフセットコンパレータ11の出力と同じ信号が出力される。

割込条件受付回路20aの一形態として出力設定回路21を示す。出力設定回路21は、インバータ(反転回路)21a及びNAND(反転論理積)ゲート21bを備える。出力設定回路21では、信号入力端子InがNANDゲート21bの一方の入力端に接続され、制御入力端子ContがNANDゲート21bの他方の入力端に接続され、NANDゲート21bの出力端がインバータ21aを介して出力端子Outに接続される。このような構成をとることにより、制御入力端子Contに入力される制御信号Scontがローレベルの場合には、出力信号Voutがローレベルに設定され、制御信号Scontがローレベルの場合には、入力される信号Sgと同じ論理を示す信号が出力信号Voutに出力される。すなわち、割込条件受付回路20aは、制御信号として入力される割込信号による割込みが解除されるまで、入力される信号Sgの出力を許可せずローレベルを示す所定の電圧を出力信号Voutとして出力する。また、割込条件受付回路20aは、割込信号による割込みが解除されると、入力される信号Sgの出力を許可して出力信号Voutとして出力する。

コンパレータ30は、入力される2つの信号の電位差を検出し、検出した電位差に基づいて判定した結果を2値化した論理信号で出力する。

割込条件生成回路10aにおける入力端子Tipには、電源が接続され電源電圧VDDが入力される。また、入力端子Tinには、図示されないセンサ回路の出力端が接続される。

コンパレータ30における非反転入力端子には、基準電圧Vrefを出力する図示されない基準電源RFが接続され、反転入力端子には、図示されないセンサ回路の出力端が接続される。

割込条件受付回路20aにおける入力端子Inにはコンパレータ30の出力端が接続され、制御入力端子Contには割込条件生成回路10aの出力端子Toが接続され、出力端子Toが検出回路100の出力端子に接続される。

コンパレータ30の出力信号Sgは、入力信号Vtempの電圧が基準電圧Vrefより低い場合にはハイレベルを示す。また、入力信号Vtempの電圧が基準電圧Vrefより高い場合にはローレベルを示す。

割込条件受付回路20aの出力信号Voutには、制御信号Scontがローレベルの場合には、固定的にローレベルが出力され、制御信号Scontがハイレベルの場合には、入力信号Vtempに応じて変化するコンパレータ30からの出力信号Sgが出力される。

点Aの波形は、センサ回路から入力され、検出回路100が検出処理をする入力信号Vtempの電圧遷移を示す。点Bの波形は、検出回路100に供給される電源電圧VDDの電圧遷移を示す。この電源電圧VDDは、検出回路100並びに図7に図示されていない基準電源RF及びセンサ回路に供給されている電源電圧を示す。点Cの波形は、割込条件生成回路10aにおけるオフセットコンパレータ11によって判定され、割込条件生成回路10aから出力された制御信号Scontの電圧遷移を示す。この信号に基づいて、割込条件受付回路20aが制御される。点Fの波形は、基準電源RFから出力される基準電圧Vrefの電圧遷移を示す。点Gの波形は、コンパレータ30による判定結果である出力信号Sgの電圧遷移を示す。この信号は、割込条件受付回路20aへの入力信号になる。点Hの波形は、割込条件受付回路20aの出力信号Voutの電圧遷移を示す。このタイミングチャートに示される範囲では、センサ回路によって検出すべき事象は生じていない状態を示し、出力信号Voutは、常時ローレベルを示す。

時刻t1において、検出回路100並びに検出回路100に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。

その後、電源電圧VDDが徐々に上昇する。同じ電源から電力が供給されるセンサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧VDDになる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路10aでは、入力される信号の判定に一方の信号にオフセット電位を印加して比較することにより、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから出力信号がハイレベルとローレベルを交互に出力してばたつくような不安定な状態となることはない。このため制御信号Scontは、ローレベルを示す。

一方、割込条件受付回路20aは、電源電圧が所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号Voutとして出力する。出力信号Voutとして出力される所定の電圧は、センサ回路において非検出状態(解除状態)を示す電圧が設定され、制御信号Scontに応じて制御される。制御信号Scontには、ローレベルが出力されていることにより、出力信号Voutがローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

割込条件生成回路10aでは、入力信号Vtempは電源電圧VDDの上昇にしたがって上昇するため、その電位差が小さな状態にある。一方の信号にはオフセット電位が印加されていることにより、出力される制御信号Scontは、ローレベルに確定している。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDの上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい2つの信号を比較して得られる出力信号Sgは、信号の状態を特定できない不定状態が継続する。割込条件受付回路20aでは、制御信号Scontがローレベルに確定していることにより、出力信号Voutがローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

基準電圧Vrefが所定の電圧を示すようになり、基準電圧Vrefは入力信号Vtempより低い電位を示すことから、出力信号Sgは、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号Scontによる制御が継続されることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

時刻t5では、センサ回路からの入力信号Vtempと電源電圧VDDとに、所定の電位差、すなわち割込条件生成回路10aにおけるオフセット電位の電圧以上の電位差が生じることを、割込条件生成回路10aによって検出される。その検出によって、電源電圧VDDがセンサ回路に動作可能な電源電圧が供給される状態に遷移したことが示される。割込条件生成回路10aでは、制御信号Scontの割込み状態(ローレベル)を解除することにより、制御信号Scontの電圧が電源電圧VDDの電位上昇にともなって上昇する。

時刻t6では、電源電圧VDDが所定の動作可能電源電圧に達して上昇が止まり、電源電圧VDDが一定値を示すようになる。また、制御信号Scontの電圧上昇も止まり一定値を示す状態に遷移する。

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧VDDが所定の動作可能電源電圧に達するまで、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

図を参照し、形態の異なる検出回路の実施形態について示す。

図9は、第3実施形態による検出回路を示す概略構成図である。図9に示す例では、図7に示す第2の実施の形態における割込条件生成回路10a(図1に示す信号電圧監視回路4と同じ構成の回路)に代えて、POC(Power On Clear)回路12を使用する例を示したものである。これは、後述する実施の形態の説明において、図9に示すPOC回路12と、図7に示す割込条件生成回路10aとを併用して使用する場合があるため、ここでPOC回路12を使用する検出回路の例について説明しておくものである。

検出回路200における割込条件生成回路10bは、電源投入時に所定時間の間、初期状態を保持する信号を出力する。割込条件生成回路10bは、POC(Power On Clear)回路12からなる。POC回路12は、いわゆる電源投入初期化回路である。

POC回路12は、直列に接続されたコンデンサ12Cと抵抗12Rは、電源(電源電圧VDD)にコンデンサ12Cの一端が接続され、基準となる電源(接地電圧VSS)に抵抗12Rの一端が接続される。コンデンサ12Cと抵抗12Rの接続点は、インバータ(NOT回路)12aの入力端に接続され、インバータ12aが割込条件生成回路10bの制御信号Scontを出力する。

この割込条件生成回路10bの出力は、割込条件受付回路20aの制御入力端子Contに接続される。

コンパレータ30の出力信号Sgは、入力信号Vtempの電圧が基準電圧Vrefより低い場合にはハイレベルを示す。また、コンパレータ30の出力信号Sgは、入力信号Vtempの電圧が基準電圧Vrefより高い場合にはローレベルを示す。

割込条件受付回路20aの出力信号Voutは、制御信号Scontがローレベルの場合には固定的にローレベルが出力され、制御信号Scontがハイレベルの場合には入力信号Vtempに応じて変化するコンパレータ30の出力信号Sgが出力される。

図9のブロック図に示された点A〜H、点P及び点Vdにしたがって、それらの点における各信号の遷移について説明する。図8と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100は、検出回路200と読み替える。

点の波形VDDは、POC回路12の電源電圧VDDの電圧遷移を示す。点Vdの波形は、POC回路12におけるCR回路の接合点Vdの電圧遷移を示す。点Pの波形は、割込条件生成回路10bにおけるPOC回路12よって判定され、出力された制御信号Scontの電圧遷移を示す。この信号に基づいて、割込条件受付回路20aが制御される。

時刻t1において、検出回路200並びに検出回路200に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧VDDが徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路10bにおけるPOC回路12では、電源電圧VDDを検出する。

コンデンサ12Cと抵抗12Rからなる時定数回路により、電源電圧VDDを入力としたステップ応答として同定される一次遅れの過度特性により点Vdの電位が遷移する。電源投入に追従して点Vdの電位が上昇するが、インバータ12aがまだ活性化されないことから制御信号Scontはローレベルを示す。

一方、割込条件受付回路20aは、電源電圧VDDが所定の電圧に達するまで入力信号の出力を許可せず所定の電圧を出力信号Voutとして出力する。出力信号Voutとして出力される所定の電圧は、センサ回路において非検出状態(解除状態)を示す電圧が設定され、制御信号Scontに応じて制御される。制御信号Scontには、ローレベルが出力されていることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

割込条件生成回路10bにおけるPOC回路12では、点Vdの電位がインバータ12aにおける閾値電位より高い状態を示す。インバータ12aの電源電圧が過度的に上昇するにつれインバータ12aの閾値電位も電源電圧の上昇に応じて上昇する。これにより、制御信号Scontは、ローレベルに確定している。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDの上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい2つの信号を比較して得られる出力信号Sgは、信号の状態を特定できない不定状態が継続する。割込条件受付回路20aでは、制御信号Scontがローレベルに確定していることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

基準電圧Vrefが所定の電圧を示すようになり、基準電圧Vrefは入力信号Vtempより低い電位を示すことから、出力信号Sgは、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号Scontによる制御が継続されることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

時刻t6では、電源電圧VDDが所定の動作可能電源電圧に達して上昇が止まり、電源電圧VDDが一定値を示すようになる。また、制御信号Scontの電位の上昇も止まり一定値を示す状態に遷移する。

割込条件生成回路10bにおけるPOC回路12では、電源電圧VDDが定電圧制御に遷移したことから、点Vdの電位上昇が止まり降下に転じる。

時刻t7では、割込条件生成回路10bにおけるPOC回路12では、点Vdの電位がインバータ12aの閾値電圧以下に低下したことにより制御信号Scontがハイレベルに遷移する。割込条件生成回路10bは、制御信号Scontに出力していた制御信号の割込み状態(ローレベル)を解除する。これにより、検出回路200は、検出信号の出力が行える通常状態に遷移する。

以上に示したように電源が投入されたことにより各信号の状態が遷移する。電源電圧VDDが所定の動作可能電源電圧に達するまで、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

図を参照し、形態の異なる検出回路の実施形態について示す。

図11は、第4実施形態による検出回路を示す概略構成図である。

検出回路300は、割込条件生成回路10c、割込条件受付回路20a及びコンパレータ30を備える。図7及び図9と同じ構成には同じ符号を付し、異なる構成について説明する。

検出回路300において割込条件生成回路10cは、オフセットコンパレータ11、POC回路13及びRSフリップフロップ14を備える。

POC回路13は、いわゆる電源投入初期化回路である。

POC回路13は、直列に接続されたコンデンサ13Cと抵抗13Rは、電源の正極(電源電圧VDD)にコンデンサ13Cの一端が接続され、電源の負極(接地電圧VSS)に抵抗13Rの一端が接続される。コンデンサ13Cと抵抗13Rの接続点は、バッファ13bの入力端に接続される。バッファ13bは、入力される電圧(点Vdの電圧)がバッファ13bの閾値電圧(反転電圧)以上になると、出力する信号Sp’が電源電圧VDDによって示されるハイレベルになり、閾値電圧(反転電圧)以下になると、信号Sp’が基準電圧VSSによって示されるローレベルになる。バッファ13bから出力される信号は、POC回路13の出力信号となる。Vdがバッファ13bの反転電圧以上になると、信号Sp’が電源電圧VDDになり、反転電圧以下になると、信号Sp’が基準電圧VSSになる。バッファ13bの閾値電圧は、電源電圧VDDの半分の電圧になる。

オフセットコンパレータ11は、信号Scを出力する。信号Scは、実施形態における制御信号Scontに相当する。

RSフリップフロップ14は、RS型フリップフロップを示す。

割込条件生成回路10cから出力される制御信号Scontは、電源の投入後、所定の時間経過するまでハイレベルを示し、所定の時間経過するとローレベルを示す。

割込条件受付回路20aの出力信号Voutは、制御信号Scontがローレベルの場合には固定的にローレベルが出力され、制御信号Scontがハイレベルの場合には入力信号Vtempに応じて変化するコンパレータ30の出力信号Sgが出力される。

図11のブロック図に示された点A〜H及び点P’にしたがって、それらの点における各信号の遷移について説明する。図8及び図10と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100及び図10に示した検出回路200は、検出回路300と読み替える。

点Cの波形は、割込条件生成回路10cにおけるオフセットコンパレータ11から出力される信号Scの電圧遷移を示す。点Eの波形は、割込条件生成回路10cにおけるRSフリップフロップ14から出力される制御信号Scontを示す。点P’の波形は、割込条件生成回路10cにおけるPOC回路13から出力される信号Sp’の電圧遷移を示す。

時刻t1において、検出回路300並びに検出回路300に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧VDDが徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

検出回路300では、電源投入後の動作可能電源電圧が供給されるまでの過度状態にあり、コンパレータ30の出力信号Sgは、信号の状態を特定できない不定状態となる。

POC回路13では、電源電圧VDDを検出する。電源投入に追従して点Vdの電位が上昇するが、バッファ13bがまだ活性化されないことから信号Sp’はローレベルを示す。RSフリップフロップ14は、セット(S)端子にローレベル、リセット(R)端子にローレベルが入力されるが、まだ活性化されないことから制御信号Scontは初期状態が保持されたローレベルが出力される。

割込条件生成回路10cにおけるオフセットコンパレータ11では、入力信号Vtempと電源電圧VDDの電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、信号Scは、ローレベルに確定している。POC回路13では、点Vdにおける信号の電圧がバッファ13bにおける閾値電位より高い状態を示す。バッファ13bの電源電圧VDDが過度的に上昇するにつれバッファ13bの閾値電位も電源電圧VDDの上昇に応じて上昇する。これにより、信号Sp’は、ハイレベルを出力する。RSフリップフロップ14は、セット(S)端子にローレベル、リセット(R)端子にハイレベルが入力され、出力(Q)端子には制御信号Scontとしてローレベルが出力される。

センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDの上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい2つの信号を比較して得られる出力信号Sgは、信号の状態を特定できない不定状態が継続する。

割込条件受付回路20aでは、制御信号Scontがローレベルに確定していることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

基準電圧Vrefが所定の電圧を示すようになり、基準電圧Vrefは入力信号Vtempより低い電位を示すことから、出力信号Sgは、状態が定まらない不定状態から正しい判定結果が出力される状態に遷移する。また、制御信号Scontによる制御が継続されることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

オフセットコンパレータ11は、信号Scにハイレベルを出力し、その電位は電源電圧VDDの電位上昇にともなって上昇する。

RSフリップフロップ14は、セット(S)端子にハイレベル、リセット(R)端子にハイレベルが入力され、出力(Q)端子にローレベルを出力する。

また、制御信号Scontによる制御が継続されることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

割込条件生成回路10cにおけるRSフリップフロップ14は、入力信号には状態の変更がなくセット(S)端子にハイレベル、リセット(R)端子にハイレベルが入力され、出力(Q)端子にローレベルの出力を継続する。割込条件生成回路10cは、制御信号Scontの割込み状態(ローレベル)を継続させる。また、制御信号Scontによる制御が継続されることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

RSフリップフロップ14は、セット(S)端子にハイレベル、リセット(R)端子にローレベルが入力され、出力(Q)端子にはハイレベルが出力され、制御信号Scontとして出力される。

図を参照し、形態の異なる検出回路の実施形態について示す。

図13は、第5実施形態による検出回路を示す概略構成図である。

検出回路400は、割込条件生成回路10d、割込条件受付回路20a及びコンパレータ30を備える。図7及び図11と同じ構成には同じ符号を付し、異なる構成について説明する。

低電源電圧検出回路15は、電源電圧の低下検出を行う。

図14は、低電源電圧検出回路15の一例を示す概略構成図である。

図14に示した低電源電圧検出回路15は、トランジスタQ1と定電流源I1を備える。

トランジスタQ1は、Nチャネル電界効果型トランジスタ(NMOSFET)を示す。トランジスタQ1は、ゲートが電源の正極(電源電圧VDD)に接続され、ソースが電源の負極(接地電圧VSS)に接続され、ドレインが片端が電源の正極に接続された定電流源I1に接続される。すなわち、トランジスタQ1は、定電流源I1を負荷としたソース接地型増幅回路を構成する。

図15(a)は、横軸にトランジスタQ1におけるゲート・ソース間電圧(VGS)を示し、縦軸にドレイン電流(ID)を示し、トランジスタQ1の増幅特性を示すグラフである。グラフの横軸における切片になるVthは、トランジスタQ1のゲート・ソース間電圧の閾値電圧を示す。このグラフに示されるように、トランジスタQ1のゲート・ソース間電圧VGSが所定の電圧Vα以下の状態では、トランジスタQ1は飽和状態にならずに、定電流源I1に設定された定電流i1を流すことができない。また、ゲート・ソース間電圧VGSが所定の電圧Vαを越えた状態では、トランジスタQ1は飽和状態になる。

電源電圧VDDが、電圧Vαに到達するまで信号Sdの電圧は、電圧VDDの変化にしたがって遷移する。電源電圧VDDが、電圧Vαに到達すると信号Sdは、ローレベルを示す状態に遷移する。

オフセットコンパレータ11の出力端がRSフリップフロップ14のセット入力端(S)に接続され、低電源電圧検出回路15の出力端がRSフリップフロップ14のリセット入力端(R)に接続され、RSフリップフロップ14の出力端が割込条件生成回路10dの出力信号を出力する。

図13のブロック図に示された点A〜Hにしたがって、それらの点における各信号の遷移について説明する。図8、図10及び図14と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100、図10に示した検出回路200及び図14に示した検出回路300は、検出回路400と読み替える。

点の波形Dは、低電源電圧検出回路15から出力される信号Sdを示す。

時刻t1において、検出回路400並びに検出回路400に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧VDDが徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧になる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

検出回路400では、電源投入後の動作可能電源電圧が供給されるまでの過度状態にあり、コンパレータ30の出力信号Sgは、信号の状態を特定できない不定状態となる。

低電源電圧検出回路15では、電源電圧が回路を構成する半導体素子(例えば、トランジスタQ1及びQ2)における閾値電位よりも低い状態にあり、信号Sdは電源電圧の上昇と共に上昇する。RSフリップフロップ14は、セット(S)端子にローレベル、リセット(R)端子にローレベルが入力されるが、まだ活性化されないことから制御信号Scontは初期状態が保持されたローレベルが出力される。

割込条件生成回路10dにおけるオフセットコンパレータ11では、入力信号Vtempと電源電圧VDDの電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、信号Scは、ローレベルに確定している。低電源電圧検出回路15では、電源電圧が回路を構成する半導体素子(例えば、トランジスタQ1及びQ2)における閾値電位よりも高い状態になり、信号Sdは電源電圧が所定の閾値電圧を超えたことから、ローレベルを出力する。RSフリップフロップ14は、セット(S)端子にローレベル、リセット(R)端子にローレベルが入力され、制御信号Scontには、回路が活性化され入力信号の状態にしたがってローレベルが出力される。

センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDの上昇にしたがって徐々に上昇するため、その電位差が小さな状態にある。電位差が小さい2つの信号を比較して得られる出力信号Sgは、信号の状態を特定できない不定状態が継続する。

割込条件受付回路20aでは、制御信号Scontがローレベルに確定していることにより、出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

オフセットコンパレータ11は、信号Scにハイレベルを出力し、電源電圧VDDの電位上昇にともなって上昇する。

RSフリップフロップ14は、セット(S)端子にハイレベル、リセット(R)端子にローレベルが入力され、出力を反転させハイレベルを出力する。

割込条件生成回路10dは、制御信号Scontの割込み状態(ローレベル)を解除する。これにより、検出回路400は、検出信号の出力が行える通常状態に遷移する。

図を参照し、形態の異なる低電源電圧検出回路の実施形態について示す。

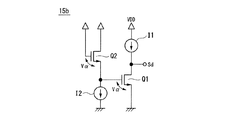

図17は、第6実施形態による低電源電圧検出回路を示す概略構成図である。

図17に示した低電源電圧検出回路15bは、トランジスタQ1、Q2と定電流源I1、I2を備える。

トランジスタQ1とQ2は、Nチャネル電界効果型トランジスタ(NMOSFET)を示す。トランジスタQ2は、ゲートとドレインが電源の正極(電源電圧VDD)に接続され、ソースが片端が電源の負極(設置電圧VSS)に接続された定電流源I2に接続される。

トランジスタQ1は、ゲートがトランジスタQ2のソースに接続され、ソースが接地電圧VSSに接続され、ドレインが片端が電源の正極に接続された定電流源I1に接続される。すなわち、トランジスタQ1とQ2は、多段接続された増幅回路を形成し、定電流源I1を負荷としたソース接地型増幅回路を出力段とした構成になる。

図18(a)は、横軸にトランジスタQ1(Q2)におけるゲート・ソース間電圧(VGS)を示し、縦軸にドレイン電流(ID)を示し、トランジスタQ1(Q2)の増幅特性を示すグラフである。グラフ横軸の切片になるVthは、トランジスタQ1(Q2)のゲート・ソース間電圧VGSの閾値電圧を示す。このグラフに示されるように、トランジスタQ1(Q2)のゲート・ソース間電圧VGSが所定の電圧Vα以下の状態では、設定された定電流I1を流すことができないトランジスタQ1(Q2)はオフ(遮断)状態になる。また、ゲート・ソース間電圧VGSが所定の電圧Vαを越えた状態では、トランジスタQ1(Q2)はオン(導通)状態になる。なお、トランジスタQ1とQ2は、特性が異なるものを選定しても良い。

電源電圧VDDが、電圧(2×Vα)に到達するまで信号Sdの電圧は、電源電圧VDDの変化にしたがって遷移する。電源電圧VDDが、電圧(2×Vα)に到達すると信号Sdは、ローレベルを示す状態に遷移する。

トランジスタQ1とQ2を多段に接続された構成にしたことで、低電源検出電圧の閾値電圧をトランジスタ1段の場合の倍の電圧にすることができる。

図を参照し、形態の異なる検出回路の実施形態について示す。

図19は、第7実施形態による検出回路を示す概略構成図である。

検出回路500は、割込条件生成回路10a、割込条件受付回路20b及びコンパレータ30を備える。図7と同じ構成には同じ符号を付し、異なる構成について説明する。

検出回路500における割込条件受付回路20bは、選択回路22を備える。

選択回路22は、入力される制御信号に連動するスイッチ22a及び22bを備える。

スイッチ22a及びスイッチ22bは、入力端(In1、In2)に対応して設けられる出力端(Out1、Out2)との間にそれぞれ接続され、制御信号入力端子Contに制御信号Scontとして入力される割込み信号に応じて、所定の電圧を出力するか入力端に入力された入力信号を出力するかを選択し切り換える。スイッチ22a及びスイッチ22bから出力される所定の電圧は、スイッチ22bから出力される電圧(V+)よりスイッチ22aから出力される電圧(V−)のほうが低く設定される。すなわち、割込条件受付回路20bは、制御信号として入力される割込信号による割込みが解除されるまで入力信号の出力を許可せず、スイッチ22a及びスイッチ22bを介して出力する所定の電圧を出力信号として出力する。また、割込条件受付回路20aは、割込信号による割込みが解除されると入力信号の出力を許可して出力信号として出力する。

次に、検出回路500の接続を示す。

検出回路500には、検出回路500を作動させる電源と、図示されないセンサ回路からの入力信号Vtempと、図示されない基準電源RFから出力される基準電圧Vrefとが入力される。

割込条件生成回路10aにおける入力端子Tipには、電源の正極に接続され電圧VDDが印加される。また、入力端子Tinには、図示されないセンサ回路の出力端が接続される。

割込条件受付回路20bにおける入力端子In1には基準電圧Vrefを出力する図示されない基準電源RFが接続され、入力端子In2には図示されないセンサ回路の出力端が接続され、制御入力端子Contには割込条件生成回路10aの出力端が接続される。

コンパレータ30における非反転入力端子には、割込条件受付回路20bにおける出力端子Oot1が接続され、反転入力端子には、割込条件受付回路20bにおける出力端子Out2が接続される。

図19のブロック図に示された点A〜G’にしたがって、それらの点における各信号の遷移について説明する。図8と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図8に示した検出回路100は、検出回路500と読み替える。

点の波形A’は、割込条件受付回路20bにおける点A’に出力する信号Sa’の電圧遷移を示す。信号Sa’には、センサ回路から入力された入力信号Vtempと同じ信号、又は、予め定められた所定の電圧のいずれかが出力される。

点の波形F’は、割込条件受付回路20bにおける点F’ に出力する信号Sf’の電圧遷移を示す。信号Sf’には、検出回路500に供給される基準電源RFから出力される基準電圧Vref、又は、予め定められた所定の電圧のいずれかが出力される。

点の波形G’は、コンパレータ30によって判定され、検出回路500の出力信号Voutになる。このタイミングチャートに示される範囲では、センサ回路によって検出すべき事象は生じていない状態を示し、出力信号Voutは、常時ローレベルを示す。

時刻t1において、検出回路500並びに検出回路500に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧VDDが徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧VDDになる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路10aでは、入力される信号の判定に一方の信号にオフセット電位を印加して比較する。これにより、割込条件生成回路10aでは、入力される信号の電位差が小さな場合でもオフセットされた電位によって比較判定された結果が出力されることから不安定となることはない。このため制御信号Scontは、ローレベルを示す。

これにより、コンパレータ30の出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

時刻t2では、電源電圧VDDが上昇し、それぞれの回路が動作可能な状態に遷移する。

割込条件生成回路10aでは、入力信号Vtempと電源電圧VDDの電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、制御信号Scontは、ローレベルに確定している。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDが上昇するのにしたがって徐々に上昇する。

制御信号Scontがローレベルであることにより、割込条件受付回路20b並びにコンパレータ30では、時刻t1からの状態が継続する。これにより、コンパレータ30の出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

基準電圧Vrefが所定の電圧を示すようになり、基準電圧Vrefは入力信号Vtempより低い電位を示すようになる。

前述の時刻t2からの状態と同様に割込条件生成回路10aでは、入力信号Vtempと電源電圧VDDの電位差が小さな状態にあるが、一方の信号にはオフセット電位が印加されていることにより、制御信号Scontは、ローレベルに確定している。センサ回路の出力、すなわち入力信号Vtempは電源電圧VDDが上昇するのにしたがって徐々に上昇する。

制御信号Scontがローレベルであることにより、割込条件受付回路20b並びにコンパレータ30では、時刻t1からの状態が継続する。これにより、コンパレータ30の出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

制御信号Scontが割込み解除状態(ハイレベル)に設定されたことにより、割込条件受付回路20bは、入力端に入力された入力信号を出力するように切り換える。割込条件受付回路20bは、信号Sa’には入力された入力信号Vtempを出力し、信号Sf’には入力された基準電圧Vrefを出力する。

図を参照し、形態の異なる検出回路の実施形態について示す。

図21は、第8実施形態による検出回路を示す概略構成図である。

検出回路600は、割込条件生成回路10b、割込条件受付回路20b及びコンパレータ30を備える。図7、図9及び図19と同じ構成には同じ符号を付している。

検出回路600には、検出回路600を作動させる電源と、図示されないセンサ回路からの入力信号Vtempと、図示されない基準電源RFから出力される基準電圧Vrefとが入力される。

割込条件受付回路20bにおける入力端子In1には、基準電圧Vrefを出力する図示されない電源の正極(電源電圧VDD)が接続され、入力端子In2には、図示されないセンサ回路の出力端が接続され、制御入力端子Contには、割込条件生成回路10bの出力端が接続される。

コンパレータ30における非反転入力端子には、割込条件受付回路20bにおける出力端子OUT1が接続され、反転入力端子には、割込条件受付回路20bにおける出力端子OUT1が接続される。

図21のブロック図に示された点A〜G’及び点Pにしたがって、それらの点における各信号の遷移について説明する。図8、図10及び図20と同じ信号、時刻には同じ符号を付し、異なる信号、時刻を中心に説明する。図7に示した検出回路100、図9に示した検出回路200及び図19に示した検出回路500は、検出回路600と読み替える。

時刻t1において、検出回路600並びに検出回路600に接続されているセンサ回路及び基準電源RFに対し、電源が投入される。その後、電源電圧VDDが徐々に上昇する。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDが低い状態では、電流源の働きによりこれらの出力電圧は電源電圧VDDになる。入力信号Vtemp及び基準電圧Vrefは、電源電圧VDDの上昇に応じて同様の変化特性を示して徐々に上昇する。

割込条件生成回路10bにおけるPOC回路12では、電源電圧VDDを検出する。

コンデンサ12Cと抵抗12Rからなる時定数回路により、電源電圧VDDを入力としたステップ応答として同定される一次遅れの過度特性により点Vdの電位が遷移する。電源投入に追従して電源電圧VDDが上昇するが、インバータ12aがまだ活性化されないことから制御信号Scontはローレベルを示す。

これにより、コンパレータ30の出力信号Voutには、ローレベルが出力され、不要な検出状態を示す信号が出力されずに解除状態を示す信号を出力する。

割込条件生成回路10bにおけるPOC回路12では、点Vdの電圧がインバータ12aにおける閾値電位より高い状態を示す。インバータ12aの電源電圧VDDが過度的に上昇するにつれインバータ12aの閾値電位も電源電圧VDDの上昇に応じて上昇する。これにより、制御信号Scontは、ローレベルに確定している。センサ回路及び基準電源RFの出力である入力信号Vtemp及び基準電圧Vrefも電源電圧VDDが上昇するのにしたがって徐々に上昇する。

制御信号Scontがローレベルであることにより、割込条件受付回路20b並びにコンパレータ30では、時刻t1からの状態が継続する。これにより、コンパレータ30の出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

基準電圧Vrefが所定の電圧を示すようになり、基準電圧Vrefは入力信号Vtempより低い電位を示すようになる。

前述の時刻t2からの状態と同様に割込条件生成回路10bにおける状態の変化はなく、制御信号Scontにはローレベルが出力されている。センサ回路の出力、すなわち入力信号Vtempは電源電圧VDDが上昇するのにしたがって徐々に上昇する。

制御信号Scontがローレベルであることにより、割込条件受付回路20b並びにコンパレータ30では、時刻t1からの状態が継続する。これにより、コンパレータ30の出力信号Voutはローレベルに確保され、不要な検出状態を示す信号が出力されることはない。

割込条件受付回路20bからの信号が入力されるコンパレータ30では、割込条件受付回路20bに入力された信号が、割込条件受付回路20bを経由して入力される。電源電圧VDDが所定の電圧に達するまで出力信号Voutを解除状態を示すように確定させる処理が施される。解除状態を示すように確定させる処理は、制御信号Scontとして入力される制御信号Scontによって制御される。

制御信号Scontがハイレベルであることにより、割込条件受付回路20bは、出力端(Out1、Out2)から信号Sf’と信号Sa’を出力し、その信号は基準電圧Vrefと入力信号Vtempによる信号になる。

これにより、検出回路600は、検出信号の出力が行える通常状態に遷移する。

実施形態1から実施形態7に示した検出回路(検出回路100から検出回路600)は、センサ900と組み合わせることにより、所望のセンサ装置を構成することができる。

センサ900として適応できる各種センサの例として、温度センサ、MRセンサ、BGRセンサなどを上げることができる。

センサ900は、電源の正極(電源電圧VDD)に接続された定電流回路と、定電流回路の負荷になるインピーダンス回路とを組み合わせて構成することができる。インピーダンス回路は、それぞれのセンサの目的により、検出した現象の大きさに応じてインピーダンスが変化する素子を選定する。

これにより、電源投入後の動作において、電源投入によって出力信号に誤った検出信号を送出することなく信頼性の高いセンサ装置を構成することが可能となる。

2 電流源回路

3,3a,3b インピーダンス回路

4 信号電圧監視回路

5 オフセットコンパレータ

5a バイアス電圧源

5b コンパレータ

6 アプリケーション回路

6a ボルテージフォロワ回路、

6b コンパレータ回路

50 電源電圧監視回路

100 検出回路

10a 割込条件生成回路

11 オフセットコンパレータ

11b バイアス電圧源

11c コンパレータ

20a 割込条件受付回路

21 出力設定回路

21a インバータ

21b NANDゲート

30 コンパレータ

Claims (12)

- 電子回路に供給される電源電圧を監視する電源電圧監視回路であって、

前記電源電圧の増加に対して飽和特性を示す信号電圧を出力する信号出力回路と、

前記電源電圧そのものと、予め設定された設定電圧を前記信号電圧に加算した加算電圧とを比較し、当該電源電圧が前記加算電圧を超えた場合に、前記信号電圧が正常であることを示す信号を出力する信号電圧監視回路と、

を備えることを特徴とする電源電圧監視回路。 - 前記信号電圧監視回路が、

前記電子回路に供給される前記電源電圧の配線が一方の入力端子に接続され、前記信号出力回路から出力される前記信号電圧の配線が他方の入力端子に接続されたコンパレータから構成され、

前記コンパレータが、

前記他方の入力端子に、前記信号電圧に予め設定された前記設定電圧を加算して前記加算電圧を生成する回路を有し、前記電源電圧と前記加算電圧とを比較し、当該電源電圧が前記加算電圧を超えた場合に、前記信号電圧が正常であることを示す信号を出力する

ことを特徴とする請求項1に記載の電源電圧監視回路。 - 前記設定電圧が、

前記信号出力回路が動作可能となる前記電源電圧と、この動作可能となる前記電源電圧が供給された際に前記信号出力回路が出力する前記信号電圧との差分電圧であることを特徴とする請求項1または請求項2に記載の電源電圧監視回路。 - コンデンサの一端と抵抗の一端とが接続され、前記コンデンサの他端が前記電源電圧の配線に接続され、前記抵抗の他端が接地された直列回路と、

前記コンデンサの一端と前記抵抗の一端との接続点の電圧である検出電圧が入力され、前記検出電圧と予め設定された閾値電圧とを比較し、前記電源電圧が前記電子回路を動作可能であるか否かを示す動作可能信号を出力する電圧監視部と、

前記動作可能信号がリセット端子に入力され、前記信号電圧が正常であることを示す信号がセット端子に入力され、出力端子から前記信号が正常な検出状態であることを示す検出信号を出力するラッチ部と

をさらに有することを特徴とする請求項1から請求項3のいずれか1項に記載の電源電圧監視回路。 - 前記信号出力回路は、

電源から電流源回路を通して電流の供給を受けるインピーダンス回路を有し、前記インピーダンス回路により前記信号電圧を生成して出力し、

前記信号電圧監視回路は、

前記電圧差が前記設定電圧を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧以上になったことを示す信号を出力する、

ことを特徴とする請求項1から請求項4のいずれか1項に記載の電源電圧監視回路。 - 前記インピーダンス回路は、

前記電源電圧と比較される基準電圧として、さらには温度依存性を示す電圧として前記信号電圧を生成して出力すること、

を特徴とする請求項5に記載の電源電圧監視回路。 - 前記信号出力回路は、

前記電源の投入時において、前記電源電圧が所定の電圧に遷移するまでの間は、前記電源電圧の増加に従い増加する前記信号電圧を出力すると共に、前記電源電圧が前記所定の電圧を超えて増加する場合に、飽和特性を持って単調増加する電圧を前記信号電圧として出力し、

前記信号電圧監視回路は、

前記信号出力回路から出力される前記信号電圧と前記電源電圧とを比較し、前記電圧差が前記設定電圧を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧を超えたことを示す信号を出力すること、

を特徴とする請求項1から請求項6のいずれか1項に記載の電源電圧監視回路。 - 前記信号電圧監視回路は、

前記設定電圧である予め定められるオフセット電位を、一方の入力端子に入力される信号の電圧に加えるオフセット機能を有し、

前記一方の入力端子に前記信号電圧を入力し、他方の入力端子に前記電源電圧を入力し、前記電源電圧の電圧値が前記オフセット電位が加えられた前記信号電圧の電圧値を超えた場合に、前記電源電圧が前記電子回路の最低動作電源電圧以上になったことを示す信号を出力する比較回路を

備えることを特徴とする請求項1から請求項7のいずれか1項に記載の電源電圧監視回路。 - 前記信号出力回路は、

前記電流源回路と前記インピーダンス回路とが直列に接続されて構成され、

前記電流源回路と前記インピーダンス回路との回路接続点から前記信号電圧が出力されること

を特徴とする請求項5から請求項8のいずれか1項に記載の電源電圧監視回路。 - 前記インピーダンス回路は、

前記電流源回路から出力される電流を入力とし、

検出された物理量に応じた電圧信号を、前記信号電圧として出力するセンサであること を特徴とする請求項9に記載の電源電圧監視回路。 - 前記センサは、温度を検出する温度センサであること

を特徴とする請求項10に記載の電源電圧監視回路。 - 請求項1から請求項11のいずれか1項に記載の電源電圧監視回路を備えることを特徴とする電子回路。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009005214A JP4636461B2 (ja) | 2009-01-13 | 2009-01-13 | 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 |

| TW099100293A TWI517573B (zh) | 2009-01-13 | 2010-01-07 | 電源電壓監視電路及具備該電源電壓監視電路之電子電路 |

| KR1020100002780A KR101372795B1 (ko) | 2009-01-13 | 2010-01-12 | 전원 전압 감시 회로, 및 그 전원 전압 감시 회로를 구비하는 전자 회로 |

| US12/686,684 US8604821B2 (en) | 2009-01-13 | 2010-01-13 | Power supply voltage monitoring circuit and electronic circuit including the power supply voltage monitoring circuit |

| CN2010100039107A CN101783664B (zh) | 2009-01-13 | 2010-01-13 | 电源电压监视电路以及具有电源电压监视电路的电子电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009005214A JP4636461B2 (ja) | 2009-01-13 | 2009-01-13 | 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010166184A JP2010166184A (ja) | 2010-07-29 |

| JP2010166184A5 JP2010166184A5 (ja) | 2010-09-09 |

| JP4636461B2 true JP4636461B2 (ja) | 2011-02-23 |

Family

ID=42318604

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009005214A Active JP4636461B2 (ja) | 2009-01-13 | 2009-01-13 | 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8604821B2 (ja) |

| JP (1) | JP4636461B2 (ja) |

| KR (1) | KR101372795B1 (ja) |

| CN (1) | CN101783664B (ja) |

| TW (1) | TWI517573B (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102486517B (zh) * | 2010-12-01 | 2015-11-25 | 中国电力科学研究院 | 冲击电压复合的高压直流输电换流阀故障电流试验方法 |

| JP5754343B2 (ja) * | 2011-10-25 | 2015-07-29 | ミツミ電機株式会社 | 低電圧検出回路 |

| US9086434B1 (en) * | 2011-12-06 | 2015-07-21 | Altera Corporation | Methods and systems for voltage reference power detection |

| JP2015211345A (ja) | 2014-04-25 | 2015-11-24 | セイコーインスツル株式会社 | 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 |

| JP6436728B2 (ja) * | 2014-11-11 | 2018-12-12 | エイブリック株式会社 | 温度検出回路及び半導体装置 |

| KR101742875B1 (ko) | 2015-06-18 | 2017-06-01 | 인하대학교 산학협력단 | 고 임피던스 전류 보정 회로를 갖는 테스트 보드용 엑티브 로드 |

| US9927317B2 (en) | 2015-07-09 | 2018-03-27 | Mks Instruments, Inc. | Ionization pressure gauge with bias voltage and emission current control and measurement |

| CN105141119B (zh) * | 2015-10-10 | 2018-01-05 | 上海灿瑞科技股份有限公司 | 一种上电清零和欠压锁定启动电路 |

| CN109379065B (zh) * | 2018-11-30 | 2023-11-10 | 上海艾为电子技术股份有限公司 | 电压检测电路、过压保护开关及电子设备 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02108323A (ja) * | 1988-10-18 | 1990-04-20 | Sanyo Electric Co Ltd | 混成集積回路 |

| JPH04181810A (ja) * | 1990-11-15 | 1992-06-29 | Mitsubishi Electric Corp | 半導体装置 |

| JPH06213941A (ja) * | 1993-01-14 | 1994-08-05 | Sharp Corp | 外部電源電圧検知回路 |

| JP2001127594A (ja) * | 1999-10-25 | 2001-05-11 | Seiko Instruments Inc | ラッチ回路 |

| JP2007081533A (ja) * | 2005-09-12 | 2007-03-29 | Ricoh Co Ltd | パワーオンリセット回路 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08279739A (ja) | 1995-04-06 | 1996-10-22 | Fuji Electric Co Ltd | 電子回路用動作指令の制御回路 |

| JP3338814B2 (ja) * | 1999-11-22 | 2002-10-28 | エヌイーシーマイクロシステム株式会社 | バンドギャップレファレンス回路 |

| JP3817446B2 (ja) * | 2001-02-15 | 2006-09-06 | 株式会社リコー | 電源回路及びdc−dcコンバータの出力電圧制御方法 |

| JP2004165649A (ja) * | 2002-10-21 | 2004-06-10 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| US6970334B1 (en) * | 2003-09-09 | 2005-11-29 | National Semiconductor Corporation | Power regulation loop performs two functions |

| US7148742B2 (en) * | 2004-07-07 | 2006-12-12 | Micron Technology, Inc. | Power supply voltage detection circuitry and methods for use of the same |

| JP4660160B2 (ja) * | 2004-10-28 | 2011-03-30 | Okiセミコンダクタ株式会社 | リセット回路 |

| JP2006217544A (ja) * | 2005-02-07 | 2006-08-17 | Sanyo Electric Co Ltd | 発振器 |

| CN1959595A (zh) * | 2005-11-04 | 2007-05-09 | 鸿富锦精密工业(深圳)有限公司 | 计算机系统复位电路 |

| JP4902390B2 (ja) * | 2007-02-17 | 2012-03-21 | セイコーインスツル株式会社 | カレント検出回路及び電流モード型スイッチングレギュレータ |

| JP5090202B2 (ja) * | 2008-02-19 | 2012-12-05 | 株式会社リコー | 電源回路 |

| US8339188B1 (en) * | 2008-07-01 | 2012-12-25 | Cypress Semiconductor Corporation | Floating gate reference for sleep/hibernate regulator |

| JP5283078B2 (ja) * | 2009-01-13 | 2013-09-04 | セイコーインスツル株式会社 | 検出回路及びセンサ装置 |

| JP2012108087A (ja) * | 2010-10-28 | 2012-06-07 | Seiko Instruments Inc | 温度検知装置 |

-

2009

- 2009-01-13 JP JP2009005214A patent/JP4636461B2/ja active Active

-

2010

- 2010-01-07 TW TW099100293A patent/TWI517573B/zh active

- 2010-01-12 KR KR1020100002780A patent/KR101372795B1/ko active IP Right Grant

- 2010-01-13 CN CN2010100039107A patent/CN101783664B/zh active Active

- 2010-01-13 US US12/686,684 patent/US8604821B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02108323A (ja) * | 1988-10-18 | 1990-04-20 | Sanyo Electric Co Ltd | 混成集積回路 |

| JPH04181810A (ja) * | 1990-11-15 | 1992-06-29 | Mitsubishi Electric Corp | 半導体装置 |

| JPH06213941A (ja) * | 1993-01-14 | 1994-08-05 | Sharp Corp | 外部電源電圧検知回路 |

| JP2001127594A (ja) * | 1999-10-25 | 2001-05-11 | Seiko Instruments Inc | ラッチ回路 |

| JP2007081533A (ja) * | 2005-09-12 | 2007-03-29 | Ricoh Co Ltd | パワーオンリセット回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101783664B (zh) | 2013-09-25 |

| TWI517573B (zh) | 2016-01-11 |

| US8604821B2 (en) | 2013-12-10 |

| KR101372795B1 (ko) | 2014-03-10 |

| KR20100083728A (ko) | 2010-07-22 |

| CN101783664A (zh) | 2010-07-21 |

| US20100176839A1 (en) | 2010-07-15 |

| JP2010166184A (ja) | 2010-07-29 |

| TW201041300A (en) | 2010-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4636461B2 (ja) | 電源電圧監視回路、および該電源電圧監視回路を備える電子回路 | |

| US10591947B2 (en) | Power supply voltage monitoring circuit | |

| JP5283078B2 (ja) | 検出回路及びセンサ装置 | |

| US9819173B2 (en) | Overheat protection circuit and voltage regulator | |

| JP5808116B2 (ja) | 基準電圧回路および半導体集積回路 | |

| TWI651609B (zh) | 低電壓鎖定電路及其整合參考電壓產生電路之裝置 | |

| US10613562B2 (en) | Voltage regulator including fault detection circuit | |

| JP6476049B2 (ja) | 温度センサ回路 | |

| JP5272467B2 (ja) | 基準電圧発生回路およびリセット回路を内蔵した半導体集積回路 | |

| US8575912B1 (en) | Circuit for generating a dual-mode PTAT current | |

| TWI686030B (zh) | 過熱檢測電路以及電源裝置 | |

| JP6378230B2 (ja) | 半導体装置 | |

| JP2004304632A (ja) | パワーオンディテクタ、及びこのパワーオンディテクタを用いたパワーオンリセット回路 | |

| JP2002323519A (ja) | 電圧監視回路 | |

| JP2008282313A (ja) | 電源回路 | |

| US20190288501A1 (en) | Semiconductor integrated circuit | |

| US9816883B2 (en) | Current source circuit and detection circuit | |

| KR102658159B1 (ko) | 과열 보호 회로 및 이것을 구비한 반도체 장치 | |

| WO2023139678A1 (ja) | 基準電圧発生回路及び半導体集積回路 | |

| JP7126931B2 (ja) | 過熱保護回路及び半導体装置 | |

| TWI666938B (zh) | 採用帶隙參考機制和相關驅動方法實現之類比區塊 | |

| JP2008085541A (ja) | 電圧レベル検出回路およびそれを用いたパワーオンリセット回路 | |

| KR20240012328A (ko) | 밴드갭 레퍼런스 전압 생성 회로 및 그를 갖는 반도체장치 | |

| JP2015207151A (ja) | レギュレータ回路 | |

| KR20200047349A (ko) | 기준 전압 회로 및 파워 온 리셋 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100609 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100609 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100609 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100713 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100906 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101019 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20101115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4636461 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |