JP4570868B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4570868B2 JP4570868B2 JP2003433851A JP2003433851A JP4570868B2 JP 4570868 B2 JP4570868 B2 JP 4570868B2 JP 2003433851 A JP2003433851 A JP 2003433851A JP 2003433851 A JP2003433851 A JP 2003433851A JP 4570868 B2 JP4570868 B2 JP 4570868B2

- Authority

- JP

- Japan

- Prior art keywords

- bonding

- electrodes

- power supply

- semiconductor device

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/90—Masterslice integrated circuits

- H10D84/998—Input and output buffer/driver structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0186—Manufacturing their interconnections or electrodes, e.g. source or drain electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W44/00—Electrical arrangements for controlling or matching impedance

- H10W44/20—Electrical arrangements for controlling or matching impedance at high-frequency [HF] or radio frequency [RF]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

- H10W70/62—Insulating or insulated package substrates; Interposers; Redistribution layers characterised by their interconnections

- H10W70/65—Shapes or dispositions of interconnections

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W44/00—Electrical arrangements for controlling or matching impedance

- H10W44/20—Electrical arrangements for controlling or matching impedance at high-frequency [HF] or radio frequency [RF]

- H10W44/203—Electrical connections

- H10W44/206—Wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/60—Insulating or insulated package substrates; Interposers; Redistribution layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

- H10W72/07541—Controlling the environment, e.g. atmosphere composition or temperature

- H10W72/07552—Controlling the environment, e.g. atmosphere composition or temperature changes in structures or sizes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

- H10W72/07541—Controlling the environment, e.g. atmosphere composition or temperature

- H10W72/07553—Controlling the environment, e.g. atmosphere composition or temperature changes in shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/075—Connecting or disconnecting of bond wires

- H10W72/07541—Controlling the environment, e.g. atmosphere composition or temperature

- H10W72/07554—Controlling the environment, e.g. atmosphere composition or temperature changes in dispositions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/521—Structures or relative sizes of bond wires

- H10W72/527—Multiple bond wires having different sizes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/536—Shapes of wire connectors the connected ends being ball-shaped

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/5363—Shapes of wire connectors the connected ends being wedge-shaped

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/5366—Shapes of wire connectors the bond wires having kinks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/531—Shapes of wire connectors

- H10W72/537—Multiple bond wires having different shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/541—Dispositions of bond wires

- H10W72/5449—Dispositions of bond wires not being orthogonal to a side surface of the chip, e.g. fan-out arrangements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/541—Dispositions of bond wires

- H10W72/547—Dispositions of multiple bond wires

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/551—Materials of bond wires

- H10W72/552—Materials of bond wires comprising metals or metalloids, e.g. silver

- H10W72/5522—Materials of bond wires comprising metals or metalloids, e.g. silver comprising gold [Au]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/50—Bond wires

- H10W72/59—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/932—Plan-view shape, i.e. in top view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/931—Shapes of bond pads

- H10W72/934—Cross-sectional shape, i.e. in side view

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/944—Dispositions of multiple bond pads

- H10W72/9445—Top-view layouts, e.g. mirror arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/951—Materials of bond pads

- H10W72/952—Materials of bond pads comprising metals or metalloids, e.g. PbSn, Ag or Cu

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/751—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires

- H10W90/754—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bond wires between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Wire Bonding (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域にリング状の複数の第1ボンディング電極が形成され、前記第1領域を囲む第2領域に複数の第2ボンディング電極が形成され、内部に前記第1ボンディング電極および前記第2ボンディング電極と電気的に接続する配線が形成された配線基板と、

第2主面および第2裏面を有し、前記第2裏面が前記チップ搭載領域と接するように前記配線基板に搭載され、前記第2主面において複数の電極が配置された半導体チップと、

前記複数の電極とこれに対応する前記第1ボンディング電極または前記第2ボンディング電極とを電気的に接続する複数のワイヤとを有し、

前記複数の第1ボンディング電極は電源電位もしくは基準電位と電気的に接続し、

前記複数の第2ボンディング電極は信号の入力もしくは出力に用いられ、

前記複数の電極は、前記第2主面の外周に沿って複数列で配列され、第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とは、前記第2主面の前記外周に沿った方向で互い違いに配置され、

前記複数の電極は、前記第1ボンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ボンディング電極と電気的に接続される複数の第2電極とを含み、

(a)前記複数のワイヤのうち、前記第1ボンディング電極と前記複数の第1電極とを電気的に接続する複数の第1ワイヤは、前記複数の第2ボンディング電極と前記複数の第2電極とを電気的に接続する複数の第2ワイヤ以上の径を有する、

もしくは、

(b)1個の前記第1電極と前記第1ボンディング電極との間には、複数の前記ワイヤが接続されている、

を満たすものである。

(a)第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域に電源電位もしくは基準電位と電気的に接続されるリング状の複数の第1ボンディング電極が形成され、前記第1領域を囲む第2領域に信号の入力もしくは出力に用いられる複数の第2ボンディング電極が形成され、内部に前記第1ボンディング電極および前記第2ボンディング電極と電気的に接続する配線が形成された配線基板を用意する工程、

(b)第2主面および第2裏面を有し、前記第2主面において複数の電極が外周に沿って複数列で配置された半導体チップを用意する工程、

(c)前記第2裏面が前記チップ搭載領域と接するように前記半導体チップを前記配線基板に搭載する工程、

(d)前記複数の電極とこれに対応する前記第1ボンディング電極とを第1ワイヤによって電気的に接続する工程、

(e)前記複数の電極とこれに対応する前記第2ボンディング電極とを第2ワイヤによって電気的に接続する工程、

を含み、

前記(b)工程は、

(b1)第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とを、前記第2主面の前記外周に沿った方向で互い違いに配置する工程、

を含み、

前記複数の電極は、前記第1ボンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ボンディング電極と電気的に接続される複数の第2電極とを含み、

前記第1ワイヤの径は、前記第2ワイヤの径以上とするものである。

(a)第1主面および第1裏面を有し、前記第1主面において中央部にチップ搭載領域が設けられ、前記チップ搭載領域を囲む第1領域に電源電位もしくは基準電位と電気的に接続されるリング状の複数の第1ボンディング電極が形成され、前記第1領域を囲む第2領域に信号の入力もしくは出力に用いられる複数の第2ボンディング電極が形成され、内部に前記第1ボンディング電極および前記第2ボンディング電極と電気的に接続する配線が形成された配線基板を用意する工程、

(b)第2主面および第2裏面を有し、前記第2主面において複数の電極が外周に沿って複数列で配置された半導体チップを用意する工程、

(c)前記第2裏面が前記チップ搭載領域と接するように前記半導体チップを前記配線基板に搭載する工程、

(d)前記複数の電極とこれに対応する前記第1ボンディング電極または前記第2ボンディング電極とを複数のワイヤによって電気的に接続する工程、

を含み、

前記(b)工程は、

(b1)第1列に含まれる前記電極と、前記第2主面内において前記第1列の内側に位置する第2列に含まれる前記電極とを、前記第2主面の前記外周に沿った方向で互い違いに配置する工程、

を含み、

前記複数の電極は、前記第1ボンディング電極と電気的に接続される複数の第1電極と、前記複数の第2ボンディング電極と電気的に接続される複数の第2電極とを含み、

1個の前記第1電極と前記第1ボンディング電極との間には、前記複数のワイヤを接続するものである。

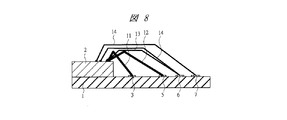

図1は本実施の形態1の半導体装置の構造の一例を示す断面図であり、図2は図1に示した半導体装置の要部平面図であり、図3は図1に示した半導体装置の要部断面図である。

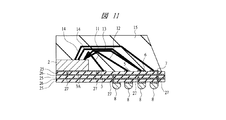

本実施の形態2の半導体装置も前記実施の形態1の半導体装置と同様に、配線基板上にチップが搭載された樹脂封止型の半導体パッケージである。

図13は本実施の形態3の半導体装置の要部平面図である。

2 チップ

2A チップ端部

3、5 ボンディング電極(第1ボンディング電極)

3A 電極(第3ボンディング電極)

4A ボンディング電極

4B、4C ボンディング電極(第4ボンディング電極)

6、7 ボンディング電極(第2ボンディング電極)

8 はんだボール

9 ボンディングパッド(電極、第1電極)

10 ボンディングパッド(電極、第2電極)

11、12 ワイヤ(第1ワイヤ)

11A、12A ワイヤ(第1ワイヤ)

13 ワイヤ(第2ワイヤ)

14 ワイヤ(第2ワイヤ)

15 封止体

16 配線

17 配線

18 電源回路セル

19 電源回路セル

20 入出力回路セル

21 入出力回路セル

22、22A、23、23A 配線

25 絶縁層

26 配線(配線層)

27 配線

31 半導体基板

32 p型ウエル

33 n型ウエル

34N、34P ゲート電極

35N、36N n型半導体領域

35P、36P p型半導体領域

37 層間絶縁膜

38A、38B、38C、38D プラグ

39A、39B、39C、39D 配線

41A ボンディングパッド

41B ボンディングパッド

41C ボンディングパッド

42、43 ワイヤ

44 配線

45 内部電源回路セル

46 配線

BUF バッファ回路

D1、D2 ダイオード

ESD 静電破壊保護回路

LEV レベルシフト回路

LOG 論理回路

PBF プリバッファ回路

Qn nチャネル型MISFET

Qp pチャネル型MISFET

Claims (11)

- 第1主面と、前記第1主面と対向する第1裏面と、前記第1主面に設けられたチップ搭載領域と、前記チップ搭載領域の周囲に設けられ、かつ電源電位または接地電位が供給される複数の第1ボンディング電極と、前記第1ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられ、かつ信号が入力または出力される複数の第2ボンディング電極とを含む配線基板と、

第2主面と、前記第2主面と対向する第2裏面と、前記第2主面に設けられ、かつ前記第2主面の外周に沿って設けられた複数の第1電極と、前記第2主面に設けられ、かつ前記複数の第1電極よりも内側に設けられた複数の第2電極と、前記第2主面に設けられ、かつ前記複数の第2電極よりも内側の領域に設けられた複数の電源回路セルと、前記第2主面に設けられ、かつ前記複数の第2電極よりも内側の領域に設けられた複数の入出力回路セルとを含み、前記第2裏面が前記チップ搭載領域と対向するように前記配線基板に搭載された半導体チップと、

前記複数の第1ボンディング電極と前記複数の第1電極をそれぞれ電気的に接続する複数の第1ワイヤと、前記複数の第2ボンディング電極と前記複数の第2電極をそれぞれ電気的に接続する複数の第2ワイヤとを有し、

前記第1電極と前記第2電極は、前記半導体チップの外周に沿った方向で互い違いに配置され、

前記第1電極の外形サイズは、前記第2電極の外形サイズよりも大きく、

前記複数の電源回路セルと前記複数の第1電極を電気的に接続する複数の第1配線の幅は、前記複数の入出力回路セルと前記複数の第2電極を電気的に接続する複数の第2配線の幅よりも太く、

前記複数の電源回路セルは、前記接地電位が供給される第1電源回路セルと、前記電源電位のうちの外部電源電位が供給される第2電源回路セルと、前記電源電位のうちの内部電源電位が供給される第3電源回路セルとを有することを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記第1ワイヤの径は、前記第2ワイヤの径よりも太いことを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記第1電極に電気的に接続される第1ワイヤの数は、前記第2電極に電気的に接続される第2ワイヤの数よりも多いことを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記電源回路セルおよび前記入出力回路セルのそれぞれは、バッファ回路、静電破壊保護回路、プリバッファ回路、レベルシフト回路、および論理回路から形成されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記第3電源回路セル上には、第3電極が形成されていることを特徴とする半導体装置。 - 請求項5記載の半導体装置において、

前記複数の第1ボンディング電極は、前記接地電位が供給され、かつ前記チップ搭載領域の周囲にリング状に形成された第3ボンディング電極と、外部電源電位が供給され、かつ前記第3ボンディング電極よりも前記チップ搭載領域から遠い位置にリング状に形成された第4ボンディング電極を有することを特徴とする半導体装置。 - 請求項6記載の半導体装置において、

前記複数の第1ボンディング電極は、更に、前記内部電源電位が供給され、かつ前記第3ボンディング電極と前記第4ボンディング電極との間にリング状に形成された第5ボンディング電極を有することを特徴とする半導体装置。 - 請求項7記載の半導体装置において、

前記第3電極は、前記第5ボンディング電極とそれぞれ電気的に接続されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記配線基板は、さらに、前記複数の第1ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第6ボンディング電極と、前記複数の第6ボンディング電極よりも前記チップ搭載領域から遠い位置に設けられた複数の第7ボンディング電極を有することを特徴とする半導体装置。 - 請求項9記載の半導体装置において、

前記半導体チップは、さらに、前記半導体チップの前記第2主面の外周に沿って、クロック信号を入力または出力する複数の第4電極を有し、

前記複数の第4電極は、前記複数の第6ボンディング電極と複数の第3ワイヤを介してそれぞれ電気的に接続されていることを特徴とする半導体装置。 - 請求項1記載の半導体装置において、

前記配線基板の前記第1裏面には、複数のはんだボールが設けられ、

前記複数のはんだボールは、前記複数の第1ボンディング電極および前記複数の第2ボンディング電極と複数の配線層を介してそれぞれ電気的に接続されていることを特徴とする半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003433851A JP4570868B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

| US11/005,217 US7211903B2 (en) | 2003-12-26 | 2004-12-07 | Semiconductor device and manufacturing method of them |

| TW93138020A TWI364803B (en) | 2003-12-26 | 2004-12-08 | Semiconductor device |

| US11/730,088 US7323788B2 (en) | 2003-12-26 | 2007-03-29 | Semiconductor device and manufacturing method of them |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003433851A JP4570868B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005191447A JP2005191447A (ja) | 2005-07-14 |

| JP2005191447A5 JP2005191447A5 (ja) | 2007-02-15 |

| JP4570868B2 true JP4570868B2 (ja) | 2010-10-27 |

Family

ID=34791113

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003433851A Expired - Fee Related JP4570868B2 (ja) | 2003-12-26 | 2003-12-26 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7211903B2 (ja) |

| JP (1) | JP4570868B2 (ja) |

| TW (1) | TWI364803B (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4570868B2 (ja) * | 2003-12-26 | 2010-10-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2007103423A (ja) * | 2005-09-30 | 2007-04-19 | Renesas Technology Corp | 半導体装置及びその製造方法 |

| JP4993929B2 (ja) * | 2006-03-23 | 2012-08-08 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| US7394164B2 (en) * | 2006-07-28 | 2008-07-01 | Ultra Chip, Inc. | Semiconductor device having bumps in a same row for staggered probing |

| US7501709B1 (en) * | 2006-08-25 | 2009-03-10 | Altera Corporation | BGA package with wiring schemes having reduced current loop paths to improve cross talk control and characteristic impedance |

| US8922028B2 (en) * | 2007-02-13 | 2014-12-30 | Advanced Semiconductor Engineering, Inc. | Semiconductor package |

| JP2010010492A (ja) * | 2008-06-27 | 2010-01-14 | Sony Corp | 半導体装置および半導体集積回路 |

| JP5395407B2 (ja) * | 2008-11-12 | 2014-01-22 | ルネサスエレクトロニクス株式会社 | 表示装置駆動用半導体集積回路装置および表示装置駆動用半導体集積回路装置の製造方法 |

| KR100935854B1 (ko) * | 2009-09-22 | 2010-01-08 | 테세라 리써치 엘엘씨 | 와이어 본딩 및 기준 와이어 본딩에 의해 제어되는 임피던스를 가진 마이크로전자 어셈블리 |

| KR100950511B1 (ko) * | 2009-09-22 | 2010-03-30 | 테세라 리써치 엘엘씨 | 와이어 본딩 및 도전성 기준 소자에 의해 제어되는 임피던스를 포함하는 마이크로전자 어셈블리 |

| JP5448727B2 (ja) * | 2009-11-05 | 2014-03-19 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| US8531013B2 (en) | 2010-06-11 | 2013-09-10 | Casio Computer Co., Ltd. | Semiconductor device equipped with bonding wires and manufacturing method of semiconductor device equipped with bonding wires |

| JP5252027B2 (ja) * | 2010-06-11 | 2013-07-31 | カシオ計算機株式会社 | 半導体装置の製造方法 |

| JP5467959B2 (ja) | 2010-07-21 | 2014-04-09 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8222725B2 (en) | 2010-09-16 | 2012-07-17 | Tessera, Inc. | Metal can impedance control structure |

| US8786083B2 (en) | 2010-09-16 | 2014-07-22 | Tessera, Inc. | Impedance controlled packages with metal sheet or 2-layer RDL |

| US9136197B2 (en) | 2010-09-16 | 2015-09-15 | Tessera, Inc. | Impedence controlled packages with metal sheet or 2-layer RDL |

| US8581377B2 (en) | 2010-09-16 | 2013-11-12 | Tessera, Inc. | TSOP with impedance control |

| US8853708B2 (en) | 2010-09-16 | 2014-10-07 | Tessera, Inc. | Stacked multi-die packages with impedance control |

| US9401717B2 (en) | 2012-05-28 | 2016-07-26 | Baysand Inc. | Flexible, space-efficient I/O circuitry for integrated circuits |

| US20160307873A1 (en) * | 2015-04-16 | 2016-10-20 | Mediatek Inc. | Bonding pad arrangment design for semiconductor package |

| WO2017183352A1 (ja) | 2016-04-22 | 2017-10-26 | 株式会社ソシオネクスト | 半導体チップおよびこれを備えた半導体装置 |

| JP2018107296A (ja) * | 2016-12-27 | 2018-07-05 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP7273654B2 (ja) * | 2019-08-09 | 2023-05-15 | ルネサスエレクトロニクス株式会社 | 半導体装置、その製造方法および電子装置 |

| US20210287965A1 (en) * | 2020-03-13 | 2021-09-16 | Samsung Electronics Co., Ltd. | Semiconductor device |

| US11688686B2 (en) | 2020-07-14 | 2023-06-27 | Samsung Electronics Co., Ltd. | Semiconductor device including an input/output circuit |

| CN114220825B (zh) * | 2022-02-22 | 2022-08-23 | 上海天马微电子有限公司 | 发光驱动基板、发光面板及显示装置 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2745628B2 (ja) * | 1989-01-25 | 1998-04-28 | 日本電気株式会社 | 樹脂封止型半導体装置 |

| JP2758322B2 (ja) * | 1992-09-30 | 1998-05-28 | 京セラ株式会社 | 電子部品搭載用回路基板 |

| JP3278093B2 (ja) * | 1994-08-31 | 2002-04-30 | 沖電気工業株式会社 | 半導体デバイス |

| FR2764115B1 (fr) * | 1997-06-02 | 2001-06-08 | Sgs Thomson Microelectronics | Dispositif semiconducteur et procede de connexion des fils internes de masse d'un tel dispositif |

| JP3472455B2 (ja) * | 1997-09-12 | 2003-12-02 | 沖電気工業株式会社 | 半導体集積回路装置及びそのパッケージ構造 |

| JPH11284006A (ja) * | 1998-03-31 | 1999-10-15 | Fujitsu Ltd | 半導体装置 |

| JP3375560B2 (ja) * | 1999-02-15 | 2003-02-10 | 松下電器産業株式会社 | 半導体装置 |

| JP4071914B2 (ja) * | 2000-02-25 | 2008-04-02 | 沖電気工業株式会社 | 半導体素子及びこれを用いた半導体装置 |

| US6476506B1 (en) * | 2001-09-28 | 2002-11-05 | Motorola, Inc. | Packaged semiconductor with multiple rows of bond pads and method therefor |

| TW536765B (en) * | 2001-10-19 | 2003-06-11 | Acer Labs Inc | Chip package structure for array type bounding pad |

| TW511193B (en) * | 2001-12-13 | 2002-11-21 | Acer Labs Inc | Inner circuit structure of array type bonding pad chip and its manufacturing method |

| TWM244576U (en) * | 2003-07-16 | 2004-09-21 | Via Tech Inc | Chip package structure |

| US6956286B2 (en) * | 2003-08-05 | 2005-10-18 | International Business Machines Corporation | Integrated circuit package with overlapping bond fingers |

| JP2005136302A (ja) * | 2003-10-31 | 2005-05-26 | Renesas Technology Corp | 半導体集積回路装置の製造方法 |

| JP4570868B2 (ja) * | 2003-12-26 | 2010-10-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP4533173B2 (ja) * | 2004-02-24 | 2010-09-01 | キヤノン株式会社 | 半導体集積回路装置 |

| JP4438579B2 (ja) * | 2004-09-14 | 2010-03-24 | 株式会社デンソー | センサ装置 |

| DE102005009163B4 (de) * | 2005-02-25 | 2013-08-14 | Infineon Technologies Ag | Halbleiterbauteil mit einem Halbleiterchip, der Signalkontaktflächen und Versorgungskontaktflächen aufweist, sowie Verfahren zur Herstellung des Halbleiterbauteils |

| US7675168B2 (en) * | 2005-02-25 | 2010-03-09 | Agere Systems Inc. | Integrated circuit with staggered differential wire bond pairs |

-

2003

- 2003-12-26 JP JP2003433851A patent/JP4570868B2/ja not_active Expired - Fee Related

-

2004

- 2004-12-07 US US11/005,217 patent/US7211903B2/en not_active Expired - Lifetime

- 2004-12-08 TW TW93138020A patent/TWI364803B/zh not_active IP Right Cessation

-

2007

- 2007-03-29 US US11/730,088 patent/US7323788B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US20050162880A1 (en) | 2005-07-28 |

| TW200531194A (en) | 2005-09-16 |

| JP2005191447A (ja) | 2005-07-14 |

| TWI364803B (en) | 2012-05-21 |

| US7211903B2 (en) | 2007-05-01 |

| US20070170601A1 (en) | 2007-07-26 |

| US7323788B2 (en) | 2008-01-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4570868B2 (ja) | 半導体装置 | |

| JP3657246B2 (ja) | 半導体装置 | |

| CN100435326C (zh) | 集成电路芯片i/o单元及其制造方法 | |

| US6449169B1 (en) | Ball grid array package with interdigitated power ring and ground ring | |

| JP5342154B2 (ja) | 半導体装置の製造方法 | |

| CN101615604B (zh) | 半导体器件和半导体集成电路 | |

| US9947651B2 (en) | Semiconductor integrated circuit device having an NMOS with a high resistance drain terminal | |

| US9087710B2 (en) | Semiconductor device with stacked semiconductor chips | |

| US9087822B2 (en) | Semiconductor device | |

| EP1897138B1 (en) | Semiconductor device and mounting structure thereof | |

| US20110089561A1 (en) | Semiconductor package and method of manufacturing the same | |

| US20080006930A1 (en) | Semiconductor package | |

| JP4068616B2 (ja) | 半導体装置 | |

| CN100369254C (zh) | 半导体集成电路器件 | |

| JP2005150248A (ja) | 半導体集積回路装置 | |

| JP2007103423A (ja) | 半導体装置及びその製造方法 | |

| US5814892A (en) | Semiconductor die with staggered bond pads | |

| US8362614B2 (en) | Fine pitch grid array type semiconductor device | |

| JP2008078354A (ja) | 半導体装置 | |

| CN111755394B (zh) | 倒装芯片封装 | |

| JP4167684B2 (ja) | 半導体集積回路装置とその製造方法及びそのテスト方法 | |

| US20100193929A1 (en) | Semiconductor device | |

| US20100320580A1 (en) | Equipotential pad connection | |

| JP2010263234A (ja) | 半導体集積回路装置 | |

| JP2014096504A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061225 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061225 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081008 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091214 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100727 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100811 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130820 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4570868 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |