JP4533173B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP4533173B2 JP4533173B2 JP2005033018A JP2005033018A JP4533173B2 JP 4533173 B2 JP4533173 B2 JP 4533173B2 JP 2005033018 A JP2005033018 A JP 2005033018A JP 2005033018 A JP2005033018 A JP 2005033018A JP 4533173 B2 JP4533173 B2 JP 4533173B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- pad

- wire bonding

- pads

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/50—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor for integrated circuit devices, e.g. power bus, number of leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04042—Bonding areas specifically adapted for wire connectors, e.g. wirebond pads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05599—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/06—Structure, shape, material or disposition of the bonding areas prior to the connecting process of a plurality of bonding areas

- H01L2224/061—Disposition

- H01L2224/0612—Layout

- H01L2224/0615—Mirror array, i.e. array having only a reflection symmetry, i.e. bilateral symmetry

- H01L2224/06153—Mirror array, i.e. array having only a reflection symmetry, i.e. bilateral symmetry with a staggered arrangement, e.g. depopulated array

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/4917—Crossed wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4943—Connecting portions the connecting portions being staggered

- H01L2224/49431—Connecting portions the connecting portions being staggered on the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/494—Connecting portions

- H01L2224/4943—Connecting portions the connecting portions being staggered

- H01L2224/49433—Connecting portions the connecting portions being staggered outside the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8538—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/85399—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01004—Beryllium [Be]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01023—Vanadium [V]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12042—LASER

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15173—Fan-out arrangement of the internal vias in a single layer of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

- Semiconductor Integrated Circuits (AREA)

- Wire Bonding (AREA)

Description

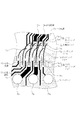

12、52、72 半導体チップ上のワイヤボンディングパッド

12a、52a、72a 半導体チップ上の給電パッド

12b、52b、72b 半導体チップ上の信号パッド

13a、53a、73a 半導体チップ上の給電配線

13b、53b、73b 半導体チップ上の信号配線

14、24、34、44、54、64、74、74a ボンディングワイヤ

15、25、35、45、55、65、75 パッケージ

16、36、46、56、66、76 パッケージ上のワイヤボンディングパッド

16a、36a、46a、56a、66a、76a パッケージ上の給電パッド

16b、36b、46b、56b、66b、76b パッケージ上の信号パッド

17a、27a、37a、47a、67a、57a、77a パッケージ上の給電配線

17b、27b、37b、47b、57b、67b、77b パッケージ上の信号配線

Claims (8)

- 半導体集積回路部と、該半導体集積回路部の周辺に配列され該半導体集積回路部と接続された複数の第1のワイヤボンディングパッドとを有する半導体チップと、前記半導体チップを封入する複数の配線を有するパッケージと、前記半導体チップに設けられた第1のワイヤボンディングパッドと前記パッケージに設けられた配線とを接続するボンディングワイヤとを備えた半導体集積回路装置であって、

前記第1のワイヤボンディングパッドは、前記半導体集積回路部に信号を伝送する第1の信号パッドと前記半導体集積回路部に給電する第1の給電パッドが、前記半導体チップの周辺に沿って複数列に配列されており、前記第1のワイヤボンディングパッドのうち、前記第1の給電パッドはすべて、前記複数列の最も内側の列に配置されており、前記第1の給電パッドから引き出される第1の給電配線の幅は、該第1の給電パッドの幅以上であり、前記複数列の最も内側の列以外の列に配置されている第1の信号パッドから引き出される第1の信号配線の幅は、該第1の信号パッドの幅よりも細いことを特徴とする半導体集積回路装置。 - 前記複数列に配列された第1のワイヤボンディングパッドは、千鳥状に配列されていることを特徴とする請求項1に記載の半導体集積回路装置。

- 前記第1の給電パッドは隣接して配置されており、隣接する2つの給電パッドの間で前記半導体チップの前記複数列の外側の列には、配線と接続されていないNCパッドが配置されている事を特徴とする請求項2に記載の半導体集積回路装置。

- 前記パッケージに設けられた複数の配線には、前記第1のワイヤボンディングパッドと前記ボンディングワイヤによって接続される第2のワイヤボンディングパッドが設けられており、

前記第2のワイヤボンディングパッドは、前記パッケージの周辺に沿って複数列に配列された第2の信号パッドと第2の給電パッドからなっており、前記第2のワイヤボンディングパッドのうち、前記第2の給電パッドはすべて、前記複数列の最も内側の列に配置されており、前記第2の給電パッドから引き出される第2の給電配線の幅は、該第2の給電パッドの幅以上であり、前記複数列の最も内側の列以外の列に配置されている第2の信号パッドから引き出される信号配線の幅は、該第2の信号パッドの幅よりも細いことを特徴とする請求項1乃至3のいずれか1項に記載の半導体集積回路装置。 - 前記パッケージは前記半導体チップの外側に複数列のボールランドを有するBGAパッケージであり、前記複数列のボールランドは、前記第2の給電パッドと第2の給電配線により接続される給電ランドと、前記第2の信号パッドと第2の信号配線により接続される信号ランドとからなり、前記給電ランドは、前記複数列のボールランドのうち前記第2の給電パッドに最も近い列に配置されていることを特徴とする請求項4に記載の半導体集積回路装置。

- 前記複数列に配列された第2のワイヤボンディングパッドは、千鳥状に配列されていることを特徴とする請求項4または5に記載の半導体集積回路装置。

- 前記第2の給電パッドは隣接して配置されており、隣接する2つの給電パッドの間で半導体チップの前記複数列の外側の列には、配線と接続されていないNCパッドが配置されている事を特徴とする請求項6に記載の半導体集積回路装置。

- 半導体集積回路部と、該半導体集積回路部の周辺に配列され該半導体集積回路部と接続された複数の配線とを有する半導体チップと、前記半導体チップを封入し、前記半導体チップの周辺部には第2のワイヤボンディングパッドと、前記第2のワイヤボンディングパッドと接続された配線とを有するパッケージと、前記半導体チップに設けられた配線と前記パッケージに設けられた第2のワイヤボンディングパッドとを接続するボンディングワイヤとを備えた半導体集積回路装置であって、

前記第2のワイヤボンディングパッドは、前記パッケージの周辺に沿って複数列に配列された第2の信号パッドと第2の給電パッドからなっており、前記第2の給電パッドはすべて、前記複数列の最も内側の列に配置されており、前記第2の給電パッドから引き出される第2の給電配線の幅は、該第2の給電パッドの幅以上であり、前記複数列の最も内側の列以外の列に配置されている第2の信号パッドから引き出される信号配線の幅は、該第2の信号パッドの幅よりも細いことを特徴とするの半導体集積回路装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005033018A JP4533173B2 (ja) | 2004-02-24 | 2005-02-09 | 半導体集積回路装置 |

| US11/061,438 US7259467B2 (en) | 2004-02-24 | 2005-02-22 | Semiconductor integrated circuit device |

| US11/765,185 US7538441B2 (en) | 2004-02-24 | 2007-06-19 | Chip with power and signal pads connected to power and signal lines on substrate |

| US12/429,461 US7902658B2 (en) | 2004-02-24 | 2009-04-24 | Integrated circuit having wide power lines |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004047408 | 2004-02-24 | ||

| JP2005033018A JP4533173B2 (ja) | 2004-02-24 | 2005-02-09 | 半導体集積回路装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005277392A JP2005277392A (ja) | 2005-10-06 |

| JP2005277392A5 JP2005277392A5 (ja) | 2006-09-14 |

| JP4533173B2 true JP4533173B2 (ja) | 2010-09-01 |

Family

ID=34863514

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005033018A Expired - Fee Related JP4533173B2 (ja) | 2004-02-24 | 2005-02-09 | 半導体集積回路装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (3) | US7259467B2 (ja) |

| JP (1) | JP4533173B2 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4570868B2 (ja) * | 2003-12-26 | 2010-10-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP4533173B2 (ja) * | 2004-02-24 | 2010-09-01 | キヤノン株式会社 | 半導体集積回路装置 |

| JP4006447B2 (ja) * | 2004-04-16 | 2007-11-14 | キヤノン株式会社 | 半導体装置およびプリント回路板 |

| JP4353328B2 (ja) * | 2005-09-28 | 2009-10-28 | エルピーダメモリ株式会社 | 半導体パッケージの製造方法及び半導体パッケージ |

| JP4993929B2 (ja) * | 2006-03-23 | 2012-08-08 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| KR100843220B1 (ko) * | 2006-12-19 | 2008-07-02 | 삼성전자주식회사 | 동일 평면상 엘.씨 벨런싱이 달성된 인쇄회로기판 |

| US8922028B2 (en) * | 2007-02-13 | 2014-12-30 | Advanced Semiconductor Engineering, Inc. | Semiconductor package |

| TWI333689B (en) * | 2007-02-13 | 2010-11-21 | Advanced Semiconductor Eng | Semiconductor package |

| TWI358577B (en) * | 2007-06-20 | 2012-02-21 | Au Optronics Corp | Light emitting device and manufacture method there |

| US7863099B2 (en) | 2007-06-27 | 2011-01-04 | Stats Chippac Ltd. | Integrated circuit package system with overhanging connection stack |

| JP2009164195A (ja) | 2007-12-28 | 2009-07-23 | Panasonic Corp | 半導体チップ |

| JP4991637B2 (ja) * | 2008-06-12 | 2012-08-01 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US7825527B2 (en) * | 2008-06-13 | 2010-11-02 | Altera Corporation | Return loss techniques in wirebond packages for high-speed data communications |

| JP5656644B2 (ja) * | 2008-12-19 | 2015-01-21 | 株式会社アドバンテスト | 半導体装置、半導体装置の製造方法およびスイッチ回路 |

| US20110103030A1 (en) * | 2009-11-02 | 2011-05-05 | International Business Machines Corporation | Packages and Methods for Mitigating Plating Stub Effects |

| EP3345213A4 (en) * | 2015-09-04 | 2019-04-24 | Octavo Systems LLC | IMPROVED SYSTEM USING A SYSTEM IN PACKAGING COMPONENTS |

| WO2017099759A1 (en) * | 2015-12-09 | 2017-06-15 | Intel Corporation | Connection pads for low cross-talk vertical wirebonds |

| CN107123636B (zh) * | 2016-02-25 | 2020-01-10 | 瑞昱半导体股份有限公司 | 集成电路装置 |

| US10833238B2 (en) | 2018-08-27 | 2020-11-10 | International Business Machines Corporation | Wirebond cross-talk reduction for quantum computing chips |

| JP7362380B2 (ja) | 2019-09-12 | 2023-10-17 | キヤノン株式会社 | 配線基板及び半導体装置 |

| CN113703099A (zh) * | 2020-05-21 | 2021-11-26 | 青岛海信宽带多媒体技术有限公司 | 一种光模块 |

| US20240248357A1 (en) * | 2022-02-23 | 2024-07-25 | Hefei BOE Ruisheng Technology Co., Ltd. | Light emitting substrate, backlight module, and display device |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04252073A (ja) * | 1991-01-10 | 1992-09-08 | Nec Ic Microcomput Syst Ltd | マスタースライス方式半導体集積回路 |

| JPH1140754A (ja) * | 1997-07-17 | 1999-02-12 | Mitsubishi Electric Corp | 半導体装置 |

| JPH1187399A (ja) * | 1997-09-12 | 1999-03-30 | Oki Electric Ind Co Ltd | 半導体集積回路装置及びそのパッケージ構造 |

| JPH11284006A (ja) * | 1998-03-31 | 1999-10-15 | Fujitsu Ltd | 半導体装置 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05160333A (ja) | 1991-12-05 | 1993-06-25 | Sharp Corp | 半導体集積回路装置 |

| US5468999A (en) * | 1994-05-26 | 1995-11-21 | Motorola, Inc. | Liquid encapsulated ball grid array semiconductor device with fine pitch wire bonding |

| JP2716005B2 (ja) * | 1995-07-04 | 1998-02-18 | 日本電気株式会社 | ワイヤボンド型半導体装置 |

| US6008532A (en) * | 1997-10-23 | 1999-12-28 | Lsi Logic Corporation | Integrated circuit package having bond fingers with alternate bonding areas |

| US6410990B2 (en) * | 1997-12-12 | 2002-06-25 | Intel Corporation | Integrated circuit device having C4 and wire bond connections |

| JP3516608B2 (ja) * | 1999-04-27 | 2004-04-05 | 沖電気工業株式会社 | 半導体装置 |

| JP4071914B2 (ja) * | 2000-02-25 | 2008-04-02 | 沖電気工業株式会社 | 半導体素子及びこれを用いた半導体装置 |

| US6291898B1 (en) * | 2000-03-27 | 2001-09-18 | Advanced Semiconductor Engineering, Inc. | Ball grid array package |

| TW495940B (en) * | 2001-07-20 | 2002-07-21 | Via Tech Inc | Method for forming a grid array packaged integrated circuit |

| US6476506B1 (en) * | 2001-09-28 | 2002-11-05 | Motorola, Inc. | Packaged semiconductor with multiple rows of bond pads and method therefor |

| TW517362B (en) * | 2002-01-10 | 2003-01-11 | Advanced Semiconductor Eng | Ball grid array package structure |

| US6700207B2 (en) * | 2002-08-05 | 2004-03-02 | Lsi Logic Corporation | Flip-chip ball grid array package for electromigration testing |

| JP2005160333A (ja) | 2003-11-28 | 2005-06-23 | Q P Corp | オリゴヌクレオチド及びこれをプライマーとして用いたラクトバチルス属細菌の検出方法 |

| JP4533173B2 (ja) * | 2004-02-24 | 2010-09-01 | キヤノン株式会社 | 半導体集積回路装置 |

-

2005

- 2005-02-09 JP JP2005033018A patent/JP4533173B2/ja not_active Expired - Fee Related

- 2005-02-22 US US11/061,438 patent/US7259467B2/en not_active Expired - Fee Related

-

2007

- 2007-06-19 US US11/765,185 patent/US7538441B2/en not_active Expired - Fee Related

-

2009

- 2009-04-24 US US12/429,461 patent/US7902658B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04252073A (ja) * | 1991-01-10 | 1992-09-08 | Nec Ic Microcomput Syst Ltd | マスタースライス方式半導体集積回路 |

| JPH1140754A (ja) * | 1997-07-17 | 1999-02-12 | Mitsubishi Electric Corp | 半導体装置 |

| JPH1187399A (ja) * | 1997-09-12 | 1999-03-30 | Oki Electric Ind Co Ltd | 半導体集積回路装置及びそのパッケージ構造 |

| JPH11284006A (ja) * | 1998-03-31 | 1999-10-15 | Fujitsu Ltd | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7259467B2 (en) | 2007-08-21 |

| US7902658B2 (en) | 2011-03-08 |

| US20050184403A1 (en) | 2005-08-25 |

| JP2005277392A (ja) | 2005-10-06 |

| US7538441B2 (en) | 2009-05-26 |

| US20090200666A1 (en) | 2009-08-13 |

| US20070235874A1 (en) | 2007-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4533173B2 (ja) | 半導体集積回路装置 | |

| KR100240525B1 (ko) | 반도체장치 및 그것을 사용한 전자장치 | |

| US7323788B2 (en) | Semiconductor device and manufacturing method of them | |

| JP3657246B2 (ja) | 半導体装置 | |

| JP2003124383A (ja) | 半導体装置と電子装置 | |

| JP2010192680A (ja) | 半導体装置 | |

| US7557646B2 (en) | Semiconductor device with non-intersecting power and ground wiring patterns | |

| TWI715234B (zh) | 晶片封裝模組 | |

| JP5264135B2 (ja) | 半導体集積回路及びマルチチップモジュール | |

| US8362614B2 (en) | Fine pitch grid array type semiconductor device | |

| JP5658640B2 (ja) | 半導体装置 | |

| KR100850286B1 (ko) | 전자소자가 장착된 반도체 칩 패키지 및 이를 구비하는집적회로 모듈 | |

| JP2009081293A (ja) | 半導体チップ、及び複数の半導体チップが搭載された半導体装置 | |

| US11823987B2 (en) | Circuit board and semiconductor apparatus | |

| US10937753B1 (en) | Semiconductor device | |

| US20080136011A1 (en) | Semiconductor device | |

| JP4243621B2 (ja) | 半導体パッケージ | |

| JP2002299568A (ja) | Icチップ | |

| WO1999013509A1 (en) | Semiconductor device | |

| JP3540232B2 (ja) | 半導体装置 | |

| JP3846777B2 (ja) | ボールグリッドアレイパッケージ | |

| US8669593B2 (en) | Semiconductor integrated circuit | |

| CN118039613A (zh) | 半导体器件 | |

| JP2009010410A (ja) | 半導体装置 | |

| JP2006319237A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060727 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060727 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091008 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091013 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091214 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100309 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100430 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100525 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100611 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130618 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |