JP4419067B2 - ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール - Google Patents

ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール Download PDFInfo

- Publication number

- JP4419067B2 JP4419067B2 JP2004217509A JP2004217509A JP4419067B2 JP 4419067 B2 JP4419067 B2 JP 4419067B2 JP 2004217509 A JP2004217509 A JP 2004217509A JP 2004217509 A JP2004217509 A JP 2004217509A JP 4419067 B2 JP4419067 B2 JP 4419067B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- delay

- data

- circuit

- input

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/01—Shaping pulses

- H03K5/08—Shaping pulses by limiting; by thresholding; by slicing, i.e. combined limiting and thresholding

- H03K5/082—Shaping pulses by limiting; by thresholding; by slicing, i.e. combined limiting and thresholding with an adaptive threshold

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/135—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of time reference signals, e.g. clock signals

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Dc Digital Transmission (AREA)

- Pulse Circuits (AREA)

Description

これを回避するため特許文献1、2に示すような従来技術がある。

データの逆符号を送信するためにジッタが低減できていた。

また、自動遅延調整回路機構によりジッタ低減するための遅延量の設定が可能なため、ケーブル長など装置毎に異なる状態の伝送線路であっても自動的に遅延量を調整できるので、装置依存のない汎用インターフェースを持つLSIを提供することができる。

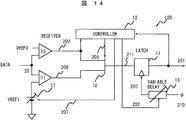

遅延制御回路12と遅延可変回路13の組合せで図2の様な遅延ΔTiに対応した制御を行う。

波形301は時刻T0以前の入力データパターンが連続したLであり、その後、Hが時刻T6まで続いた波形である。ここで、点線で示した時刻T0〜T5はジッタ調整回路機能を有する入力回路100に入力されたデータのサイクルを示す。なお、対象としている範囲で連続したデータパターンをL*と表すと、波形301のデータパターン(...LLLLHHH...)は(L*H*)と記述できる。

波形302は、時刻T0以前がLであり、1サイクルのみHとなり、その後時刻T2以降はLとなる。このデータパターンは(L*HL*)と表せる。

波形301は時刻T0以降H状態であり伝送線路の鈍りのため、おおよそ充電曲線を描く。もちろん、伝送線路上のインピーダンスミスマッチに起因する反射やクロストークも重畳されるが、良く設計された伝送線路の場合、これらの反射・クロストークノイズは小さいが、そうであっても高周波での誘電損失や表皮効果による波形鈍りは大きく受端波形は301のように鈍る。

完全に立ち上がる前にあるいは充電される前にデータが変化すると次サイクルの波形軌線が大きく変わる。図2の波形302は、波形301の充電中途の位置からLが始まるので、参照電圧VREF0を横切る時間が波形301に比べて早くなっている。波形301のVREF0を横切る時間を基準にとると各波形302〜305にはVREF0を横切る時間に時間差が有ることが分かる。この時間差を、波形302〜305に対してそれぞれΔT1〜ΔT4(或いはΔTi)と表す。

ここでレシーバ10の遅延時間は無視できるものとして書いてある。203−1〜203−3はクロック信号210を遅延可変回路13と遅延制御回路12で入力データパターンに従った遅延量を持つ遅延クロック信号であり、ラッチ11は該信号203−1〜203−3に従いデータをラッチする。

(1)L*H*L*入力(波形302)に対して

この入力データに対するレシーバ10の出力波形は200−1である。T0サイクル(T0〜T1)におけるレシーバ出力200−1に対して、遅延制御回路12は遅延可変回路13に対してk×ΔT1早めるように機能し、ラッチ11は該可変遅延のクロック信号203−1で取り込む。ここで、kは0.5などの適切な定数である。またこの203−1には、実線と点線があるが、実線は対象データサイクルで確定された信号であり、点線は未確定の信号を意味する。この様に動作することで、T0サイクルでHのデータを取る再に安定したセットアップ、ホールド時間を確保することができる。

(2)(L*HHL*)入力(波形303)に対して

この入力データに対するレシーバ出力10の出力波形は200−2である。T1サイクル(T1〜T2)おける波形レシーバ出力200−2に対して、遅延制御回路12は遅延可変回路13に対してk×ΔT2早めるように機能し、ラッチ11は該可変遅延のクロック信号203−2で取り込む。この様に動作することで、T1サイクルで安定してHのデータを取る際に、安定したホールド時間を確保することができる。

同様に入力データがL*HHHL*のへ記304に対しては、T2サイクル(T2〜T3)でラッチ11の取り込みタイミングを遅延可変回路13を用いてk×ΔT3早める様に動作する。この様に動作することで、T2サイクルでHのデータを取る際に、安定したホールド時間を確保することができる。

このように、遅延制御回路12と遅延可変回路13が動作すればジッタ調整回路機能を有する入力回路100は(L*H)や(H*L)の様な前サイクルのデータに関わらずデータを取り込めることになり、これらの入力データに対してジッタを低減できることになる。

遅延制御回路12には、レシーバ出力信号200、同期出力信号201が入力される。そして、内部処理された後、遅延制御信号202を出力する。

図6は、時刻T0、T1、T2...という、データ転送のサイクル毎のレシーバに入力される入力波形を示しており、実線310は時刻T0での立上り波形、波線311は時刻T0での立下がり波形を示している。これらの波形は1サイクル後の時刻T1でも完全にH状態になっておらず、時刻T1、T2、T3、T4の電圧を立上り波形310に対して、w1、w2、w3、w4とする。同様に立下がり波形311に対してはu1、u2、u3、u4とする。この図では切替えから4サイクル後にほぼ信号振幅に充電されることを表しているが、系によりこれより長い場合も短い場合もある。これらの場合は、ui、wiの状態数が異なることになるが、本発明の本質的な動作は同じである。

a)初期値(データ転送前の状態)

v(t) = Vol or Voh (t < 0) ・・・・・ (1)

ここで、Volは伝送線路に接続されているドライバのL状態出力電圧であり、VohはH状態出力電圧である。入力波形v(t)はv(Tn-1)に、Volからw1の、ないしは、Vohからu1の信号振幅が重畳されるので、

b)nサイクル目の入力電圧v(t)

v(t) = v(Tn-1) + Q'n-1u(t - Tn-1) v0(t - Tn-1)

(Tn-1< t ≦ Tn) ・・・・・(2)

ここで、v(Tn-1)はnサイクル目の開始時刻(Tn-1)での入力電圧であり、Q'n-1は(nー1)サイクルとnサイクルのデータQの微分である。遷移がある場合は{+1、 -1}を取り、前者が立上り後者が立下がりを意味する。また、遷移がない場合は"0"となる。そして、v0(t)は、単パルス入力L*H*に対する立上りパルスの電圧関数である。また、u(t)はユニット関数でその定義は、

c)

u(t) = 1 (t ≧ 0)

= 0 (t < 0) ・・・・・(3)

である。

切替えの電圧振幅は同じであるため、u1→w4、u2→w3、u3→w2、u4→w1と状態遷移する。その逆も同じ組合せで、w4→u1、w3→u2、w2→u3、w1→u4と状態遷移する。

d)

ΔT1 = Q'n ( u1 + w1 )

ΔT2 = Q'n ( u2 + w2 )

ΔT3 = Q'n ( u3 + w3 )

ΔT4 = Q'n ( u4 + w4 )= 0 ・・・・・(4)

となる。この演算を行うのが遅延選択回路122である。ここで、Q'nはラッチ124で保持されたXOR回路123の出力信号125で実現されており、また、括弧()内のデータは電圧保持回路121の出力信号126で実現されている。これらの出力信号125と出力信号126の積を取ることで遅延制御信号202を生成できる。

構成の差は、第1の実施例では、遅延される量がラッチ11のクロックであったが、本実施例ではデータ信号を遅延させることにある。構成は、差動コンパレータ10の出力信号200は、遅延可変回路13’を介して、ラッチ11に入力され同期化される。遅延可変回路13’は、遅延制御回路12で制御され、遅延制御回路12は第1の実施例である、図5のように動作する。そのため、遅延制御信号202は、データ信号20の入力データのパターンに応じて遅延調整量を遅延可変回路13’に伝える。

LSI500、501に電源投入シーケンス601後.初期化シーケンス602が動作する。このシーケンスではリセット信号による回路リセットやDLL調整用のクロック入力、LSI内の各レジスタの設定などを行う。これは各LSIの仕様による。

ジッタ位相調整ステップ603に対応した波形を図10bに示す。

入力されたDQ信号351のDQS信号に対応する立上りと立下がり時の位相差ΔT1r、ΔT1fを測定する。簡単のため、レシーバ100の出力信号は鈍っている入力波形351で代表させた。この測定は、図9には書いていない可変遅延素子の段数をインクリメント或いはデクリメントすることで2つの波形の位相を比較し、その比較結果が同じになるまで1サイクルパルス入力を繰り返すことで為される。

更に、DQ信号のレシーバ100の立下がりからの可変遅延回路の遅延量を調整し、DQS信号用のレシーバ100aの別のサイクルの立上り信号と位相比較することで、遅延時間差ΔT1fが求まる。

e)

ΔT1=ΔT1f−ΔT1r ・・・・・(5)

なぜならば、ΔT1rは(L*H)に対するDQ信号の入力回路100とDQS信号の入力回路100aの遅延時間差であり、これをL*HLの立下がりのΔT1fが伝送線路15のデータ依存性を持つ遅延量を含んでいるからである。

また、DRAM32はデータ(DQ)信号36を用いてここには記載されていないメモリコントローラとデータの読み書きを行っている。

また、データ信号36に対してレシーバをC/A信号38と同じくデジッタ入力回路型にすることでデータ信号の高速化にも好適である。

波形301は時刻T0以前の入力データパターンが連続したLであり、その後、Hが時刻T6まで続いた波形である。ここで、点線で示した時刻T0〜T5はジッタ調整回路機能を有する入力回路101に入力されたデータのサイクルを示す。なお、波形301のデータパターンを(L*H*)と記述するのは、実施例1で示した方式に従う。以下同様に、波形302等のデータパターンは、(L*HL*)等と表せる。

波形301乃至305に関する説明は、上述の第5の実施例の場合と同じである。

図16で101は、本発明のジッタ調整回路機能を有する入力回路であり、伝送線路に接続されたデータ信号20とクロック信号(Φ)210を入力とし、データ信号20はクロック信号210で同期を取られ出力信号201として出力される。

11…ラッチ、

12…制御回路、

13,13’ …遅延可変回路、

14,14a…ドライバ、

15,15a…配線、

16…レシーバ、

17…可変電圧源

18…切替えスイッチ

20,20a…データ信号、

30…メモリモジュール、

31…制御・アドレス信号レジスタ、

32…DRAM、

35、38…制御・アドレス信号、

36…データ(DQ)信号、

37…ストローブ(DQS)信号、

100,100’,100a…ジッタ調整回路機能を有する入力回路(デスキュー・レシーバ)、

101、102…ジッタ調整回路機能を有する入力回路(デスキュー・レシーバ)、

122…遅延選択回路、

123…XOR回路、

124…ラッチ、

125…ラッチ124で保持されたXOR回路123の出力信号(Q'n)、

126…電圧保持回路121の出力信号、

200…レシーバ出力信号、

201…同期出力信号、

202…遅延制御信号、

203…遅延されたクロック信号、

210…クロック信号(φ)、

301〜305…伝送線路により鈍った波形、

310…立上り波形、

311…立下り波形、

320…バイナリデータの例、

321…伝送線路により鈍った波形、

322…レシーバで復調されたジッタの含むデータ、

350,360,370…自動遅延調整用の送信バイナリデータ、

351,361,371…自動遅延調整用の入力波形、

500…送信LSI、

501…受信LSI、

601〜607…自動遅延調整シーケンス、

1301…データ幅、

1301〜1308…コンパレータ10からの出力信号、

DQ…データ信号、

DQS…データストローブ信号、

VREF0…参照電圧、

VREF1…参照電圧、

VOL…ドライバのL出力電圧、

VOH…ドライバのH出力電圧、

u1〜u4…遅延可変回路13の内部状態、

w1〜w4…遅延可変回路13の内部状態、

ΔT1〜ΔT4…データパターンに応じた遅延調整量。

Claims (11)

- ディジタルデータを受信するレシーバ回路を有する半導体装置であって、

前記レシーバ回路は、入力された前記ディジタルデータを基準電圧と比較しバイナリデータを出力する差動コンパレータと、前記差動コンパレータからの出力をクロック信号に応じて取り込んで出力信号を出すラッチと、前記差動コンパレータからの出力信号と前記ラッチの出力信号に基き遅延量を決定する遅延制御回路と、前記遅延制御回路の出力信号を受けて前記ラッチへ信号を送る遅延可変回路とからなり、

前記ラッチは、前記遅延制御回路からの遅延量情報に基づき、前記遅延可変回路により出力される遅延されたクロック信号をトリガとして前記差動コンパレータの出力を取り込むことを特徴とする半導体装置。 - 前記遅延制御回路は、前記差動コンパレータの出力信号と前記ラッチの出力信号に基き、前記ディジタルデータの切替えを検出し切替え信号を生成するデータ切替え検出手段と、

前記ラッチの出力信号を用いて、データサイクル毎の前記半導体装置に入力される前記ディジタルデータの入力波形の電圧を保持する電圧保持手段とを有し、

前記電圧保持手段からの状態信号と前記データ切替え検出手段からの前記切替え信号との積を取ることにより遅延可変信号を生成することを特徴とする請求項1に記載の半導体装置。 - 前記電圧保持機能は、抵抗と容量を含む1次回路により構成されることを特徴とする請求項2に記載の半導体装置。

- ディジタルデータを受信するレシーバ回路を有する半導体装置であって、

前記レシーバ回路は、入力された前記ディジタルデータを基準電圧と比較しバイナリデータを出力する差動コンパレータと、クロック信号に応じて出力信号を出力するラッチと、前記差動コンパレータからの出力信号と前記ラッチの出力信号に基き遅延量を決定する遅延制御回路と、前記遅延制御回路の出力信号を受けて前記ラッチへ信号を送る遅延可変回路とからなり、

前記コンパレータの出力信号は、前記遅延制御回路からの遅延情報に基づき前記遅延可変回路により遅延され、前記遅延された前記コンパレータの出力信号を、前記ラッチへクロック信号トリガタイミングで取り込むことを特徴とする半導体装置。 - 前記遅延制御回路は、前記差動コンパレータの出力信号と前記ラッチの出力信号に基き、前記ディジタルデータの切替えを検出し切替え信号を生成するデータ切替え検出手段と、

前記ラッチの出力信号を用いて、データサイクル毎の前記半導体装置に入力される前記ディジタルデータの入力波形の電圧を保持する電圧保持手段とを有し、

前記電圧保持手段からの状態信号と前記データ切替え検出手段からの前記切替え信号との積を取ることにより遅延可変信号を生成することを特徴とする請求項4に記載の半導体装置。 - 前記電圧保持機能は、抵抗と容量を含む1次回路により構成されることを特徴とする請求項5に記載の半導体装置。

- ジッタ低減用自動調整用のシーケンスを有する半導体装置において、

前記半導体装置に有限のデータサイクルの幅を持つパルス信号と、前記パルス信号と同期したストローブ信号が入力され、

前記ストローブ信号を用いて前記パルス信号の立上り時間と、前記パルスの立下り時間との差を計測し求めた遅延差時間を、前記遅延可変回路へ入力する遅延量として前記遅延可変回路に設定することを特徴とする請求項1乃至6のいずれかに一に記載の半導体装置。 - ジッタ低減用自動調整用のシーケンスを有する半導体装置において、

前記半導体装置に有限のデータサイクルの幅を持つパルス信号と、前記パルス信号と同期したストローブ信号が入力され、

前記シーケンスにおけるi番目の動作状態をパラメータiで識別する時、

前記半導体装置にパラメータiのデータサイクル幅を持つパルス信号と、前記パルス信号と同期した前記ストローブ信号が入力され、前記ストローブ信号を用いて前記パルス信号の立上り時間と、前記パルスの立下がり時間との差を計測し、計測された前記時間の差を前記遅延可変回路のi番目の遅延量として前記遅延制御回路に設定し、

iを1からnまで繰り返して遅延量調整を行なうことを特徴とする請求項1乃至6のいずれかに一に記載の半導体装置。 - 複数のDRAMと、

前記複数のDRAMに信号線により接続され、制御・アドレス信号およびストローブ信号を前記複数のDRAMに伝送するレジスタとを有し、

前記複数のDRAMの各々には、請求項1乃至8に記載の半導体装置により構成されたデータ入力回路が搭載されていることを特徴とするメモリ素子。 - 請求項9に記載のメモリ素子を、複数個搭載するメモリモジュールであって、

前記メモリ素子に送信される制御・アドレス信号は、前記メモリモジュールに搭載されたレジスタにより前記メモリ素子に分配され、分配された前記制御・アドレス信号のデータ取り込み用の前記メモリ素子にジッタ低減機能を有するレシーバ回路を用いたことを特徴とするメモリモジュール。 - ディジタルデータを受信するレシーバ回路を有する半導体装置であって、

前記レシーバ回路は、入力された前記ディジタルデータを基準電圧と比較しバイナリデータを出力する第1および第2の差動コンパレータと、前記第2の差動コンパレータの基準電圧を設定する可変電圧源と、前記第1および第2の差動コンパレータからの出力信号のどちらかを所定の時間保持し出力するラッチと、前記第1および第2の差動コンパレータからの出力信号のどちらかを選択し前記ラッチに伝送する切替えスイッチと、前記第1の差動コンパレータからの出力信号と前記ラッチの出力信号に基き参照電圧及び遅延量を決定する制御回路と、前記制御回路から信号を受け、前記遅延量を前記ラッチに伝送する遅延可変回路とからなり、

前記可変電圧源は、前記制御回路からの参照電圧情報に基き制御され前記第2の差動コンパレータに対する参照電圧を決定し、決定された前記参照電圧に応じて前記コンパレータの出力信号が遅延され、遅延された前記コンパレータの出力信号を前記切替えスイッチを介して、前記ラッチはデータ信号として取り込み、さらに前記ラッチは、前記制御回路からの遅延量情報に基づき、前記遅延可変回路により出力される遅延されたクロック信号をトリガとして前記差動コンパレータの出力を取り込むことを特徴とする半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004217509A JP4419067B2 (ja) | 2004-07-26 | 2004-07-26 | ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール |

| US10/982,946 US7558336B2 (en) | 2004-07-26 | 2004-11-08 | Semiconductor device, memory device and memory module having digital interface |

| CN200410101360A CN100588148C (zh) | 2004-07-26 | 2004-12-17 | 具有数字接口的半导体器件 |

| US12/481,798 US7856072B2 (en) | 2004-07-26 | 2009-06-10 | Semiconductor device, memory device and memory module having digital interface |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004217509A JP4419067B2 (ja) | 2004-07-26 | 2004-07-26 | ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009216805A Division JP4945616B2 (ja) | 2009-09-18 | 2009-09-18 | ディジタルインターフェースを有する半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006041818A JP2006041818A (ja) | 2006-02-09 |

| JP2006041818A5 JP2006041818A5 (ja) | 2007-06-28 |

| JP4419067B2 true JP4419067B2 (ja) | 2010-02-24 |

Family

ID=35657098

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004217509A Expired - Fee Related JP4419067B2 (ja) | 2004-07-26 | 2004-07-26 | ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7558336B2 (ja) |

| JP (1) | JP4419067B2 (ja) |

| CN (1) | CN100588148C (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI268473B (en) * | 2004-11-04 | 2006-12-11 | Realtek Semiconductor Corp | Display controlling device and controlling method |

| KR100692529B1 (ko) * | 2005-07-01 | 2007-03-09 | 삼성전자주식회사 | 최적화된 딜레이 타임 결정 방법, 장치 및 최적화된 딜레이타임 결정 프로그램이 기록된 컴퓨터로 판독 가능한기록매체 |

| JP4753800B2 (ja) * | 2006-06-05 | 2011-08-24 | 日本電信電話株式会社 | Cdr回路 |

| US8384410B1 (en) | 2007-08-24 | 2013-02-26 | Advantest (Singapore) Pte Ltd | Parallel test circuit with active devices |

| US8242796B2 (en) * | 2008-02-21 | 2012-08-14 | Advantest (Singapore) Pte Ltd | Transmit/receive unit, and methods and apparatus for transmitting signals between transmit/receive units |

| JP5614791B2 (ja) | 2008-02-28 | 2014-10-29 | 日本電気株式会社 | 伝送方法、伝送回路及び伝送システム |

| JP4992927B2 (ja) * | 2009-03-24 | 2012-08-08 | 富士通株式会社 | シリアルパラレル変換装置 |

| CN102129362B (zh) * | 2010-01-14 | 2015-08-05 | 旺宏电子股份有限公司 | 指令解码电路及其方法 |

| KR20130045652A (ko) * | 2011-10-26 | 2013-05-06 | 에스케이하이닉스 주식회사 | 신호 지연 회로 |

| US8867595B1 (en) * | 2012-06-25 | 2014-10-21 | Rambus Inc. | Reference voltage generation and calibration for single-ended signaling |

| JP6068193B2 (ja) * | 2013-02-28 | 2017-01-25 | シナプティクス・ジャパン合同会社 | 受信装置及び送受信システム |

| WO2014138091A1 (en) * | 2013-03-05 | 2014-09-12 | Silicon Image, Inc. | Calibration of single-ended high-speed interfaces |

| JP6417094B2 (ja) * | 2013-12-18 | 2018-10-31 | キヤノン株式会社 | 記録再生装置、記録再生装置の制御方法及びコンピュータプログラム |

| JP6476659B2 (ja) | 2014-08-28 | 2019-03-06 | 富士通株式会社 | 信号再生回路および信号再生方法 |

| JP6421515B2 (ja) * | 2014-09-25 | 2018-11-14 | 富士通株式会社 | 信号再生回路および信号再生方法 |

| TWI705666B (zh) * | 2015-06-15 | 2020-09-21 | 日商新力股份有限公司 | 傳送裝置、接收裝置、通信系統 |

| US10164732B2 (en) * | 2015-06-24 | 2018-12-25 | Intel IP Corporation | Encoding circuit, method for transmitting data over a data bus, and radio communication device |

| KR20180000199A (ko) * | 2016-06-22 | 2018-01-02 | 에스케이하이닉스 주식회사 | 크로스 토크를 보상할 수 있는 인터페이스 회로, 이를 포함하는 반도체 장치 및 시스템 |

| DE102018124375A1 (de) * | 2017-11-21 | 2019-05-23 | Samsung Electronics Co., Ltd. | Betriebsverfahren eines signalempfängers, pulsbreitensteuerungund elektronische vorrichtung mit denselben |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4779617A (en) * | 1986-10-06 | 1988-10-25 | Telectronics N.V. | Pacemaker noise rejection system |

| US4907230A (en) * | 1988-02-29 | 1990-03-06 | Rik Heller | Apparatus and method for testing printed circuit boards and their components |

| US5297091A (en) | 1991-10-31 | 1994-03-22 | International Business Machines Corporation | Early row address strobe (RAS) precharge |

| KR940007846B1 (ko) * | 1991-12-09 | 1994-08-25 | 주식회사 금성사 | 움직임 검출장치 |

| JP3489147B2 (ja) * | 1993-09-20 | 2004-01-19 | 株式会社日立製作所 | データ転送方式 |

| JPH07154381A (ja) * | 1993-11-30 | 1995-06-16 | Hitachi Ltd | データ転送装置 |

| JPH07177202A (ja) * | 1993-12-21 | 1995-07-14 | Mitsubishi Electric Corp | 通信制御装置 |

| JP4052697B2 (ja) * | 1996-10-09 | 2008-02-27 | 富士通株式会社 | 信号伝送システム、および、該信号伝送システムのレシーバ回路 |

| JP3979690B2 (ja) * | 1996-12-27 | 2007-09-19 | 富士通株式会社 | 半導体記憶装置システム及び半導体記憶装置 |

| US6247138B1 (en) * | 1997-06-12 | 2001-06-12 | Fujitsu Limited | Timing signal generating circuit, semiconductor integrated circuit device and semiconductor integrated circuit system to which the timing signal generating circuit is applied, and signal transmission system |

| US5953521A (en) | 1997-11-03 | 1999-09-14 | Intel Corporation | Data-pattern induced skew reducer |

| JPH11306757A (ja) * | 1998-04-27 | 1999-11-05 | Mitsubishi Electric Corp | 同期型半導体記憶装置 |

| TW440767B (en) * | 1998-06-02 | 2001-06-16 | Fujitsu Ltd | Method of and apparatus for correctly transmitting signals at high speed without waveform distortion |

| JP2000148656A (ja) * | 1998-11-09 | 2000-05-30 | Mitsubishi Electric Corp | メモリシステム |

| JP2000155751A (ja) * | 1998-11-18 | 2000-06-06 | Mitsubishi Electric Corp | システムlsi |

| US6577687B2 (en) | 1998-12-23 | 2003-06-10 | Maxtor Corporation | Method for transmitting data over a data bus with minimized digital inter-symbol interference |

| JP4683690B2 (ja) * | 1999-11-05 | 2011-05-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US7123660B2 (en) * | 2001-02-27 | 2006-10-17 | Jazio, Inc. | Method and system for deskewing parallel bus channels to increase data transfer rates |

| KR100426990B1 (ko) * | 2001-06-27 | 2004-04-13 | 삼성전자주식회사 | 외부의 코드에 따라 프로그래머블하게 기준 전압을 발생시키는 기준 전압 발생 회로 |

| FI113312B (fi) * | 2002-04-19 | 2004-03-31 | Micro Analog Syst Oy | Komparaattoripiiri |

| US6661717B1 (en) * | 2002-05-30 | 2003-12-09 | Micron Technology, Inc. | Dynamically centered setup-time and hold-time window |

| JP2004127147A (ja) * | 2002-10-07 | 2004-04-22 | Hitachi Ltd | デスキュー回路およびそれを用いたディスクアレイ制御装置 |

| JP3742051B2 (ja) | 2002-10-31 | 2006-02-01 | エルピーダメモリ株式会社 | メモリモジュール、メモリチップ、及びメモリシステム |

| US6970029B2 (en) * | 2003-12-30 | 2005-11-29 | Intel Corporation | Variable-delay signal generators and methods of operation therefor |

| KR100673899B1 (ko) * | 2005-03-02 | 2007-01-25 | 주식회사 하이닉스반도체 | 반도체 소자의 데이터 입력 버퍼 |

-

2004

- 2004-07-26 JP JP2004217509A patent/JP4419067B2/ja not_active Expired - Fee Related

- 2004-11-08 US US10/982,946 patent/US7558336B2/en not_active Expired - Fee Related

- 2004-12-17 CN CN200410101360A patent/CN100588148C/zh not_active Expired - Fee Related

-

2009

- 2009-06-10 US US12/481,798 patent/US7856072B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7856072B2 (en) | 2010-12-21 |

| CN1728630A (zh) | 2006-02-01 |

| CN100588148C (zh) | 2010-02-03 |

| US7558336B2 (en) | 2009-07-07 |

| US20060018407A1 (en) | 2006-01-26 |

| JP2006041818A (ja) | 2006-02-09 |

| US20090245424A1 (en) | 2009-10-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4419067B2 (ja) | ディジタルインターフェースを有する半導体装置、メモリ素子及びメモリモジュール | |

| US7249290B2 (en) | Deskew circuit and disk array control device using the deskew circuit, and deskew method | |

| JP4878215B2 (ja) | インタフェース回路及びメモリ制御装置 | |

| US6647027B1 (en) | Method and apparatus for multi-channel data delay equalization | |

| US8861666B2 (en) | Communication protocol method and apparatus for a single wire device | |

| JPH0150150B2 (ja) | ||

| JP5005928B2 (ja) | インタフェース回路及びそのインタフェース回路を備えた記憶制御装置 | |

| JP3415891B2 (ja) | パケットデータ再生システム | |

| JP4945616B2 (ja) | ディジタルインターフェースを有する半導体装置 | |

| JP2532740B2 (ja) | アドレス遷移検出回路 | |

| TWI635706B (zh) | 決定出取樣時脈訊號的取樣相位的方法及相關的電子裝置 | |

| JP5772398B2 (ja) | 電子部品及び反射波キャンセル方法 | |

| US6137306A (en) | Input buffer having adjustment function for suppressing skew | |

| US6205192B1 (en) | Clock input control circuit | |

| JP2000049595A (ja) | Dll回路 | |

| JP4248074B2 (ja) | 動作タイミング制御機能を有するシステム | |

| JP2687788B2 (ja) | クロックスキュー自動調整回路 | |

| KR100545075B1 (ko) | 스큐 억제 기능을 갖는 출력 버퍼회로 | |

| KR101100756B1 (ko) | 스큐 일치 출력 회로 | |

| US11901038B2 (en) | Memory system | |

| JP3408486B2 (ja) | 装置間の同期回路 | |

| TWI781017B (zh) | 測試系統以及其測試電路 | |

| JP3188679B2 (ja) | スキュー抑制機能を有する出力バッファ回路 | |

| JP4313469B2 (ja) | スキュー抑制のための調整機能を有する入力バッファ | |

| US5299200A (en) | Adaptive interface that automatically adjusts for timing skews caused by signal delays |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20070411 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070426 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070426 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20090423 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20090423 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090715 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090722 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090918 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091028 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091118 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121211 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees | ||

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |