JP3975014B2 - 液晶表示装置の製造方法 - Google Patents

液晶表示装置の製造方法 Download PDFInfo

- Publication number

- JP3975014B2 JP3975014B2 JP33171198A JP33171198A JP3975014B2 JP 3975014 B2 JP3975014 B2 JP 3975014B2 JP 33171198 A JP33171198 A JP 33171198A JP 33171198 A JP33171198 A JP 33171198A JP 3975014 B2 JP3975014 B2 JP 3975014B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode wiring

- electrode

- insulating film

- wiring terminal

- gas

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 49

- 238000004519 manufacturing process Methods 0.000 title claims description 39

- 239000011229 interlayer Substances 0.000 claims description 161

- 238000005530 etching Methods 0.000 claims description 147

- 238000000034 method Methods 0.000 claims description 128

- 239000000758 substrate Substances 0.000 claims description 115

- 238000002161 passivation Methods 0.000 claims description 79

- 239000010410 layer Substances 0.000 claims description 44

- 238000004380 ashing Methods 0.000 claims description 38

- 238000001312 dry etching Methods 0.000 claims description 36

- 239000004065 semiconductor Substances 0.000 claims description 28

- 239000011347 resin Substances 0.000 claims description 22

- 229920005989 resin Polymers 0.000 claims description 22

- 206010034972 Photosensitivity reaction Diseases 0.000 claims description 15

- 230000036211 photosensitivity Effects 0.000 claims description 15

- 239000000463 material Substances 0.000 claims description 13

- 238000000059 patterning Methods 0.000 claims description 13

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 claims description 12

- 229910052731 fluorine Inorganic materials 0.000 claims description 12

- 239000011737 fluorine Substances 0.000 claims description 12

- 229920002120 photoresistant polymer Polymers 0.000 claims description 8

- 230000003247 decreasing effect Effects 0.000 claims description 2

- 239000010408 film Substances 0.000 description 345

- 229910052581 Si3N4 Inorganic materials 0.000 description 14

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 14

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 10

- 230000000694 effects Effects 0.000 description 8

- 238000000206 photolithography Methods 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 238000004061 bleaching Methods 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- 238000001039 wet etching Methods 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- ing And Chemical Polishing (AREA)

Description

【発明の属する技術分野】

この発明は、スイッチング素子として薄膜トランジスタ(以下、TFTと称する)を搭載したアクティブマトリクス型の液晶表示装置の製造方法に関するものである。

【0002】

【従来の技術】

液晶表示装置は、その駆動方法として、高表示品質の観点からTFTをスイッチング素子として用いたアクティブマトリクス型のTFTアレイが主として用いられている。

また、液晶表示装置の低消費電力化のためには、液晶表示パネルの画素部の有効表示面積を大きくすること、すなわち画素の開口率を向上させることが有効であり、従来、高開口率の液晶表示パネルを得るために有効なTFTアレイとして、走査電極、信号電極および半導体層からなるTFTを形成した後に、これらを覆うように透明樹脂からなる層間絶縁膜を設け、最上層に画素電極を形成する構造が、例えば特許第2521752号公報、特許第2598420号公報および特開平4−163528号公報等に開示されている。

【0003】

画素電極が最上層に形成された構造を有する高開口率TFTアレイの製造方法としては、まずガラス基板等の透明絶縁性基板上にゲート電極配線およびゲート電極、ゲート絶縁膜、半導体層、ソース電極配線およびソース・ドレイン電極を順次形成してTFTを形成する。次にTFTを保護するために窒化シリコン膜からなるパッシベーション膜を成膜する。

次に透明樹脂からなる層間絶縁膜を形成し、パッシベーション膜および層間絶縁膜にコンタクトホールを形成する。最後に層間絶縁膜上に画素電極を形成し、TFTアレイを形成する。なお、画素電極はパッシベーション膜および層間絶縁膜に形成されたコンタクトホールを介してドレイン電極と電気的に接続される。また、上記のTFTアレイが形成されたTFTアレイ基板における表示領域の外側には、各電極配線を外部基板と電気的に接続するための端子が形成されている。

このような構造を有するTFTアレイでは、ゲート電極配線やソース電極配線上に画素電極をオーバーラップさせることが可能であり、画素の開口率を向上させることができる。

【0004】

しかし、TFTアレイ基板の表示領域の外側の端子が形成された実装領域には層間絶縁膜が形成されていないため、次に示すような問題が生じている。

層間絶縁膜上への画素電極の形成工程において、層間絶縁膜上に画素電極を構成するITO膜を成膜後、エッチング処理時に、層間絶縁膜上と層間絶縁膜が除去された実装領域となる透明絶縁性基板上とでは、ITO膜のエッチング速度が大きく異なり、層間絶縁膜上のITO膜の方が透明絶縁性基板上のITO膜より約5倍以上エッチング速度が速いため、層間絶縁膜上のITO膜と透明絶縁性基板上のITO膜を一括でエッチングすることができない。すなわち、画素電極形成時に、層間絶縁膜上のITO膜のエッチングにエッチング時間を合わせると、透明絶縁性基板上のITO膜は完全にエッチングされず、残存したITO膜により端子間に短絡を生じさせる。

【0005】

従来、この端子間の短絡を防止するために、まず、表示領域となる層間絶縁膜上のITO膜のエッチングに合わせたエッチング時間で一回目のエッチング処理を行い、次に、層間絶縁膜上のITOパターンを写真製版工程により形成したレジストで保護した後、実装領域となる透明絶縁性基板上のITO膜のエッチングに合わせたエッチング時間で二回目のエッチング処理を行い、画素電極を形成していた。

また、特開平9−90397号公報では、実装領域の端子間に層間絶縁膜を残存させることにより、端子間の短絡を防止できると共に一回のエッチング処理によりITO膜をエッチングする方法が開示されている。

【0006】

【発明が解決しようとする課題】

従来の高開口率TFTアレイを実現するための液晶表示装置は以上のように構成されており、TFTアレイ基板の表示領域の外側に設けられた外部基板と各電極配線との電気的接続のための実装領域には層間絶縁膜が形成されていないため、層間絶縁膜上の画素電極形成工程においては、二回の写真製版工程および二回のエッチング処理工程が必要であり、製造工程が煩雑となり、スループットの低下およびコストアップを生じさせるなどの問題があった。

また、端子間に層間絶縁膜を残存させる方法では、端子と外部基板との接続時に、層間絶縁膜による凹凸が接続抵抗を増加させるという問題があった。

【0007】

一般に、上記の構造を有するTFTアレイにおける画素電極とTFTのドレイン電極との電気的接続は、層間絶縁膜に形成されたコンタクトホールを介してなされているが、画素電極とドレイン電極との接続抵抗低減のために、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスを用いたドライエッチング法によるコンタクトホール形成後、O2 ガスによりアッシング処理を行い、コンタクトホール内の残さ物を除去している。

しかし、このO2 ガスによるアッシング処理により、層間絶縁膜の表面もエッチングされて、層間絶縁膜の表面に凹凸が形成される。この層間絶縁膜の表面状態が、層間絶縁膜上に成膜されるITO膜のエッチング性に影響を及ぼしているという知見が得られた。

【0008】

例えば、CF4 +O2 、またはSF6 +O2 、またはフッ素系ガス+O2 ガスを用いたエッチング処理後では、層間絶縁膜の表面は平滑であり、この状態の層間絶縁膜上にITO膜を成膜した場合、層間絶縁膜上のITO膜と透明絶縁性基板上のITO膜のエッチング速度はほぼ同じとなり、一回のエッチング処理によりITO膜をパターニングすることができる。実際に、透明絶縁性基板上のITO膜の最適エッチング時間でエッチング処理を行った場合、層間絶縁膜上のITOパターンのサイドエッチ量は片側1μm以下であり、良好なITOパターンが得られる。

しかし、CF4 +O2 、またはSF6 +O2 、またはフッ素系ガス+O2 ガスを用いたエッチング処理後にO2 ガスによりアッシング処理を行うと、層間絶縁膜表面に凹凸が生じ、この状態の層間絶縁膜上にITO膜を成膜した場合、層間絶縁膜上のITO膜の方が透明絶縁性基板上のITO膜より約5倍以上エッチング速度が速くなり、一回のエッチング処理によりITO膜をパターニングすることができない。実際に、透明絶縁性基板上のITO膜の最適エッチング時間でエッチング処理を行った場合、層間絶縁膜上のITOパターンのサイドエッチ量は片側3μm以上となり、ITOパターンは極端なテーパ形状となる。

【0009】

以上のように、画素電極とドレイン電極との接続抵抗低減のために、O2 ガスによるアッシング処理を行った場合、層間絶縁膜上のITO膜と透明絶縁性基板上のITO膜を一回のエッチング処理工程でパターニングすることができず、また、O2 ガスによるアッシング処理を行わない場合、層間絶縁膜上のITO膜と透明絶縁性基板上のITO膜を一回のエッチング処理工程でパターニングすることができるが、画素電極とドレイン電極の接続抵抗が上昇するという問題があった。

【0010】

この発明は、上記のような問題点を解消するためになされたもので、画素電極とドレイン電極の接続抵抗を低くかつ安定化できると共に、画素電極形成時に、実装領域の端子間に短絡を生じさせることなく、ITO膜を一回のエッチング処理工程でパターニングすることのできる液晶表示装置の製造方法を提供することを目的とする。

【0011】

【課題を解決するための手段】

この発明に係わる液晶表示装置の製造方法は、少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、上記層間絶縁膜をマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜および絶縁膜をドライエッチング法によりエッチングする工程と、上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記ドライエッチング法によるエッチングは、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なった後、O 2 ガスによるアッシング処理を施し、その後更にCF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なうものである。

【0012】

また、少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、上記走査電極配線端子および第一の電極配線端子が形成される実装領域の上記絶縁膜を除去する工程と、上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、上記層間絶縁膜をマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜をドライエッチング法によりエッチングする工程と、上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記ドライエッチング法によるエッチングは、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なった後、O 2 ガスによるアッシング処理を施し、その後更にCF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なうものである。

【0015】

また、アッシング処理後に行なわれるCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理は、アッシング処理前に行なわれるCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理より短時間で行なう、あるいはO2ガスの流量比率を高くする、あるいはパワーを小さくする、あるいは上記処理条件の少なくともいずれか二条件を組み合わせて行なうものである。

更にまた、少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、上記絶縁膜を除去する工程と、上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、フォトレジストを塗布し、上記層間絶縁膜と同一形状にパターニングしてレジストを形成する工程と、上記レジストをマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜および絶縁膜をドライエッチング法によりエッチングした後、上記レジストを除去する工程と、上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記エッチング処理は、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる一回目のエッチング処理を行なった後、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる二回目のエッチング処理をO 2 ガスの流量比率を一回目より高くして行なうものである。

【0016】

また、少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、上記絶縁膜を除去する工程と、上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、上記パッシベーション膜上に感光性を有しない透明樹脂を塗布し、層間絶縁膜を形成する工程と、レジストを形成し、上記層間絶縁膜、パッシベーション膜および絶縁膜をドライエッチング法によりエッチングして、上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を形成した後、レジストを除去する工程と、上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記エッチング処理は、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる一回目のエッチング処理を行なった後、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる二回目のエッチング処理をO 2 ガスの流量比率を一回目より高くして行なうものである。

【0017】

【発明の実施の形態】

実施の形態1.

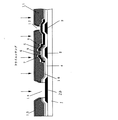

以下、この発明の一実施の形態である液晶表示装置の製造方法を図について説明する。図1は本発明の実施の形態1によるスイッチング素子としてTFTを搭載した液晶表示装置のTFTアレイ基板を示す断面図、図2は図1に示すTFTアレイ基板の周辺部の概略平面図、図3は図1のTFTアレイ基板の製造工程途中の状態を示す断面図である。

図において、1はガラス基板等の透明絶縁性基板、2は透明絶縁性基板1上に形成された走査電極(本実施の形態ではゲート電極)、2aは走査電極2を有する走査電極配線(本実施の形態ではゲート電極配線)、2bは走査電極配線2aから延長して形成された走査電極配線端子(本実施の形態ではゲート端子)、3は透明絶縁性基板1上に形成された共通電極、4はゲート電極2、ゲート電極配線2aおよび共通配線3上に形成されたゲート絶縁膜、5はゲート絶縁膜4を介してゲート電極2上に形成された半導体層、6は半導体層5上に形成されたコンタクト層、7、8はコンタクト層6上に形成された第一の電極と第二の電極(本実施の形態ではソース電極とドレイン電極)、7aは第一の電極7を有する第一の電極配線(本実施の形態ではソース電極配線)、7bは第一の電極配線7aから延長して形成された第一の電極配線端子(本実施の形態ではソース端子)、9はチャネル部、10はパッシベーション膜、11はパッシベーション膜10上に形成された層間絶縁膜、12はパッシベーション膜10および層間絶縁膜11に形成されたコンタクトホール、13は層間絶縁膜11上に形成された画素電極で、パッシベーション膜10および層間絶縁膜11に形成されたコンタクトホール12を介してドレイン電極8と電気的に接続される。13aは画素電極13と同時に形成された端子2b、7b上のITO膜、14は端子2b、7bが配設された実装領域で、実装領域14ではゲート絶縁膜4、パッシベーション膜10および層間絶縁膜11は除去され、端子2b、7b間には透明絶縁性基板1が露出している。

【0018】

次に本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。まず、透明絶縁性基板1の表面にスパッタ法等を用いてCrを成膜し、写真製版法によるレジストの形成およびウェットエッチング法によりパターニングを行い、ゲート電極2、ゲート電極配線2a、ゲート端子2bおよび共通配線3を形成する。

次に、プラズマCVD法を用いてゲート絶縁膜4を構成する窒化シリコン膜、アモルファスシリコン膜、不純物がドープされた低抵抗アモルファスシリコン膜を順次成膜した後、写真製版法によるレジストの形成およびドライエッチング法によりパターニングを行い、半導体層5およびコンタクト層6を形成する。

次に、スパッタ法を用いてCrを成膜し、写真製版法によるレジストの形成およびウェットエッチング法によりパターニングを行い、ソース電極7、ソース電極配線7a、ソース端子7bおよびドレイン電極8を形成後、ソース電極7とドレイン電極8に覆われていない部分の低抵抗アモルファスシリコン膜(コンタクト層6)をドライエッチング法を用いてエッチングし、チャネル部9を形成してTFTを形成する。

【0019】

次に、TFTを保護するために、パッシベーション膜10となる窒化シリコンをプラズマCVD法を用いて成膜する。

次に、TFTおよび電極配線による段差を吸収して表面が平坦化されるように、感光性を有するアクリル系透明樹脂をスピンコート法等を用いて塗布し、露光、現像処理を施してコンタクトホールを形成後、ブリーチング露光、焼成を行い層間絶縁膜11を形成する。このとき、図2に示すように、ゲート電極配線2aまたはソース電極配線7aを外部基板(図示せず)と電気的に接続するためのゲート端子2bおよびソース端子7bが配設された実装領域14においては、各端子2b、7b上および各端子2b、7b間に層間絶縁膜11が存在しないよう除去されている。各端子2b、7b間の層間絶縁膜11を除去するのは、層間絶縁膜11の凹凸により各端子2b、7bと外部基板との接続抵抗が増加するのを防止するためである。

次に、ドライエッチング法を用い、層間絶縁膜11をマスクとして、層間絶縁膜11に形成されたコンタクトホールにより露出したパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14におけるパッシベーション膜10とゲート絶縁膜4のエッチングを行う。このとき、実装領域14では、各端子2b、7b間に透明絶縁性基板1が露出する。

【0020】

図3は、層間絶縁膜11をマスクとしたパッシベーション膜10およびゲート絶縁膜4のドライエッチング法によるエッチング工程を示している。パッシベーション膜10およびゲート絶縁膜4のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10およびゲート絶縁膜4を構成する窒化シリコンをエッチングした後、次工程で形成される画素電極13とドレイン電極8との接続抵抗低減のため、O2 ガスによるアッシング処理を行い、コンタクトホール12底部のドレイン電極8上の残さ物を除去する。このとき、層間絶縁膜11の表面にも、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理およびO2 ガスによるアッシング処理が施されるため、層間絶縁膜11の表面に凹凸が形成される。

次に、O2 ガスのアッシング処理により形成された層間絶縁膜11表面の凹凸低減を目的として、再度CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行う。

【0021】

なお、二回目のCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理は、コンタクトホール12内での層間絶縁膜11への残さ物の再付着を防止するために、一回目のエッチング時間より短時間で二回目のエッチング処理を行なう。または、CF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスのO2ガスの流量比率を高くして二回目のエッチング処理を行なう。または、一回目のエッチング処理よりパワーを小さくして二回目のエッチング処理を行なう。または、前記の短時間処理、O2の流量比率アップおよびパワーダウンの少なくともいずれか二条件を組み合わせてエッチング処理を行なう。

【0022】

次に、スパッタ法を用いてITOを成膜し、写真製版法によるレジストの形成およびエッチングにより層間絶縁膜11上に画素電極13および各端子2b、7b上にITO膜13aを形成する。このとき、画素電極13はコンタクトホール12を介してドレイン電極8と電気的に接続される。

なお、ITO膜のエッチングは、前工程において、O2 ガスのアッシング処理後に再度CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を施して、層間絶縁膜11表面の凹凸を低減することにより、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング速度はほぼ同じとなり、一回のエッチング処理により画素電極13と実装領域14のITO膜13aを同時にパターニングできる。

【0023】

以上の工程により形成されたTFTアレイ基板と、他の透明絶縁性基板上に対向電極等が形成された対向基板の表面に配向膜を形成後対向させ、この間に液晶材料を注入することにより液晶表示素子を構成する。

【0024】

なお、画素電極13を構成するITO膜のエッチングにおいては、透明絶縁性基板1上のITO膜の最適エッチング時間でエッチング処理を行った場合、層間絶縁膜11上のITOパターン(画素電極13)のサイドエッチ量は片側1μm以下であり、良好な形状を有するパターンが得られた。

また、画素電極13とドレイン電極8との接続抵抗は35μm□で数百Ω以下であった。

【0025】

この発明によれば、層間絶縁膜11上に形成された画素電極13とドレイン電極8を接続するためのコンタクトホール12の形成工程において、層間絶縁膜11をマスクとしての、パッシベーション膜10およびゲート絶縁膜4のCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理、およびコンタクトホール12内の残さ物除去を目的としたO2 ガスによるアッシング処理後に、再度CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を施すことにより、O2 ガスのアッシング処理により形成された層間絶縁膜11表面の凹凸を低減でき、コンタクトホール12を介して画素電極13とドレイン電極8との接続抵抗を低減できると共に、画素電極13形成時に、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜を一回のエッチング処理によりパターニングできる。

【0026】

実施の形態2.

実施の形態1では、層間絶縁膜11をマスクとしたパッシベーション膜10およびゲート絶縁膜4のエッチング処理を、まずCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるパッシベーション膜10およびゲート絶縁膜4のエッチング処理、次にコンタクトホール12底部の残さ物除去を目的としたO2 ガスによるアッシング処理、次に層間絶縁膜11表面の凹凸低減を目的とした二回目のCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理により行ったが、まずCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10およびゲート絶縁膜4のエッチング処理を行い、次にO2 ガスの流量比率を高くして二回目のCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことにより、コンタクトホール12底部の残さ物を除去してコンタクトホール12を介しての画素電極13とドレイン電極8との接続抵抗を低減できると共に、O2 ガスによるアッシング処理に比べて層間絶縁膜11表面の凹凸を低減でき、画素電極13形成時に、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング性を改善できる。

【0027】

実施の形態3.

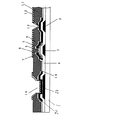

図4はこの発明の実施の形態3による液晶表示装置のTFTアレイ基板の製造工程途中の状態を示す断面図である。図において、15は層間絶縁膜11上に形成されたレジストである。なお、図3と同一部分については同符号を付し説明を省略する。

【0028】

次に、本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。

実施の形態1と同様の方法により、透明絶縁性基板1上にゲート電極2、ゲート電極配線(図示せず)、ゲート端子2b、共通電極3、ゲート絶縁膜4、半導体層5、コンタクト層6、ソース電極7、ドレイン電極8、ソース電極配線(図示せず)、ソース端子(図示せず)、チャネル部9およびパッシベーション膜10を順次形成する。

次に、感光性を有するアクリル系透明樹脂をスピンコート法等を用いて塗布し、露光、現像処理を施してコンタクトホールを形成後、ブリーチング露光、焼成を行い層間絶縁膜11を形成する。このとき、図2に示すように、ゲート電極配線2aまたはソース電極配線7aを外部基板(図示せず)と電気的に接続するためのゲート端子2bおよびソース端子7bが配設された実装領域14においては、各端子2b、7b上および各端子2b、7b間に層間絶縁膜11が存在しないよう除去されている。

【0029】

次に、層間絶縁膜11上にフォトレジストを塗布し、前記のアクリル系透明樹脂を露光する際に用いたマスクを用いてフォトレジストを露光後、現像処理を施して、層間絶縁膜11と同じパターンのレジスト15を形成する。

次に、レジスト15をマスクとして、ドライエッチング法によりパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14におけるパッシベーション膜10とゲート絶縁膜4のエッチングを行う。

パッシベーション膜10およびゲート絶縁膜4のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10およびゲート絶縁膜4を構成する窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物を除去し、次工程で形成される画素電極とドレイン電極8との接続抵抗低減を目的として、O2 ガスによるアッシング処理を行う。その後、レジスト15を除去する。なお、O2 ガスによるアッシング処理時には、層間絶縁膜11の表面はレジスト15で保護されているため、層間絶縁膜11の表面に凹凸は形成されない。

【0030】

その後、実施の形態1と同様の方法により画素電極および各端子2b、7b上にITO膜を形成し、TFTアレイ基板を形成する。

なお、パッシベーション膜10およびゲート絶縁膜4のドライエッチング処理を、まず、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物除去を目的として、O2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことによっても、同様の効果が得られる。

【0031】

本実施の形態によれば、コンタクトホール12底部の残さ物除去を目的としたO2 ガスのアッシング処理、あるいはO2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を、層間絶縁膜11の表面をレジスト15で保護した状態で行うことにより、層間絶縁膜11の表面には凹凸は形成されず、コンタクトホール12を介しての画素電極とドレイン電極8との接続抵抗を低減できると共に、画素電極形成時に、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング速度はほぼ同じとなり、一回のエッチング処理により画素電極と実装領域14のITO膜をパターニングできる。

【0032】

実施の形態4.

図5はこの発明の実施の形態4による液晶表示装置のTFTアレイ基板の製造工程途中の状態を示す断面図である。なお、図中の符号は図4と同じであるので説明を省略する。

【0033】

次に、本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。

実施の形態1と同様の方法により、透明絶縁性基板1上にゲート電極2、ゲート電極配線(図示せず)、ゲート端子2b、共通電極3、ゲート絶縁膜4、半導体層5、コンタクト層6、ソース電極7、ドレイン電極8、ソース電極配線(図示せず)、ソース端子(図示せず)、チャネル部9およびパッシベーション膜10を順次形成する。

次に、感光性を有しないアクリル系透明樹脂をスピンコート法等を用いて塗布し、焼成を行い層間絶縁膜11を形成する。

次に、層間絶縁膜11上にフォトレジストを塗布し、露光、現像処理を施して、所定の位置に開口パターンを有するレジスト15を形成する。

【0034】

次に、レジスト15をマスクとして、ドライエッチング法により層間絶縁膜11とパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14における層間絶縁膜11、パッシベーション膜10およびゲート絶縁膜4のエッチングを行う。

層間絶縁膜11、パッシベーション膜10およびゲート絶縁膜4のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより層間絶縁膜11、およびパッシベーション膜10とゲート絶縁膜4を構成する窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物を除去し、次工程で形成される画素電極とドレイン電極8との接続抵抗低減を目的として、O2 ガスによるアッシング処理を行う。その後、レジスト15を除去する。 なお、O2 ガスによるアッシング処理時には、層間絶縁膜11の表面はレジスト15で保護されているため、層間絶縁膜11の表面に凹凸は形成されない。

その後、実施の形態1と同様の方法により画素電極およびゲート端子2b、ソース端子上にITO膜を形成し、TFTアレイ基板を形成する。

【0035】

なお、層間絶縁膜11、パッシベーション膜10およびゲート絶縁膜4のドライエッチング処理を、まず、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより層間絶縁膜11および窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物除去を目的として、O2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことによっても、同様の効果が得られる。

【0036】

本実施の形態によれば、層間絶縁膜11を安価な感光性を有しないアクリル系透明樹脂を用いて構成し、層間絶縁膜11のパターニングは、層間絶縁膜11表面の保護の目的で形成されるレジスト15をマスクとして、パッシベーション膜10のエッチングと一括して行うことができるため、材料コストを低減できると共に、製造工程数を増やすことなく実施の形態3と同様の効果が得られる。

【0037】

実施の形態5.

実施の形態1、2、3および4では、実装領域14におけるゲート端子2b上のゲート絶縁膜4は、層間絶縁膜11を形成後、層間絶縁膜11もしくはレジスト15をマスクとしてエッチングしたが、半導体層5およびコンタクト層6の形成後にゲート端子2b上のゲート絶縁膜4をエッチング除去する構造および製造工程による液晶表示装置に適用することによっても同様の効果が得られる。

【0038】

図6はこの発明の実施の形態5による液晶表示装置のTFTアレイ基板を示す断面図、図7は図6のTFTアレイ基板の製造工程途中の状態を示す断面図である。なお、図中の符号は図3と同じであるので説明を省略する。

次に、本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。

実施の形態1と同様の方法により、透明絶縁性基板1上にゲート電極2、ゲート電極配線(図示せず)、ゲート端子2b、共通電極3、ゲート絶縁膜4、半導体層5およびコンタクト層6を順次形成する。

次に、写真製版法により所定の位置に開口パターンを有するレジストを形成後、ドライエッチング法により実装領域14のゲート絶縁膜4をエッチングする。

次に、スパッタ法を用いてCrを成膜し、写真製版法によるレジストの形成およびウェットエッチング法によりパターニングを行い、ソース電極7、ソース電極配線(図示せず)、ソース端子(図示せず)、ドレイン電極8およびゲート端子2b上にCr膜7cを形成後、ソース電極7とドレイン電極8に覆われていない部分の低抵抗アモルファスシリコン膜(コンタクト層6)をドライエッチング法を用いてエッチングし、チャネル部9を形成してTFTを形成する。

【0039】

次に、TFTを保護するために、パッシベーション膜10となる窒化シリコンをプラズマCVD法を用いて成膜する。

次に、TFTおよび電極配線による段差を吸収して表面が平坦化されるように、感光性を有するアクリル系透明樹脂をスピンコート法等を用いて塗布し、露光、現像処理を施してコンタクトホールを形成後、ブリーチング露光、焼成を行い層間絶縁膜11を形成する。このとき、図2に示すように、ゲート電極配線2aまたはソース電極配線7aを外部基板(図示せず)と電気的に接続するためのゲート端子2bおよびソース端子7bが配設された実装領域14においては、各端子2b。7b上および各端子2b、7b間に層間絶縁膜11が存在しないよう除去されている。

次に、ドライエッチング法を用い、層間絶縁膜11をマスクとして、層間絶縁膜11に形成されたコンタクトホールにより露出したパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14におけるパッシベーション膜10のエッチングを行う。このとき、実装領域14では、各端子2b、7b間に透明絶縁性基板1が露出する。

【0040】

図7は、層間絶縁膜11をマスクとしたパッシベーション膜10のドライエッチング法によるエッチング工程を示している。パッシベーション膜10のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10を構成する窒化シリコンをエッチングした後、次工程で形成される画素電極13とドレイン電極8との接続抵抗低減のため、O2 ガスによるアッシング処理を行い、コンタクトホール12底部のドレイン電極8上の残さ物を除去する。このとき、層間絶縁膜11の表面にも、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理およびO2 ガスによるアッシング処理が施されるため、層間絶縁膜11の表面に凹凸が形成される。

次に、O2 ガスのアッシング処理により形成された層間絶縁膜11表面の凹凸低減を目的として、再度CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行う。

【0041】

なお、二回目のCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理は、コンタクトホール12内での層間絶縁膜11への残さ物の再付着を防止するために、一回目のエッチング時間より短時間で二回目のエッチング処理を行なう。または、CF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスのO2ガスの流量比率を高くして二回目のエッチング処理を行なう。または、一回目のエッチング処理よりパワーを小さくして二回目のエッチング処理を行なう。または、前記の短時間処理、O2の流量比率アップおよびパワーダウンの少なくともいずれか二条件を組み合わせてエッチング処理を行なう。

【0042】

次に、スパッタ法を用いてITOを成膜し、写真製版法によるレジストの形成およびエッチングにより層間絶縁膜11上に画素電極13および各端子2b、7b上にITO膜13aを形成する。このとき、画素電極13はコンタクトホール12を介してドレイン電極8と電気的に接続される。

なお、ITO膜のエッチングは、前工程において、O2 ガスのアッシング処理後に再度CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を施して、層間絶縁膜11表面の凹凸を低減することにより、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング速度はほぼ同じとなり、一回のエッチング処理により画素電極13と実装領域14のITO膜13aを同時にパターニングできる。

【0043】

以上の工程により形成されたTFTアレイ基板と、他の透明絶縁性基板上に対向電極等が形成された対向基板の表面に配向膜を形成後対向させ、この間に液晶材料を注入することにより液晶表示素子を構成する。

【0044】

なお、画素電極13を構成するITO膜のエッチングにおいては、透明絶縁性基板1上のITO膜の最適エッチング時間でエッチング処理を行った場合、層間絶縁膜11上のITOパターン(画素電極13)のサイドエッチ量は片側1μm以下であり、良好な形状を有するパターンが得られた。

また、画素電極13とドレイン電極8との接続抵抗は35μm□で数百Ω以下であった。

【0045】

本実施の形態によれば、*(質問参照)

【0046】

実施の形態6.

実施の形態5では、層間絶縁膜11をマスクとしたパッシベーション膜10のエッチング処理を、まずCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるパッシベーション膜10およびゲート絶縁膜4のエッチング処理、次にコンタクトホール12底部の残さ物除去を目的としたO2 ガスによるアッシング処理、次に層間絶縁膜11表面の凹凸低減を目的とした二回目のCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理により行ったが、まずCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10のエッチング処理を行い、次にO2 ガスの流量比率を高くして二回目のCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことにより、コンタクトホール12底部の残さ物を除去してコンタクトホール12を介しての画素電極13とドレイン電極8との接続抵抗を低減できると共に、O2 ガスによるアッシング処理に比べて層間絶縁膜11表面の凹凸を低減でき、画素電極13形成時に、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング性を改善できる。

【0047】

実施の形態7.

図8はこの発明の実施の形態7による液晶表示装置のTFTアレイ基板の製造工程途中の状態を示す断面図である。図中の符号は図4と同じであるので説明を省略する。

【0048】

次に、本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。

実施の形態5と同様の方法により、透明絶縁性基板1上にゲート電極2、ゲート電極配線(図示せず)、ゲート端子2b、共通電極3、ゲート絶縁膜4、半導体層5、コンタクト層6、ソース電極7、ドレイン電極8、ソース電極配線(図示せず)、ソース端子(図示せず)、チャネル部9およびパッシベーション膜10を順次形成する。

次に、感光性を有するアクリル系透明樹脂をスピンコート法等を用いて塗布し、露光、現像処理を施してコンタクトホールを形成後、ブリーチング露光、焼成を行い層間絶縁膜11を形成する。このとき、図2に示すように、ゲート電極配線2aまたはソース電極配線7aを外部基板(図示せず)と電気的に接続するためのゲート端子2bおよびソース端子7bが配設された実装領域14においては、各端子2b、7b上および各端子2b、7b間に層間絶縁膜11が存在しないよう除去されている。

【0049】

次に、層間絶縁膜11上にフォトレジストを塗布し、前記のアクリル系透明樹脂を露光する際に用いたマスクを用いてフォトレジストを露光後、現像処理を施して、層間絶縁膜11と同じパターンのレジスト15を形成する。

次に、レジスト15をマスクとして、ドライエッチング法によりパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14におけるパッシベーション膜10のエッチングを行う。

パッシベーション膜10のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによりパッシベーション膜10を構成する窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物を除去し、次工程で形成される画素電極とドレイン電極8との接続抵抗低減を目的として、O2 ガスによるアッシング処理を行う。その後、レジスト15を除去する。なお、O2 ガスによるアッシング処理時には、層間絶縁膜11の表面はレジスト15で保護されているため、層間絶縁膜11の表面に凹凸は形成されない。

【0050】

その後、実施の形態5と同様の方法により画素電極および各端子2b、7b上にITO膜を形成し、TFTアレイ基板を形成する。

なお、パッシベーション膜10およびゲート絶縁膜4のドライエッチング処理を、まず、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物除去を目的として、O2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことによっても、同様の効果が得られる。

【0051】

本実施の形態によれば、コンタクトホール12底部の残さ物除去を目的としたO2 ガスのアッシング処理、あるいはO2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を、層間絶縁膜11の表面をレジスト15で保護した状態で行うことにより、層間絶縁膜11の表面には凹凸は形成されず、コンタクトホール12を介しての画素電極とドレイン電極8との接続抵抗を低減できると共に、画素電極形成時に、層間絶縁膜11上のITO膜と、実装領域14における各端子2b、7b間の透明絶縁性基板1上のITO膜のエッチング速度はほぼ同じとなり、一回のエッチング処理により画素電極と実装領域のITO膜13aをパターニングできる。

【0052】

実施の形態8.

図9はこの発明の実施の形態8による液晶表示装置のTFTアレイ基板の製造工程途中の状態を示す断面図である。なお、図中の符号は図4と同じであるので説明を省略する。

【0053】

次に、本実施の形態による液晶表示装置のTFTアレイ基板の製造工程について説明する。

実施の形態5と同様の方法により、透明絶縁性基板1上にゲート電極2、ゲート電極配線(図示せず)、ゲート端子2b、共通電極3、ゲート絶縁膜4、半導体層5、コンタクト層6、ソース電極7、ドレイン電極8、ソース電極配線(図示せず)、ソース端子(図示せず)、チャネル部9およびパッシベーション膜10を順次形成する。

次に、感光性を有しないアクリル系透明樹脂をスピンコート法等を用いて塗布し、焼成を行い層間絶縁膜11を形成する。

次に、層間絶縁膜11上にフォトレジストを塗布し、露光、現像処理を施して、所定の位置に開口パターンを有するレジスト15を形成する。

【0054】

次に、レジスト15をマスクとして、ドライエッチング法により層間絶縁膜11とパッシベーション膜10をエッチングしてコンタクトホール12の形成、および実装領域14における層間絶縁膜11およびパッシベーション膜10のエッチングを行う。

層間絶縁膜11およびパッシベーション膜10のドライエッチング条件は、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより層間絶縁膜11、およびパッシベーション膜10を構成する窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物を除去し、次工程で形成される画素電極とドレイン電極8との接続抵抗低減を目的として、O2 ガスによるアッシング処理を行う。その後、レジスト15を除去する。なお、O2 ガスによるアッシング処理時には、層間絶縁膜11の表面はレジスト15で保護されているため、層間絶縁膜11の表面に凹凸は形成されない。

その後、実施の形態5と同様の方法により画素電極およびゲート端子2b、ソース端子上にITO膜を形成し、TFTアレイ基板を形成する。

【0055】

なお、層間絶縁膜11およびパッシベーション膜10のドライエッチング処理を、まず、CF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスにより層間絶縁膜11および窒化シリコンをエッチングした後、コンタクトホール12底部の残さ物除去を目的として、O2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うことによっても、同様の効果が得られる。

【0056】

本実施の形態によれば、層間絶縁膜11を安価な感光性を有しないアクリル系透明樹脂を用いて構成し、層間絶縁膜11のパターニングは、層間絶縁膜11表面の保護の目的で形成されるレジスト15をマスクとして、パッシベーション膜10のエッチングと一括して行うことができるため、材料コストを低減できると共に、製造工程数を増やすことなく実施の形態7と同様の効果が得られる。

【0057】

実施の形態9.

実施の形態1から実施の形態8では、実装領域14において、各端子2b、7b間に層間絶縁膜11が存在しないように層間絶縁膜11を除去したが、表示領域の外側の層間絶縁膜11をすべて除去する構造としてもよい。

【0058】

また、実施の形態1から実施の形態8では、パッシベーション膜10を有する構造としたが、パッシベーション膜10を有せず、TFT上に直接層間絶縁膜11が形成される構造としてもよく、パッシベーション膜を有しない場合は、実施の形態5から実施の形態7におけるTFTアレイ基板の製造方法においては、層間絶縁膜11あるいはレジスト15をマスクとしたパッシベーション膜10のエッチング工程が不要となるため、コンタクトホール12底部の残さ物除去を目的としたO2 ガスのアッシング処理、あるいはO2 ガスの流量比率を高くしたCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスによるエッチング処理を行うだけでよい。

【0059】

また、実施の形態1から実施の形態8では、層間絶縁膜11を構成する材料としては、アクリル系以外の透明樹脂を用いてもよい。

また、実施の形態1から実施の形態8では、コンタクトホール12形成工程において、ドライエッチング処理に使用するCF4 +O2 、またはSF6 +O2 、または他のフッ素系ガス+O2 ガスに、面内均一性改善を目的としてArあるいはHe等を添加して用いてもよい。

また、実施の形態1から実施の形態8では、半導体層5としてアモルファスシリコンを用いたが、多結晶シリコンを用い画素最上層構造のデバイスに適用してもよい。

【0060】

【発明の効果】

以上のように、この発明によれば、電極配線およびTFT上に透明樹脂からなる層間絶縁膜を形成してその表面を平坦化し、最上層に画素電極を形成した構造を有することにより開口率の向上を実現する液晶表示装置の製造方法において、層間絶縁膜上に形成された画素電極とドレイン電極を電気的に接続するコンタクトホール形成のためのドライエッチング条件を最適化して、コンタクトホール底部の残さ物除去を確実に行うと共に、コンタクトホール形成後画素電極を構成するITO膜の成膜時には、層間絶縁膜表面に凹凸がない状態とすることにより、画素電極とドレイン電極の接続抵抗を低減できると共に、画素電極形成時に、層間絶縁膜上のITO膜と実装領域の端子間に露出した透明絶縁性基板上のITO膜を、一回のエッチング処理工程で、端子間に短絡のないかつ良好な形状にパターニングすることができ、高性能かつ高開口率の液晶表示装置を低コストで製造することができる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1による液晶表示装置のTFTアレイ基板を示す断面図である。

【図2】 この発明の実施の形態1による液晶表示装置のTFTアレイ基板の周辺部の概略平面図である。

【図3】 この発明の実施の形態1による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【図4】 この発明の実施の形態3による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【図5】 この発明の実施の形態4による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【図6】 この発明の実施の形態5による液晶表示装置のTFTアレイ基板を示す断面図である。

【図7】 この発明の実施の形態5による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【図8】 この発明の実施の形態7による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【図9】 この発明の実施の形態8による液晶表示装置のTFTアレイ基板の製造工程を示す断面図である。

【符号の説明】

1 透明絶縁性基板、2 ゲート電極、2a ゲート電極配線、

2b ゲート端子、3 共通電極、4 ゲート絶縁膜、5 半導体層、

6 コンタクト層、7 ソース電極、7a ソース電極配線、

7b ソース端子、8 ドレイン電極、9 チャネル部、

10 パッシベーション膜、11 層間絶縁膜、12 コンタクトホール、

13 画素電極、13a ITO膜、14 実装領域、15 レジスト。

Claims (5)

- 少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、

上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、

上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、

上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、

上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、

上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、

上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、

上記層間絶縁膜をマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜および絶縁膜をドライエッチング法によりエッチングする工程と、

上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、

上記ドライエッチング法によるエッチングは、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なった後、O 2 ガスによるアッシング処理を施し、その後更にCF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なうことを特徴とする液晶表示装置の製造方法。 - 少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、

上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、

上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、

上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、

上記走査電極配線端子および第一の電極配線端子が形成される実装領域の上記絶縁膜を除去する工程と、

上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、

上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、

上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、

上記層間絶縁膜をマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜をドライエッチング法によりエッチングする工程と、

上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、

上記ドライエッチング法によるエッチングは、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なった後、O 2 ガスによるアッシング処理を施し、その後更にCF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによるエッチング処理を行なうことを特徴とする液晶表示装置の製造方法。 - アッシング処理後に行なわれるCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理は、アッシング処理前に行なわれるCF4+O2、またはSF6+O2、または他のフッ素系ガス+O2ガスによるエッチング処理より短時間で行う、あるいはO2ガスの流量比率を高くする、あるいはパワーを小さくする、あるいは上記処理条件の少なくともいずれか二条件を組み合わせて行なうことを特徴とする請求項1または請求項2記載の液晶表示装置の製造方法。

- 少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、

上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、

上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、

上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、

上記絶縁膜を除去する工程と、

上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、

上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、

上記パッシベーション膜上に感光性を有する透明樹脂を塗布し、露光、現像処理により上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を有する層間絶縁膜を形成する工程と、

フォトレジストを塗布し、上記層間絶縁膜と同一形状にパターニングしてレジストを形成する工程と、

上記レジストをマスクとして、上記コンタクトホールおよび開口部により露出した上記パッシベーション膜および絶縁膜をドライエッチング法によりエッチングした後、上記レジストを除去する工程と、

上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記エッチング処理は、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる一回目のエッチング処理を行なった後、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる二回目のエッチング処理をO 2 ガスの流量比率を一回目より高くして行なうことを特徴とする液晶表示装置の製造方法。 - 少なくともいずれか一方には電極が形成されている二枚の透明絶縁性基板を対向させて接着すると共に、上記二枚の透明絶縁性基板の間に液晶材料を挟持してなる液晶表示装置の製造方法において、

上記二枚の透明絶縁性基板の一方に走査電極、走査電極配線および走査電極配線端子を形成する工程と、

上記走査電極、走査電極配線および走査電極配線端子上に絶縁膜を形成する工程と、

上記走査電極上に上記絶縁膜を介して半導体層を形成する工程と、

上記絶縁膜を除去する工程と、

上記半導体層上に第一の電極、第一の電極配線、第一の電極配線端子および第二の電極を形成する工程と、

上記第一の電極、第一の電極配線、第一の電極配線端子および第二の電極上にパッシベーション膜を形成する工程と、

上記パッシベーション膜上に感光性を有しない透明樹脂を塗布し、層間絶縁膜を形成する工程と、

レジストを形成し、上記層間絶縁膜、パッシベーション膜および絶縁膜をドライエッチング法によりエッチングして、上記第二の電極上にコンタクトホール、および上記走査電極配線端子と第一の電極配線端子が形成された実装領域に開口部を形成した後、レジストを除去する工程と、

上記層間絶縁膜上と上記コンタクトホール内、および上記開口部により露出した上記透明絶縁性基板上と上記走査電極配線端子、第一の電極配線端子上に透明導電膜を成膜し、一回のエッチング処理によりパターニングして、上記第二の電極と上記コンタクトホールを介して電気的に接続された画素電極、および上記走査電極配線端子と第一の電極配線端子上に透明導電膜パターンを形成する工程を含み、上記エッチング処理は、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる一回目のエッチング処理を行なった後、CF 4 +O 2 、またはSF 6 +O 2 、または他のフッ素系ガス+O 2 ガスによる二回目のエッチング処理をO 2 ガスの流量比率を一回目より高くして行なうことを特徴とする液晶表示装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33171198A JP3975014B2 (ja) | 1998-11-20 | 1998-11-20 | 液晶表示装置の製造方法 |

| US09/437,090 US6353464B1 (en) | 1998-11-20 | 1999-11-09 | TFT array substrate, liquid crystal display using TFT array substrate, and manufacturing method thereof in which the interlayer insulating film covers the guard resistance and the short ring |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33171198A JP3975014B2 (ja) | 1998-11-20 | 1998-11-20 | 液晶表示装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000155335A JP2000155335A (ja) | 2000-06-06 |

| JP3975014B2 true JP3975014B2 (ja) | 2007-09-12 |

Family

ID=18246743

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP33171198A Expired - Fee Related JP3975014B2 (ja) | 1998-11-20 | 1998-11-20 | 液晶表示装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3975014B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100443840B1 (ko) * | 1998-09-01 | 2005-01-13 | 엘지.필립스 엘시디 주식회사 | 액정표시장치의제조방법 |

| JP2002258768A (ja) * | 2001-03-02 | 2002-09-11 | Seiko Epson Corp | 電気光学装置、その製造方法および電子機器 |

| KR20020080857A (ko) * | 2001-04-18 | 2002-10-26 | 주식회사 현대 디스플레이 테크놀로지 | 박막트랜지스터 액정표시장치의 제조방법 |

| KR100803177B1 (ko) * | 2001-05-14 | 2008-02-14 | 삼성전자주식회사 | 액정표시장치용 박막 트랜지스터 및 그 제조방법 |

| KR100701658B1 (ko) * | 2001-06-14 | 2007-03-30 | 비오이 하이디스 테크놀로지 주식회사 | 액정표시장치의 제조방법 |

| KR20030015604A (ko) * | 2001-08-16 | 2003-02-25 | 씨엘디 주식회사 | 유기 전계 발광소자 제조 방법 |

| KR100796795B1 (ko) | 2001-10-22 | 2008-01-22 | 삼성전자주식회사 | 반도체 소자의 접촉부 및 그 제조 방법과 이를 포함하는표시 장치용 박막 트랜지스터 어레이 기판 및 그 제조 방법 |

| JP4197233B2 (ja) | 2002-03-20 | 2008-12-17 | 株式会社日立製作所 | 表示装置 |

| JP2006047827A (ja) | 2004-08-06 | 2006-02-16 | Mitsubishi Electric Corp | 液晶表示装置およびその製造方法 |

| JP5079463B2 (ja) * | 2007-11-20 | 2012-11-21 | 株式会社ジャパンディスプレイウェスト | 液晶表示装置及びその製造方法 |

| JP5306369B2 (ja) | 2008-11-21 | 2013-10-02 | シャープ株式会社 | 表示パネル用の基板、表示パネル |

| US8114720B2 (en) * | 2008-12-25 | 2012-02-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR101777863B1 (ko) | 2009-12-30 | 2017-09-14 | 엘지디스플레이 주식회사 | 박막 트랜지스터 어레이 기판 및 이의 제조방법 |

| KR101728164B1 (ko) * | 2009-12-31 | 2017-05-02 | 엘지디스플레이 주식회사 | 박막 트랜지스터 어레이 기판 및 이의 제조방법 |

| KR101801974B1 (ko) | 2009-12-31 | 2017-11-28 | 엘지디스플레이 주식회사 | 박막 트랜지스터 어레이 기판, 이를 포함하는 액정표시장치 및 이들의 제조방법 |

| CN111063255B (zh) * | 2019-12-17 | 2021-09-03 | 深圳市华星光电半导体显示技术有限公司 | 显示面板及显示装置 |

| CN116230632A (zh) * | 2023-03-10 | 2023-06-06 | 华映科技(集团)股份有限公司 | 一种避免上下两层电极短接的阵列基板的制造方法 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04324683A (ja) * | 1991-04-25 | 1992-11-13 | Fujitsu Ltd | 薄膜トランジスタ及びその製造方法 |

| JP3383047B2 (ja) * | 1992-12-25 | 2003-03-04 | ソニー株式会社 | アクティブマトリクス基板 |

| JPH07191347A (ja) * | 1993-12-27 | 1995-07-28 | Casio Comput Co Ltd | 薄膜トランジスタアレイの製造方法 |

| JP3221240B2 (ja) * | 1994-06-24 | 2001-10-22 | ソニー株式会社 | 表示用基板の製造方法 |

| JP3299869B2 (ja) * | 1995-09-27 | 2002-07-08 | シャープ株式会社 | 液晶表示装置とその製造方法 |

| JP3152193B2 (ja) * | 1996-12-18 | 2001-04-03 | 日本電気株式会社 | 薄膜トランジスタアレイ基板およびその製造方法 |

| JPH10221712A (ja) * | 1997-02-04 | 1998-08-21 | Sharp Corp | 液晶表示装置の製造方法 |

| JP3208658B2 (ja) * | 1997-03-27 | 2001-09-17 | 株式会社アドバンスト・ディスプレイ | 電気光学素子の製法 |

-

1998

- 1998-11-20 JP JP33171198A patent/JP3975014B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000155335A (ja) | 2000-06-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3975014B2 (ja) | 液晶表示装置の製造方法 | |

| US6927105B2 (en) | Thin film transistor array substrate and manufacturing method thereof | |

| KR100686228B1 (ko) | 사진 식각용 장치 및 방법, 그리고 이를 이용한 액정 표시장치용 박막 트랜지스터 기판의 제조 방법 | |

| US6001539A (en) | Method for manufacturing liquid crystal display | |

| US7649581B2 (en) | Array substrate of an LCD comprising first and second gate insulating layers and method of fabricating the same | |

| KR100314201B1 (ko) | 박막트랜지스터형액정표시장치및그제조방법 | |

| JP2005242372A (ja) | 液晶表示装置および液晶表示装置の製造方法 | |

| US5998230A (en) | Method for making liquid crystal display device with reduced mask steps | |

| JP2012103697A (ja) | アレイ基板及び液晶ディスプレイ | |

| KR20020036023A (ko) | 액정 표시 장치용 어레이 기판의 제조 방법 | |

| KR100650401B1 (ko) | 액정 표시 장치용 어레이 기판 및 그의 제조 방법 | |

| US7125756B2 (en) | Method for fabricating liquid crystal display device | |

| US6317174B1 (en) | TFT array substrate, liquid crystal display using TFT array substrate, and manufacturing method thereof | |

| JPH11352515A (ja) | 液晶表示装置およびその製造方法 | |

| KR20040097517A (ko) | 박막 트랜지스터 기판 | |

| JP3591061B2 (ja) | 薄膜トランジスタの製造方法 | |

| US20200035709A1 (en) | Method for manufacturing thin-film transistor array substrate and thin-film transistor array substrate | |

| KR100663288B1 (ko) | 박막 트랜지스터 액정표시장치의 제조방법 | |

| KR100527086B1 (ko) | 액정표시장치의 제조방법 | |

| KR100897720B1 (ko) | 액정표시장치의 제조방법 | |

| KR100205867B1 (ko) | 액티브매트릭스기판의 제조방법 및 그 방법에 의해제조되는액티브매트릭스기판 | |

| JP2001051297A (ja) | アレイ基板及びその製造方法 | |

| KR100599958B1 (ko) | 고개구율 및 고투과율 액정표시장치의 제조방법 | |

| KR20000061175A (ko) | 액정표시장치의 제조방법 | |

| KR100891070B1 (ko) | 액정표시장치 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060517 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061226 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070605 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070618 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100622 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| S631 | Written request for registration of reclamation of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313632 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100622 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100622 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110622 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120622 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130622 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |