JP3967002B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP3967002B2 JP3967002B2 JP17336398A JP17336398A JP3967002B2 JP 3967002 B2 JP3967002 B2 JP 3967002B2 JP 17336398 A JP17336398 A JP 17336398A JP 17336398 A JP17336398 A JP 17336398A JP 3967002 B2 JP3967002 B2 JP 3967002B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- node

- circuit

- power supply

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Power Sources (AREA)

- Static Random-Access Memory (AREA)

- Logic Circuits (AREA)

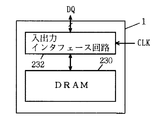

- Dram (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17336398A JP3967002B2 (ja) | 1997-09-11 | 1998-06-19 | 半導体集積回路 |

| US09/149,050 US6087885A (en) | 1997-09-11 | 1998-09-08 | Semiconductor device allowing fast and stable transmission of signals |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP9-246643 | 1997-09-11 | ||

| JP24664397 | 1997-09-11 | ||

| JP17336398A JP3967002B2 (ja) | 1997-09-11 | 1998-06-19 | 半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH11150469A JPH11150469A (ja) | 1999-06-02 |

| JPH11150469A5 JPH11150469A5 (enExample) | 2005-10-13 |

| JP3967002B2 true JP3967002B2 (ja) | 2007-08-29 |

Family

ID=26495370

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP17336398A Expired - Fee Related JP3967002B2 (ja) | 1997-09-11 | 1998-06-19 | 半導体集積回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3967002B2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014209765A1 (en) | 2013-06-28 | 2014-12-31 | Intel Corporation | I/o driver transmit swing control |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4822572B2 (ja) * | 1999-09-02 | 2011-11-24 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| JP4504536B2 (ja) * | 2000-08-29 | 2010-07-14 | ルネサスエレクトロニクス株式会社 | 出力制御装置及び出力制御方法 |

| US6496044B1 (en) * | 2001-12-13 | 2002-12-17 | Xilinx, Inc. | High-speed output circuit with low voltage capability |

| KR100607168B1 (ko) * | 2002-01-21 | 2006-08-01 | 삼성전자주식회사 | 1/2 전원전압 발생회로 및 이를 이용한 반도체 메모리 장치 |

| JP3989358B2 (ja) | 2002-11-13 | 2007-10-10 | 株式会社日立製作所 | 半導体集積回路装置および電子システム |

| US7292088B2 (en) * | 2004-05-19 | 2007-11-06 | International Rectifier Corporation | Gate driver output stage with bias circuit for high and wide operating voltage range |

| JP4795670B2 (ja) * | 2004-06-18 | 2011-10-19 | 三星電子株式会社 | 共有ディカップリングキャパシタンス |

| US9071243B2 (en) * | 2011-06-30 | 2015-06-30 | Silicon Image, Inc. | Single ended configurable multi-mode driver |

| JP5408274B2 (ja) * | 2012-02-20 | 2014-02-05 | 富士通セミコンダクター株式会社 | 半導体出力回路及び外部出力信号生成方法並びに半導体装置 |

| US20160162214A1 (en) * | 2014-12-08 | 2016-06-09 | James A McCall | Adjustable low swing memory interface |

| JP6616953B2 (ja) * | 2015-03-30 | 2019-12-04 | ラピスセミコンダクタ株式会社 | 信号出力回路 |

| US9793882B1 (en) * | 2016-12-05 | 2017-10-17 | Texas Instruments Incorporated | Voltage clamp circuit |

| US10903145B2 (en) * | 2017-11-02 | 2021-01-26 | Microchip Technology Incorporated | Symmetric input circuitry for IC in two-pin package |

| JP7717077B2 (ja) * | 2020-09-07 | 2025-08-01 | ソニーセミコンダクタソリューションズ株式会社 | 制御回路および駆動回路 |

-

1998

- 1998-06-19 JP JP17336398A patent/JP3967002B2/ja not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2014209765A1 (en) | 2013-06-28 | 2014-12-31 | Intel Corporation | I/o driver transmit swing control |

| EP3014772A4 (en) * | 2013-06-28 | 2017-03-08 | Intel Corporation | I/o driver transmit swing control |

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11150469A (ja) | 1999-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6087885A (en) | Semiconductor device allowing fast and stable transmission of signals | |

| JP3967002B2 (ja) | 半導体集積回路 | |

| KR100786924B1 (ko) | 반도체 장치 | |

| JP4850387B2 (ja) | 半導体装置 | |

| JP4037470B2 (ja) | 半導体装置 | |

| TWI423395B (zh) | Semiconductor integrated circuit device | |

| JPH10135424A (ja) | 半導体集積回路装置 | |

| JP3838607B2 (ja) | 半導体集積回路装置 | |

| US6724223B2 (en) | Semiconductor device used in two systems having different power supply voltages | |

| US6411160B1 (en) | Semiconductor integrated circuit device | |

| JPH10173509A (ja) | 半導体集積回路装置 | |

| US6100744A (en) | Integrated circuit devices having improved internal voltage generators which reduce timing skew in buffer circuits therein | |

| JPS5870482A (ja) | 半導体集積回路 | |

| US7782653B2 (en) | Semiconductor memory device and method of operating the semiconductor memory device | |

| JP2008310918A (ja) | 半導体記憶装置 | |

| KR100299806B1 (ko) | 고속 또한 안정하게 신호를 전달할 수 있는 반도체 장치 | |

| JP2928531B2 (ja) | 大規模集積回路 | |

| US6304508B1 (en) | Semiconductor device | |

| JP6522186B2 (ja) | 半導体記憶装置 | |

| JPH04123466A (ja) | 半導体装置 | |

| TW200405343A (en) | Semiconductor memory | |

| JPH023176A (ja) | 半導体メモリ回路 | |

| JP2000353785A (ja) | 半導体装置 | |

| US6590810B2 (en) | Source biasing circuit for flash EEPROM | |

| JP3786660B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050610 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050610 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070320 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070427 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070522 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070530 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110608 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110608 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110608 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |