JP3813640B2 - メモリ - Google Patents

メモリ Download PDFInfo

- Publication number

- JP3813640B2 JP3813640B2 JP29465394A JP29465394A JP3813640B2 JP 3813640 B2 JP3813640 B2 JP 3813640B2 JP 29465394 A JP29465394 A JP 29465394A JP 29465394 A JP29465394 A JP 29465394A JP 3813640 B2 JP3813640 B2 JP 3813640B2

- Authority

- JP

- Japan

- Prior art keywords

- cell

- program

- array

- gate

- cells

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000015654 memory Effects 0.000 title claims description 25

- 238000007667 floating Methods 0.000 claims description 10

- 238000012795 verification Methods 0.000 claims description 2

- 238000000034 method Methods 0.000 description 30

- 239000000872 buffer Substances 0.000 description 21

- 238000010586 diagram Methods 0.000 description 14

- 101100328890 Arabidopsis thaliana COL3 gene Proteins 0.000 description 7

- 230000000295 complement effect Effects 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 230000003213 activating effect Effects 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 238000013459 approach Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is DC

- G05F3/10—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices

- G05F3/20—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations

- G05F3/24—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations wherein the transistors are of the field-effect type only

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/563—Multilevel memory reading aspects

- G11C2211/5634—Reference cells

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Read Only Memory (AREA)

Description

【発明の分野】

この発明は一般に、メモリアレイのための基準化方式に関し、より特定的には低電圧源および多密度メモリアレイで使用される一括電気的消去可能プログラム可能リードオンリメモリ(EEPROM)セルのしきい値を決定するのに用いられる基準化方式に関する。

【0002】

【関連技術の説明】

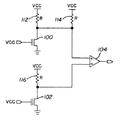

メモリセルのしきい値を決定するのに用いられる伝統的な基準化方式の1つは、センス比と結合されたプログラムされていない基準セルを含む。図1はセンス比と結合されてアレイセル102のための基準を提供するそのような基準セル100を示す。センス比は、VCCとアレイセル100のドレインとの間に接続された同一の値Rを有する2つの並列の抵抗素子112および114、ならびにVCCとアレイセル102のドレインとの間に接続された値Rの付加的な抵抗素子116によって提供される。基準セル100のドレインはコンパレータ104の1つの入力に基準出力を与える。アレイセル102のドレインはコンパレータ104の第2の入力にアレイセル出力を与える。コンパレータ104の出力はアレイセル102のしきい値状態を示す。

【0003】

図1におけるアレイセル102の状態を読出すため、基準セル100とアレイセル102とのゲートにVCCが与えられる。VCCが与えられると、センス比はコンパレータ104が基準セル100のドレインに見る電圧を、アレイセル102のドレインと比べて変動させる。コンパレータ104が基準セル100のドレインに見る電圧は、したがってVCC−1/2RID であり、コンパレータがアレイセル102のドレインに見る電圧はVCC−ID Rである。ID はMOSトランジスタのための飽和領域の式ID =K(VGS−Vt )2 からわかるように基準セル100およびアレイセル102のしきい値Vt によって制御される。ここでVGSはVCCに等しい。基準セル100とアレイセル102との両方がプログラムされていない、または同一のしきい値Vt を有している場合、センス比はアレイセル出力よりもコンパレータ104への基準出力においてより高い電圧を与え、それによりコンパレータ104が第1の状態を出力することになる。アレイセルがある一定のレベルまで高められたしきい値を有するようにプログラムされていれば、そのアレイセルのためのID は低減され、アレイセル出力の電圧は基準セル出力における電圧を超えて上昇し、これによりコンパレータ104は第2の状態を出力するようになる。

【0004】

センス比の方法は、基準セルおよびアレイセルのドレインに接続された異なる抵抗器の比を用いるので、このセンス比の方法は抵抗素子の温度およびプロセスの変動によってもVCCの変動によってもアレイセル出力に関して変動する基準出力を提供する。

【0005】

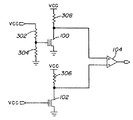

図3の回路は、バイアスゲート方法と呼ばれる別の伝統的な基準化方式を示す。バイアスゲート方法はセンス比の方法よりも正確な基準を提供するが、これはセンス比の方法と比べてプロセスや温度やVCCの変動の影響が低減されているからである。図3の回路は、図1のセンス比回路に類似のプログラムされていない基準セル100、アレイセル102、およびコンパレータ104を含む。便宜上、図3およびそれ以降の図面では、前の図面から引継がれる構成要素を示すために使用されている参照番号は、同様に引継がれている。

【0006】

基準セル100とアレイセル102とのドレインに直接接続された抵抗器の比を提供する、図1のセンス比の方法とは違って、図3の回路は基準セル100のゲートに接続されてVGSを変動させる抵抗器の比を有する。抵抗器の比は、VCCと基準セル100のゲートとの間に接続された抵抗素子302、ならびに基準セル100のゲートを接地する抵抗素子304によって提供される。基準セル100のドレインはコンパレータ104の1つの入力に基準出力を与える。アレイセル102のドレインはコンパレータ104の第2の入力にアレイセル出力を与える。同じものである抵抗素子306および308がVCCを基準およびアレイセル出力に接続して、それらのID 出力をコンパレータ104の入力における電圧に変換する。直接ID を変える代わりに、VGSを変動させることによって、抵抗素子に対するプロセスおよび温度の影響、ならびにVCCの変動が基準セルとアレイセルとの出力間にもたらす変動は、センス比の方法における場合よりも少なくなる。

【0007】

図3におけるアレイセル102の状態を読出すために、電圧VCCがアレイセル102のゲートには直接に与えられる一方で、基準セル100のゲートには抵抗素子302および304を介して与えられる。基準セル100とアレイセル102とが双方ともプログラムされていない、または同一のVt を有している場合、抵抗素子302および304はより低いVGSを与え、したがってコンパレータ104への基準セル出力においてアレイセル出力における電流よりも低いID を与える。それによりコンパレータ104は第1の状態を示すようになる。アレイセルがある一定のレベルまで高められたしきい値を有するようにプログラムされていれば、アレイセル出力は基準セル出力を超えて上昇し、コンパレータ104に第2の状態を出力させる。

【0008】

センス比やバイアスゲート方式などの基準方式では、アレイセル出力に関してのプロセス、温度、およびVCCの変動による基準出力の変動は、読出エラーを生じることがあり得る。エラーの起こる可能性は、多密度の、または低電圧源のメモリなどアレイセルのしきい値状態間の動作マージンが低いメモリで、より著しい。図2は、単一密度、3/2密度、および2倍密度となるように構成された典型的な多密度メモリのための基準レベルおよびアレイセルのしきい値状態を示す。示されるように、密度が高まるにつれ、基準レベルとアレイセル状態との間の動作マージンは減少する。たとえば、単一密度を用いるなら、ゼロ状態と基準状態との間のマージンは(4.00−2.9V=1.10V)である。3/2密度では、マージンは50%低減されて(4.00V−3.45V=0.55V)となり、2倍密度ではマージンは0.33Vまで低減される。低電圧源メモリにおける動作マージンが制限されているのは、VCCの低減がアレイセルのしきい値状態に利用可能な範囲を制限するからである。動作マージンが低ければ、起こるかもしれないエラーを低減するため、アレイセルの電気的特性における変動に追随する基準が必要である。

【0009】

【発明の概要】

この発明は、アレイセルの電気的特性における変動に追随する基準を備えた基準化方式を提供する。

【0010】

この発明はプログラム可能基準であって、1つまたはそれ以上の基準セルを含み、各基準セルはそのしきい値を設定するために制御された環境の中でプログラムされたフローティングゲートを有する。アレイセルの状態を読出すために、アレイセルおよび基準セルのゲートに同一の電圧VCCが与えられる。加えて、アレイセルおよび基準セルの出力は同じバイアス条件下に維持される。読出中、基準セルのドレインは、基準セルのしきい値に対するアレイセルのしきい値を決定するためにアレイセルのドレイン出力と比較される出力を提供する。

【0011】

この発明はさらに、プログラムされていないセルに関してバイアスを行なうためのバイアスゲート方法を用いる基準セルをプログラムするための回路を含む。基準セルは好ましくは製造者によってテスト時間にプログラムされ、それにより確実にVCCおよび温度が厳密な許容誤差内に留まって、バイアスゲート方法を用いて基準しきい値をプログラムするときの変動が排除される。アレイセルは次により緩やかなVCCおよび温度の許容誤差のもとでプログラムされ読出されて、その後基準セルが使用される。

【0012】

アレイセルの読出中、基準セルおよびアレイセルはセンス比またはバイアスされたゲートの方法を用いるのではなく、むしろ同じバイアス条件下に維持され、それにより基準およびアレイセル出力に対するプロセス変動の影響が低減される。VCCは基準セルのゲートにもアレイセルのゲートにも同じように読出電圧として与えられるので、基準セルおよびアレイセルの出力間の動作マージンはVCCの変化に対して実質的に一定を維持する。しきい値の変化が確実に温度に対し一定に留まるようにするため、アレイセルおよび基準セルはまた、好ましくは同じ集積回路上のコアセルとして含まれる。

【0013】

【詳しい説明】

この発明のさらなる詳細は、添付の図面の助けを借りて説明される。

【0014】

図4は、アレイセル400を、このアレイセル400を読出すのに用いられる本発明のプログラム可能基準セル402−1から402−(n−1)とともに示す。アレイセル400は、ワード選択回路404でデコードされるワードアドレスを与えかつアレイセル400のゲートに選択電圧VSEL を印加することによって読出される。選択電圧は基準セル402−1から402−(n−1)のゲートに同じように与えられる。VSEL は、1993年12月1日に提出された本件の発明者らによる「多密度および低電圧源メモリのための基準トラッキングを備える昇圧・安定化ゲート電源(Boosted and Regulated Gate Power Supply With Reference Tracking for Multi-Density and Low Voltage Supply Memories )」と題されここに引用により援用される米国特許出願連続番号08/160,578号で開示されるようにVCCでも、VDDでも、または昇圧ゲート電圧でもよい。アレイセル400の出力は、本発明の基準セル402−1から402−(n−1)の1つまたはそれ以上の出力に接続され、比較回路406に至る。比較回路406は、アレイセル400の状態を示す信号を出力する。

【0015】

アレイセル400はプログラム可能なしきい値を有するフローティングゲートを備えたトランジスタとして示されているが、アレイセル400がしきい値の固定されたROMトランジスタであってもよい。アレイセル400は、図2に示されるように3/2密度セルの0 0状態、0 0.5状態、または1 1状態などの状態を示すn個のしきい値の1つを記憶する。

【0016】

基準セル402−1から402−(n−1)は、各々フローティングゲートを有しており、このフローティングゲートは基準しきい値を設定するべくプログラムされてもよい電荷を蓄積する。合計n−1個の基準セルが用いられ、これらは各々が図2の3/2密度セルにおける基準状態AおよびBなどの連続的なしきい値レベルにプログラムされる。基準セル402−1から402−(n−1)とアレイセル400とを同様にバイアスし、それらのゲートに同一の電圧VSEL を印加することにより、基準セル402−1から402−(n−1)のしきい値を、アレイセル400のしきい値と比較することができる。

【0017】

比較回路406は、選択電圧VSEL が印加されたときにアレイセル400の出力を基準セル402−1から402−(n−1)の出力と比較することによってしきい値の比較を行なう。比較回路406のための典型的な回路構成は、「メモリセル1つあたりNビットを備える電気的に書換え可能な不揮発性メモリ(Electrically Alterable Non-volatile Memory)」と題されたバンクス(Banks )による米国特許第5,218,569号、および「多ビットリードオンリメモリ回路(Multi-bit Read Only Memory Circuit)」と題されたシェパード(Sheppard)による米国特許第4,495,602号に示されており、これらは双方ともここに引用によって援用される。比較回路406は、アレイセル400によって記憶可能なしきい値の状態により示されることのできる数のビットを有するデジタル信号として比較結果を出力する。

【0018】

図5は、アレイセル400をプログラムするため、およびアレイセル400をプログラムするのに用いられる本発明の基準セル402−1から402−(n−1)および502−1から502−nをプログラムするために接続される回路のブロック図である。アレイセル400をプログラムするためにはアレイセルプログラムベリファイ回路504が設けられており、その一方で基準セルをプログラムするためには基準セルプログラムベリファイ回路506が設けられている。基準セル502−1から502−nは、図2で3/2密度セルについて示されたような0 0状態、0 0.5状態、または1 1状態などのn個の状態のうちの1つに各々がプログラムされたプログラム可能しきい値を有しており、これらの状態は3/2密度設計における状態AおよびBなどの状態間のものであって、基準セル402−1から402−(n−1)によって記憶可能である。

【0019】

アレイセルプログラムベリファイ回路504はアレイセル400のゲートおよびドレインに接続されて、アレイセル400をプログラムする。アレイセルプログラムベリファイ回路504はまた、基準セル502−1から502−nのドレインにも接続されて、アレイセルの出力と基準セルの出力とを比較し、アレイセル400が適正にプログラムされているかどうかを判断する。アレイセルプログラムベリファイ回路504のための典型的な回路構成は、多密度セルをプログラムするのに用いられる方法とともに、前に引用したバンクスによる米国特許第5,218,569号で示され、説明されている。

【0020】

基準セルプログラムベリファイ回路506は、ゲートおよびドレインに接続されて、基準セル402−1から402−(n−1)および基準セル502−1から502−nのプログラムができるようにする。基準セルプログラムベリファイ回路506は、伝統的な方法を用いてプログラムおよびベリファイ電圧を供給し、基準セルのプログラミングを可能にする。基準プログラムベリファイ回路506はさらに、適正なプログラミングをベリファイするのにバイアスゲート方法を用いるプログラムされていないセルに関して各基準をバイアスするための回路を用いる。回路はさらに、基準ビットの各々を最後まで順序付けて、プログラムされている基準セルの適正なビットラインおよびワードラインを能動化するためにも設けられる。

【0021】

基準プログラムベリファイ回路506は、好ましくは製造者がテスト時間に基準をプログラムするのに用いられ、それによりVCCおよび温度はバイアスされたゲートの方法を使用している場合に基準しきい値を設定する際の変動を排除するべく厳密な許容誤差内に留まる。アレイプログラムベリファイ回路504は、後にVCCおよび温度のより緩やかな許容誤差を用いたアレイセルをプログラムするのに利用される。

【0022】

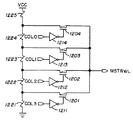

図6および7は図2に示されるような3/2密度のメモリアレイのために設計された本発明のプログラムされた基準の一実施例を表わす。図6および7は、図5の基準セルプログラムベリファイ回路506を構成する構成要素を、プログラムされるべき基準セルを含む基準アレイ600とともに含む。基準セルをプログラムするのに必要とされる回路の量および複雑さを低減するため、図6および7の回路は基準セルを1度に1つずつプログラムするように設計される。

【0023】

図6および7の回路はプログラムベリファイ信号回路602を含み、これは基準がプログラムされるべきであるということを示すPRREF信号を受取ると、プログラム信号とベリファイ信号とを交互に生成して個々の基準セルをプログラムする。プログラム中、基準セルのドレインに与えられるプログラム電圧は、信号VPROGとして供給される。信号VPXは基準セルのゲートにプログラム電圧とベリファイ電圧とを交互に与えて、基準セルをプログラムする。VPXはアレイセルのプログラミングを読出している、またはベリファイしている間、読出電圧を与える。ベリファイの間、信号VERIFYがアサートされる。プログラム中は、信号PGMがアサートされる。プログラムベリファイ信号回路602を設けるには、単一フローティングゲートメモリセルをプログラムするための伝統的な回路を用いることができる。そのような伝統的な回路は一般的に前述のバンクスによる米国特許第5,218,569号に記載されている。

【0024】

すべての基準セルを最後まで順序付し、選択されたセルにプログラムおよびベリファイ電圧を送るには、制御論理が設けられて適正な基準ビットラインおよび基準ワードラインを能動化する。制御論理は、基準カウント回路604およびそれに伴ういくらかの混合論理からなる。基準カウント回路604は、PRREF信号を受取ると順序付を始め、列信号(COL0〜COL3)および行信号(ROW0〜ROW5)を与えて、プログラムおよびベリファイ電圧をどの基準セルが受取るのかを示す。基準カウント回路604は前のセルが適正にプログラムされたことを示す信号RDSO0〜RDSO3およびVERIFYが与えられると、次の順序の基準セルビットに進む。

【0025】

データバッファ基準606とセンスバイアス回路608とは、基準カウント回路604によって出力された列および行信号をデコードして、選択された基準セルにプログラムおよびベリファイ電圧を与える。データバッファ基準606はPRREFとPGMとを受取ると、列信号(COL0〜COL3)をデコードして、基準ビットライン(REFBL0〜REFBL3)の1つにおけるプログラム電圧信号VPROGを基準アレイ600における基準セルの列のドレインに向ける。センスバイアス回路608はPRREFを受取ると、行信号(ROW0〜ROW3)をデコードして、基準ワードライン(REFWL0〜REFWL5)の1つにおけるプログラムおよびベリファイ電圧信号VPXを基準アレイ600内の基準セルの列のゲートに送る。センスバイアス回路608は読出信号をも受取り、アレイセルの読出またはベリファイ中に、すべてのワードラインへVPXを与える。PGMは、アレイセルのプログラム中に、センスバイアス回路608を不能化するために受取られる。

【0026】

基準アレイ600における1つのビットが基準ビットをプログラムするための基準として設けられる。このビットを黄金基準と呼ぶ。バイアスゲート方法を用いてこの黄金基準のゲートをバイアスするために、基準バイアス回路610によって提供されるいくつかの抵抗器の比の1つを、黄金基準のゲートへのマスタワードライン(MSTRWL)に接続することができる。基準バイアス回路610の特定の抵抗器の比が、基準カウント回路604から受取られる列信号(COL0〜COL3)によって制御される。

【0027】

基準信号が適正にプログラムされたかどうかをベリファイするため、プログラム基準は基準センス回路612、カスコードプリアンプ614、およびセンスアンプ616を含む。VERIFYとPRREFとがアサートされたときに、基準センス回路612は列信号(COL0〜COL3)をデコードしてイネーブル信号(REFSEN0〜REFSEN4)を与え、適正な回路614のカスコードプリアンプと回路616のセンスアンプとを能動化する。回路614の能動化されたカスコードプリアンプは、プログラムされている基準セルのビットライン(REFBL0〜REFBL3)からの電流を受取るように接続され、能動化された基準セル出力電圧(SAREF0〜SAREF3)を印加する。回路614における付加的なカスコードプリアンプは、黄金基準のビットライン(GOLBL)からの電流を受取るように接続されて、イネーブル信号(REFSEN0〜REFSEN4)が受取られると黄金基準出力電圧(SAREF4)を与える。回路616の能動化されたセンスアンプは、能動化された基準セル出力電圧(SAREF0〜SAREF3)を黄金基準出力電圧(SAREF4)と比較し、能動化された基準セル出力電圧と黄金基準セル出力電圧とが実質的に等しいかどうかを示す信号(RDSO0〜RESO3)を出力する。

【0028】

図6および7の構成要素のための詳細な回路構成は、後続する図面に示されており、それらは以下で説明される。

【0029】

[基準アレイ600]

図8は、図6に示した基準アレイ600の基準セルおよび黄金基準のための回路を示す。基準セルのゲートにはワードライン接続(REFWL0〜REFWL5)が提供され、基準セルのドレインにはビットライン接続(REFBL0〜REFBL3)が提供される。基準セルは、予め定められたしきい値にプログラムされてよいフローティングゲートを有する。

【0030】

図6の回路は、8ビット出力を有する3/2密度設計に必要とされる合計24個の基準セルを含む。図2の3/2密度設計の値からわかるように、1つのアレイセルに4つの基準セルビットライン出力を与えるには4つの基準セルが必要である。2つの基準セルは、アレイセルのしきい値状態を定めるために読出中に必要な基準状態AおよびB値を提供する。2つの付加的な基準セルが、アレイセルの適正なプログラミングをベリファイするのに必要な0 0状態および0 0.5状態を提供する。ここで1 1状態はプログラムされていない状態である。4ビットライン出力のそれぞれ異なった6つの組を6つの異なったアレイセルに与えて8ビット出力を提供するには、4つの基準セルが6組必要である。3/2密度設計で8ビット出力を提供するのに6個のアレイセルが使用されているのは、各アレイセルが3つの可能な状態のうち単一密度設計でのように2つではなく1つの状態を記憶している場合には、8ビットを表わすのに必要とされる可能な値を記憶するのに要求されるセルは6個だけだからである。

【0031】

図8の回路はさらに、ワードライン接続(MSTRWL)とビットライン接続(GOLBL)とを備える黄金基準セルを含む。黄金ビットはプログラムされないままのUV(紫外線)消去されたフローティングゲートを有する。図8の基準セルは好ましくはアレイセルと同じ集積回路上にコアセルとして含まれ、アレイセルはプログラムおよび読出にこの基準セルを用いるので、温度およびプロセスが変動しても、基準セルとアレイセルとの間での変動は実質的に均一なもののままとなる。

【0032】

[基準カウント回路604]

図9および10は、図6の基準カウント回路604のための回路を示す。カウンタを提供するため、図9および10の回路は複数個のシフトレジスタ801〜806を含む。カウントを同期させるため、VERIFY信号が、シフタ801のCLK入力と、インバータ810を介してシフタ801のCLKB入力とに与えられる。RDSO0〜RDSO3信号がNORゲート812およびインバータ814によって受取られてOR処理され、シフタ801のDATA入力を提供する。ビットがプログラムされるべくベリファイされると、RDSO0〜RDSO3信号の1つがアサートされ、それによりVERIFYの立下がり端縁で、シフタ801のQおよびQBが状態を変える。

【0033】

シフタ801のQおよびQB出力は、それぞれシフタ802のCLKBおよびCLK入力に接続される。さらに、シフタ802および803のQおよびQB出力がシフタ803および804のそれぞれのCLKおよびCLKB入力に接続され、その一方でシフタ802、803、および804のQB出力がそれらのDATA入力それぞれにフィードバックされる。シフタ802、803、および804のQおよびQB出力は、それぞれQ0、QB0、Q1、QB1、Q2、およびQB2出力を形成する。Q1およびQ2出力はシフタ805のCLK入力に至るNANDゲート816に接続され、その一方でNANDゲート816の出力はインバータ818を介してシフタ805のCLKB入力に接続される。シフタ805のQおよびQB出力はシフタ806のCLKおよびCLKB入力に接続され、シフタ805および806のQB出力はそれらのDATA入力それぞれにフィードバックされる。シフタ805および806のQおよびQB出力は、それぞれQ3、QB3、Q4、およびQB4出力を形成する。

【0034】

ROW0〜ROW5およびCOL0〜COL3出力信号を与えるためには、論理回路がシフタ802〜806のQ1〜Q4およびQB1〜QB4出力に接続されるように設けられる。論理回路820は、図示されているようにQ0〜Q2およびQB0〜QB2出力のいくつかの組合せに接続されて行ビット(ROW0〜ROW5)を最後まで順序付し、その一方で作用される列(COL0〜COL3)は論理822に接続されたQ3、QB3、Q4、およびQB4の出力の組合せによって制御されるにつれ更新される。

【0035】

プログラム基準モードに入る際、シフトレジスタをリセットするため、シフトレジスタ801、805、および806には、インバータ810を介してPRREF信号の補信号を受取るべく接続されたリセットがある。さらに、シフトレジスタ802〜804はプログラム基準モードに入る際にNANDゲート824を介してPRREF信号の補信号を受取る。NANDゲート816の出力はさらに、作用される列が更新されるときにシフトレジスタ802〜804をリセットするようNANDゲート824を介して接続される。

【0036】

図11は、図9および10のシフトレジスタ801〜806のための回路を示す。図11のシフトレジスタは、2つのラッチ902および904を含む。トランジスタ906はDATA入力信号をラッチ902の入力に結合する電流経路を有する。トランジスタ906はCLK入力に接続されるゲートを有する。ラッチ902の入力はさらにトランジスタ908を介して接地され、トランジスタ908はRESET入力に接続されたゲートを有する。トランジスタ910は、そのゲートに接続されたCLKB入力によって制御され、ラッチ902の出力をラッチ904の入力に結合する電流経路を有する。ラッチ904はさらにRESET入力によって制御されるトランジスタ912を介してVCCに接続される。ラッチ904の出力はシフタのQ出力を提供し、その一方でQB出力がラッチ904の出力からインバータ914を介して提供される。

【0037】

[データバッファ基準回路606]

図12は、図6に示したデータバッファ基準回路606のための回路構成を示す。図12の回路はプログラム基準モードに入るとPRREF信号を受取り、プログラムベリファイ信号回路602からのPGM信号はプログラム信号が与えられたことを示し、COL0〜COL3信号は図6に示されるように基準カウント回路604から出力される。PRREFおよびPGM信号はCOL0〜COL3信号の各々とともにそれぞれのNANDゲート1001〜1004の入力に接続されて、PRREF、PGM、およびそれぞれのCOL0〜COL3入力が能動化されるとバッファ1011〜1014の1つを能動化する。バッファ1011〜1014は、図6のプログラムベリファイ信号回路602から高電圧VPROG信号を受取り、VPROGをそれぞれの基準セルビットライン(REFBL0〜REFBL3)にそのバッファそれぞれが能動化されたときに与える。VPROGが与えられていないときには、REFBL0〜REFBL3出力はハイインピーダンスを与える。

【0038】

バッファ1011〜1014は同一の回路構成を有しているので、バッファ1011の回路だけを説明する。バッファ1011はNANDゲート1001の出力からの選択入力信号をpチャネルトランジスタ1022のゲートで受取り、このpチャネルトランジスタ1022はVPROGをREFBL0に結合する電流経路を有する。したがって、バッファが選択されていないとき、トランジスタ1022はラインREFBL0にハイインピーダンス出力を与える。nチャネルトランジスタ1024がトランジスタ1022のゲートとNANDゲート1001の出力との間で接続され、このnチャネルトランジスタ1024のゲートはVPROGに接続されて、VPROGがVCCより下まで降下することがあれば保護を提供する。VPROGはVCCよりも著しく高い値を有しているので、VPROGのフィードバックを阻止するため、nチャネルトランジスタ1026がトランジスタ1022のゲートとNANDゲート1001の出力との間に接続され、このnチャネルトランジスタ1026のゲートはVCCに接続される。別のpチャネルトランジスタ1028がVPROGをトランジスタ1022の入力に結合し、バッファ1011が非選択のときトランジスタ1022が確実にオフに留まるようにする。トランジスタ1028は、インバータ1030によって制御されるゲートを有しており、インバータ1030はトランジスタ1022の入力とVPROGによって供給される電力とに接続された入力を有する。図12、およびそれ以降の図面では、トランジスタ1022でのようにトランジスタのドレインからソースにかけて引かれた斜めの線はpチャネルトランジスタを表わし、線がなければnチャネルトランジスタを表わす。

【0039】

[センスバイアス回路608]

図13は図6に示したセンスバイアス回路608のための回路を示す。図13の回路は、プログラム基準モードに入り、ROW0〜ROW5信号が図6に示した基準カウント回路604から出力されると、PRREF信号を受取る。PRREF信号はROW0〜ROW5信号の各々とともにそれぞれのNANDゲート1101〜1106の入力に接続されて、PRREF信号とそれぞれのROW0〜ROW5入力とが能動化されると、バッファ1111〜1116の1つを能動化する。バッファ1111〜1116は、図6のプログラムベリファイ信号回路602からVPXを介してプログラム電圧とベリファイ電圧とを交互に受取り、そのそれぞれのバッファが能動化されたときにVPXをそれぞれの基準セルワードライン(REFWL0〜REFWL5)に結合する。選択されないワードラインは、典型的には接地される。

【0040】

図13の回路はさらに読出またはベリファイモードに入るとREAD信号を受取って、アレイセルの状態を判断する。PGM信号もインバータ1108を介して受取られ、これはアレイセルをプログラムするまたは消去するためにVPX信号が与えられてはいないということを示す。PRREF信号がさらにインバータ1109を介して受取られ、これは基準セルのベリファイが行なわれていないということを示す。READ信号とインバータ1108および1109の出力とはNANDゲート1110の入力に与えられる。アレイセルの読出中、バッファ1111〜1116はVPXを介して読出電圧またはベリファイ電圧を受取り、VPX信号をすべての基準セルワードライン(REFWL0〜REFWL5)に与える。

【0041】

バッファ1111〜1116は同一の回路構成を有しているので、バッファ1111の回路のみを説明する。バッファ1111はNANDゲート1118の入力でNANDゲート1101および1110の出力からの選択入力信号を受取る。NANDゲート1118の出力はインバータ1120を介してトランジスタ1122および1124によって形成されるインバータの入力に与えられる。インバータ1122・1124の出力はREFWL0信号を与える。プルアップトランジスタ1122は出力インバータ1120がローであるときに、REFWL0出力にVPX信号を結合する。プルダウントランジスタ1124はインバータ1120の出力がハイであるときにREFWL0出力を接地する。トランジスタ1126は、VPXとインバータ1122・1124の入力との間に接続された電流経路を有しており、かつREFWL0出力に接続されたゲートを有していて、それによりバッファ1111が非選択のときトランジスタ1122は確実にオフとなる。VPXはプログラム中、VCCよりも著しく高い値を有しているので、フィードバックを阻止するため、インバータ1122・1124の入力とインバータ1120の出力との間にnチャネルトランジスタ1128が接続され、そのゲートがVCCに接続される。

【0042】

[基準バイアス回路610]

図14は、図6に示した基準バイアス回路610のための回路を示す。図14の回路は図6に示した基準カウント回路604から出力されるCOL0〜COL3信号を受取る。COL0〜COL3信号はインバータ1211〜1214を介してpチャネルトランジスタ1201〜1204のゲートに接続され、抵抗器の比をCOL0〜COL3信号によって選択された黄金基準MSTRWLのゲートに結合する。抵抗器の比は、トランジスタ1201〜1204の電流経路をそれぞれ抵抗器1221〜1225の連続するそれぞれのものとMSTRWLとの間で結合することによって形成される。

【0043】

前述のように、図14の回路は基準セルがバイアスゲート方法を用いて適正にプログラムされたものとしてベリファイされることを可能にする。バイアスゲート方法は、抵抗器の比を黄金基準のゲートに結合し、黄金基準出力をプログラムされている基準セルの出力と比較して、基準セルのフローティングゲートが適正なしきい値のレベルまで充電されているかどうかを判断する。この方法は、黄金ビットがMOSトランジスタの飽和領域の式ID =K(VGS−Vt )2 に従って飽和させられるため、ゲート電圧VGSを抵抗器の比を用いて固定された量だけ低減することにより、所望のしきい値Vt にプログラムされた基準セルと同じだけの電流がもたらされるということを利用するものである。

【0044】

たとえばバイアスゲートの方法を用いる場合、しきい値間の0.55Vの差が4.0Vから1.8Vのプログラム可能なしきい値電圧の最大範囲の間に留まることが要求されるならば、図2に示すように4つの基準しきい値が3/2密度アレイで3.45V、2.90V、2.35V、および1.80Vにプログラムされるだろう。第1の基準を3.45Vのレベルにプログラムするためには、抵抗器の比が黄金基準のゲートをVCC−0.55Vにバイアスするよう選択される。続いて異なった抵抗器の比が黄金基準のゲートをバイアスするために選択され、残りの基準セルがプログラムされる。前述のように、バイアスゲート方法ではVCCが変動するにつれ、プログラムされるしきい値は互いに関して変動するので、VCCを厳密な許容誤差の範囲内に維持するために製造者によってプログラミングは好ましくはテスト時間中に行なわれるということに注意されたい。同様に、しきい値が互いに関して一定に維持されることを確実にするために、製造者は好ましくは温度を厳密な許容誤差の範囲内に制御する。

【0045】

[基準センス回路612]

図15は、図6に示した基準センス回路612のための回路構成を示す。図15の回路は、回路614のカスコードプリアンプと回路616のセンスアンプとを能動化するためのイネーブル信号(REFSEN0〜REFSEN4)を与えて、現在選択されている基準が適正にプログラムされているかどうかをベリファイする。REFSEN0〜REFSEN4信号は、VERIFYがアサートされPRREF信号が受取られると与えられる。電力を保存するため、基準カウント回路604からの列信号(COL0〜COL3)を用いて必要なREFSEN0〜REFSEN4出力だけが選択され、選択された基準セルが適正にプログラムされているかをベリファイするのに必要なカスコードプリアンプとセンスアンプとを能動化する。

【0046】

図15の回路はNANDゲート1302の入力でVERIFYおよびPRREF信号を受取る。NANDゲート1302の出力は、インバータ1321〜1324を介して与えられるCOL0〜COL3のそれぞれとともにNORゲート1311〜1314の入力に接続される。NORゲート1311〜1314の出力はREFSEN0〜REFSEN3出力信号を与える。NORゲート1311〜1314の出力はさらにNORゲート1326およびインバータ1328によってOR処理されてREFSEN4信号を与え、このREFSEN4信号はカスコードプリアンプを能動化するために与えられるものであって、カスコードプリアンプはREFSEN0〜REFSEN3信号の1つが能動化されたときに黄金基準に接続される。

【0047】

[カスコードプリアンプ614]

図16は、図7に示したカスコードプリアンプ614で用いられるカスコードプリアンプの1つのための回路を示す。図7のカスコードプリアンプ614は、図16に示すようなカスコードプリアンプを5つ含む。4つのカスコードプリアンプはビットライン出力REFBL0〜REFBL3の各々を受取るために設けられており、付加的なカスコードプリアンプがGOLBL出力を受取る。カスコードプリアンプは受取られたビットラインからの電流をベリファイのプロセスの間に出力電圧SAREF1〜SAREF4に変換する。各カスコードプリアンプは基準センス回路612から前述のベリファイプロセスを能動化するためのイネーブル信号REFSEN0〜REFSEN4のそれぞれを受取る。

【0048】

図示されるように図16の回路は、特定のビットライン信号(REFBL0〜REFBL3またはGOLBL)を表わすREFBLi信号、およびREFSEN0〜REFSEN4のイネーブル信号を表わすREFSENi信号を受取る。出力SAREFiは、特定のSAREF0〜SAREF4信号出力を表わす。ドレインがSAREFi出力に接続されたカスコードトランジスタ1402によって図16の回路にはカスコード増幅器が実現される。

【0049】

プリアンプは、インバータ1408を介してイネーブルトランジスタ1404のゲートに与えられるREFSENiの補信号によって能動化される。イネーブルトランジスタ1404はVCCとSAREFi出力との間でnチャネルレベルシフトトランジスタ1418およびpチャネルロードトランジスタ1406に直列に接続される。カスコード1402のためのバイアスを提供するために、REFSENiの補数はさらにインバータ1408を介してスイッチングトランジスタ1410のゲートに与えられる。トランジスタ1410は、VCCとカスコード1402のゲートとの間でフィードバックロードトランジスタ1420へ直列に接続される。プリアンプを不能化するために、nチャネルスイッチングトランジスタ1412がゲートをインバータ1408の出力に接続されて設けられ、REFSENiの補数が提供されていないときにカスコード1402のゲートを接地する。

【0050】

REFBLi信号はトランジスタ1414を介してカスコード1402のソースに与えられ、SAREFi出力で増幅される。トランジスタ1414のゲートは、プリアンプが能動化されたときにREFSENiによって能動化される。カスコード1402のためのさらなるバイアスは、トランジスタ1416によるカスコード1402のソースからのフィードバックによってもたらされる。トランジスタ1416はトランジスタ1402のソースに接続されたゲートと、トランジスタ1402のゲートに接続されたドレインと、接地されたソースとを有する。

【0051】

[センスアンプ616]

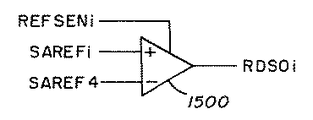

図17は図7に示したセンスアンプ616で用いられるセンスアンプの1つのための回路を示す。図7のセンスアンプ616は、図17に示すようなセンスアンプを4つ含む。4つのセンスアンプは能動化された基準セル出力電圧(SAREF0〜SAREF3)を黄金基準出力電圧(SAREF4)に比較するために設けられる。センスアンプ出力信号(RDSO0〜RDSO3)は、プログラムされているセルが完全にプログラムされているかどうかを示す。

【0052】

図示されるように、図17の回路は選択された基準セルからの特定のカスコードプリアンプ出力(SAREF0〜SAREF3)を表わすSAREFi信号と、黄金基準に接続されたカスコードプリアンプからのSAREF4信号とを受取る。図17の回路はさらに、REFSEN0〜REFSEN3イネーブル信号を表わすREFSENi信号を受取り、特定のRDSO1〜RDSO3出力を表わすRDSOi信号を出力する。

【0053】

図17のセンスアンプは、差動増幅器1500であって、REFSENi信号によって能動化される。センスアンプはSAREFi信号とSAREF4信号とを比較し、SAREFiの値がSAREF4を上回ったときにRDSOi信号を出力する。

【0054】

以上でこの発明を特定的に説明してきたが、これはこの発明をどのように作り上げ利用するかを当業者に教示するためにすぎない。多くの変形がこの発明の範囲内に包含され、この範囲は前掲の特許請求の範囲によって規定されるものである。

【図面の簡単な説明】

【図1】センス比の方法を用いてメモリアレイのための基準を提供するための回路の図である。

【図2】単一密度、3/2密度、および2倍密度のメモリのために必要とされる基準レベルを示す図である。

【図3】バイアスゲート方法を用いてメモリのための基準を提供するための回路の図である。

【図4】アレイセルを、そのアレイセルを読出すのに用いられるこの発明のプログラム可能基準セルとともに示す図である。

【図5】アレイセルをプログラムするのに用いられる回路を、そのアレイセルのプログラムおよび読出中に用いられる基準セルとともに示したブロック図である。

【図6】3/2密度のメモリアレイのために設計されたこの発明のプログラムされた基準の一実施例を示す図である。

【図7】3/2密度のメモリアレイのための設計されたこの発明のプログラムされた基準の一実施例を示す図である。

【図8】図6に示した基準アレイの基準セルおよび黄金基準のための回路図である。

【図9】図6に示した基準カウント回路の回路図である。

【図10】図6に示した基準カウント回路の回路図である。

【図11】図9および10で用いられるシフトレジスタのための回路図である。

【図12】図6に示したデータバッファ基準回路の回路図である。

【図13】図6に示したセンスバイアス回路のための回路図である。

【図14】図6に示した基準バイアス回路のための回路図である。

【図15】図6に示した基準センス回路のための回路図である。

【図16】図7に示した回路で用いられるカスコードプリアンプの1つのための回路図である。

【図17】図7に示した回路で用いられるセンスアンプの1つのための回路図である。

【符号の説明】

400 アレイセル

402−1 プログラム可能基準セル

402−2 プログラム可能基準セル

402−(n−1) プログラム可能基準セル

404 ワード選択回路

406 比較回路

Claims (3)

- アレイしきい値を決定させるゲートと、前記アレイしきい値をプログラムさせる電荷を蓄積するフローティングゲートと、出力とを有するアレイセル(400)と、

前記読出基準しきい値を決定させるゲートと、前記読出基準しきい値をプログラムさせる電荷を蓄積するフローティングゲートと、出力とを、各々が有する(n−1)個の読出基準セル(402−1〜402−(n−1))とを備えたメモリであって、

前記メモリは、

プログラム基準しきい値を決定させるゲートと、前記プログラム基準しきい値をプログラムさせる電荷を蓄積するフローティングゲートと、出力とを、各々が有するn個のプログラム基準セル(502−1〜502−n)と、

前記n個のプログラム基準セルの前記ゲートおよび前記出力に結合され、かつ前記(n−1)個の読出基準セルの前記ゲートおよび前記出力に結合された基準プログラム−ベリファイ手段(506)とをさらに備え、

前記基準プログラム−ベリファイ手段(506)は、プログラム電圧および基準ベリファイ電圧を前記n個のプログラム基準セルの前記ゲートに交互に供給して前記n個のプログラム基準セルを異なるn個のプログラム基準しきい値にプログラムし、かつプログラム電圧および基準ベリファイ電圧を前記(n−1)個の読出基準セルの前記ゲートに交互に供給して、前記プログラム基準しきい値のうちの2つの連続するしきい値の間に各々がある、連続する読出基準セルに対する読出基準しきい値をプログラムし、

前記アレイセルの前記ゲートおよび前記出力に結合され、かつ前記n個のプログラム基準セルの前記出力に結合されたアレイプログラム−ベリファイ手段(504)をさらに備え、

前記アレイプログラム−ベリファイ手段(504)は、アレイしきい値が前記n個のプ

ログラム基準セルのうちの所与の1つのプログラム基準しきい値に等しくなるようにプログラムされるまで、プログラム電圧およびアレイベリファイ電圧を前記アレイセルの前記ゲートに交互に供給し、

前記アレイセルの前記ゲートおよび前記読出基準セルの前記ゲートに読出電圧を供給して、前記アレイセルの前記出力からのアレイセル出力および前記読出基準セルの各々の前記出力からの読出基準セル出力を得るセレクタ(404)と、

前記アレイセル出力および前記読出基準セル出力を受取るように結合され、前記アレイセル出力を前記読出基準セル出力と比較し、かつ前記アレイセルをプログラムするのに用いられる前記n個のプログラム基準セルのうちの所与の1つを示す信号を供給する比較手段(406)とをさらに備えることを特徴とする、メモリ。 - 前記読出電圧または前記ベリファイ電圧が供給されているときに、前記読出基準セル、前記プログラム基準セル、および前記アレイセルを、同様にバイアスする回路をさらに備えることを特徴とする、請求項1に記載のメモリ。

- 前記プログラム基準セル、前記読出基準セル、および前記アレイセルは、単一の集積回路上にコアセルとして含まれる、請求項1に記載のメモリ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US160582 | 1993-12-01 | ||

| US08/160,582 US5828601A (en) | 1993-12-01 | 1993-12-01 | Programmed reference |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006114736A Division JP2006196184A (ja) | 1993-12-01 | 2006-04-18 | アレイセルのしきい値電圧を検出する方法およびメモリ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH07192478A JPH07192478A (ja) | 1995-07-28 |

| JP3813640B2 true JP3813640B2 (ja) | 2006-08-23 |

Family

ID=22577486

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP29465394A Expired - Lifetime JP3813640B2 (ja) | 1993-12-01 | 1994-11-29 | メモリ |

| JP2006114736A Pending JP2006196184A (ja) | 1993-12-01 | 2006-04-18 | アレイセルのしきい値電圧を検出する方法およびメモリ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006114736A Pending JP2006196184A (ja) | 1993-12-01 | 2006-04-18 | アレイセルのしきい値電圧を検出する方法およびメモリ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US5828601A (ja) |

| EP (1) | EP0656628B1 (ja) |

| JP (2) | JP3813640B2 (ja) |

| KR (1) | KR100357444B1 (ja) |

| DE (1) | DE69432452T2 (ja) |

| TW (1) | TW302479B (ja) |

Families Citing this family (83)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE69024086T2 (de) * | 1989-04-13 | 1996-06-20 | Sundisk Corp | EEprom-System mit Blocklöschung |

| US7071060B1 (en) | 1996-02-28 | 2006-07-04 | Sandisk Corporation | EEPROM with split gate source side infection with sidewall spacers |

| US6222762B1 (en) | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| JP3336813B2 (ja) * | 1995-02-01 | 2002-10-21 | ソニー株式会社 | 不揮発性半導体メモリ装置 |

| FR2745114B1 (fr) * | 1996-02-20 | 1998-04-17 | Sgs Thomson Microelectronics | Memoire non volatile multiniveau modifiable electriquement avec rafraichissement autonome |

| IL125604A (en) | 1997-07-30 | 2004-03-28 | Saifun Semiconductors Ltd | Non-volatile electrically erasable and programmble semiconductor memory cell utilizing asymmetrical charge |

| US6768165B1 (en) | 1997-08-01 | 2004-07-27 | Saifun Semiconductors Ltd. | Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping |

| KR100339023B1 (ko) | 1998-03-28 | 2002-09-18 | 주식회사 하이닉스반도체 | 문턱전압을조절할수있는플래쉬메모리장치의센싱회로 |

| FR2786910B1 (fr) * | 1998-12-04 | 2002-11-29 | St Microelectronics Sa | Memoire a grille flottante multiniveau |

| KR100295361B1 (ko) * | 1998-12-30 | 2001-07-12 | 윤종용 | 불 휘발성 반도체 메모리 장치 |

| FR2794277B1 (fr) * | 1999-05-25 | 2001-08-10 | St Microelectronics Sa | Memoire morte a faible consommation |

| US6215702B1 (en) | 2000-02-16 | 2001-04-10 | Advanced Micro Devices, Inc. | Method of maintaining constant erasing speeds for non-volatile memory cells |

| JP3776307B2 (ja) * | 2000-04-26 | 2006-05-17 | 沖電気工業株式会社 | 不揮発性メモリアナログ電圧書き込み回路 |

| US6490204B2 (en) * | 2000-05-04 | 2002-12-03 | Saifun Semiconductors Ltd. | Programming and erasing methods for a reference cell of an NROM array |

| US6928001B2 (en) | 2000-12-07 | 2005-08-09 | Saifun Semiconductors Ltd. | Programming and erasing methods for a non-volatile memory cell |

| US6396741B1 (en) | 2000-05-04 | 2002-05-28 | Saifun Semiconductors Ltd. | Programming of nonvolatile memory cells |

| US6538922B1 (en) * | 2000-09-27 | 2003-03-25 | Sandisk Corporation | Writable tracking cells |

| US6449190B1 (en) * | 2001-01-17 | 2002-09-10 | Advanced Micro Devices, Inc. | Adaptive reference cells for a memory device |

| US6614692B2 (en) | 2001-01-18 | 2003-09-02 | Saifun Semiconductors Ltd. | EEPROM array and method for operation thereof |

| US6538923B1 (en) * | 2001-02-26 | 2003-03-25 | Advanced Micro Devices, Inc. | Staircase program verify for multi-level cell flash memory designs |

| US6466480B2 (en) * | 2001-03-27 | 2002-10-15 | Micron Technology, Inc. | Method and apparatus for trimming non-volatile memory cells |

| IL148960A (en) * | 2001-04-05 | 2005-09-25 | Saifun Semiconductors Ltd | Method for programming a reference cell |

| US6584017B2 (en) | 2001-04-05 | 2003-06-24 | Saifun Semiconductors Ltd. | Method for programming a reference cell |

| TW504702B (en) * | 2001-04-13 | 2002-10-01 | Amic Technology Corp | Circuit and method for correcting overerased flash memory cells |

| US6643169B2 (en) * | 2001-09-18 | 2003-11-04 | Intel Corporation | Variable level memory |

| US6678192B2 (en) | 2001-11-02 | 2004-01-13 | Sandisk Corporation | Error management for writable tracking storage units |

| DE60134870D1 (de) | 2001-12-28 | 2008-08-28 | St Microelectronics Srl | Programmierverfahren für eine Multibitspeicherzelle |

| US6975536B2 (en) * | 2002-01-31 | 2005-12-13 | Saifun Semiconductors Ltd. | Mass storage array and methods for operation thereof |

| US6700818B2 (en) | 2002-01-31 | 2004-03-02 | Saifun Semiconductors Ltd. | Method for operating a memory device |

| US7190620B2 (en) | 2002-01-31 | 2007-03-13 | Saifun Semiconductors Ltd. | Method for operating a memory device |

| US6917544B2 (en) | 2002-07-10 | 2005-07-12 | Saifun Semiconductors Ltd. | Multiple use memory chip |

| US6826107B2 (en) | 2002-08-01 | 2004-11-30 | Saifun Semiconductors Ltd. | High voltage insertion in flash memory cards |

| US7136304B2 (en) | 2002-10-29 | 2006-11-14 | Saifun Semiconductor Ltd | Method, system and circuit for programming a non-volatile memory array |

| US6992932B2 (en) | 2002-10-29 | 2006-01-31 | Saifun Semiconductors Ltd | Method circuit and system for read error detection in a non-volatile memory array |

| US6963505B2 (en) * | 2002-10-29 | 2005-11-08 | Aifun Semiconductors Ltd. | Method circuit and system for determining a reference voltage |

| US6967896B2 (en) | 2003-01-30 | 2005-11-22 | Saifun Semiconductors Ltd | Address scramble |

| US7178004B2 (en) | 2003-01-31 | 2007-02-13 | Yan Polansky | Memory array programming circuit and a method for using the circuit |

| US7142464B2 (en) | 2003-04-29 | 2006-11-28 | Saifun Semiconductors Ltd. | Apparatus and methods for multi-level sensing in a memory array |

| US7237074B2 (en) * | 2003-06-13 | 2007-06-26 | Sandisk Corporation | Tracking cells for a memory system |

| US7123532B2 (en) | 2003-09-16 | 2006-10-17 | Saifun Semiconductors Ltd. | Operating array cells with matched reference cells |

| US6954393B2 (en) * | 2003-09-16 | 2005-10-11 | Saifun Semiconductors Ltd. | Reading array cell with matched reference cell |

| US7301807B2 (en) | 2003-10-23 | 2007-11-27 | Sandisk Corporation | Writable tracking cells |

| US7652930B2 (en) | 2004-04-01 | 2010-01-26 | Saifun Semiconductors Ltd. | Method, circuit and system for erasing one or more non-volatile memory cells |

| US7755938B2 (en) * | 2004-04-19 | 2010-07-13 | Saifun Semiconductors Ltd. | Method for reading a memory array with neighbor effect cancellation |

| US7366025B2 (en) | 2004-06-10 | 2008-04-29 | Saifun Semiconductors Ltd. | Reduced power programming of non-volatile cells |

| US7317633B2 (en) | 2004-07-06 | 2008-01-08 | Saifun Semiconductors Ltd | Protection of NROM devices from charge damage |

| US7095655B2 (en) | 2004-08-12 | 2006-08-22 | Saifun Semiconductors Ltd. | Dynamic matching of signal path and reference path for sensing |

| ITMI20041927A1 (it) * | 2004-10-12 | 2005-01-12 | Atmel Corp | Sistema e metodo pee evitare l'offset e ridurre il footprint di una memoria non volatile |

| US7638850B2 (en) | 2004-10-14 | 2009-12-29 | Saifun Semiconductors Ltd. | Non-volatile memory structure and method of fabrication |

| US7257025B2 (en) * | 2004-12-09 | 2007-08-14 | Saifun Semiconductors Ltd | Method for reading non-volatile memory cells |

| US7535765B2 (en) | 2004-12-09 | 2009-05-19 | Saifun Semiconductors Ltd. | Non-volatile memory device and method for reading cells |

| WO2006071402A1 (en) * | 2004-12-23 | 2006-07-06 | Atmel Corporation | System for performing fast testing during flash reference cell setting |

| EP1686592A3 (en) | 2005-01-19 | 2007-04-25 | Saifun Semiconductors Ltd. | Partial erase verify |

| US8053812B2 (en) * | 2005-03-17 | 2011-11-08 | Spansion Israel Ltd | Contact in planar NROM technology |

| US8400841B2 (en) | 2005-06-15 | 2013-03-19 | Spansion Israel Ltd. | Device to program adjacent storage cells of different NROM cells |

| US7184313B2 (en) | 2005-06-17 | 2007-02-27 | Saifun Semiconductors Ltd. | Method circuit and system for compensating for temperature induced margin loss in non-volatile memory cells |

| JP2007027760A (ja) | 2005-07-18 | 2007-02-01 | Saifun Semiconductors Ltd | 高密度不揮発性メモリアレイ及び製造方法 |

| US7668017B2 (en) | 2005-08-17 | 2010-02-23 | Saifun Semiconductors Ltd. | Method of erasing non-volatile memory cells |

| US7221138B2 (en) * | 2005-09-27 | 2007-05-22 | Saifun Semiconductors Ltd | Method and apparatus for measuring charge pump output current |

| JP2007164934A (ja) * | 2005-12-16 | 2007-06-28 | Fujitsu Ltd | 不揮発性半導体記憶装置 |

| US7352627B2 (en) | 2006-01-03 | 2008-04-01 | Saifon Semiconductors Ltd. | Method, system, and circuit for operating a non-volatile memory array |

| KR100772389B1 (ko) * | 2006-01-12 | 2007-11-01 | 삼성전자주식회사 | 메모리 인식 장치 |

| US7808818B2 (en) | 2006-01-12 | 2010-10-05 | Saifun Semiconductors Ltd. | Secondary injection for NROM |

| US7692961B2 (en) | 2006-02-21 | 2010-04-06 | Saifun Semiconductors Ltd. | Method, circuit and device for disturb-control of programming nonvolatile memory cells by hot-hole injection (HHI) and by channel hot-electron (CHE) injection |

| US7760554B2 (en) | 2006-02-21 | 2010-07-20 | Saifun Semiconductors Ltd. | NROM non-volatile memory and mode of operation |

| US8253452B2 (en) | 2006-02-21 | 2012-08-28 | Spansion Israel Ltd | Circuit and method for powering up an integrated circuit and an integrated circuit utilizing same |

| US7638835B2 (en) * | 2006-02-28 | 2009-12-29 | Saifun Semiconductors Ltd. | Double density NROM with nitride strips (DDNS) |

| US7388781B2 (en) * | 2006-03-06 | 2008-06-17 | Sandisk Il Ltd. | Multi-bit-per-cell flash memory device with non-bijective mapping |

| US8848442B2 (en) | 2006-03-06 | 2014-09-30 | Sandisk Il Ltd. | Multi-bit-per-cell flash memory device with non-bijective mapping |

| US7701779B2 (en) | 2006-04-27 | 2010-04-20 | Sajfun Semiconductors Ltd. | Method for programming a reference cell |

| US7605579B2 (en) | 2006-09-18 | 2009-10-20 | Saifun Semiconductors Ltd. | Measuring and controlling current consumption and output current of charge pumps |

| ITMI20062211A1 (it) * | 2006-11-17 | 2008-05-18 | St Microelectronics Srl | Circuito e metodo per generare una tensione di riferimento in dispositivi di memoria a matrice di celle non volatili |

| US7590001B2 (en) | 2007-12-18 | 2009-09-15 | Saifun Semiconductors Ltd. | Flash memory with optimized write sector spares |

| US7778098B2 (en) * | 2007-12-31 | 2010-08-17 | Cypress Semiconductor Corporation | Dummy cell for memory circuits |

| US20090219776A1 (en) | 2008-02-29 | 2009-09-03 | Xian Liu | Non-volatile memory device with plural reference cells, and method of setting the reference cells |

| KR101055568B1 (ko) | 2009-06-17 | 2011-08-08 | 한양대학교 산학협력단 | 플래시 메모리 장치의 센싱 회로 및 플래시 메모리 장치의 센싱 방법 |

| US9424946B2 (en) * | 2013-02-08 | 2016-08-23 | Seagate Technology Llc | Non-volatile buffering to enable sloppy writes and fast write verification |

| KR102111510B1 (ko) * | 2014-04-10 | 2020-05-19 | 에스케이하이닉스 주식회사 | 전자 장치 |

| US11822358B2 (en) * | 2018-08-27 | 2023-11-21 | Sigmasense, Llc. | Drive-sense circuit to determine effects of different electrical characteristics on load |

| US12087397B1 (en) | 2020-04-06 | 2024-09-10 | Crossbar, Inc. | Dynamic host allocation of physical unclonable feature operation for resistive switching memory |

| WO2021207224A1 (en) | 2020-04-06 | 2021-10-14 | Crossbar, Inc. | Distinct chip identifier utilizing unclonable characteristics of on-chip resistive memory array |

| US11727986B2 (en) * | 2020-04-06 | 2023-08-15 | Crossbar, Inc. | Physically unclonable function (PUF) generation involving programming of marginal bits |

| US11823739B2 (en) * | 2020-04-06 | 2023-11-21 | Crossbar, Inc. | Physically unclonable function (PUF) generation involving high side programming of bits |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4449203A (en) * | 1981-02-25 | 1984-05-15 | Motorola, Inc. | Memory with reference voltage generator |

| US4495602A (en) * | 1981-12-28 | 1985-01-22 | Mostek Corporation | Multi-bit read only memory circuit |

| FR2599176A1 (fr) * | 1986-05-23 | 1987-11-27 | Eurotechnique Sa | Memoire morte programmable electriquement |

| JPH02260298A (ja) * | 1989-03-31 | 1990-10-23 | Oki Electric Ind Co Ltd | 不揮発性多値メモリ装置 |

| US5172338B1 (en) * | 1989-04-13 | 1997-07-08 | Sandisk Corp | Multi-state eeprom read and write circuits and techniques |

| EP0477369B1 (en) * | 1989-06-12 | 1997-08-13 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| JPH0346197A (ja) * | 1989-07-13 | 1991-02-27 | Fujitsu Ltd | 半導体記憶装置 |

| FR2650109B1 (fr) * | 1989-07-20 | 1993-04-02 | Gemplus Card Int | Circuit integre mos a tension de seuil ajustable |

| JP2853217B2 (ja) * | 1989-11-21 | 1999-02-03 | 日本電気株式会社 | 半導体メモリ |

| JP3454520B2 (ja) * | 1990-11-30 | 2003-10-06 | インテル・コーポレーション | フラッシュ記憶装置の書込み状態を確認する回路及びその方法 |

| US5218569A (en) * | 1991-02-08 | 1993-06-08 | Banks Gerald J | Electrically alterable non-volatile memory with n-bits per memory cell |

-

1993

- 1993-12-01 US US08/160,582 patent/US5828601A/en not_active Expired - Lifetime

-

1994

- 1994-03-10 TW TW083102080A patent/TW302479B/zh not_active IP Right Cessation

- 1994-11-10 DE DE69432452T patent/DE69432452T2/de not_active Expired - Fee Related

- 1994-11-10 EP EP94308288A patent/EP0656628B1/en not_active Expired - Lifetime

- 1994-11-25 KR KR1019940031281A patent/KR100357444B1/ko not_active Expired - Lifetime

- 1994-11-29 JP JP29465394A patent/JP3813640B2/ja not_active Expired - Lifetime

-

2006

- 2006-04-18 JP JP2006114736A patent/JP2006196184A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US5828601A (en) | 1998-10-27 |

| JPH07192478A (ja) | 1995-07-28 |

| DE69432452T2 (de) | 2004-03-11 |

| KR100357444B1 (ko) | 2003-01-24 |

| EP0656628A3 (en) | 1995-08-09 |

| EP0656628B1 (en) | 2003-04-09 |

| KR950020743A (ko) | 1995-07-24 |

| DE69432452D1 (de) | 2003-05-15 |

| TW302479B (ja) | 1997-04-11 |

| JP2006196184A (ja) | 2006-07-27 |

| EP0656628A2 (en) | 1995-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3813640B2 (ja) | メモリ | |

| US5673223A (en) | Nonvolatile semiconductor memory device with multiple word line voltage generators | |

| US5638326A (en) | Parallel page buffer verify or read of cells on a word line using a signal from a reference cell in a flash memory device | |

| KR100454116B1 (ko) | 비휘발성 메모리를 프로그래밍하기 위한 비트라인 셋업 및디스차지 회로 | |

| US5335198A (en) | Flash EEPROM array with high endurance | |

| US5661685A (en) | Programmable logic device with configurable power supply | |

| US5768188A (en) | Multi-state non-volatile semiconductor memory and method for driving the same | |

| US8270213B2 (en) | Flash memory array system including a top gate memory cell | |

| EP0477369B1 (en) | Semiconductor memory device | |

| US7855583B2 (en) | Sense amplifier for low voltage high speed sensing | |

| EP0713164B1 (en) | A reference circuit | |

| US5724284A (en) | Multiple bits-per-cell flash shift register page buffer | |

| US5982662A (en) | Semiconductor memory device with improved read characteristics for data having multi values | |

| KR20190002711A (ko) | 개선된 플래시 메모리 셀 및 연관된 디코더들 | |

| JP3993354B2 (ja) | 電圧発生回路 | |

| US6999345B1 (en) | Method of sense and program verify without a reference cell for non-volatile semiconductor memory | |

| US7755945B2 (en) | Page buffer and method of programming and reading a memory | |

| CN213459059U (zh) | 非易失性存储器设备和电压生成器电路 | |

| JP3414587B2 (ja) | 不揮発性半導体記憶装置 | |

| US6178118B1 (en) | Electrically programmable semiconductor device with multi-level wordline voltages for programming multi-level threshold voltages | |

| JPH11191299A (ja) | レベルシフト回路を有する非揮発性半導体メモリ装置 | |

| US6185130B1 (en) | Programmable current source | |

| JPH0917189A (ja) | 不揮発性半導体メモリ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040922 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040928 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20041227 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20050105 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050328 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20051018 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20060117 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20060123 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060516 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060601 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090609 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090609 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090609 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100609 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110609 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110609 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120609 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120609 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130609 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130609 Year of fee payment: 7 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130609 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |