JP3681121B2 - 駆動回路及び表示装置 - Google Patents

駆動回路及び表示装置 Download PDFInfo

- Publication number

- JP3681121B2 JP3681121B2 JP2002167096A JP2002167096A JP3681121B2 JP 3681121 B2 JP3681121 B2 JP 3681121B2 JP 2002167096 A JP2002167096 A JP 2002167096A JP 2002167096 A JP2002167096 A JP 2002167096A JP 3681121 B2 JP3681121 B2 JP 3681121B2

- Authority

- JP

- Japan

- Prior art keywords

- peak value

- waveform

- drive

- driving

- slot

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2011—Display of intermediate tones by amplitude modulation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/10—Intensity circuits

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/06—Details of flat display driving waveforms

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

Description

【発明の属する技術分野】

本発明は、輝度データに対応する駆動波形を発生する駆動回路に関し、またその駆動回路を用いた表示装置に関する。また該駆動波形を発生する駆動方法に関する。特に複数の発光素子をマトリクス配線した画像表示パネルを備える画像表示装置における前記発光素子の駆動方法に関する。

【0002】

【従来の技術】

従来から、電子放出素子として熱陰極素子と冷陰極素子の2種類が知られている。このうち冷陰極素子としては、例えば表面伝導型放出素子や、電界放出型素子(以下FE型と記す)や、金属/絶縁層/金属型放出素子(以下MIM型と記す)等が知られている。表面伝導型放出素子としては、例えば、M.I.Elinson,Radio Eng.Electron Phys.,10,1290(1965)や、後述する他の例が知られている。

【0003】

表面伝導型放出素子は、基板上に形成された小面積の薄膜に、膜面に平行に電流を流すことにより電子放出が生ずる現象を利用するものである。この表面伝導型放出素子としては、前記エリンソン等によるSnO2薄膜を用いたものの他に、Au薄膜によるもの(G.Dittmer:Thin Solid Films,9,317(1972))や、In2O3/SnO2薄膜によるもの(M.Hartwell and C.G.Fonstad:IEEE Trans.ED Conf.,519(1975))や、カーボン薄膜によるもの(荒木久他:真空、第26巻、第1号、22(1983))等が報告されている。

【0004】

これらの表面伝導型放出素子の素子構成の典型的な例として、図28に前述のM.Hartwellらによる素子の平面図を示す。同図において、3001は基板であり、3004はスパッタで形成された金属酸化物よりなる導電性薄膜である。導電性薄膜3004は図示のようにH字形の平面形状に形成されている。この導電性薄膜3004に後述の通電フォーミングと呼ばれる通電処理を施すことにより、電子放出部3005が形成される。図中の間隔Lは0.5〜1(mm)、Wは0.1(mm)で設定されている。なお、図示の便宜から、電子放出部3005は導電性薄膜3004の中央に矩形の形状で示したが、これは模式的なものであり、実際の電子放出部の位置や形状を忠実に表現しているわけではない。

【0005】

M.Hartwellらによる素子をはじめとして、上述の表面伝導型放出素子においては、電子放出を行う前に導電性薄膜3004に通電フォーミングと呼ばれる通電処理を施すことにより電子放出部3005を形成するのが一般的であった。すなわち、通電フォーミングとは、導電性薄膜3004の両端に一定の直流電圧、もしくは、例えば1V/分程度の非常にゆっくりとしたレートで昇圧する直流電圧を印加して通電し、導電性薄膜3004を局所的に破壊、変形もしくは変質せしめ、電気的に高抵抗な状態の電子放出部3005を形成することである。なお、局所的に破壊、変形もしくは変質した導電性薄膜3004の一部には、亀裂が発生する。前記通電フォーミング後に導電性薄膜3004に適宜の電圧を印加した場合には、前記亀裂付近において電子放出が行われる。

【0006】

FE型の例としては、例えば、W.P.Dyke & W.W.Dolan,Field emission,Advance in Electron Physics,8,89(1956)や、あるいはC.A.Spindt,Physical properties of thin−film fieldemission cathodes with molybdenum cones,J.Appl.Phys.,47,5248(1976)等が知られている。

【0007】

FE型の素子構成の典型的な例として、図29に前述のC.A.Spindtらによる素子の断面図を示す。同図において、3010は基板であり、3011は導電材料よりなるエミッタ配線、3012はエミッタコーン、3013は絶縁層、3014はゲート電極である。本素子は、エミッタコーン3012とゲート電極3014の間に適宜の電圧を印加することにより、エミッタコーン3012の先端部より電界放出を起させるものである。また、FE型の他の素子構成として、図29のような積層構造ではなく、基板上に基板平面とほぼ平行にエミッタとゲート電極を配置した例もある。

【0008】

MIM型の例としては、例えば、C.A.Mead,Operation of tunnel−emission Devices,J.Appl.Phys.,32,646(1961)などが知られている。MIM型の素子構成の典型的な例を図30に示す。同図は断面図であり、図において、3020は基板、3021は金属よりなる下電極、3022は厚さ100オングストローム程度の薄い絶縁層、3023は厚さ80〜300オングストローム程度の金属よりなる上電極である。MIM型においては、上電極3023と下電極3021の間に適宜の電圧を印加することにより、上電極3023の表面より電子放出を起させる。

【0009】

上述の冷陰極素子は、熱陰極素子と比較して低温で電子放出を得ることができるため、加熱用ヒータを必要としない。したがって、熱陰極素子よりも構造が単純であり、微細な素子を作成可能である。また、基板上に多数の素子を高い密度で配置しても、基板の熱溶融などの問題が発生しにくい。また、熱陰極素子がヒータの加熱により動作するために応答速度が遅いのとは異なり、冷陰極素子の場合には応答速度が速いという利点もある。

このため、冷陰極素子を応用するための研究が盛んに行われてきている。

【0010】

例えば、表面伝導型放出素子は、冷陰極素子のなかでも特に構造が単純で製造も容易であることから、大面積にわたり多数の素子を形成できる利点がある。そこで、例えば本出願人による特開昭64−31332号公報において開示されるように、多数の素子を配列して駆動するための方法が研究されている。

また表面伝導型放出素子の応用については、例えば、画像表示装置、画像記録装置などの画像形成装置や、荷電ビーム源等が研究されている。

【0011】

特に、画像表示装置への応用としては、例えばUSP5,066,883や特開平2−257551号公報や特開平4−28137号公報等において開示されているように、表面伝導型放出素子と電子ビームの照射により発光する蛍光体とを組み合わせて用いた画像表示装置が研究されている。表面伝導型放出素子と蛍光体とを組み合わせて用いた画像表示装置は、従来の他の方式の画像表示装置よりも優れた特性が期待されている。例えば、近年普及してきた液晶表示装置と比較しても、自発光型であるためにバックライトを必要としない点や、視野角が広い点が優れていると言える。

【0012】

また、FE型を多数個ならべて駆動する方法は、例えばUSP4,904,895に開示されている。また、FE型を画像表示装置に応用した例として、例えば、R.Meyerらにより報告された平板型表示装置が知られている(R.Meyer:Recent Development on MicrotipsDisplay at LETI,Tech.Digest of 4th Int.Vacuum Microelectronics Conf.,Nagahama,pp.6〜9(1991))。

【0013】

またMIM型を多数個並べて画像表示装置に応用した例は、例えば特開平3−55738号公報に開示されている。

さらに、電子放出素子以外の素子を用いた画像表示装置として、EL(エレクトロルミネッセンス)素子を用いたものが、例えば特開平09−281928号公報に開示されている。

【0014】

本発明者らは、例えば図31に示す電気的な配線方法によるマルチ電子ビーム源を試みてきた。すなわち、電子放出素子を2次元的に多数個配列し、これらの素子を図示のようにマトリクス状に配線したマルチ電子ビーム源である。

【0015】

図中、1は電子放出素子を模式的に示したもの、2は行方向配線、3は列方向配線である。行方向配線2および列方向配線3は、配線抵抗4、5、配線インダクタンス6、7、および配線容量8を有するものである。なお、図示の便宜上、4×4のマトリクスで示しているが、マトリクスの規模はむろんこれに限ったわけではなく、例えば画像表示装置用のマルチ電子ビーム源の場合には、所望の画像表示を行うのに足りるだけの素子を配列し配線するものである。

【0016】

電子放出素子をマトリクス配線したマルチ電子ビーム源においては、所望の電子ビームを出力させるため、行方向配線および列方向配線に適宜の電気信号を印加する。

【0017】

図32にパルス幅変調波形を示す。例えば、マトリクスの中の任意の1行の電子放出素子を駆動するには、選択する行の行方向配線には選択電位Vsを印加し、同時に非選択の行の行方向配線には非選択電位Vnsを印加する。これと同期して列方向配線に電子ビームを出力するための駆動電位Veを印加する。この方法によれば、選択する行の電子放出素子には、Ve−Vsの電圧が印加され、また非選択行の電子放出素子にはVe−Vnsの電圧が印加される。Ve、Vs、Vnsを適宜の大きさの電位にすれば選択する行の電子放出素子だけから所望の強度の電子ビームが出力される。また、冷陰極素子の応答速度は高速であるため、駆動電位Veを印加する時間の長さを変えれば、電子ビームが出力される時間の長さも変えることができる。

同様に、列方向配線に印加する電位や電流値を変化させて輝度を制御する波高値変調と呼ばれる方式によっても電子ビームを制御することが可能である。

【0018】

【発明が解決しようとする課題】

ところで、有効画素数1920×1080、フレームレート60Hz、10ビット階調の表示装置においては、パルス波高値変調方式の場合、素子に印加するエネルギーの波高値をPiとすると、Pi/210=Pi/1024の分解能が必要とされる。電圧駆動の場合Piは数V程度となるため、1920×1080の画面全体に渡って駆動波形に数mVの分解能を要求される。この値は駆動回路を構成するICやプリント基板、電源などの特性を考慮すると実現が困難である。

【0019】

一方、パルス幅変調方式の場合、1走査線を駆動する時間は1/(60×1080)≒15μsecである。10ビットパルス幅変調を行った場合、最小パルス幅は、1/(60×1080×210)≒15nsecであり、最小15ナノ秒のパルス幅分解能が必要とされる。

【0020】

しかしながら、図31に示すような配線は、配線インダクタンス(L)と配線容量(C)と配線抵抗(R)で決定されるカットオフ周波数を持つローパスフィルタと等価である。このようなローパス特性を持つ信号配線や表示部配線を、カットオフ周波数以上の周波数スペクトル成分で構成される、線順次−パルス幅変調(PWM)駆動方式で駆動した場合、図33に示すように、素子に印加されるPWM波形の立ち上がりおよび立ち下がり波形が鈍ってしまい、低輝度における表示品位の低下が生じる。特に、情報電極駆動回路10から低階調のパルス幅変調駆動波形を印加すると、電子放出素子1に印加される走査回路11の出力波形との合成波形は、波高値が低くなった波形となる。つまり、高い周波数スペクトル成分のみで構成されるような駆動波形すなわち低階調のパルス幅変調駆動波形は波高値が低くなってしまい、低階調領域で所望の階調の画像を表示できない。

【0021】

また、非常に多数の電子放出素子をマトリクス配線したマルチ電子源に対して、制御定電流源から時間的長さの短い定電流パルスを供給する場合にも、ほとんど電子が放出されない。比較的長い期間定電流パルスを供給し続ける場合には、もちろん電子は放出され始めるが、電子放出が開始するまでには大きな立ち上がり時間が必要となっていた。

【0022】

図33は、これを説明するためのタイムチャートであって、図に示したように、制御定電流源から短い電流パルスを供給しても、電子放出素子にはほとんど電流Ifは流れない。また、長いパルスを供給した場合でも、電子放出素子に流れる駆動電流Ifは、立ち上がり時間の大きな波形になってしまう。冷陰極型の電子放出素子自身は高速応答性能を有しているのにもかかわらず、電子放出素子に供給される電流波形がなまってしまうため、結果的に放出電流Ieの波形も変形してしまっていた。

【0023】

単純マトリクス配線されたマルチ電子源においては、マトリクスの規模を大きくするとそれにともなって寄生容量(配線容量)が増大する。寄生容量の主要部分は行方向配線と列方向配線の交差部に存在するが、この等価回路を図34に示す。列方向配線3に接続された制御定電流源9から定電流I1の供給を開始すると、初めのうち電流は寄生容量8の充電に費やされてしまい、電子放出素子1の駆動電流としてほとんど作用しない。このため、電子放出素子の実効的な応答速度が低下する。

【0024】

また、電圧駆動については以下の解決すべき問題点がある。発光素子として駆動に伴って電流が流れる素子、例えばLED、EL、FED、SEDなどを用いたディスプレイでは、一般的に配線抵抗は低く設計される。したがって、等価回路としては、寄生容量、寄生抵抗、寄生インダクタンスによって構成された図31に示すモデルとなる。このような回路に従来の電圧駆動法を適用すると、電圧の印加によって寄生容量へ充電電流iが流れ込むため駆動波形立ち上がり部の鈍りが生じる。さらに寄生インダクタンスの自己誘導作用によって起電力U=−L×(di/dt)が発生し、オーバーシュート、リンギングが発生し、発光素子への異常電圧の印加が起こってしまっていた。

【0025】

近年、ディスプレイに対する大面積化、高精細化、高階調化の要求は著しくそれに伴って、配線の寄生インダクタンス、寄生容量は増加しており、駆動波形立ち上がり部の鈍りによる低輝度領域での階調のつぶれ、オーバーシュート、リンギングはますます解決すべき重要課題となっている。

【0026】

また、単純なパルス幅制御とパルス波高値制御による駆動波形は発光素子の電圧/発光強度特性の変化やばらつきによって階調の単純増加性が保証できなくなることが問題となっていた。

【0027】

また、例えば、特開平09−319327号公報で開示されるように、前記冷陰極素子に駆動電流パルスを供給するための制御電流源と、マルチ電子源の寄生容量を高速に充電するための電圧源と、前記駆動電流パルスの立ち上がりに同期させて前記電圧源と前記列方向配線とを電気的に接続する充電電圧印加手段によって、配線の寄生容量に対してほぼ充電が完了するまでの間、駆動電流パルスに加えて充電電圧を印加する方法などが行われていた。このような駆動を行った場合には階調の線形性を保証することが可能となる。

【0028】

また、特開平8−22261号公報では、デジタル映像信号の各ワードを複数のサブワードに分割し、下位のサブワードには波高値が低く、上位のサブワードには波高値の高いPWM波形を割り当てることによって従来のPWM波形のタイムスロットの期間より長い期間を有する駆動波形を実現し、低輝度における画像の表示品位の低下を防止している。

【0029】

また、特開平10−39825号公報では、輝度信号に応じて高電圧がV1で低電圧がV2である2値信号を出力する第2のパルス幅変調出力手段と、前記輝度信号に応じて前記2値信号を所定のパルス幅で切り込む第2のパルス幅信号出力手段を有する駆動方法によってパルス幅変調回路の周波数の低減を可能とし、高階調化に伴って問題となるPWM動作周波数の高周波化の問題を解決している。

【0030】

さらに、特開平11−015430号公報では、電圧パルスとして、M階調に対応するパルス幅制御とN階調に対応するパルス波高値制御とで定義されるM×N階調の情報を含ませたパルス駆動波形を用いることによって高階調化を容易に実現している。

【0031】

しかしながら、従来のパルス幅変調による駆動ではさらに、階調によっては駆動波形の立ち上がり立ち下がり時に大きな電磁波ノイズすなわち電磁波の不要輻射が誘起される可能性があった。

【0032】

また、上述した電子放出素子を多数個、マトリクス配置したマルチ電子ビーム源においては、その配線の抵抗分の影響によって生じる電圧降下のために、各素子に印加される電圧はその給電端から遠い素子ほど小さくなり、その結果、各素子の放出電子分布が一様にならないという問題がある。そして、このマルチ電子放出素子を画像表示装置に応用した場合は、配線抵抗によって生じる電圧降下のために、画質が劣化する問題がある。

【0033】

図34および図35を用いて説明する。図34はマルチ電子ビーム源基板の一例を示す。図中、1は電子放出素子、2は選択電極(行方向配線)、3は情報電極(列方向配線)、9は選択回路、10は変調回路、12は基板を表している。

【0034】

また、図35は図34のマルチ電子ビーム源基板11を用いた画像表示パネルの斜視図である。図中、13はメタルバック、14は蛍光面、15はフェースプレート、16は電子源からの電流を表している。

【0035】

今、ある選択電極2が選択され、その選択電極に接続されている画素の全てが点灯したとする。この時の等価回路を図36に示す。図中、16は情報電極から電子放出素子を通じ、選択電極に流れる電流成分、4は選択電極の抵抗成分を表している。

【0036】

ここで選択電極に流れ込む電流は各素子とも、同一の値Ifとし、一画素あたりの選択電極の抵抗値をrfと仮定する。この時の選択電極上での電位を計算する。

【0037】

Rf5に流れる電流はIfであり、Rf5による電圧降下分は、If・rfである。Rf4に流れる電流は2・Ifであり、Rf4による電圧降下分は、2・If・rfである。以下同様に各抵抗成分での電圧降下分を計算し、選択電極上の各部の電位を計算した結果を図37に示す。なお、ここではVe>Vsとした場合について示した。

【0038】

注目すべき点は、給電点である選択回路9から電位Vsを出力した時、選択電極2に電流が流れ込み、給電点から離れるにつれて電位が上昇し、最遠方端では21・If・rfだけ電位上昇している点である。図38は、このときの最遠方端の画素に印加される駆動波形を示したものである。図中(a)は選択電極に印加される電位波形、(b)は情報電極に印加される電位波形、(c)は選択された電子放出素子に印加される電圧波形を示している。電位上昇によって、選択電位がVsからVs’となることで、素子に印加される電圧が低下することがわかる。

【0039】

この電圧のばらつきは、選択電極の抵抗成分がきわめて小さい場合にはさほど問題とならないが、例えば、画像表示装置の大画面化等により、選択電極の抵抗成分が大きい場合、その電圧ばらつきは無視できないものとなる。また画素数が増大し、選択電極に流れ込む電流が増大した場合もその電圧ばらつきは大きくなる。

【0040】

この電圧ばらつきが生じることによって、電子放出素子に印加される電圧が各素子で異なることになり、とりわけ、給電点に近い電子放出素子と給電点から離れた電子放出素子とでは、同じ電圧が印加されず、電子の放出量に差異が生じる。このことは、その電子放出素子から放出される電子ビームにより発光する素子である画素間の輝度差として表れてしまい、画像表示装置としての表示品位が低下してしまうことにつながる。

【0041】

特開平10−112391号公報には、X−Yマトリクス型有機EL表示装置の配線電極の抵抗値と当該配線電極に流れる電流に注目し、データ電極を低抵抗側配線に、走査電極を高抵抗側配線に配設するようにするとともに、駆動電圧Vccの電圧源に接続された電流源で駆動する駆動方法とし、この時の駆動電圧Vccを画素である発光素子の位置による配線抵抗のばらつきがあっても電流源が必ず定電流動作する条件を満足する特定の電圧以上とすることによって、多数の発光素子を均一に発光させ、画像表示装置として優れた特性を実現することが開示されている。

【0042】

また、特許第3049061号には、変調配線(情報信号配線)に印加する信号の立ち下がりを複数のステップに分けて行うことが記載されている。

また、特開平7−181917号公報には、単数または複数個の単位駆動ブロックに対応する複数個の電圧を用い、この単位駆動ブロックをパルス幅および波高値方向に積み重ねて、駆動波形を作成する方法が記載されている。

【0043】

本願に係る発明は、発光素子を駆動する信号の駆動波形として好適なものを実現することを課題とし、特には、発光素子を正確に駆動できる駆動波形を実現することを課題とする。

【0047】

【課題を解決するための手段】

本願にかかわる発光素子の駆動回路の発明の一つは以下のように構成される。

スロット幅Δt単位でパルス幅制御されかつ各スロットにおける波高値がA 1〜Anのn段階(但し、nは2以上の整数で、0<A1<A2<・・・・<An でありA 1 は0でない階調データに対応する波高値)のいずれかの波高値に制御される駆動波形を1選択期間中に発光素子に供給する駆動回路であって、前記駆動波形は、波高値が波高値A1から波高値Ak−1までの波高値に制御される部分を少なくとも1スロットずつ経て所定波高値Ak(但し、kは2以上n以下の整数)に制御される部分まで立ち上がる部分と、波高値が前記所定波高値Ak に制御されている部分から、波高値が前記波高値Ak−1から波高値A1までの波高値に制御される部分を少なくとも1スロットずつ経て立ち下がる部分を有することを特徴とする発光素子の駆動回路。

この発明によれば駆動波形を段階的に立ち上げ、かつ立ち下げることで発光素子を正確に駆動することが可能となる。なお、駆動波形の立ち上がり部分に波高値Akよりも高い波高値まで立ち上がる部分を有している場合、波高値Akに達した後駆動波形を急激に立ち上げるのは好ましくない。よって上記発明において、波高値Akは駆動波形の(少なくとも立ち上がり部分の)最大波高値であることが望ましい。

【0048】

なお以上述べた各発明において、駆動波形の立ち上がり部分で波高値A1に立ち上がる直前の波高値は発光素子が実質的に駆動されない波高値であればよい。また駆動波形の立ち下がり部分で波高値A1から立ち下がった直後の波高値は発光素子が実質的に駆動されない波高値であればよい。ここで、発光素子が実質的に駆動されない波高値とは、該波高値が1スロット入力されても発光素子が輝度データの最低階調に対応する発光を生じさせない波高値であり、具体的には該波高値が発光素子の駆動しきい値を越えないように選ばれる。

【0049】

発光素子に基礎電位(例えば後述するマトリクス駆動の際の選択電位)が与えられた状態を考える。この発光素子に本願に係る発明による駆動波形が与えられると、駆動波形の各部分に対応する電位(波高値制御を電位制御により行う場合はその電位、波高値制御を電流制御により行う場合は該電流を流すための電位)と前記基礎電位との電位差が発光素子に与えられる。この電位差により輝度データに応じた表示に際して無視できない発光を生じたときの波高値が発光素子の駆動しきい値である。

【0050】

なお、この駆動波形がA1に立ち上がる前の発光素子が実質的に駆動されない波高値と、A1から立ち下がった後の発光素子が実質的に駆動されない波高値とは、同じ値である構成を好適に採用できる。またここで波高値の大小(高低)をいうとき、より大きい(高い)波高値とはより多くの駆動エネルギーを発光素子に与える波高値であることを指し、必ずしも電位の大小関係と一致するものではない。例えば、基礎電位として所定電位を与え、駆動波形の電位をそれよりも低い電位とするときには、電位が低いほうが波高値が高い状態となる。

【0051】

また、以上の構成において、ある駆動波形と、該駆動波形が発光素子を駆動する駆動エネルギーを増減させた他の駆動波形の関係を以下のように規定することにより、駆動波形を好適に設定することが可能となる。すなわち、前記駆動波形が波高値A1に立ち上がったスロットを第1スロットとするとき、第1〜第k−1スロットの波高値がそれぞれA1〜Ak-1、第kと第Nk+k−1スロット(但し、Nkは1以上の整数)の波高値がAk、第Nk+k〜第Nk+2(k−1)スロットの波高値がそれぞれAk-1〜A1となる駆動波形に対し、前記発光素子を駆動する駆動エネルギーを1段階増加させた駆動波形が、前記駆動波形の第Nk+2k−1スロットの波高値をA1に増加させたものであり、以降順次前記駆動エネルギーを1段階増加させた駆動波形が前段階の駆動波形に対して、さらに第Nk+2(k−1)スロットの波高値をA1からA2に、‥‥、第Nk+kスロットの波高値をAk-1からAkに変更した波形を有するようにすることである。

【0052】

すなわち波高値Akから波高値Akより低い各波高値を順番に1スロットずつ経て前記発光素子が実質的に駆動されない波高値まで立ち下がる部分を有する駆動波形に対して、前記発光素子を駆動するエネルギーを一段階増加した駆動波形が、前段の駆動波形の前記立ち下がる部分において波高値がA1であったスロットに続くスロットの波高値をA1に増加させた波形を有しており、以降前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有するとよい。

【0053】

なおここで述べる発明は駆動信号の波形を規定するものであり、ある階調エネルギーに相当する第1の駆動波形に対し、1段階駆動エネルギーを増加させたときの第2の駆動波形がこの発明に従うものである時に、ある所定期間における第1および第2の駆動波形の印加のタイミングを限定するものではなく、例えば第1の駆動波形を用いるときに所定期間の2番目のスロットから第1の駆動波形を立ち上げる構成において、第2の駆動波形を用いる場合に、第2の駆動波形を前記所定期間の最初のスロットから立ち上げる実施形態を含む発明である。すなわち、この発明の実施の形態は、第1の駆動波形の立ち上がりのタイミングと第2の駆動波形の立ち上がりのタイミングがある所定期間(例えば後述のようにマトリクス駆動する際の1選択期間)において同じである構成に限らない。

【0054】

また以上述べた各発明において以下のようにしてもよい。すなわち、波高値Akから波高値Akより低い各波高値を順番に少なくとも1スロットずつ経て立ち下がる部分を有する所定の駆動波形に対して、前記発光素子を駆動するエネルギーを一段階増加した駆動波形が、前段の駆動波形の前記立ち下がる部分において波高値がA1であったスロットに続くスロットの波高値をA1に増加させた波形を有しており、以降前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有することを特徴とする駆動方法である。

このように各駆動波形の関係を設定することにより各駆動波形の立ち下がり部分で連続するスロットにおいて波高値の変化を1段階以内にすることができる。

【0055】

特に、前段の駆動波形に対して前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有するという前記関係は、該関係によって決まる駆動波形が前段の駆動波形に対して波高値を増加させたスロットの波高値が波高値Akよりも一段階高い波高値である駆動波形までの一連の駆動波形が満たすものである構成を好適に採用することができる。これらの一連の駆動波形の最後の駆動波形に対して更に一段階駆動エネルギーを増加させた駆動波形は、前記最後の駆動波形の立ち下がり部分において波高値が波高値がA1であったスロットに続くスロットの波高値をA1に変更した波形を有するようにすればよい。

【0056】

また、波高値Akが許容される最高波高値であったり、波高値の更新をなるべく回避したい場合には、以下のようにすればよい。すなわち、

前段の駆動波形に対して前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有するという前記関係は、該関係によって決まる駆動波形が前段の駆動波形に対して波高値を増加させたスロットの波高値が波高値Akである駆動波形までの一連の駆動波形が満たすものである構成である。これらの一連の駆動波形の最後の駆動波形に対して更に一段階駆動エネルギーを増加させた駆動波形は、前記最後の駆動波形の立ち下がり部分において波高値が波高値がA1であったスロットに続くスロットの波高値をA1に変更した波形を有するようにすればよい。

【0057】

また、一段階ずつ駆動エネルギーが異なる一連の駆動波形を以下のように設定しても良い。すなわち、

前記駆動波形が波高値A1に立ち上がったスロットを第1スロットとするとき、第1〜第k−1スロットの波高値がそれぞれA1〜Ak−1、第kと第Nk+k−1スロット(但し、Nkは1以上の整数)の波高値がAk、第Nk+k〜第Nk+2(k−1)スロットの波高値がそれぞれAk−1〜A1となる駆動波形に対し、前記発光素子を駆動する駆動エネルギーを1段階減少させた駆動波形が、前記駆動波形の第kスロットの波高値をAkからAk−1に変更したものであり、以降順次前記駆動エネルギーを1段階減少させた駆動波形が前段階の駆動波形に対して、さらに第k−1スロットの波高値をAk−1からAk−2に、・・・・、第1スロットの波高値をA1から輝度データの最低階調に対応する発光を生じさせない波高値に変更した波形を有する構成である。

【0058】

なおこの発明も駆動信号の波形を規定するものであり、ある階調エネルギーに相当する第1の駆動波形に対し、1段階駆動エネルギーを減少させたときの第2の駆動波形がこの発明に従うものである時に、ある所定期間における第1および第2の駆動波形の印加のタイミングを限定するものではなく、例えば第1の駆動波形を用いるときに所定期間の最初のスロットから第1の駆動波形を立ち上げる構成において、第2の駆動波形を用いる場合に、第2の駆動波形を前記所定期間の2番目のスロットから立ち上げる実施形態をも含む発明である。すなわち、この発明の実施の形態は、第1の駆動波形の立ち下がりのタイミングと第2の駆動波形の立ち下がりのタイミングがある所定期間(例えば後述のようにマトリクス駆動する際の1選択期間)において同じである構成に限らない。

【0059】

また、以下のようにいうこともできる。すなわち、

波高値Akより低い各波高値を順番に少なくとも1スロットずつ経て波高値Akまで立ち上がる部分を有する駆動波形に対して、前記発光素子を駆動するエネルギーを一段階減少した駆動波形が、前段の駆動波形の前記立ち上がる部分において波高値がAk-1であったスロットに続くスロットであり波高値がAkであったスロットの波高値をAk-1とした波形を有しており、以降前記発光素子を駆動するエネルギーを一段階ずつ減少した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階減少させたスロットの一つ手前のスロットの波高値を一段階減少させた波形を有することを特徴とする構成である。

【0060】

以上述べた各発明において、波高値がAkである2つのスロットの間のスロットにおける波高値はAkであると好適である。立ち上がり部と立ち下がり部以外では波高値を維持できるため、発光素子をより正確に駆動でき、また駆動波形の生成も容易になる。

【0061】

また、以下のように設定するのも好適である。すなわち、

前記波高値がAkである2つのスロットの間に他のスロットがある時には、該他のスロットにおける波高値はAkとするものであり、k=1の場合を含み前記波高値AkがAnよりも小さく、かつ前段階の駆動波形に対して駆動エネルギーを一段階増加させることにより波高値がAkであるスロットの数が2個から3個になった駆動波形に対して、駆動エネルギーを更に一段階増加させた駆動波形は、前記駆動波形の波高値がAkである3個のスロットのうちの真中のスロットの波高値をAkからAk+1に変更した形状を有することを特徴とする構成である。

【0062】

また、所定の駆動波形よりも前記発光素子を駆動する駆動エネルギーを増加させた駆動波形は、前記所定の駆動波形に対して最大波高値を上昇させるよりもパルス幅を増加させることを優先させた形状を有するようにすることも好適である。

【0063】

駆動エネルギーを増加させる際に、波高値の上昇よりもパルス幅の増加を優先することにより、瞬間的に流れる電流を減らす作用が期待できる。ここで波高値の上昇よりもパルス幅の増加を優先する場合の好適な構成は、少なくとも1スロットずつ各波高値を経ながら立ち上がる、もしくは立ち下がる形状を維持しつつ、いずれかの波高値のパルス幅を伸ばすことによって駆動エネルギーを増加させられる場合は、最大波高値を上昇させない構成となる。

【0064】

また以下のように設定することも好適である。すなわち、

所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを一段階増加して駆動波形の最大波高値を高くしたときの駆動波形は、波高値差An−An-1、‥‥、もしくはA2−A1または波高値A1と前記発光素子の駆動しきい値となる波高値との波高値差、およびスロット幅Δtとで定まる単位駆動波形ブロックの数を前記所定の駆動波形で用いた数よりも一つ増加させて、最大波高値がなるべく連続するように積み直した形状を有する構成である。

【0065】

駆動エネルギーを増加させる際に、波高値の上昇よりもパルス幅の増加を優先することにより、瞬間的に流れる電流を減らす作用が期待できる。ただし、駆動エネルギーを増加させるためにパルス幅を増やしていく構成においても、駆動波形のパルス幅の制限がある場合所定の段階でより高い波高値を使う必要がでてくる。波高値、特には最大波高値の連続性を重視する場合は、階段状の立ち上がりもしくは階段状の立ち下がりもしくはその両方を充足する範囲において最大波高値がなるべく連続するように駆動波形を構成する単位駆動波形ブロックを積み直した形状にすると良い。

【0066】

また以下のように設定することも好適である。すなわち、

所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを増加した駆動波形は、波高値差An−An-1、‥‥、もしくはA2−A1または波高値A1と前記発光素子の駆動しきい値となる波高値との波高値差、およびスロット幅Δtとで定まる単位駆動波形ブロックを、k=1を含む最大波高値Akがより低くなる位置に優先的に付加した形状を有する構成である。特に、所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを増加した駆動波形は、波高値差An−An-1、‥‥、もしくはA2−A1または波高値A1と前記発光素子の駆動しきい値となる波高値との波高値差、およびスロット幅Δtとで定まる単位駆動波形ブロックを、最大波高値がより低くかつ最大波高値が連続する位置に優先的に付加した形状を有する構成を好適に採用できる。

【0067】

具体的には、最大スロット数をSとして、最大波高値Akであるスロット数がS−2(k−1)になった駆動波形に対し、前記単位駆動波形ブロックを付加することによって前記駆動エネルギーをさらに1段階増加させた駆動波形は、第k+1〜第S−kスロットのうち任意のスロットの波高値をAkからAk+1に変更した形状を有する駆動波形である。波高値をAkからAk+1に変更するスロットは、例えば第k+1または第S−kスロットのいずれかとするとよい。

【0068】

なお、本発明は、所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを一段階増加して駆動波形の最大波高値を高くしたときの駆動波形として、前記単位駆動波形ブロックの数を前記所定の駆動波形で用いた数よりも一つ増加させて、最大波高値がなるべく連続するように積み直した形状を有する構成と、前記単位駆動波形ブロックを、k=1を含む最大波高値Akがより低くなる位置に優先的に付加した形状を有する構成との中間の構成をも含んでいる。すなわち、所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを一段階増加して駆動波形の最大波高値を高くしたときの駆動波形は、前記単位駆動波形ブロックの数を前記所定の駆動波形で用いた数よりも一つ増加させて、最大波高値が2スロット以上連続するように積み直した形状を有する構成である。

【0069】

さらに、本発明は、2スロット以上の最大波高値が連続しない構成も含んでいる。すなわち、所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを一段階増加して駆動波形の最大波高値を高くしたときの駆動波形は、前記単位駆動波形ブロックの数を前記所定の駆動波形で用いた数よりも一つ増加させて、最大波高値が2スロット以上となるように積み直した形状を有する構成である。

【0070】

以上の各発明において、波高値がA1でスロット幅がΔtの駆動波形は、前記発光素子を輝度データの概ね1LSBに対応する輝度で発光させる駆動エネルギーを有するようにすると好適である。

【0071】

また、前記波高値A1〜Anはそれぞれ異なる電位の値である構成を好適に採用でき、例えば、前記波高値A1〜Anは前記発光素子の輝度が概ね1:2:‥‥:nとなる電位である構成を採用できる。また、前記波高値A1〜Anは波高値差Am−Am-1(但し、mは1以上n以下の整数、A0は発光素子の駆動しきい値)が概ね一定となる電位である構成を採用できる。また、前記波高値A1〜Anはそれぞれ異なる電流値である構成も採用できる。

【0072】

また、波高値差Am−Am−1(但し、mは1以上n以下の整数、A0は発光素子の駆動しきい値)が概ね一定であるか、または2以上のmに対してAm−Am−1≧Am−1−Am−2であり、k=1の場合を含み前記波高値Akが駆動波形の最大波高値になっておりかつ前記波高値AkがAnより小さく、かつ前記波高値がAkであるスロットに挟まれるスロットの波高値はAkであり、かつ前記Nk+2(k−1)が所定の最大スロット数S(但し、Sは2n−1以上の整数)に達した駆動波形に対し、前記駆動エネルギーをさらに1段階増加させる場合、波高値がA1になっているスロットに隣接しておりかつ波高値が前記発光素子が実質的に駆動されない波高値になっているスロットの波高値をA1に変更する代わりに、波高値がA1よりも高いスロットの数が(S・k+2k+1)/(k+1)以上のこれに最も近い整数であり、最大波高値がAk+1であり、前記波高値差Am−Am−1とスロット幅Δtとで定まる単位駆動波形ブロックの数が前記駆動波形に対して1個だけ多く、かつ本願にかかわる駆動回路において前述した駆動波形に変更し、波高値がA1〜Akのいずれかであり同一であるスロットが複数個ある場合は、以後さらに前記駆動エネルギーを1段階増加させるときに、波高値がより小さく、波高値が1段階上であるスロットにより近いスロットの波高値を1段階大きくすることを特徴とする構成を採用できる。

【0073】

この構成において、前記波高値A1〜Anは前記発光素子の輝度が概ね1:2:‥‥:nとなる電位である構成や、前記波高値A1〜Anは波高値差Am−Am-1(但し、mは1以上n以下の整数、A0は発光素子の駆動しきい値)が概ね一定な電位である構成を採用できる。また、前記波高値A1〜Anは波高値が概ね1:2:‥‥:nとなる電流値である構成を採用できる。

【0074】

また本願は以下の発明を含んでいる。すなわち、

階調データに対応する駆動波形を発生する駆動回路であって、

0でない前記階調データに対応する波高値である最小の波高値とより大きい前記階調データに対応する波高値である1つ以上の非最小の波高値とを含む不連続な複数の波高値に波高値が制御される駆動波形を1選択期間中に発生するものであり、

前記非最小の波高値に制御される部分を有する前記駆動波形が、前記最小の波高値に制御される部分を該駆動波形の先頭および末尾に有するものであることを特徴とする駆動回路である。

【0075】

ここで、0でない輝度階調データに対応する波高値とは、該波高値に制御した駆動波形を発光素子に印加することにより0以外の輝度階調データに対応する発光を生じさせることができる波高値を言う。

【0085】

以上述べた各発明において、前記発光素子が、マトリクスディスプレイを構成する複数個の発光素子であり、各発光素子にそれぞれの階調データに応じた前記駆動波形を印加する構成を好適に採用できる。

【0086】

また本願は、表示装置の発明として以下の構成の発明を含んでいる。

複数の発光素子を走査信号配線と情報信号配線とを用いてマトリクス配線したマルチ発光素子と、前記走査信号配線に接続された走査回路と、前記情報信号配線に接続された変調回路とを有する表示装置において、

前記変調回路は、前記走査回路により選択された発光素子を上述の各発明の駆動方法を用いて駆動するものであることを特徴とする表示装置。

【0087】

具体的には、走査回路が各走査信号配線を順次選択し、選択した走査信号配線に所定の基礎電位として選択電位を与え、該選択された走査信号配線に接続される複数の発光素子にそれらが接続される複数の情報信号配線を介して上述の駆動波形を有する信号が与えられるようにすればよい。

【0088】

この構成において、前記駆動波形の立ち上がり開始時から最大波高値Akに達するまでの時間が前記マルチ発光素子の情報信号配線の負荷と前記駆動回路の駆動能力とで決定される0%〜90%時定数に概ね等しいかそれより長くなるように設定すると好適である。

【0089】

0%〜90%時定数とは、駆動波形を配線に供給する部分において測定できるものであり、駆動波形を所望の電位まで立ち上げるときに該部分における電位が変化し始めてから所望電位までの電位差の0.9倍の電位に達するまでに要する時間をいう。0%〜90%時定数に概ね等しいかそれより長いよりも長い時間で駆動波形を立ち上げることによって電子源の両端に印加すべき電圧の90%以上の電圧を印加することが可能となり、所望の発光量の90%以上の輝度を得ることが可能となる。

【0090】

また複数の情報信号配線に流れる同時に流れる電流を分散できる構成として、前記複数の情報信号配線の一部の情報信号配線に印加する駆動波形は、立ち上がりが選択期間の前半になるように制御し、他の一部の情報信号配線に印加する駆動波形は、立ち下がりが選択期間の後半になるように制御する構成を好適に採用できる。一つの選択期間においては、パルス幅制御のためのスロットが複数設定される。具体的には、複数の情報信号配線の一部の情報信号配線に印加する駆動波形は、対応する駆動エネルギー(階調)によらず選択期間におけるパルス幅制御のための最初(もしくはその近傍)のスロットから立ち上がるように印加し、残りの情報信号配線に印加する駆動波形は、対応する駆動エネルギーによらず選択期間におけるパルス幅制御のための最後(もしくはその近傍)のスロットで立ち下がるように印加することによって、複数の情報信号配線に同時に流れる電流を分散することができる。特には、印加される駆動波形の立ち上がりタイミングが選択期間の前半に設定される情報信号配線と、印加される駆動波形の立ち下がりのタイミングが選択期間の後半に設定される情報信号配線とが交互に配置されるようにすると好適である。またこのとき、前記駆動波形の時間軸を前記複数の情報信号配線の一部と残部とで逆にする構成を好適に採用できる。

【0091】

また、上記構成において、前記変調回路は、画像データとしてRビットの輝度データを入力され、スロット数2P個以下の範囲で前記パルス幅制御を行い、かつn=2Q段階の波高値制御とを行うものであり、前記R、P、Qの各データがR<P+Qなる関係を有するようにすると好適である。

【0093】

なお、本発明で言う発光素子としては、LEDやELや、電子放出素子を挙げることができる。電子放出素子はそれ単体では発光するものではないが、放出される電子により発光する蛍光体を用いることにより発光素子として用いることができる。なお、電子放出素子としては冷陰極素子が好適である。電界放出(FE)型電子放出素子、MIM型電子放出素子を好適に用いることができる。特に好適には表面伝導型放出素子(SCE)を用いることができる。表面伝導型放出素子は電子放出特性のばらつきが少ない多数の素子を比較的容易に製作できるので好ましい。

【0094】

なお、以上述べた各発明はそれぞれ他の発明と組み合わせて用いることができる。

【0095】

【作用】

本発明の駆動方法によれば、パルス幅制御とパルス波高値制御を併用することにより、パルス波高値制御の波高値の分解能すなわち最小波高値差を実現容易な値に設定することができる。また、パルス幅制御の分解能すなわちスロット幅をより大きくして駆動信号の最大周波数および最大波高値を下げることができる。特に、駆動波形を階段状に立ち上げまたは立ち下げることにより、立ち上がりもしくは立ち下がり部分の波高値の急激な変化を抑制することができる。これにより、例えば不要輻射を低減することができる。また駆動波形のなまりを低減して特に低階調での階調特性の劣化を防ぐことができる。またオーバーシュート、リンギングの発生や、それによる発光素子への異常電圧の印加を防止することができる。

【0096】

【発明の実施の形態】

本発明の好ましい実施の形態の一つにおいて、駆動波形の駆動エネルギーを1段階増加させて波高値が最大波高値Akであるスロットの数がNk−1個からNk個(但し、Nkは1以上の整数)になったときの駆動波形は、該波形が波高値A1に立ち上がるスロットを第1スロットとして、第1〜第k−1スロットの波高値がそれぞれA1〜Ak-1、第k〜第Nk+k−1スロットの波高値がAk、第Nk+k〜第Nk+2(k−1)スロットの波高値がそれぞれAk-1〜A1、とする。それ以外のスロットの波高値は素子が実質的に駆動されない値にする。そして、これに対し、駆動エネルギーが1段階多い駆動波形は、第Nk+2k−1スロットの波高値を素子が実質的に駆動されない値からA1に変更したものであり、以後、第Nk+2(k−1)スロットの波高値をA1からA2に、‥‥、第Nk+kスロットの波高値をAk-1からAkに変更することにより前記駆動エネルギーを1段階ずつ増加した駆動波形を形成することができる。

なおこの波形設定の仕方は前後を逆転させても良い。

【0097】

最大波高値を繰り上げるには、例えば、k=1の場合を含み前記最大波高値AkがAnより小さく、かつ波高値が最大波高値Akであるスロットの数が2個から3個になった駆動波形に対し、前記駆動エネルギーをさらに1段階増加させる場合、前記第Nk+2k−1スロットの波高値を0からA1に変更する代わりに、第k+1スロットの波高値をAkからAk+1に変更する。

【0098】

すなわち、前段階の駆動波形に対して駆動エネルギーを一段階増加させることにより波高値がAkであるスロットの数が2個から3個になった駆動波形に対して、駆動エネルギーを更に一段階増加させた駆動波形は、前記駆動波形の波高値がAkである3個のスロットのうちの真中のスロットの波高値をAkからAk+1に変更した形状とする。またこれは、前段階の駆動波形に対して駆動エネルギーを一段階増加させることにより波高値がAkであるスロットの数が3個から4個になった駆動波形に対して、駆動エネルギーを更に一段階増加させた駆動波形は、前記駆動波形の波高値がAkである4個のスロットのうちの両端の2つ以外のスロットの波高値をAkからAk+1に変更した形状としてもよい。このような駆動波形列を用いる駆動方法を以下「V14駆動」という。

【0099】

または、k=1の場合を含み前記最大波高値AkがAnより小さく、かつ前記Nk+2(k−1)が所定の最大スロット数S(但し、Sは2n-1以上の整数)に達した駆動波形に対し、前記駆動エネルギーをさらに1段階増加させる場合、前記第Nk+2k−1スロットの波高値を素子が実質的に駆動されない波高値からA1に変更する代わりに、パルス幅が(S・k+2k+1)/(k+1)以上のこれに最も近いスロット数であり、最大波高値がAk+1であり、かつ前記単位駆動波形ブロックの数が該駆動波形に対して1個だけ多い階段状立ち上がりおよび立ち下がりを呈する駆動波形に変更する。そして、波高値がA1〜Akのいずれかであり同一であるスロットが複数個ある場合は、以後さらに前記駆動エネルギーを1段階増加させるときに、波高値がより小さく、波高値が1段階上であるスロットにより近いスロットの波高値を1段階大きくする。

【0100】

このような駆動波形列を用いる駆動方法を以下「Vn駆動」という。このVn駆動においては、最大波高値を繰り上げた場合の単調増加性を保つため、波高値および波高値差はAn−An-1≧‥‥≧A2−A1≧A1であるか、概ね一定であることが好ましく、特に、An−An-1=‥‥=A2−A1=A1であることが好ましい。また、波高値差An−An-1、‥‥、もしくはA2−A1または波高値A1と素子の駆動しきい値となる波高値との波高値差およびスロット幅Δtとで定まる単位駆動波形ブロックがそれぞれ前記発光素子を輝度データの概ね1LSBに対応する輝度(最低階調に対応する輝度)で発光させる駆動エネルギーを有することが好ましい。

【0101】

最大波高値を繰り上げるさらに別の方法は、波高値差An−An-1、‥‥、もしくはA2−A1または波高値A1と素子の駆動しきい値となる波高値との波高値差およびスロット幅Δtとで定まる単位駆動波形ブロックを、k=1を含む最大波高値Akがより低くかつ最大波高値が連続する位置に優先的に付加することによって、前記駆動波形を形成し、最大スロット数をSとして最大波高値Akとなっているスロット数がS−2(k−1)になった駆動波形に対し、前記駆動エネルギーをさらに1段階増加させる場合、第k+1〜第S−kスロットのうち任意のスロット、好ましくは前記範囲の先頭または末尾のスロットの波高値をAkからAk+1に変更する。このような駆動波形列を用いる駆動方法を以下「新Vn駆動」という。

【0102】

【実施例】

以下、本発明の実施例を説明する。

[第1の実施例]

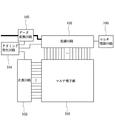

図1は本発明の一実施例に係るマルチ電子源の駆動回路のブロック図を示す。同図において、101はマルチ電子源、102は変調回路、103は走査回路、104はタイミング発生回路、105はデータ変換回路、106はマルチ電源回路である。本構成により、マルチ電子源101を駆動する。マルチ電子源101は、図34に示すように行方向配線2と列方向配線3の交点に電子源(電子放出素子)1が構成されたものである。電子源としては、前述のようにSCE型、FE型およびMIM型の電子放出素子が知られているが、本実施例では、SCE型の電子放出素子を用いた。

【0103】

データ変換回路105は、外部からマルチ電子源101を駆動する駆動データを変調回路102に適したフォーマットに変換する回路である。変調回路102はマルチ電子源101の列方向配線に接続されており、データ変換回路105からのデータ変換された駆動データに応じてマルチ電子源101に変調信号を入力する回路である。走査回路103はマルチ電子源101の行方向配線に接続されており、変調回路102の出力をマルチ電子源101のどの行に信号を加えるかを選択する回路である。一般的には、一行ずつ順次行選択する線順次走査を行うが、これに限定されることなく、複数の行を選択しても面を選択しても構わない。タイミング発生回路104は、変調回路102、走査回路103およびデータ変換回路104の各回路のタイミング信号を発生する回路である。マルチ電源回路106は、複数の電源値を出力する電源回路であり、変調回路102の出力値を制御する回路である。一般的には、電圧源回路であるが、これに限定されるものではない。

【0104】

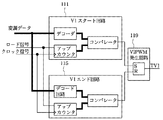

次に図2のブロック図により、変調回路102の詳しい説明をする。図2は、変調回路102の内部構成を現したブロック図である。変調回路102は、シフトレジスタ107、PWM回路108および出力段回路109で構成される。シフトレジスタ107には駆動データをデータ変換回路105でフォーマット変換された変調データが入力され、シフトレジスタ107によりマルチ電子源101の列方向配線に応じた変調データが転送される。出力段回路109はマルチ電源回路106に接続され、本発明に従った駆動波形を出力する回路である。PWM回路108はシフトレジスタ107からマルチ電子源101の列方向配線に応じた変調データが入力され、出力段回路106のそれぞれの出力電圧に応じたパルス幅出力を発生する回路である。また、シフトレジスタ107およびPWM回路108の制御のためのタイミング信号がタイミング発生回路104から入力される。

【0105】

さらに、図3のブロック図により、PWM回路108の詳しい説明をする。図3は、PWM回路108の内部構成を現したブロック図である。ここでは4段の電圧出力段回路の場合を例に説明を行うが、これに限定されるものではない。PWM回路108は、ラッチ110、V1スタート回路111、V2スタート回路112、V3スタート回路113、V4スタート回路114、V1エンド回路115、V2エンド回路116、V3エンド回路117、V4エンド回路118、V1PWM発生回路119、V2PWM発生回路120、V3PWM発生回路121およびV4PWM発生回路122で構成される。ラッチ回路110では、各シフトレジスタ107から出力された各変調データをタイミング発生回路104から出力されたロード信号に応じてラッチする。ここで、タイミング発生回路104から出力されたロード信号は各PWM信号のスタートのタイミング信号にも用いている。

【0106】

ラッチ回路110でラッチされた変調データは、さらに、V1からV4のスタート回路111〜114と、V1からV4のエンド回路115〜118に入力される。次に、V1スタート回路111から出力されたスタート信号とV1エンド回路115から出力されたエンド信号がV1PWM回路119に入力され、出力電圧V1に対応するPWM出力が出力段回路109に入力される。同様に、V2スタート回路112から出力されたスタート信号とV2エンド回路116から出力されたエンド信号がV2PWM回路120に入力されて出力電圧V2に対応するPWM出力が出力段回路109に入力され、V3スタート回路113から出力されたスタート信号とV3エンド回路117から出力されたエンド信号がV3PWM回路121に入力されて出力電圧V3に対応するPWM出力が出力段回路109に入力され、V4スタート回路114から出力されたスタート信号とV4エンド回路118から出力されたエンド信号がV4PWM回路122に入力されて出力電圧V4に対応するPWM出力が出力段回路109に入力される。

【0107】

ここでは、本発明に従った駆動波形を作成するために、V1スタート回路111から出力されたスタート信号よりもV2スタート回路112から出力されたスタート信号が、V2スタート回路112から出力されたスタート信号よりもV3スタート回路113から出力されたスタート信号が、V3スタート回路113から出力されたスタート信号よりもV4スタート回路114から出力されたスタート信号が遅いタイミングで出力される。さらに、V4エンド回路118から出力されたエンド信号よりもV3エンド回路117から出力されたエンド信号が、V3エンド回路117から出力されたエンド信号よりもV2エンド回路116から出力されたエンド信号が、V2エンド回路116から出力されたエンド信号よりもV1エンド回路115から出力されたエンド信号が遅いタイミングで出力される。

【0108】

次に、V1〜V4スタート回路111〜114とV4〜V1エンド回路115〜118とV1〜V4PWM回路119〜122の詳細な説明を行う。図4に第1の回路例を、図5に第2の回路例を挙げ説明する。

【0109】

図4はマルチ電子源101の複数の変調信号配線への出力波形の立ち上がりがほぼ同時になるように揃える場合の回路構成を示した図である。ここでは、V1スタート回路111、V1エンド回路115およびV1PWM発生回路119のみを示しているが、他のスタート回路、エンド回路およびPWM発生回路は上記回路と同じ構成である。

【0110】

V1スタート回路111は、デコード回路とアップカウンタとコンパレータで構成され、V1エンド回路115は、デコード回路とアップカウンタとコンパレータで構成され、V1PWM発生回路119はRSフリップフロップで構成されている。

【0111】

V1スタート回路111内のデコード回路において変調データに含まれる制御信号によりデコードされたデータが出力される。V1スタート回路111内のデコード回路の出力値とV1スタート回路111内のアップカウンタとの出力が一致した場合に、V1スタート回路111内のコンパレータからV1スタート信号が出力される。変調データの各階調値ごと信号波形は決まるので、変調データの階調値に対応したデータを出力できるようにデコード回路は設定されている。ここで0でない階調値に対応する波高値のうちの最小波高値であるV1は変調データの階調値が0以外のときに用いるので、変調データの階調値が0以外の時には、アップカウンタの出力値との比較によってV1出力の開始を規定するスタート信号が発生されるような出力を出力するようにデコード回路は構成されている。変調データの階調値に対応する信号波形において、V2、V3、V4が必要か否かも各階調値ごとに決まっているので、V2、V3、V4のスタート回路においてもアップカウンタの出力と比較されるデータをデコード回路が変調データの階調値に応じて出力する。一方V1エンド回路111内のデコード回路において変調データに含まれる制御信号によりデコードされたデータが出力される。変調データの階調値によってV1出力を終了するタイミングが決まるので、階調値に応じた出力をデコード回路が出力する。V2、V3、V4のスタート回路においても同様である。V1エンド回路111内のデコード回路の出力値とV1エンド回路111内のアップカウンタの出力が一致した場合に、V1エンド回路111内のコンパレータからV1エンド信号が出力される。

【0112】

以上のスタート信号とエンド信号がV1PWM発生回路119に入力されることにより、V1出力に対応するPWM波形TV1が出力される。図4において、V1PWM発生回路119は、RSフリップフロップにより構成されている。このRSフリップフロップのセット端子Sにスタート信号が、リセット端子Rにエンド信号が入力されることによって、スタート信号の入力タイミングで立ち上がってエンド信号の入力タイミングで立ち下がる信号がV1PWM発生回路119のPWM波形TV1としてRSフリップフロップから出力される。なお、ここでは、V1PWM発生回路119としてRSフリップフロップを用いたが、JKフリップフロップや、他の回路でも構わない。

【0113】

次に、第2の回路例として、図5はマルチ電子源101の複数の変調信号配線への出力波形の立ち下がりがほぼ同時になるように揃える場合の回路構成を示した図である。V1スタート回路111は、デコード回路とダウンカウンタとコンパレータで構成され、V1エンド回路115は、コンスタント回路とダウンカウンタとコンパレータで構成され、V1PWM発生回路119はRSフリップフロップで構成されている。ここでは、V1スタート回路111、V1エンド回路115およびV1PWM発生回路119のみを示しているが、他のスタート回路、エンド回路およびPWM発生回路は上記回路と同じ構成である。

【0114】

V1スタート回路111内のデコード回路において変調データに含まれる制御信号によりデコードされたデータが出力される。V1スタート回路111内のデコード回路の出力値とV1スタート回路111内のダウンカウンタの出力が一致した場合に、V1スタート回路内のコンパレータからV1スタート信号が出力される。V1エンド回路111内のデコード回路において変調データに含まれる制御信号によりデコードされたデータが出力される。V1エンド回路111内のデコード回路の出力値とV1エンド回路内のダウンカウンタとの出力が一致した場合に、V1エンド回路のコンパレータからV1エンド信号が出力される。以上のスタート信号とエンド信号がV1PWM発生回路119に入力されることにより、V1出力に対応するPWM波形TV1が出力される。

【0115】

上述のPWM回路108および出力段回路109は、マルチ電子源101の各列方向配線に対応して、図4または図5のいずれかに示される回路を用いることができるが、第3の例として、列方向配線に、図4の回路と図5の回路を交互に設けることにより、立ち上がり揃えと、立ち下がり揃えを交互に行うこともできる。

【0116】

図6は、図2および図3に示す出力段回路109として列方向配線1本当たり用いられる回路の一例を示す。図6の回路において、電位V1〜V4は、0<V1<V2<V3<V4であり、それぞれPWM出力波形TV1〜TV4に対応して出力される。Q1〜Q4はオンすることによりそれぞれ電位V1〜V4を出力端子Outに出力するトランジスタまたはペアトランジスタである。PWM出力波形TV1〜TV4は、これらのうち2つ以上がHレベルであっても2個以上のトランジスタQ1〜Q4が同時にオンすることがないように、かつHレベルであるPWM出力波形TV1〜TV4に対応する電位V1〜V4のうち最大のもののみが出力端子Outに出力されるように、論理回路を介して各トランジスタQ1〜Q4のゲートGV1〜GV4に印加される。図39はTV4〜TV1およびGV4〜GV0の波形の一例を示す。

【0117】

図7はLEDや電子放出素子のような電圧/発光強度特性が非線形のしきい値特性を持つ発光素子の電圧/発光強度特性を示す。横軸が印加電圧で縦軸が発光強度を表す。発光強度の比が1:2:3:4になるように、V1、V2、V3、V4の各駆動レベル電位を設定することによって発光量の時間変化グラフ中のa、b、c、dの各領域の発光量は等価となる。つまり、V1、V2、V3、V4の各駆動レベル電位を最適に設定することによって、駆動波形の時間変化グラフ中で表される単位パルス幅Δtと単位波高値すなわち電圧差V4−V3、V3−V2、V2−V1、V1−V0で構成されるA、B、C、Dの単位駆動波形ブロックの発光量を等しくすることができる。ここでは、各単位駆動波形ブロックA〜Dの発光量が輝度データの1LSB(1階調)に概ね一致するように電位V1〜V4を定めている。

【0118】

なお、素子には基礎電位として走査信号配線により選択電位が与えられる。ここでは選択電位は−9.9[V]である。よって素子に印加される電圧は電圧降下の影響を無視して考えると、駆動信号のレベルがV1、V2、V3、V4のとき、それぞれV1−(−9.9)[V]、V2−(−9.9)[V]、V3−(−9.9)[V]、V4−(−9.9)[V]である。なお、V0−(−9.9)[V]が素子の駆動電圧しきい値以下になるようにV0を選ぶ。ここではV0をグランド電位としている。またここではこの値は素子の駆動しきい値と同じにしている。すなわち素子の駆動電圧しきい値は9.9[V]である。

【0119】

図8は階調を表現するための駆動波形の形状の一例としてV14駆動波形を示す。図8において、各階調の信号は、その階調数に応じた個数の単位駆動波形ブロックからなる。1階調は1個の単位駆動波形ブロック、2階調は2個の単位駆動波形ブロック、そしてN階調はN個の単位駆動波形ブロックからなる。図中、N階調目の白抜きの単位駆動波形ブロックはN−1階調からの差分を表す。N−1階調目の駆動波形に単位駆動ブロックを、駆動波形が連続する位置に付加することによってN階調目の駆動波形を形成する。このように駆動波形を形成することによって電圧/発光強度特性が変化した場合や、発光素子間のばらつきがあった場合にも単純増加性を保証することができる。

【0120】

本実施例においては、データビット長R=10の画像データを表示するために、P=9ビットを用いてスロット幅Δtの単位パルスを0〜259個の範囲でパルス幅制御し、残りの1ビットを含むQ=2ビットを用いて波高レベルが1〜4レベルすなわち波高値V1からV4の範囲で波高値(振幅)制御する。つまり10ビットの画像データを表示するために前記R、P、Qの各データはR<P+Qなる関係を持つ。

【0121】

R=P+Qである場合、例えば、波高値制御に上位2ビットを使い、残りの8ビットでパルス幅の制御を行うと、駆動波形の立ち下がり部を階段状にした場合には10ビットのすべての画像データを表現することができない。すなわち階調数が低下する。しかし、本実施例では、R<P+Qとなるように、パルス幅の制御を9ビットで行っており、これにより、10ビットのすべての画像データを表現することができる。

【0122】

図8に示すように、N階調目の最高駆動レベルがkのとき駆動波形の立ち上がり時に1レベル(電位V1)からkレベル(電位Vk)の駆動波形を低いレベルから高いレベルに順番にすべてのレベルを出力し、かつ各レベルの出力を単位パルス幅Δt以上保持することによって、駆動波形の立ち上がり時に流れる電流を低減することが可能となる。

【0123】

同様に駆動波形の立ち下がり時にもkレベル(電位Vk)から1レベル(電位V1)の駆動波形を高いレベルから低いレベルに順番にすべてのレベルを出力しかつ、各レベルの出力を単位パルス幅Δt以上保持することによって、駆動波形の立ち下がり時に流れる電流を低減することが可能となる。

【0124】

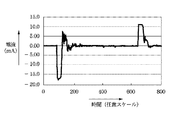

図12にマルチ発光素子の等価回路を示す。実際の駆動においては選択する行方向配線2に選択電位を印加して、列方向配線3に駆動電位を印加するが、直感的理解のためにモデルを単純化して、図13に示す単ビット列方向配線モデルを使ってシミュレーションを行った。寄生抵抗は10Ω、寄生インダクタンスは300nH、寄生容量は10pF、変調回路は4種の電源とMOSトランジスタによって形成した。

【0125】

図13の回路について図8中の9階調の駆動波形をV0=0V、V1=3V、V2=3.7V、V3=4.4V、V4=5.0Vの条件で駆動した場合のシミュレーションを行った。行方向配線末端の電圧波形を図14に、列方向配線に流れ込む電流波形を図15に示す。

【0126】

比較のためにV0=0V、V1=V2=V3=V4=5.0Vの条件で駆動した場合、つまり従来波形で駆動した場合の行方向配線末端の電圧波形を図16に、列方向配線に流れ込む電流波形を図17に示す。

【0127】

本実施例の駆動波形(図8)で駆動した場合には列方向配線に流れ込む電流が従来波形での駆動に比べて半分程度に収まっていることが分かる。その結果、従来波形で駆動した場合はオーバーシュート電圧は2V程度も発生しているのに比べ本実施例の駆動波形で駆動し場合にはオーバーシュート電圧は0.8V程度に収まっている。

【0128】

すなわち、本実施例によれば、安価な駆動回路で、高階調の実現、階調の単純増加性の確保、発光素子の均一発光、放射ノイズの低減、駆動波形の安定化が可能となる駆動波形および駆動方法を提供することが可能となる。

【0129】

[第2の実施例]

図18は、V14駆動波形の他の例を示す。図8の駆動波形は、図7に示すように、発光強度の比が1:2:3:4になるように、V1、V2、V3、V4の各駆動レベル電位を設定した場合の例を示した。LEDや電子放出素子において、発光強度は駆動電流に概ね比例するので、以下これを電流等分割方式と呼ぶ。一方、図18は、図19に示すように、V1、V2、V3、V4を、それらの比が1:2:3:4になるように、すなわち電位差V4−V3、V3−V2、V2−V1およびV1−V0(ここでも駆動波形の基準電位V0を素子の駆動しきい値と同じにした)が一定となるように定めたもので、以下これを電圧等分割方式と呼ぶ。図19は電圧等分割方式における電圧/電流(発光強度)を示す。

【0130】

図18において、N階調目の白抜きの単位駆動波形ブロックはN−1階調からの差分を表す。N−1階調目の駆動波形に1個の単位駆動ブロックを、駆動波形が連続する位置に付加することによってN階調目の駆動波形を形成する。図18において用いる図19の単位駆動ブロックA〜Dの発光量a〜dはa<b<c<dの関係にある。そのため、単位駆動ブロックA〜Dの発光量が一定である図8の波形においては、3階調と4階調との差分は単位駆動ブロックBであるのに対し、図18の波形においては、単位駆動ブロックAとして低階調である3階調と4階調との間の変化を小さくしている。

【0131】

図20にV14駆動における直線性を示す。このように駆動波形を形成することによって電圧、発光強度特性が変化した場合や、発光素子間のバラツキがあった場合にも単純増加性を保証することができる。

【0132】

図18に示すように、N階調目の最高駆動レベルがkのとき駆動波形の立ち上がり時に1レベル(電位V1)からkレベル(電位Vk)の駆動波形を低いレベルから高いレベルに順番にすべてのレベルを出力し、かつ各レベルの出力を単位パルス幅Δt以上保持することによって、駆動波形の立ち上がり時に流れる電流を低減することが可能となる。

【0133】

同様に駆動波形の立ち下がり時にもkレベル(電位Vk)から1レベル(電位V1)の駆動波形を高いレベルから低いレベルに順番にすべてのレベルを出力しかつ、各レベルの出力を単位パルス幅Δt以上保持することによって、駆動波形の立ち下がり時に流れる電流を低減することが可能となる。

【0134】

[第3の実施例]

図21は、Vn駆動波形の一例を示す。この波形は、輝度データがRビットから構成される時に、輝度データが概略0<N≦((2R)k/n−1)の時、データNの駆動波形の波高値をk(kは1以上n未満の整数)とする波形で駆動するためのものである。図8の駆動波形では、波高値kが3以下の場合、n−2階調目の駆動波形に単位駆動ブロックを付加することによってn−1階調目の駆動波形の波高値kの単位駆動ブロック数(スロット数)が3になったとき、次のn階調目の駆動波形では波高値k+1の単位駆動ブロックを付加していたのに対し、図21の駆動波形では、階調を増加する際、波高値1(1レベル;最低波高値)の単位駆動ブロック数が所定の最大数S(本実施例では259)に達するまでは、波高値(レベル)の繰上げを行わず、最大数Sに達して次に1階調増加するときに、1レベルの単位駆動ブロック数が(S・k+2k+1)/(k+1)以上のこれに最も近い数となり、かつそれぞれ1つ上のレベルのブロック数が下のものより2個または3個少なくなるように折り返して、繰上げを行っている。

【0135】

例えば、S=259の場合、259階調目で1レベルの単位駆動ブロック数が259個と一杯になると、次の260階調目では1レベルが131個と2レベルが129個になり、同様に、516階調目で1レベルが259個と2レベルが257個となって1レベルの単位駆動ブロック数が一杯になると、次の517階調目では、1レベルが175個と2レベルが172個と3レベルが170個になり、771階調目で1レベルが259個と2レベルが257個と3レベルが255となって1レベルの単位駆動ブロック数が一杯になると、次の772階調目では、1レベルが196個と2レベルが194個と3レベルが192個と4レベルが190個になり、最大波高値が1つずつ繰り上がる。

【0136】

図21の駆動波形によると、n=4、k=1すなわち輝度データが0〜最大輝度の1/4までの場合は、従来のパルス幅変調波形に対し、パルス幅変調波形の振幅の実効部分を1/4にし、パルス幅を4倍にして駆動を行うことにより、発光素子1素子当たりに流れる電流はi/4となり、選択された行方向配線に流れる電流もr*i/4となる。したがって電圧降下量も1/4に低減することが可能となり発光素子に印加される電圧の減少量も1/4に低減することが可能となる。同様にn=4、k=2すなわち輝度データが0〜最大輝度の1/2までの場合は電圧降下量を1/2に、n=4、k=3すなわち輝度データが0〜最大輝度の3/4までの場合は電圧降下量を3/4に低減することが可能となる。

【0137】

図9にr×sマトリクスの画像表示装置を示す。図10にn=4、k=1すなわち輝度データが0〜最大輝度の1/4までの場合の従来技術によるパルス幅変調回路での駆動波形を示す。発光素子1素子当たりに流れる電流をiとすると選択された行方向配線Yqにはr*iなる電流が流れることにより電圧降下が発生し、発光素子に印加される電圧が減少してしまうことが分かる。

【0138】

図11にn=4、k=1すなわち最大輝度の1/4迄の輝度データの場合の本実施例によるパルス幅変調回路での駆動波形を示す。パルス幅変調波形の振幅の実効部分(振幅から素子の駆動電圧しきい値に含まれる部分を引いた部分;本実施例では変調波形の基準電位となるV0を素子の駆動しきい値と同じ値としたため、変調波形の振幅から素子の駆動電圧しきい値に含まれる部分を引いた部分=変調波形の振幅である)を1/4にし、パルス幅を4倍にした駆動を行った様子を示す。発光素子1素子当たりに流れる電流はi/4となり、選択された行方向配線に流れる電流もr*i/4となる。したがって電圧降下量も1/4に低減することが可能となり発光素子に印加される電圧の減少量も1/4に低減することが可能となる。

【0139】

同様にn=4、k=2すなわち輝度データが0〜最大輝度の1/2までの場合は電圧降下量を1/2に、n=4、k=3すなわち輝度データが0〜最大輝度の3/4までの場合は電圧降下量を3/4に低減することが可能となる。

【0140】

図22に第1または第2実施例のV14駆動(前揃え)における変調波形の例と任意の走査配線Yqに流れる電流を示す。また、図23に本実施例であるVn駆動(前揃え)における変調波形の例と任意の走査配線Yqに流れる電流を示す。本実施例のVn駆動の方が、電流が平均化されることによって走査配線に流れる電流のピークが大幅に減少しているのが分かる。

【0141】

図24にVn駆動に前後揃えを併用した場合の走査配線(行方向配線)Yqに流れる電流を示す。さらに電流が平均化されている。ここで、前揃えとは、駆動波形の立ち上がり部分が1選択期間の前半になるように制御することであり、好適には時間的に最初の単位駆動ブロックをパルス幅制御の前半の所定のスロットで発生するとよい。また、後ろ揃えとは、駆動波形の立ち下がり部分が1選択期間の後半になるように制御することであり、好適には時間的に最後の単位駆動ブロックをパルス幅制御の後半の所定のスロットで発生するようにするとよい。なお、これら所定のスロットを固定する場合は、前半の所定のスロットとして1選択期間の最初のスロットを、後半の所定のスロットとして最終スロットを設定するのが好ましいが、より内側のスロットを設定してもよい。また、各列方向配線ごとに、その列方向配線または他の列方向配線を介して駆動すべき発光素子の階調または変調波形に応じて、前半または後半の各所定のスロットを設定するようにしてもよい。あるいは同時に選択される複数の発光素子の階調または変調波形に応じてそれらを駆動する全列方向配線に対して同じスロットを、前半または後半の各所定のスロットとして設定するようにしてもよい。

【0142】

[第4の実施例]

図25に新Vn駆動波形を示す。この駆動波形は、階調を増加する際、先ず波高値1(1レベル)の単位駆動ブロックを所定の最大数S(本実施例では259)に達するまで配列し、次に2レベル(電位V2)の単位駆動ブロックを第2スロットから第S−1スロットに達するまで配列し、‥‥、kレベル(電位Vk)の単位駆動ブロックを第kスロットから第S+1−kスロットに達するまで配列するというように、順序良く配列するものである。

【0143】

図26に新Vn駆動(前揃え)における変調波形の例と任意の走査配線Yqに流れる電流を示す。電流が平均化されている。さらに新Vn駆動に前後揃えを併用することによって図27に示すように走査配線Yqに流れる電流を1H期間内でほぼ均一にすることが可能となる。

【0144】

ここで1920×3本の情報配線および1024本の走査配線を持つマトリクスパネルについて情報配線に流れる電流の低減効果を算出する。素子に流す電流を最大0.8mAとすると、図7に示すように駆動電流を等分割になるように変調波形を設定した場合、従来の単純PWMやV14駆動の場合は1素子当たりの電流変化の最大値は0.8mAであるから1走査配線当たりの電流変化の最大値ΔIyは

ΔIy=0.8mA×1920×3=4.608A

前後揃えを併用することによって1/2になるので

ΔIy=2.304A

新Vn駆動の場合は波形の立ち上がり、立ち下がり部を除いた部分では電流の変化は0.8mA/4=0.2mAであるので

ΔIy=0.2mA×1920×3=1.152A

さらに、前後揃え駆動を併用すると1素子ごとに前揃え、後ろ揃えが繰り返されるので1/2になり、

ΔIy=576mA

となる。

【0145】

[実施例の変形例]

図21のVn駆動および図25の新Vn駆動において、変調波形は、図7に示すように駆動電流が等分割になるように設定することも、図19に示すように駆動電位振幅の実効部分が等分割になるように設定することも可能である。波形の立ち上がり立ち下がり時に発生するリンギングやオーバーシュートを防止するためには、基礎電位との電位差が素子の駆動電圧しきい値となる電位(V0)、ならびにV1、V2、V3、およびV4間の電圧を等しくすることが有効である。図19に駆動電位振幅の実効部分を等分割した場合の印加電圧と発光量の関係を示す。駆動波形の時間変化グラフ中で表される単位パルス幅と単位波高値で構成されるA、B、C、Dの単位駆動波形ブロックの発光量が等しくならないことが分かる。

【0146】

図20にV14駆動において電流等分割にした場合と、電圧等分割にした場合の輝度とデータの関係を示す。低輝度領域で直線性がやや損なわれるが、単純増加性は保証されており、データの補正等によって対処可能である。

【0147】

γ補正については、リンギング発生を最小限に出来るV1〜V4の電圧等分割に設定によって、輝度データ対輝度の関係が通常使用される2.2乗の逆γ特性よりも深いカーブ(低輝度領域で輝度分解能が高くなる)となる。その結果、逆γ変換時に低輝度から中輝度の輝度分解能を高めることが可能となる。

【0148】

上述した実施例においては、4レベルの波高値制御を行い階調数が0から1023の1024階調の例を挙げたが、本発明において、制御波高値、階調数の限定は無い。

【0149】

【発明の効果】

本発明によって、安価な駆動回路で、高階調の実現、階調の単純増加性の確保、発光素子の均一発光、放射ノイズの低減、駆動波形の安定化が可能となる駆動波形、駆動方法を提供することが可能となる。また、安価な駆動回路で、輝度分布の偏りを低減することができる発光素子制御方法を提供することが可能となる。

【図面の簡単な説明】

【図1】 本発明の一実施例に係るマルチ電子源駆動回路のブロック図である。

【図2】 図1における変調回路のブロック図である。

【図3】 図2におけるPWM回路のブロック図である。

【図4】 図3のPWM回路の要部構成の一例を示すブロック図である。

【図5】 図3のPWM回路の要部構成の他の例を示すブロック図である。

【図6】 図2における出力段回路の一例を示す回路図である。

【図7】 発光素子の電圧/発光強度特性(電流等分割)を示すグラフである。

【図8】 電流等分割によるV14駆動波形の一例を示す波形図である。

【図9】 r×sマトリクスの画像表示装置の構成図である。

【図10】 輝度データが0〜最大輝度の1/4までの場合の従来技術によるパルス幅変調回路での駆動波形の波形図である。

【図11】 輝度データが0〜最大輝度の1/4までの場合の第1の実施例によるパルス幅変調回路での駆動波形の波形図である。

【図12】 図1のマルチ発光素子の等価回路図である。

【図13】 図12の等価回路図の単ビット列方向配線モデルの図である。

【図14】 図13のモデルの行方向配線末端の電圧波形図である。

【図15】 図13のモデルの列方向配線に流れ込む電流波形図である。

【図16】 従来波形で駆動した場合の行方向配線末端の電圧波形図である。

【図17】 従来波形で駆動した場合の列方向配線に流れ込む電流波形図である。

【図18】 電圧等分割によるV14駆動波形の一例を示す波形図である。

【図19】 発光素子の電圧/発光強度特性(電圧等分割)を示すグラフである。

【図20】 図8および図18のV14駆動における直線性を示すグラフである。

【図21】 Vn駆動波形の一例を示す波形図である。

【図22】 V14駆動(前揃え)における変調波形および任意の走査配線Yqに流れる電流を示す波形図である。

【図23】 Vn駆動(前揃え)における変調波形および任意の走査配線Yqに流れる電流を示す波形図である。

【図24】 Vn駆動に前後揃えを併用した場合の変調波形および任意の走査配線Yqに流れる電流を示す波形図である。

【図25】 新Vn駆動波形の一例を示す波形図である。

【図26】 新Vn駆動(前揃え)における変調波形の例と任意の走査配線Yqに流れる電流を示す波形図である。

【図27】 新Vn駆動に前後揃えを併用した場合の変調波形および任意の走査配線Yqに流れる電流を示す波形図である。

【図28】 表面伝導型放出素子の素子構成の一例を示す図である。

【図29】 FE型の素子構成の一例を示す断面図である。

【図30】 MIM型の素子構成の一例を示す断面図である。

【図31】 マルチ電子ビーム源の電気的構成を示す配線図である。

【図32】 従来の走査回路およびパルス幅変調回路の出力波形図である。

【図33】 従来の走査回路およびパルス幅変調回路の出力波形図である。

【図34】 マルチ電子源の構成図である。

【図35】 図34のマルチ電子源の分解斜視図である。

【図36】 ある選択電極に接続されている画素の全てが点灯したときの等価回路図である。

【図37】 図36の回路における選択電極上の各部の電圧を示すグラフである。

【図38】 図36の回路で最遠方端の画素に印加される駆動波形の図である。

【図39】 図6における信号TV4〜TV1およびGV4〜GV0の波形図である。

【符号の説明】

1:電子源(電子放出素子)、2:行方向配線、3:列方向配線、4:行方向配線寄生抵抗、5:列方向配線寄生抵抗、6:行方向配線寄生インダクタンス、7:列方向配線寄生インダクタンス、8:寄生容量、9:走査回路、10:変調回路、11:画像表示装置、12:基板、13:メタルバック、14:蛍光面、15:フェースプレート、16:電子源からの電流、101:マルチ電子源、102:変調回路、103:走査回路、104:タイミング発生回路、105:データ変換回路、106:マルチ電源回路、107:シフトレジスタ、108:PWM回路、109:出力段回路、110:ラッチ、111:V1スタート回路、112:V2スタート回路、113:V3スタート回路、114:V4スタート回路、115:V1エンド回路、116:V2エンド回路、117:V3エンド回路、118:V4エンド回路、119:V1PWM発生回路、120:V2PWM発生回路、121:V3PWM発生回路、122:V4PWM発生回路。

Claims (17)

- スロット幅Δt単位でパルス幅制御されかつ各スロットにおける波高値がA 1〜Anのn段階(但し、nは2以上の整数で、0<A1<A2<・・・・<An でありA 1 は0でない階調データに対応する波高値)のいずれかの波高値に制御される駆動波形を1選択期間中に発光素子に供給する駆動回路であって、

前記駆動波形は、波高値が波高値A1から波高値Ak−1までの波高値に制御される部分を少なくとも1スロットずつ経て所定波高値Ak(但し、kは2以上n以下の整数)に制御される部分まで立ち上がる部分と、波高値が前記所定波高値Ak に制御されている部分から、波高値が前記波高値Ak−1から波高値A1までの波高値に制御される部分を少なくとも1スロットずつ経て立ち下がる部分とを有することを特徴とする発光素子の駆動回路。 - 前記駆動波形が波高値A1に立ち上がったスロットを第1スロットとするとき、第1〜第k−1スロットの波高値がそれぞれA1〜Ak−1、第kと第Nk+k−1スロット(但し、Nkは1以上の整数)の波高値がAk、第Nk+k〜第Nk+2(k−1)スロットの波高値がそれぞれAk−1〜A1となる駆動波形に対し、前記発光素子を駆動する駆動エネルギーを1段階増加させた駆動波形が、前記駆動波形の第Nk+2k−1スロットの波高値をA1に増加させたものであり、以降順次前記駆動エネルギーを1段階増加させた駆動波形が前段階の駆動波形に対して、さらに第Nk+2(k−1)スロットの波高値をA1からA2に、・・・・、第Nk+kスロットの波高値をAk−1からAkに変更した波形を有することを特徴とする請求項1に記載の駆動回路。

- 波高値Akから波高値Akより低い各波高値を順番に少なくとも1スロットずつ経て立ち下がる部分を有する所定の駆動波形に対して、前記発光素子を駆動するエネルギーを一段階増加した駆動波形が、前段の駆動波形の前記立ち下がる部分において波高値がA1であったスロットに続くスロットの波高値をA1に増加させた波形を有しており、以降前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有することを特徴とする請求項1もしくは2に記載の駆動回路。

- 前段の駆動波形に対して前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有するという前記関係は、該関係によって決まる駆動波形が前段の駆動波形に対して波高値を増加させたスロットの波高値が波高値Akよりも一段階高い波高値である駆動波形までの一連の駆動波形が満たすものである請求項3に記載の駆動回路。

- 前段の駆動波形に対して前記発光素子を駆動するエネルギーを一段階ずつ増加した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階増加させたスロットの一つ手前のスロットの波高値を一段階増加させた波形を有するという前記関係は、該関係によって決まる駆動波形が前段の駆動波形に対して波高値を増加させたスロットの波高値が波高値Akである駆動波形までの一連の駆動波形が満たすものである請求項3に記載の駆動回路。

- 前記駆動波形が波高値A1に立ち上がったスロットを第1スロットとするとき、第1〜第k−1スロットの波高値がそれぞれA1〜Ak−1、第kと第Nk+k−1スロット(但し、Nkは1以上の整数)の波高値がAk、第Nk+k〜第Nk+2(k−1)スロットの波高値がそれぞれAk−1〜A1となる駆動波形に対し、前記発光素子を駆動する駆動エネルギーを1段階減少させた駆動波形が、前記駆動波形の第kスロットの波高値をAkからAk−1に変更したものであり、以降順次前記駆動エネルギーを1段階減少させた駆動波形が前段階の駆動波形に対して、さらに第k−1スロットの波高値をAk−1からAk−2に、・・・・、第1スロットの波高値をA1から輝度データの最低階調に対応する発光を生じさせない波高値に変更した波形を有することを特徴とする請求項1に記載の駆動回路。

- 波高値Akより低い各波高値を順番に少なくとも1スロットずつ経て波高値Akまで立ち上がる部分を有する駆動波形に対して、前記発光素子を駆動するエネルギーを一段階減少した駆動波形が、前段の駆動波形の前記立ち上がる部分において波高値がAk−1であったスロットに続くスロットであり波高値がAkであったスロットの波高値をAk−1とした波形を有しており、以降前記発光素子を駆動するエネルギーを一段階ずつ減少した駆動波形が、前段の駆動波形において、前々段の駆動波形に対して波高値を一段階減少させたスロットの一つ手前のスロットの波高値を一段階減少させた波形を有することを特徴とする請求項1もしくは6に記載の駆動回路。

- 前記駆動波形において波高値がAkである2つのスロットの間のスロットにおける波高値はAkである請求項1乃至7のいずれか1つに記載の駆動回路。

- 前記波高値がAkである2つのスロットの間に他のスロットがある時には、該他のスロットにおける波高値はAkとするものであり、k=1の場合を含み前記波高値AkがAnよりも小さく、かつ前段階の駆動波形に対して駆動エネルギーを一段階増加させることにより波高値がAkであるスロットの数が2個から3個になった駆動波形に対して、駆動エネルギーを更に一段階増加させた駆動波形は、前記駆動波形の波高値がAkである3個のスロットのうちの真中のスロットの波高値をAkからAk+1に変更した形状を有することを特徴とする請求項2乃至4、6、7のいずれか1つに記載の駆動回路。

- 所定の駆動波形よりも前記発光素子を駆動する駆動エネルギーを増加させた駆動波形は、前記所定の駆動波形に対して最大波高値を上昇させるよりもパルス幅を増加させることを優先させた形状を有する請求項1乃至3もしくは5乃至8のいずれか1つに記載の駆動回路。

- 所定の駆動波形に対して前記発光素子を駆動する駆動エネルギーを一段階増加して駆動波形の最大波高値を高くしたときの駆動波形は、波高値差An−An−1、・・・・、もしくはA2−A1または波高値A1と前記発光素子の駆動しきい値となる波高値との波高値差、およびスロット幅Δtとで定まる単位駆動波形ブロックの数を前記所定の駆動波形で用いた数よりも一つ増加させて、最大波高値がなるべく連続するように積み直した形状を有する請求項1乃至3もしくは5乃至8もしくは10のいずれか1つに記載の駆動回路。

- 階調データに対応する駆動波形を発生する駆動回路であって、

0でない前記階調データに対応する波高値である最小の波高値とより大きい前記階調データに対応する波高値である1つ以上の非最小の波高値とを含む不連続な複数の波高値に波高値が制御される駆動波形を1選択期間中に発生するものであり、

前記非最小の波高値に制御される部分を有する前記駆動波形が、前記最小の波高値に制御される部分を該駆動波形の先頭および末尾に有するものであることを特徴とする駆動回路。 - マトリクスディスプレイを構成する複数個の発光素子に対してそれぞれの階調データに応じた前記駆動波形を印加することを特徴とする請求項1乃至12のいずれか1つに記載の駆動回路。

- 複数の発光素子と、該複数の発光素子をマトリクス配線する走査信号配線及び情報信号配線と、請求項1乃至13のいずれか1つに記載の駆動回路とを有しており、前記駆動回路は、複数の前記発光素子を駆動する駆動波形を発生するものであることを特徴とする表示装置。

- 前記走査信号配線に接続された走査回路を有しており、

前記駆動波形は、前記走査回路により選択された発光素子に対して前記情報信号配線を介して供給される請求項14に記載の表示装置。 - 前記複数の情報信号配線の一部の情報信号配線に印加する駆動波形は、立ち上がりが走査回路が一つの走査信号配線を選択する選択期間の前半になるように制御し、他の一部の情報信号配線に印加する駆動波形は、立ち下がりが前記選択期間の後半になるように制御することを特徴とする請求項15に記載の表示装置。

- 前記発光素子が表面伝導型放出素子を用いたものであることを特徴とする請求項14乃至16のいずれか1つに記載の表示装置。

Priority Applications (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002167096A JP3681121B2 (ja) | 2001-06-15 | 2002-06-07 | 駆動回路及び表示装置 |

| US10/167,666 US6995516B2 (en) | 2001-06-15 | 2002-06-13 | Drive circuit, display device, and driving method |

| EP02013080A EP1267319A2 (en) | 2001-06-15 | 2002-06-13 | Drive circuit, display device, and driving method |

| CNB2005100528263A CN100394466C (zh) | 2001-06-15 | 2002-06-14 | 驱动电路、显示装置 |

| KR1020020033285A KR100557183B1 (ko) | 2001-06-15 | 2002-06-14 | 구동회로, 표시장치 및 구동방법 |

| CNB021429154A CN100483494C (zh) | 2001-06-15 | 2002-06-14 | 驱动电路和显示装置 |

| KR1020040110215A KR100802225B1 (ko) | 2001-06-15 | 2004-12-22 | 구동회로, 표시장치 및 구동방법 |

| KR1020050080536A KR100639687B1 (ko) | 2001-06-15 | 2005-08-31 | 구동회로, 표시장치 및 구동방법 |

| US11/264,162 US7573472B2 (en) | 2001-06-15 | 2005-11-02 | Drive circuit, display device, and driving method |

Applications Claiming Priority (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001-181841 | 2001-06-15 | ||

| JP2001181841 | 2001-06-15 | ||

| JP2001248978 | 2001-08-20 | ||

| JP2001-248978 | 2001-08-20 | ||

| JP2001296397 | 2001-09-27 | ||

| JP2001-296397 | 2001-09-27 | ||

| JP2002167096A JP3681121B2 (ja) | 2001-06-15 | 2002-06-07 | 駆動回路及び表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003173159A JP2003173159A (ja) | 2003-06-20 |

| JP3681121B2 true JP3681121B2 (ja) | 2005-08-10 |

| JP2003173159A5 JP2003173159A5 (ja) | 2005-09-22 |

Family

ID=27482344

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002167096A Expired - Fee Related JP3681121B2 (ja) | 2001-06-15 | 2002-06-07 | 駆動回路及び表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US6995516B2 (ja) |

| EP (1) | EP1267319A2 (ja) |

| JP (1) | JP3681121B2 (ja) |

| KR (3) | KR100557183B1 (ja) |

| CN (2) | CN100394466C (ja) |

Families Citing this family (42)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI280547B (en) * | 2000-02-03 | 2007-05-01 | Samsung Electronics Co Ltd | Liquid crystal display and driving method thereof |

| JP3647426B2 (ja) * | 2001-07-31 | 2005-05-11 | キヤノン株式会社 | 走査回路及び画像表示装置 |

| JP3715967B2 (ja) * | 2002-06-26 | 2005-11-16 | キヤノン株式会社 | 駆動装置及び駆動回路及び画像表示装置 |

| JP4320413B2 (ja) * | 2002-09-11 | 2009-08-26 | 日本電気株式会社 | 半導体集積回路およびレイアウト設計装置 |

| JP3830888B2 (ja) * | 2002-12-02 | 2006-10-11 | オプトレックス株式会社 | 有機el表示装置の駆動方法 |

| JP4136670B2 (ja) * | 2003-01-09 | 2008-08-20 | キヤノン株式会社 | マトリクスパネルの駆動制御装置及び駆動制御方法 |

| JP4332358B2 (ja) * | 2003-01-30 | 2009-09-16 | キヤノン株式会社 | 駆動回路 |

| JP3880540B2 (ja) | 2003-05-16 | 2007-02-14 | キヤノン株式会社 | 表示パネルの駆動制御装置 |

| JP4012118B2 (ja) | 2003-05-19 | 2007-11-21 | キヤノン株式会社 | 画像表示装置 |

| JP4035490B2 (ja) | 2003-08-15 | 2008-01-23 | キヤノン株式会社 | 画像表示装置の製造方法、画像表示装置 |

| KR100599649B1 (ko) * | 2003-11-24 | 2006-07-12 | 삼성에스디아이 주식회사 | 플라즈마 디스플레이 패널의 구동 장치 |

| JP2005257791A (ja) * | 2004-03-09 | 2005-09-22 | Canon Inc | 画像表示装置及び画像表示装置の駆動方法 |

| JP2005292804A (ja) * | 2004-03-10 | 2005-10-20 | Canon Inc | 制御装置及び画像表示装置 |

| JP4086852B2 (ja) | 2004-03-16 | 2008-05-14 | キヤノン株式会社 | 画像表示装置 |

| KR101022657B1 (ko) * | 2004-05-31 | 2011-03-22 | 삼성에스디아이 주식회사 | 전자 방출 장치의 구동방법 |

| US7227317B2 (en) * | 2004-06-10 | 2007-06-05 | Atmel Corporation | Method and system for enhanced dimming resolution in a light ballast through use of multiple control frequencies |

| JP4908784B2 (ja) * | 2004-06-30 | 2012-04-04 | キヤノン株式会社 | 表示素子の駆動回路、画像表示装置、テレビジョン装置 |

| CN100390840C (zh) * | 2004-06-30 | 2008-05-28 | 佳能株式会社 | 显示装置、电视装置、和驱动显示装置的方法 |

| JP4560445B2 (ja) | 2004-06-30 | 2010-10-13 | キヤノン株式会社 | 表示装置及び駆動方法 |

| JP4174494B2 (ja) | 2004-06-30 | 2008-10-29 | キヤノン株式会社 | 駆動装置、画像表示装置及びテレビジョン装置 |

| CN100428294C (zh) * | 2004-06-30 | 2008-10-22 | 佳能株式会社 | 调制电路、驱动电路、调制信号的生成方法、图像显示装置和电视设备 |

| JP2006047997A (ja) | 2004-06-30 | 2006-02-16 | Canon Inc | 変調回路、駆動回路および出力方法 |

| US20060050031A1 (en) * | 2004-09-06 | 2006-03-09 | Sanyo Electric Co., Ltd. | Display-device driving circuit suitable for inorganic electroluminescence (EL) display device |

| JP2006186277A (ja) * | 2004-12-28 | 2006-07-13 | Sanyo Electric Co Ltd | 発光素子駆動装置 |

| KR100676190B1 (ko) * | 2005-05-17 | 2007-01-30 | 엘지전자 주식회사 | 유기 전계 발광 소자 |

| JP4494298B2 (ja) * | 2005-06-24 | 2010-06-30 | シャープ株式会社 | 駆動回路 |

| KR100732809B1 (ko) * | 2005-11-03 | 2007-06-27 | 삼성에스디아이 주식회사 | 데이터 구동부 및 이를 이용한 유기 발광표시장치 |

| US8373355B2 (en) * | 2006-11-09 | 2013-02-12 | Apple Inc. | Brightness control of a status indicator light |

| JP4861937B2 (ja) * | 2007-09-11 | 2012-01-25 | オムロン株式会社 | 送信装置、受信装置、送受信装置、送信制御方法、受信制御方法、光伝送モジュール、電子機器 |

| JP2009211052A (ja) * | 2008-02-06 | 2009-09-17 | Canon Inc | 表示パネルの駆動回路および表示装置 |

| JP2009251046A (ja) | 2008-04-01 | 2009-10-29 | Canon Inc | 画像表示装置およびその制御方法 |

| CN102113046B (zh) * | 2008-08-01 | 2014-01-22 | 希毕克斯影像有限公司 | 用于电泳显示器的带有误差扩散的伽马调节 |

| JP2010145739A (ja) * | 2008-12-18 | 2010-07-01 | Sanyo Electric Co Ltd | 発光素子駆動回路 |

| JP2011018012A (ja) * | 2009-06-08 | 2011-01-27 | Canon Inc | 画像表示装置の制御方法 |

| JP2011002651A (ja) * | 2009-06-18 | 2011-01-06 | Canon Inc | 画像表示装置および画像表示装置の制御方法 |

| US8138687B2 (en) * | 2009-06-30 | 2012-03-20 | Apple Inc. | Multicolor lighting system |

| WO2011026217A1 (en) * | 2009-09-02 | 2011-03-10 | Scobil Industries Corp. | Method and apparatus for driving an electroluminescent display |

| US8400626B2 (en) | 2010-06-10 | 2013-03-19 | Apple Inc. | Ambient light sensor |

| JP2013083826A (ja) * | 2011-10-11 | 2013-05-09 | Canon Inc | 液晶表示装置、液晶表示装置の制御方法 |

| CN103247251B (zh) * | 2012-02-03 | 2015-06-03 | 深圳市明微电子股份有限公司 | Led驱动芯片的整体调变控制方法及系统 |

| US10455653B1 (en) * | 2018-08-09 | 2019-10-22 | Innolux Corporation | LED driving circuits |

| US11835382B2 (en) | 2021-03-02 | 2023-12-05 | Apple Inc. | Handheld electronic device |

Family Cites Families (49)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4904895A (en) * | 1987-05-06 | 1990-02-27 | Canon Kabushiki Kaisha | Electron emission device |

| DE3853744T2 (de) * | 1987-07-15 | 1996-01-25 | Canon Kk | Elektronenemittierende Vorrichtung. |

| JPS6431332A (en) | 1987-07-28 | 1989-02-01 | Canon Kk | Electron beam generating apparatus and its driving method |

| JPH0518585Y2 (ja) | 1987-08-13 | 1993-05-18 | ||

| JPH02257551A (ja) | 1989-03-30 | 1990-10-18 | Canon Inc | 画像形成装置 |

| JP3044382B2 (ja) | 1989-03-30 | 2000-05-22 | キヤノン株式会社 | 電子源及びそれを用いた画像表示装置 |

| JP2967288B2 (ja) | 1990-05-23 | 1999-10-25 | キヤノン株式会社 | マルチ電子ビーム源及びこれを用いた画像表示装置 |

| US5682085A (en) * | 1990-05-23 | 1997-10-28 | Canon Kabushiki Kaisha | Multi-electron beam source and image display device using the same |

| JP3165701B2 (ja) * | 1991-03-06 | 2001-05-14 | キヤノン株式会社 | 振動波モーター |

| JP2901032B2 (ja) | 1992-01-31 | 1999-06-02 | 京セラ株式会社 | Ledプリントヘッド |

| JP3167072B2 (ja) | 1992-12-29 | 2001-05-14 | キヤノン株式会社 | 画像形成装置 |

| US5455597A (en) * | 1992-12-29 | 1995-10-03 | Canon Kabushiki Kaisha | Image-forming apparatus, and designation of electron beam diameter at image-forming member in image-forming apparatus |

| CA2112431C (en) * | 1992-12-29 | 2000-05-09 | Masato Yamanobe | Electron source, and image-forming apparatus and method of driving the same |

| CA2112733C (en) * | 1993-01-07 | 1999-03-30 | Naoto Nakamura | Electron beam-generating apparatus, image-forming apparatus, and driving methods thereof |

| JP3235893B2 (ja) | 1993-01-28 | 2001-12-04 | 京セラ株式会社 | 液晶表示装置の駆動回路 |

| US6157137A (en) * | 1993-01-28 | 2000-12-05 | Canon Kabushiki Kaisha | Multi-electron beam source with driving circuit for preventing voltage spikes |

| JP3205167B2 (ja) * | 1993-04-05 | 2001-09-04 | キヤノン株式会社 | 電子源の製造方法及び画像形成装置の製造方法 |

| JPH075836A (ja) * | 1993-04-05 | 1995-01-10 | Canon Inc | 画像形成装置及び画像形成方法 |

| FR2708129B1 (fr) * | 1993-07-22 | 1995-09-01 | Commissariat Energie Atomique | Procédé et dispositif de commande d'un écran fluorescent à micropointes. |

| JPH07177446A (ja) | 1993-12-17 | 1995-07-14 | Matsushita Electric Ind Co Ltd | 画像表示装置 |

| CA2138363C (en) * | 1993-12-22 | 1999-06-22 | Yasuyuki Todokoro | Electron beam generating apparatus, image display apparatus, and method of driving the apparatuses |

| US5477110A (en) | 1994-06-30 | 1995-12-19 | Motorola | Method of controlling a field emission device |

| JPH09101759A (ja) * | 1995-10-04 | 1997-04-15 | Pioneer Electron Corp | 発光素子の駆動方法および駆動装置 |

| JP3278375B2 (ja) * | 1996-03-28 | 2002-04-30 | キヤノン株式会社 | 電子線発生装置、それを備える画像表示装置、およびそれらの駆動方法 |

| JPH09281928A (ja) | 1996-04-16 | 1997-10-31 | Pioneer Electron Corp | 表示装置 |

| JPH1039825A (ja) | 1996-07-23 | 1998-02-13 | Canon Inc | 電子発生装置、画像表示装置およびそれらの駆動回路、駆動方法 |

| JP4059537B2 (ja) | 1996-10-04 | 2008-03-12 | 三菱電機株式会社 | 有機薄膜el表示装置及びその駆動方法 |

| JP3027126B2 (ja) | 1996-11-26 | 2000-03-27 | 松下電器産業株式会社 | 液晶表示装置 |

| CN2300165Y (zh) * | 1996-11-27 | 1998-12-09 | 矽诚科技股份有限公司 | 电致发光板驱动装置 |

| JPH1115430A (ja) | 1997-06-19 | 1999-01-22 | Yamaha Corp | 電界放出型ディスプレイ装置 |

| JP3049061B1 (ja) * | 1999-02-26 | 2000-06-05 | キヤノン株式会社 | 画像表示装置及び画像表示方法 |

| JP3644240B2 (ja) | 1998-03-24 | 2005-04-27 | セイコーエプソン株式会社 | 電気光学装置用のデジタルドライバ回路及びこれを備えた電気光学装置 |

| JP3554185B2 (ja) | 1998-04-03 | 2004-08-18 | キヤノン株式会社 | 電子源駆動装置及びそれを用いた画像形成装置 |

| US6489940B1 (en) * | 1998-07-31 | 2002-12-03 | Canon Kabushiki Kaisha | Display device driver IC |

| JP2000148074A (ja) * | 1998-11-06 | 2000-05-26 | Victor Co Of Japan Ltd | マトリクス型表示装置 |

| JP2000172217A (ja) | 1998-12-09 | 2000-06-23 | Victor Co Of Japan Ltd | マトリクス型表示装置 |

| JP3747142B2 (ja) * | 1999-02-24 | 2006-02-22 | キヤノン株式会社 | 画像表示装置 |

| JP3611293B2 (ja) * | 1999-02-24 | 2005-01-19 | キヤノン株式会社 | 電子線装置及び画像形成装置 |

| JP2000250471A (ja) * | 1999-02-25 | 2000-09-14 | Canon Inc | マルチ電子源の駆動装置と方法及び画像形成装置 |

| JP3840027B2 (ja) * | 1999-02-26 | 2006-11-01 | キヤノン株式会社 | 画像表示装置及び表示制御方法 |

| JP3931470B2 (ja) * | 1999-03-25 | 2007-06-13 | 日本ビクター株式会社 | マトリクス型表示装置 |

| JP3815710B2 (ja) * | 1999-04-28 | 2006-08-30 | 矢崎総業株式会社 | El素子の駆動装置 |

| EP1148468A4 (en) * | 1999-09-27 | 2005-02-02 | Citizen Watch Co Ltd | METHOD FOR CONTROLLING A COLOR LIQUID SIGNAL DISPLAY DEVICE AND METHOD FOR CONTROLLING THE DISPLAY OF A CLOCK |

| US6867755B2 (en) * | 2000-04-28 | 2005-03-15 | Yazaki Corporation | Device and method for driving EL device |

| JP3755585B2 (ja) * | 2001-05-11 | 2006-03-15 | セイコーエプソン株式会社 | 表示コントローラ、表示ユニット及び電子機器 |

| JP3647426B2 (ja) * | 2001-07-31 | 2005-05-11 | キヤノン株式会社 | 走査回路及び画像表示装置 |

| US6970162B2 (en) * | 2001-08-03 | 2005-11-29 | Canon Kabushiki Kaisha | Image display apparatus |

| US6882329B2 (en) * | 2001-09-28 | 2005-04-19 | Canon Kabushiki Kaisha | Drive signal generator and image display apparatus |

| JP3715967B2 (ja) * | 2002-06-26 | 2005-11-16 | キヤノン株式会社 | 駆動装置及び駆動回路及び画像表示装置 |

-

2002

- 2002-06-07 JP JP2002167096A patent/JP3681121B2/ja not_active Expired - Fee Related

- 2002-06-13 US US10/167,666 patent/US6995516B2/en not_active Expired - Fee Related

- 2002-06-13 EP EP02013080A patent/EP1267319A2/en not_active Withdrawn

- 2002-06-14 CN CNB2005100528263A patent/CN100394466C/zh not_active Expired - Fee Related

- 2002-06-14 KR KR1020020033285A patent/KR100557183B1/ko not_active IP Right Cessation

- 2002-06-14 CN CNB021429154A patent/CN100483494C/zh not_active Expired - Fee Related

-

2004

- 2004-12-22 KR KR1020040110215A patent/KR100802225B1/ko not_active IP Right Cessation

-

2005

- 2005-08-31 KR KR1020050080536A patent/KR100639687B1/ko not_active IP Right Cessation

- 2005-11-02 US US11/264,162 patent/US7573472B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR20020096923A (ko) | 2002-12-31 |

| CN100483494C (zh) | 2009-04-29 |

| US6995516B2 (en) | 2006-02-07 |

| EP1267319A2 (en) | 2002-12-18 |

| KR20050090118A (ko) | 2005-09-12 |

| CN1402213A (zh) | 2003-03-12 |

| CN100394466C (zh) | 2008-06-11 |

| US7573472B2 (en) | 2009-08-11 |

| KR100802225B1 (ko) | 2008-02-11 |

| KR100557183B1 (ko) | 2006-03-03 |

| KR100639687B1 (ko) | 2006-10-31 |

| CN1652173A (zh) | 2005-08-10 |

| JP2003173159A (ja) | 2003-06-20 |

| US20020195966A1 (en) | 2002-12-26 |

| KR20050014779A (ko) | 2005-02-07 |

| US20060050030A1 (en) | 2006-03-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3681121B2 (ja) | 駆動回路及び表示装置 | |

| US7283131B2 (en) | Image display apparatus | |

| US6839054B2 (en) | Image display apparatus and image display method | |

| JP2004287118A (ja) | 表示装置 | |

| US6515641B1 (en) | Image display apparatus and method of driving image display apparatus | |

| JP2002156938A (ja) | 画像表示装置およびその駆動方法 | |

| JP3679784B2 (ja) | 画像表示素子の変調装置および画像表示装置 | |

| JP2002311885A (ja) | 画像表示装置の駆動回路、画像表示装置、画像表示装置の駆動方法 | |

| JP2001195026A (ja) | マトリクス型表示装置 | |

| JP2003316312A (ja) | 発光素子の駆動方法 | |

| JP2011018012A (ja) | 画像表示装置の制御方法 | |

| JP2005062382A (ja) | ディスプレイ駆動回路及び表示装置 | |

| JP2009251046A (ja) | 画像表示装置およびその制御方法 | |

| KR101022658B1 (ko) | 신호 지연 저감형 전자 방출 장치 구동방법 | |

| JP2005257791A (ja) | 画像表示装置及び画像表示装置の駆動方法 | |

| JP3931470B2 (ja) | マトリクス型表示装置 | |

| JP4595177B2 (ja) | マトリクス型表示装置 | |

| US20090256866A1 (en) | Image display apparatus | |

| JP4453136B2 (ja) | マトリクス型画像表示装置 | |

| JP2000148074A (ja) | マトリクス型表示装置 | |

| JP2000267623A (ja) | 表示装置の画像表示方法とその駆動装置 | |

| JP2000148073A (ja) | マトリクス型表示装置 | |

| JP2004206148A (ja) | 画像表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050419 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050511 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050513 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090527 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100527 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100527 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110527 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120527 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |