JP3654474B2 - アクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにその製造方法 - Google Patents

アクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにその製造方法 Download PDFInfo

- Publication number

- JP3654474B2 JP3654474B2 JP31150896A JP31150896A JP3654474B2 JP 3654474 B2 JP3654474 B2 JP 3654474B2 JP 31150896 A JP31150896 A JP 31150896A JP 31150896 A JP31150896 A JP 31150896A JP 3654474 B2 JP3654474 B2 JP 3654474B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- electrode

- liquid crystal

- crystal display

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/1368—Active matrix addressed cells in which the switching element is a three-electrode device

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

Description

【発明の属する技術分野】

本発明はアクティブマトリックス液晶表示装置(AMLCD)に係り、マトリックスアレイのバスラインと薄膜トランジスタの最適構造の設計を通して開口率を向上させ省エネルギ−に寄与し、輝度の向上、及び反射度の減少によるコントラスト比を改善したアクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにその製造方法に関する。

【0002】

【従来の技術】

アクティブマトリックス液晶表示装置のマトリックスアレイは薄膜トランジスタのようなスイッチング素子と、これに電気的に連結されており光を透過したり反射する画素電極を基本単位とする画素子が縦横に配列された構造を有する。この際、画素の特性を向上させるために補助容量キャパシタを追加して形成する場合もある。また、この画素を互いに連結する複数本のゲ−トバスラインと複数本のデ−タバスライン及び各ゲ−トバスラインと各デ−タバスラインの終端に形成された複数のパッドなどが含まれた構造である。

【0003】

図1に示したように、従来の一般のアクティブマトリックス液晶表示装置のマトリックスアレイの各画素は互いに交差するゲ−トライン1とデ−タライン2があり、ゲ−トライン1から突設されたゲ−ト電極11と、ゲ−ト電極に重畳するアイランド状の非晶質シリコン層14と、デ−タライン2から突設されたソ−ス電極16と、ソ−ス電極16に対向形成されたドレイン電極17を含む薄膜トランジスタ3と、ドレイン電極17に連結されて形成された画素電極19を有し、隣り合うゲ−トライン1の一部領域である第1補助容量キャパシタ電極と、第1電極と絶縁層を挟んで重畳する画素電極19を第2補助容量キャパシタ電極とする補助容量キャパシタ4を有する。

【0004】

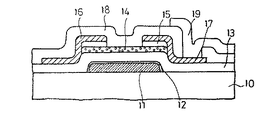

一方、図2に示したように、従来のアクティブマトリックス液晶表示装置のマトリックスアレイに形成される薄膜トランジスタは、絶縁基板10上に形成されたゲ−トラインの突起部のゲ−ト電極11と、ゲ−ト電極11と絶縁基板10の露出された表面上に形成された第1絶縁膜13と、第1絶縁膜13上に形成されチャネルが生成される、ド−プされていない非晶質シリコン層14とド−プされた非晶質シリコン層15があり、ド−プされた非晶質シリコン層15上に下部のゲ−ト電極11と一部重畳するように形成されたソ−ス電極16と、ソ−ス電極16に対称にゲ−ト電極11と一部重畳するように形成されたドレイン電極17と、ソ−ス/ドレイン電極16、17の上部に形成され絶縁基板を保護するパッシベ−ション層18と、パッシベ−ション層18に形成されたコンタクトホ−ルを介してドレイン電極17と連結形成された画素電極19がある。主として、ゲ−ト電極11は陽極酸化の可能な導電物質で形成してゲ−ト電極の表面に酸化絶縁膜12が形成されている。

【0005】

アクティブマトリックス液晶表示装置は高画質を具現するために高開口率が求められる。開口率とは画素面積のうち実際の光が透過する面積の比である。

【0006】

一般に、ゲ−トライン、デ−タライン、そして薄膜トランジスタ及び補助容量キャパシタの各電極部は不透明な導電物質で形成されるが、ゲ−トライン、デ−タライン及び薄膜トランジスタ領域の幅は電流伝達能力と関わり、補助容量キャパシタの大きさは画素に印加された電圧維持とフリッカ(Flicker)減少効果などとかかわり、前述した不透明な領域の縮小には限界があって開口率向上に制限要素として作用する。

【0007】

それで、従来にゲ−トライン上に薄膜トランジスタを形成して開口率を高めようとする技術が提案されている。図示していないが、この薄膜トランジスタの構造は直線形ゲ−トラインの一部領域のゲ−ト電極と、その上部に形成された第1絶縁膜と、第1絶縁膜上にアイランド状に形成された半導体層と、半導体層上に対向して形成されたソ−ス/ドレイン電極よりなり、ソ−ス電極はデ−タラインに突起部を形成してゲ−ト電極と一部重畳するように形成した構造であり、ドレイン電極は画素電極と連結されゲ−ト電極と一部重畳するように形成した構造である。従って、不透明な領域であるゲ−ト電極を別に形成せず、ゲ−トラインの一部領域を用いることにより開口率を向上させうる。

【0008】

しかし、ゲ−トライン上に薄膜トランジスタを形成した従来のアクティブマトリックス液晶表示装置は薄膜トランジスタの構造において、ゲ−トライン/絶縁層/ソ−ス電極及びドレイン電極のMIM(Metal-Insulator-Metal)構造により寄生容量が生ずるが、このうち画素電極と連結されたドレイン電極とゲ−トラインとの間に発生する寄生容量Cgdはその容量大きさが

Cgd = ε(Agd/dgd) (1)

であって、液晶の誘電率異方性により現れる画素電圧のレベルシフト値である△VPの値を決定する要素である。式(1)において、εはゲ−ト電極とドレイン電極との間に形成された誘電層、すなわち第1絶縁膜及び酸化絶縁膜の誘電率であり、Agdはゲ−ト電極とドレイン電極が重なる部位の面積であり、dgdはゲ−ト電極とドレイン電極との距離を意味する。

【0009】

一方、寄生容量Cgdと△VP との関係は、

△VP = VSC−VPC=Vg(Cgd/Ct) (2)

である。式(2)において、電圧VSCは信号電圧の中間値であり、電圧VPCはピクセル電極に印加される電圧の中間値であり、電圧Vgはゲ−ト電極に印加される電圧であり、全体容量CtはCgd+CS(補助容量)+CLC(液晶容量)である。

【0010】

式(2)において、寄生容量Cgdが補助容量CSや液晶容量CLCに比べて極めて小さいとすれば、分母Ct =CS +CLCとなって定数と仮定しうる。従って、画素レベルシフト値である△VPの大きさは寄生容量Cgdの大きさに比例することがわかる。

【0011】

△VPは液晶表示装置の残像、画素間の不均一、信頼性の劣化などの不良を誘発させる要因であって、良好な画像を得るためには△VPを小さくすべきである。式(2)によれば、△VPの値を低めるためには寄生容量Cgdの値を低めなければならなく、式(1)により、第1絶縁膜の誘電率(ε)を低めたり、距離dgdの値を大きくしたり、ゲ−ト電極とドレイン電極が重なる面積Agdを縮める方法がありうる。しかし、前述した二種の方法は素子の異なる電気的な特性を変化させうる。

【0012】

【発明が解決しようとする課題】

従って、本発明の目的は薄膜トランジスタをゲ−トライン上に形成させ高開口率化を追求しながら、従来のような寄生容量Cgdが大きくなる問題点を解決し得る構造の薄膜トランジスタを有するアクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにアクティブマトリックス液晶表示装置のマトリックスアレイの製造方法及び薄膜トランジスタ液晶表示装置の製造方法を提供することである。

【0013】

【課題を解決するための手段】

前述した本発明の目的を達成するために本発明は、アクティブマトリックス液晶表示装置のマトリックスアレイにおいて、絶縁基板と、前記絶縁基板上に平行に延設された複数のゲートラインと、前記ゲートラインと前記絶縁基板の露出された表面に形成された絶縁膜と、前記絶縁膜上で前記各ゲートラインに重畳して形成された複数のアイランド状の半導体層と、前記ゲートラインが延設された方向に突出するソース電極を有し、前記各半導体層上で前記ゲートラインに直角に交差する複数のデータラインと、前記各半導体層上で前記ソース電極に対向するように形成されたドレイン電極と、前記ゲートラインにより構成されるゲート電極とを包含して構成された複数の薄膜トランジスタと、前記ドレイン電極に接続され、前記ゲートラインとデータラインとによって定義される領域に形成された画素電極とを備えてなり、前記各半導体層上において、前記データライン及び該データラインから突出しているソース電極と前記ドレイン電極との対向部分がL字形に形成されていることを特徴とする。さらに、本発明は、アクティブマトリックス液晶表示装置のマトリックスアレイにおいて、絶縁基板と、前記絶縁基板上に第1方向に延設され、ゲート電極に当たる第1領域と隣接する前記第!領域を連結する第2領域を有するゲートラインと、前記ゲートラインと前記絶縁基板の露出された表面に形成された第1絶縁膜と、前記第1絶縁膜上で前記ゲートラインの第1領域に重畳して形成されたアイランド状の半導体層と、前記半導体層上で前記ゲートラインに交差し、前記ゲートラインの第1領域の上部で前記第1方向の突起部を有し、前記突起部とその一側部をソース電極と限定するデータラインと、前記半導体層上で前記ソース電極に応ずるように形成されたドレイン電極を含めてなる複数個の薄膜トランジスタと、前記ドレイン電極に連なり、前記ゲートラインの第2領域に重畳されるように形成される画素電極と、前記ゲートラインの第2領域の一部を第1補助容量キャパシタ電極とする補助容量キャパシタを備えることを特徴とする。

【0014】

また、本発明はアクティブマトリックス液晶表示装置のマトリックスアレイの製造方法において、絶縁基板上に第1導電層を形成する段階と、前記第1導電層をパタ−ン食刻して前記第1方向に延長されるゲ−トラインを形成する段階と、前記ゲ−トラインと前記絶縁基板の露出された部分に絶縁膜を形成する段階と、前記絶縁膜上に半導体層を形成する段階と、前記ゲ−トラインと前記基板の所定部分に重畳するように前記半導体層をパタ−ン食刻する段階と、前記基板の全面に第2導電層を形成する段階と、前記第2導電層をパタ−ン食刻して前記パタ−ン食刻された半導体層上に形成され、前記第1方向とは異なる方向である第2方向に延長され、前記パタ−ン食刻された半導体層に連結される突出部を有し、前記デ−タラインの内側の一部と前記突出部に限定されるソ−ス電極を有し、前記ゲ−トラインに電圧を印加する場合、前記デ−タラインの内側一部と前記突出部から電流が流れるように形成されるデ−タライン及び前記ソ−ス電極に対応し、前記ソ−ス電極とは所定距離を隔てて位置するドレイン電極を形成する段階を含む。

【0015】

【発明の実施の形態】

発明の実施の形態1.

以下、添付した図面に基づき本発明の望ましい実施例を詳述する。

【0016】

図3は本発明のアクティブマトリックス液晶表示装置のマトリックスアレイの実施の形態1であって、便宜上、一つの画素を中心として示した。絶縁基板(図示せず)上に直線状のゲ−トライン50が通り、ゲ−トライン50に交差して通るデ−タライン60がある。デ−タライン60はゲ−トラインと重畳する領域でゲ−トライン50の長手方向と同方向の突起部60−1を有する。また、デ−タラインの突起部60−1及びその一側のデ−タラインより構成されるソ−ス電極38に応じてドレイン電極39が形成されており、ドレイン電極39はコンタクトホ−ル43を介して上部の画素電極45に連結される。この際、ドレイン電極39はゲ−トライン50と一部領域が重畳され、デ−タラインの突起部60−1とデ−タライン60から等距離を有するように形成される。デ−タライン60及びデ−タラインの突起部60−1とドレイン電極39の下部には非晶質シリコン層36がアイランド状に形成されていて、チャネル領域46が非直線的、すなわちL形である。この際、電流はデ−タライン60の突出部60−1のみならずデ−タライン60のうち突出部の側面部でも流れる。その結果、チャネルが長くなるので同程度の電流が流れるようにする従来の薄膜トランジスタに比べてドレイン電極の物理的な大きさを減少させる。従って、本発明によれば、ドレイン電極は物理的にさらに小さくてゲ−ト電極とドレイン電極の重畳部分が小さくなり、発生される寄生容量Cgdが減少される。

【0017】

一方、補助容量キャパシタ75は次段のゲ−トライン50上に形成されるが、最下部に第1補助容量キャパシタ電極であるゲ−トライン50と、第2補助容量キャパシタ電極40が第1絶縁膜(図示せず)と非晶質シリコン層及びド−プされた非晶質シリコン層(図示せず)を挟んで形成されている。第2補助容量キャパシタ電極40はパッシベ−ション層(図示せず)で覆われ、パッシベ−ション層に形成されたコンタクトホ−ル44を介して画素電極45と連結される。

【0018】

また、図3の実施の形態は実質的に不透明な層、例えばブラックマトリックス(B/M:Black Matrix)層41を下部基板に備える。図3でさらに示されるように、デ−タライン60とゲ−トライン50の一部領域及び画素電極45の一部領域は互いに重なっている。

【0019】

図4(a)から図10(a)と図4(b)ないし図10(b)は本発明のアクティブマトリックス液晶表示装置のマトリックスアレイ製造方法の一実施の形態を示したもので、図4(a)ないし図10(a)は図3のII−II線に沿って切断した断面図であり、図4(b)ないし図10(b)は図3のIII−III線に沿って切断した断面図である。

【0020】

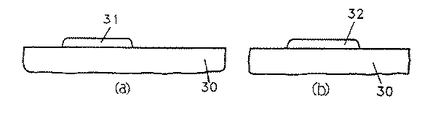

まず、図4(a)及び図4(b)に示したように、透明基板30上にスパッタ装置を用いて第1導電物質層を形成しパタニングしてゲ−トラインの一部領域であるゲ−ト電極31及び第1補助容量キャパシタ電極32を形成する。第1金属物質としてはアルミニウム、アルミニウム合金、モリブデン、モリブデン合金または陽極酸化可能な金属のうちいずれか一つを用いる。

【0021】

ついで、図5(a)と図5(b)に示したように、ゲ−ト電極31及び第1補助容量キャパシタ電極32を陽極酸化してそれぞれの表面に酸化絶縁膜33、34を形成する。次いで、酸化絶縁膜33、34及び絶縁基板30の露出された表面にシリコン酸化膜またはシリコン窒化膜を用いて単一または二重絶縁層を形成して第1絶縁膜35を形成する。

【0022】

引き続き、図6(a)及び図6(b)に示したように、第1絶縁膜上に非晶質シリコンとド−プされた非晶質シリコンを連続して積層した後、食刻工程でパタニングして薄膜トランジスタのゲ−ト電極31の上部及び補助容量キャパシタ電極32と重畳されるように水素化された非晶質シリコン層36とド−プされた非晶質シリコン層37を形成する。

【0023】

図7(a)及び図7(b)に示したように、非晶質シリコン層36、ド−プされた非晶質シリコン層37及び第1絶縁膜35の上部に第2導電物質を積層し、パタニングして突起部を有するデ−タライン60(図示せず)とドレイン電極39及び第2補助容量キャパシタ電極40を形成する。この際、デ−タライン60の突起部60−1及び突起部の側部のデ−タライン領域がソ−ス電極38となる。ソ−ス/ドレイン電極38、39をマスクとして乾式食刻してド−プされた非晶質シリコン層37を取り除く。この段階を経れば、ソース電極38はデータライン60の突起部60−1(図3)により定まる部分を備える。この部分は、非晶質シリコン層36及びドープされた非晶質シリコン層37の上部でドレイン電極39が対応的に非直線状、望ましくは直角に曲がるように、望ましくは曲がっていて、望ましくはL型である。したがって、曲がったチャネル領域46が得られる。

【0024】

図8(a)及び図8(b)に示したように、露出された表面の全面に不透明の絶縁物質であるブラック樹脂を積層しパタニングしてソ−ス電極38とドレイン電極39の一部及びゲ−ト電極31の上部などの光を遮断すべき領域にブラックマトリックス41を形成する。また、補助容量キャパシタの第2補助容量キャパシタ電極40の一部を覆うようにブラックマトシックス41を形成する。従って、ブラックマトリックス41は全体アレイ上で補助容量キャパシタの一部領域を除いたゲ−トラインとデ−タラインを覆うように形成される。

【0025】

図9(a)及び図9(b)に示したように、ブラックマトリックス41及び第1絶縁膜35などの露出された表面にスパッタまたは化学気相蒸着(CVD)装備を用いてシリコン酸化膜またはシリコン窒化膜でパッシベ−ション層42を形成した後、薄膜トランジスタのドレイン電極39及び補助容量キャパシタの第2補助容量キャパシタ電極40の一部領域が露出されるように乾式食刻してコンタクトホ−ル43、44を形成する。

【0026】

図10(a)及び図10(b)に示したように、全面に透明導電物質、望ましくはITO膜を積層し、続いて薄膜トランジスタのゲ−ト電極31の上部のパッシベ−ション層42を露出させ、補助容量キャパシタのブラックマトリックス41が形成された部位の上部に形成されたパッシベ−ション層42を露出させ、各画素毎に画素電極45を分離して形成する。この際、水平的に見れば、デ−タライン60に沿って画素電極45が互いに分離される。一方、画素電極45は予め形成されたコンタクトホ−ル43、44を介してドレイン電極39及び補助容量キャパシタの第2補助容量キャパシタ電極40に接触させる。

【0027】

発明の実施の形態2.

図11は本発明の実施の形態2であって、ソ−ス電極38の一部である突起部60−1に近接するデ−タライン60とドレイン電極38に一部重畳するようにゲ−トライン50に突起部50−1を形成したもので、基本的な構造は図3の実施の形態と同様なので説明を省く。

【0028】

図11に示したアクティブマトリックス液晶表示装置のマトリックスアレイはゲ−ト電極31と第1補助容量キャパシタ電極32、すなわちゲ−トライン50を形成しながら突起部50−1を形成する。その後、図5(a)ないし図10(a)と図5(b)ないし図10(b)に示した工程を進めて製造しうる。

【0029】

以上説明したような本発明のアクティブマトリックス液晶表示装置のマトリックスアレイは薄膜トランジスタをゲ−トラインの上部に形成して開口率の増加を図りながら従来とは異なり、簡単な作図法を通してわかるように、チャネル領域が非直線的に形成されうるので、チャネル長さの増加の効果があって同じチャネル長さの薄膜トランジスタを製造する場合、ゲ−トラインとドレイン電極との間に発生する寄生容量を最大限減らせる。従って、画素電圧のシフトレベル値である△VPを減らせてフリッカ現象及び画質の向上を期待できる。

【0030】

発明の実施の形態3.

図12は本発明の実施の形態3を示した平面図であって、エッチストッパがさらに追加された。本実施の形態3の基本的な構造は実施の形態1、2において示した通りであるが、その相違点は次の通りである。すなわち、適宜な大きさのコンタクトホ−ルがゲ−トライン82に形成され、このゲ−トライン82をマスクとして用いてエッチストッパが形成される。

【0031】

絶縁基板80上に直線状であり所定位置にコンタクトホ−ルTが形成されたゲ−トライン82が形成されている。コンタクトホ−ルの存するゲ−トライン82部分はコンタクトホ−ルによりゲ−ト領域と非ゲ−ト領域とに区分される。そして、ゲ−トライン82に交差してデ−タライン81が形成されている。デ−タライン81はゲ−トライン82と重畳される領域でゲ−トライン82の長手方向に位置し、ゲ−トライン82に形成されたコンタクトホ−ルTの一部を覆う突起部、すなわちソ−ス電極83に当たる部分を有している。本実施の形態3において、ソ−ス電極82はエッチストッパのコンタクトホ−ルを介して非晶質シリコン層86に接触される。そして、画素電極89がソ−ス電極83と同一導電物質で形成されたドレイン電極84に連結され形成されている。本発明の実施の形態3はゲ−トライン82から延設された突出部が部分的にデ−タライン81に重畳されている。ここで、ゲ−トラインは突出部を有さず、図3に示したように直線状をなすように形成することもできる。

【0032】

図13は図12のIV−IV線に沿って示した断面図である。

【0033】

ソ−ス電極83とドレイン電極84の下部には半導体活性層86が形成されており、その下部にゲ−トライン82のゲ−ト領域82−1が位置している。したがって、ソ−ス電極83、ドレイン電極84及び非晶質シリコン層86が形成された部位の下部に位置したゲ−トライン82の部分のゲ−ト領域82−1はスイッチング素子の機能を果たす薄膜トランジスタをなす。一方、すでに示したように、ソ−ス電極83とドレイン電極84の下部に位置した非晶質シリコン層86には非直線的なチャネル領域が形成されている。ドレイン電極84は保護膜85−2に形成されたコンタクトホ−ルを通して上部の画素電極89に連結される。そして、エッチストッパ87が走査線のゲ−ト領域82−1と同形状に半導体活性層86上にオミックコンタクト層80と接して形成されている。

【0034】

未説明の82−2はコンタクトホ−ルを挟んで両側に位置したゲ−トラインのうち非ゲ−ト領域を、85−1はゲ−ト絶縁膜を、88は走査線の表面上に形成される陽極酸化膜を示す。

【0035】

図14ないし図18は本発明の実施の形態3による液晶表示装置の製造工程図を図12のIV−IV線に沿って切断した図である。

【0036】

まず、図14に示したように、絶縁基板80上にスパッタ装備を用いて第1導電物質層を形成する。以後、導電層をパタ−ン食刻して所定部分にコンタクトホ−ルTが形成されたゲ−トライン82を形成する。コンタクトホ−ルのあるゲ−トライン部分は二つの領域82−1、82−2に分かれるが、このうち一つの領域82−1はゲ−ト領域となり、もう一つの領域は非ゲ−ト領域82−2となる。第1導電物質としてはアルミニウム、アルミニウム合金、モリブデン、モリブデン合金及び陽極酸化可能な金属のうちいずれか一つを用いる。以後、ゲ−トライン32の表面上に陽極酸化膜88を形成する。

【0037】

次いで、図15に示したように、陽極酸化膜上に第1絶縁膜85−1を形成する。この際、第1絶縁膜としてシリコン酸化膜あるいはシリコン窒化膜が使われる。以後、第1絶縁膜85−1上に非晶質シリコン層を積層した後、非晶質シリコン層をゲ−トラインのゲ−ト領域82−1に当たる部分に重畳するようにパタ−ン食刻する。

【0038】

その後、図16に示したように、非晶質シリコン層86と露出された第1絶縁膜85−1上にエッチストッパ用絶縁膜を形成する。以後、背面露光を施して非晶質シリコン層86と露出された第1絶縁膜85−1上にエッチストッパを形成する。その結果、ゲ−トライン82のコンタクトホ−ルと同位置にコンタクトホ−ルを有するエッチストッパ87が形成される。

【0039】

背面露光を用いたエッチストッパの形成は次のような一般の方法を用いて達成できる。

【0040】

非晶質シリコン層と露出された第1絶縁膜上にエッチストッパ用絶縁膜とポジティブ感光性を有するフォトレジスト層を連続的に蒸着する。以後、基板の背面で光を照射する背面露光を施す。したがって、光は走査線を除いた部分を通過してポジティブ型のフォトレジスト層に達することになる。その結果、フォトレジスト層の露光部分は弱化され、非露光部分は硬化した状態に残る。その後、現像過程を施せば、フォトレジストの非露光部分、すなわち走査線のような形状を有するフォトレジストパタ−ンが形成される。このフォトレジストパタ−ンをマスクとして下部に存するエッチストッパ用絶縁膜を食刻する。従って、形成されるエッチストッパは走査線と同様な形状を有する。本実施の形態ではエッチストッパを形成するための別のマスクを必要としない。以後、次の工程のためにフォトレジストパタ−ンを取り除く。

【0041】

次いで、図17に示したように、エッチストパ87、露出された非晶質シリコン層及び露出された第1絶縁膜上にド−プされた非晶質シリコン層と第2導電層を連続的に形成する。以後、所定の形状通り第2導電層をパタ−ン食刻して突出部を有するデ−タライン82とドレイン電極84を形成する。以後、デ−タラインとドレイン電極34をマスクとして下部に存するド−プされた非晶質シリコン層を食刻してオミックコンタクト層87を形成する。

【0042】

この際、デ−タラインの突出部と突出部の近傍のデ−タラインの内側の一部がソ−ス電極83に限定される。従って、平面図(図12)に示したように非直線形、すなわちL形のチャネルが得られる。

【0043】

図18に示したように、露出された基板の表面にスパッタ装置を用いてシリコン酸化膜あるいはシリコン窒化膜よりなる保護膜85−2を形成する。以後、保護膜85−2をパタ−ン食刻してドレイン電極84の一部を露出させるコンタクトホ−ルを形成する。

【0044】

その後、保護膜85−2とドレイン電極84の露出された表面に透明導電膜を蒸着した後、パタ−ン食刻してドレイン電極84に連結される画素電極89を形成する。

【0045】

図19及び図20は本発明による第3実施例の他の製造方法を説明するための図であって、図12のIV−IV切断線に沿って示した工程図である。

【0046】

前述した製造方法により完成されるエッチストッパはゲ−トラインのような形状を有している。ところが、エッチストッパはオミックコンタクト層を食刻する過程で生ずる半導体活性層の食刻を防止するために形成するものなので、半導体活性層上にのみ形成することもできる。

【0047】

まず、図14で説明したように、絶縁基板上にコンタクトホ−ル、ゲ−ト領域82−1及び非ゲ−ト領域82−2を有するゲ−トラインと陽極酸化膜88を形成する。

【0048】

その後、図19に示したように、第1絶縁膜85−1、非晶質シリコン層86a、エッチストッパ用絶縁膜を蒸着し続ける。図16に基づき説明したように、一般の背面露光方法を用いてエッチストッパ用絶縁膜を形成する。従って、ゲ−トラインのような形状を有するエッチストッパ87が得られる。

【0049】

その後、図20に示したように、走査線のような形状を有するエッチストッパ87をパタ−ン食刻して所定部分のみ残し全部取り除く。すなわち、走査線のゲ−ト領域82−1に当たる部分にのみエッチストッパ87を残すが、これは予め作られたマスクパタ−ンを用いて得られる。以後、全面に蒸着された非晶質シリコン層86aをパタ−ン食刻してエッチストッパ87の外側に所定部分が露出する非晶質シリコン層86を形成する。

【0050】

次いで、図17ないし図18を参照して説明した通り、後続工程を進行してオミックコンタクト層、信号線、ソ−ス電極、ドレイン電極、保護膜及び画素電極を形成する。

【0051】

【発明の効果】

以上述べたように、本発明のアクティブマトリックス液晶表示装置のマトリックスアレイによれば、薄膜トランジスタをゲ−トラインの上部に形成して開口率の増加を図りながら、簡単な作図法を通してわかるように、従来とは異なりチャネル領域が非直線的に形成されうるのでチャネル長さの増加の効果があり、同一チャネル長さの薄膜トランジスタを製造する場合、ゲ−トラインとドレイン電極との間に発生する寄生容量を減らすことができる。従って、画素電圧のシフトレベル値である△VPを減らせてフリッカ現象及び画質の向上が図れる。

【0052】

また、ゲ−トライン上にコンタクトホ−ルを形成する場合は開口率を減少させなく背面露光によりエッチストッパを容易に形成しうる。すなわち、マスクを別に備えなくても予め形成されたゲ−トラインをマスクとして用いてエッチストッパを形成できて工程上有利である。

【図面の簡単な説明】

【図1】従来の液晶表示装置の平面図である。

【図2】図1のI−I線に沿って切断した断面図である。

【図3】本発明によるアクティブマトリックスLCDのマトリックスアレイの実施の形態1を示した平面図である。

【図4】図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図5】図4の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図6】図5の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図7】図6の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図8】図7の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図9】図8の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図10】図9の工程に続く、図3のII−II線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(a)、図3のIII−III線に沿って切断して示した本発明の実施の形態1による液晶表示装置の製造工程図(b)である。

【図11】本発明によるアクティブマトリックスLCDのマトリックスアレイの実施の形態2を示した平面図である。

【図12】本発明によるアクティブマトリックスLCDのマトリックスアレイの実施の形態3を示した平面図である。

【図13】図12のIV−IV線に沿って切断して示した断面図である。

【図14】図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の製造工程図である。

【図15】図14の工程に続く、図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の製造工程図である。

【図16】図15の工程に続く、図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の製造工程図である。

【図17】図16の工程に続く、図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の製造工程図である。

【図18】図17の工程に続く、図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の製造工程図である。

【図19】図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の他の製造工程図である。

【図20】図19の工程に続く、図12のIV−IV線に沿って切断して示した本発明の実施の形態3による液晶表示装置の他の製造工程図である。

【符号の説明】

50 ゲ−トライン

60 デ−タライン

60−1 突起部

38 ソ−ス電極

39 ドレイン電極

45 画素電極

40 第2補助容量キャパシタ電極

70 薄膜トランジスタ

75 補助容量キャパシタ

Claims (36)

- 薄膜トランジスタを含むアクティブマトリックス液晶表示装置において、

絶縁基板、

前記絶縁基板上に第1方向に延設され、前記薄膜トランジスタのゲート電極に相当する第1領域と隣接する前記第1領域を連結する第2領域を有するゲートライン、

前記ゲートライン上に形成された絶縁膜、

前記絶縁膜上で前記ゲートラインの第1領域に重畳して形成されたアイランド状の半導体層、

前記絶縁基板上に前記第1方向と略直角な第2方向に延設され前記ゲートラインとの交差部を有するデータラインであって、前記半導体層と重畳するよう前記交差部付近から前記第1方向に突出した突起部を前記薄膜トランジスタのソース電極として含むデータラインと、

前記半導体層上で前記突起部ソース電極に対応するように形成された前記薄膜トランジスタのドレイン電極、及び

前記ドレイン電極に連結された画素電極とからなり、

前記データラインは、前記交差部において前記第2方向に延設されたその一部箇所が前記半導体層と重畳しており、それにより前記第1方向の突起部ソース電極と前記ドレイン電極との間及び前記データラインの前記半導体層と重畳している前記第2方向の一部箇所と前記ドレイン電極との間に前記薄膜トランジスタのL字状チャネルが形成されていることを特徴とする液晶表示装置。 - 前記薄膜トランジスタの前記ソース電極と前記ドレイン電極、前記ゲートライン、及び前記データラインの上部に形成され、前記画素電極と一部重畳して形成されたブラックマトリックスをさらに含むことを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 前記ゲートラインの第2領域の一部を第1補助容量キャパシタ電極とする補助容量キャパシタとを備え、前記第1補助容量キャパシタ電極の一部領域と重畳するように前記第1補助容量キャパシタの上部に形成されたブラックマトリックスをさらに含むことを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 前記補助容量キャパシタは、

前記ゲートラインの第2領域の一部領域である第1補助容量キャパシタ電極と、

前記第1補助容量キャパシタ電極と前記絶縁基板の露出された表面上に形成された電極絶縁膜と、

前記電極絶縁膜上に形成された半導体層と、

前記半導体層上に形成された第2補助容量キャパシタ電極と、

前記第2補助容量キャパシタ電極の一部を覆うブラックマトリックスと、

前記電極絶縁膜と前記第2補助容量キャパシタ電極と前記ブラックマトリックスの露出された表面に形成され、前記第2補助容量キャパシタ電極の上部にコンタクト領域が限定されたパッシベーション層と、

前記コンタクト領域を介して前記第2補助容量キャパシタ電極と連結された画素電極とを含めてなることを特徴とする請求項3に記載のアクティブマトリックス液晶表示装置。 - 前記ゲートラインは直線形であり、同一な幅を有することを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 前記ゲートラインは前記ソース電極の一部と前記ドレイン電極に一部重畳される突起部を有することを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 前記ソース電極と前記ドレイン電極は、前記薄膜トランジスタで角をなすチャネル領域を形成することを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 前記ソース電極と前記ドレイン電極が形成するチャネル領域は、前記ゲートラインの線幅内で前記ドレイン電極を囲むことを特徴とする請求項1に記載のアクティブマトリックス液晶表示装置。

- 液晶表示装置において、

第1方向に延設されるゲートライン、

前記ゲートラインとの交差部を有するように前記第1方向と異なる第2方向に延設され、前記交差部付近で前記第1方向に突出される突起部としての第1領域と前記第1領域に隣り合う前記第2方向の第2領域を有するデータライン、及び

前記交差部付近で前記ゲートライン上に形成された薄膜トランジスタであって、ゲート電極、絶縁膜、半導体層、ソース電極及び液晶画素電極に接続されたドレイン電極とからなる薄膜トランジスタとからなり、

前記ゲートラインの一部が前記ゲート電極を形成しており、前記データラインの第1領域と第2領域が前記半導体層と重畳して前記ソース電極を形成しており、及び前記ドレイン電極が前記半導体層と重畳しており、それにより前記データラインの第1領域と前記ドレイン電極との間及び前記データラインの第2領域と前記ドレイン電極との間にL字状の薄膜トランジスタ・チャネルが形成されていることを特徴とする液晶表示装置。 - 前記データラインの第2領域は前記データラインの第1領域に接触することを特徴とする請求項9に記載の液晶表示装置。

- 前記ゲートラインと前記データラインは基板上に形成され、前記データラインの第1領域及び第2領域は前記基板の所定部分を限定し、前記ソース電極が前記基板の所定部分に重畳されることを特徴とする請求項10に記載の液晶表示装置。

- 前記第1方向と前記第2方向は互いに垂直であることを特徴とする請求項9に記載の液晶表示装置。

- 前記データラインの第1領域及び第2領域に重畳されるブラックマトリックスを形成することを特徴とする講求項9に記載の液晶表示装置。

- 前記データラインの前記第1領域、前記第2領域の上部領域及び前記ゲートラインの第1領域に重畳され、前記ゲートラインの第2領域を露出させるブラックマトリックスと、

前記ゲートラインの第2領域を電極として使う補助容量キャパシタをさらに含むことを特徴とする請求項9に記載の液晶表示装置。 - 前記ドレイン電極に連結され、その一部が前記ブラックマトリックス上に形成される画素電極をさらに含むことを特徴とする請求項13に記載の液晶表示装置。

- 前記ゲートラインの第2領域に一部が重畳され、前記ストレージキャパシタの一電極として使われる画素電極をさらに含むことを特徴とする請求項14に記載の液晶表示装置。

- 前記ゲートラインは、前記交差部付近で前記半導体層に重畳して前記第2の方向に突出するゲート突出部を有し、前記ゲート突出部は前記薄膜トランジスタの付加的ゲート電極をなしており、前記L字状チャネルが前記付加的ゲート電極の重畳する前記半導体層部分にも形成されていることを特徴とする請求項9に記載の液晶表示装置。

- 前記第1方向と前記第2方向は互いに垂直であることを特徴とする請求項17に記載の液晶表示装置。

- 前記データラインの前記第2領域は前記ゲート突出部とは重畳していることを特徴とする請求項17に記載の液晶表示装置。

- 前記ゲートラインと前記データラインは前記基板上に形成され、前記データラインの第1領域及び第2領域は前記基板の所定部分を限定し、前記ソース電極が前記基板の所定部分に重畳することを特徴とする講求項17に記載の液晶表示装置。

- 薄膜トランジスタを含むアクティブマトリックス液晶表示装置において、

絶縁基板、

前記絶縁基板上に第1方向に延設され、前記薄膜トランジスタのゲート領域に当たる第1領域と、非ゲート領域に当たる第2領域と、前記第1領域と前記第2領域に近接するコンタクトホールを有するゲートライン、

前記ゲートラインと前記露出された絶縁基板上に形成される絶縁膜、

前記ゲートラインのコンタクトホールの一部と第1領域に重畳されるアイランド状の前記薄膜トランジスタの半導体活性層と、

前記半導体活性層の一部を露出させるように形成されるエッチストッパ、

前記ゲートラインとの交差部を有するデータラインであって、前記交差部付近で前記第1方向に形成された前記半導体活性層に重畳された突出部である第1領域と前記第1領域に隣接し前記半導体活性層に重畳する第2領域を有し、前記データラインの突出部と前記データラインの第2領域が前記薄膜トランジスタのソース電極をなしているデータライン、及び

前記半導体活性層に重畳し、液晶画素電極と連結された前記薄膜トランジスタのドレイン電極とからなり、

前記データラインの突出部である第1領域と前記ドレイン電極との間及び前記データラインの第2領域と前記ドレイン電極との間に前記薄膜トランジスタのL字状チャネルが形成されていることを特徴とする液晶表示装置。 - 前記エッチストッパは、第1領域と第2領域を有するゲートラインの形状と同一であることを特徴とする請求項21に記載のアクティブマトリックス液晶表示装置。

- 前記エッチストッパは、前記ゲートラインの第1領域と同形状で形成されることを特徴とする講求項21に記載のアクティブマトリックス液晶表示装置。

- 前記ゲートラインは直線形で形成され、均一な幅を有することを特徴とする講求項21に記載のアクティブマトリックス液晶表示装置。

- 前記ゲートラインは前記ドレイン電極と前記ソース電極の一部に重畳される突出部を有することを特徴とする講求項21に記載のアクティブマトリックス液晶表示装置。

- 前記ソース電極と前記ドレイン電極は、前記薄膜トランジスタで角をなすチャネル領域を形成することを特徴とする請求項21に記載のアクティブマトリックス液晶表示装置。

- 請求項1又は9に記載のアクティブマトリックス液晶表示装置の製造方法において、

絶縁基板上に第1導電層を形成する段階と、

前記第1導電層をパターン食刻して前記第1方向に延長される前記ゲートラインを形成する段階と、

前記ゲートラインと前記絶縁基板の露出された部分に前記絶縁膜を形成する段階と、

前記絶縁膜上に前記半導体層を形成する段階と、

前記ゲートラインと前記基板の所定部分に重畳するように前記半導体層をパターン食刻する段階と、

前記基板の全面に第2導電層を形成する段階と、

前記第2導電層をパターン食刻して、前記パターン食刻された前記半導体層上に重畳的に形成された前記パターン食刻された半導体層に連結される前記データラインの突起部を形成する製造方法。 - 前記基板の露出部分に透明導電層を形成する段階と、

前記透明導電層をパターン食刻して前記ドレイン電極に連結される画素電極を形成する段階とをさらに含むことを特徴とする請求項27に記載のアクティブマトリックス不液晶表示装置の製造方法。 - 前記パターン食刻された半導体層に重畳するブラックマトリックスを形成することを特徴とする請求項27に記載のアクティブマトリックス液晶表示装置の製造方法。

- 前記第1方向は前記第2方向に垂直であることを特徴とする請求項27に記載のアクティブマトリックス液晶表示装置のマトリックスアレイの製造方法。

- 請求項21に記載の液晶表示装置の製造方法において、

前記絶縁基板上に第1導電層を積層する段階と、

前記第1導電層をパターン食刻して前記ゲートラインを形成する段階と、

前記ゲートラインと前記絶縁基板の露出された表面に第1絶縁膜を積層する段階と、

前記第1絶縁膜上に非晶質シリコン層を積層する段階と、

前記非晶質シリコン層をパターン食刻して前記半導体活性層を形成する段階と、

前記半導体活性層上と前記第1絶縁膜の露出された表面に前記エッチストッパ用の絶縁膜を積層する段階と、

前記エッチストッパ用の絶縁膜を背面露光工程を用いてパターン食刻して前記ゲートラインを形成して前記半導体活性層の一部を露出させる前記エッチストッパを形成する段階と、

前記エッチストッパ上と前記半導体活性層の露出された表面にドープされた非晶質シリコン層と第2導電層を順次に積層する段階と、

前記第2導電層と前記ドープされた非晶質層をパターン食刻して前記データラインと、前記ドレイン電極を形成する段階とを含むことを特徴とする製造方法。 - 前記背面露光工程を用いる前記エッチストッパの形成段階は、

前記エッチストッパ用の絶縁膜上に所定の感光性を有するフォトレジスト層を連続蒸着する段階と、

前記基板の背面で前記走査線をマスクとして前記フォトレジスト層を選択露光する段階と、

前記選択露光されたフォトレジスト層を現像してフォトレジストパターンを形成する段階と、

前記フォトレジストパターンをマスクとして前記エッチストッパ用の絶縁膜を食刻してエッチストッパを形成する段階を含むことを特徴とする請求項31に記載の製造方法。 - 前記基板の全面に第2絶縁膜を積層する段階と、

前記第2絶縁膜をパターン食刻して前記ドレイン電極の一都を露出させるコンタクトホールを形成する段階と、

前記コンタクトホールを介して前記ドレイン電極に連結される画素電極を形成する段階とをさらに含むことを特徴とする請求項31に記載の液晶表示装置の製造方法。 - 請求項21に記載の液晶表示装置の製造方法において、

絶縁基板上に第1導電層を積層する段階と、

前記第1導電層をパターン食刻して前記ゲート領域と、前記ゲート領域の一側に置かれる前記コンタクトホールと、前記ゲート領域と前記コンタクトホールに連結される前記非ゲート領域を有する前記ゲートラインを形成する段階と、

前記ゲートラインと前記絶縁基板の露出された表面に第1絶縁膜、非晶質シリコン層、エッチストッパ用の絶縁膜を連続積層する段階と、

前記エッチストッパ用の絶縁膜を背面露光工程を用いてパターン食刻して前記ゲートラインの形状通り形成され前記非晶質シリコン層の一部を露出させてエッチストッパを形成する段階と、

前記エッチストッパをパターン食刻して前記ゲート領域に当たる部分のみ残留させる段階と、

前記非晶質シリコン層をパターン食刻して前記エッチストッパの外側に露出される前記半導体活性層を形成する段階と、

全面にドープされた非晶質シリコン層と第2導電層を順次に積層する段階と、

前記第2導電層と前記ドープされた非晶質層をパターン食刻して前記半導体活性層に一部が接する前記ソース電極と、前記ソース電極に連結される信号線と、前記ドレイン電極を形成する段階とを含むことを特徴とする薄膜トランジスタ液晶表示装置の製造方法。 - 絶縁基板と、

前記絶縁基板上に平行に延設された複数のゲートラインと、

前記各ゲートラインに重畳して形成された複数のアイランド状の半導体層と、

前記ゲートラインに直角に交差する複数のデータラインであって、前記交差付近で前記ゲートラインが延設された方向に突出する突起電極を有するデータラインと、

前記各半導体層上で前記突起電極に対向するように形成されたドレイン電極と、前記ゲートラインにより構成されるゲート電極とを各々が含む複数の薄膜トランジスタと、

前記ドレイン電極に接続され、前記ゲートラインとデータラインとによって定義される領域に形成された画素電極とを備えてなり、

前記各半導体層において、前記データラインの前記突起電極に隣接する部分及び該データラインの突起電極と前記ドレイン電極との対向部分が前記薄膜トランジスタのL字状チャネルとなっていることを特徴とするアクティブマトリックス液晶表示装置。 - 各ゲートラインの一部に、該ゲートラインの一部を第1電極とし、隣接する画素領域の画素電極の一部を第2電極とする補助容量キャパシタが形成されていることを特徴とする請求項35に記載のアクティブマトリックス液晶表示装置のマトリックスアレイ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1019950043742A KR0158260B1 (ko) | 1995-11-25 | 1995-11-25 | 엑티브 매트릭스 액정표시장치의 매트릭스 어레이 및 제조방법 |

| KR95-43742 | 1995-11-25 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH09292632A JPH09292632A (ja) | 1997-11-11 |

| JP3654474B2 true JP3654474B2 (ja) | 2005-06-02 |

Family

ID=19435726

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31150896A Expired - Lifetime JP3654474B2 (ja) | 1995-11-25 | 1996-11-22 | アクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US5694185A (ja) |

| JP (1) | JP3654474B2 (ja) |

| KR (1) | KR0158260B1 (ja) |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0926603A (ja) * | 1995-05-08 | 1997-01-28 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| US5835177A (en) * | 1995-10-05 | 1998-11-10 | Kabushiki Kaisha Toshiba | Array substrate with bus lines takeout/terminal sections having multiple conductive layers |

| KR100195269B1 (ko) * | 1995-12-22 | 1999-06-15 | 윤종용 | 액정표시장치의 제조방법 |

| JPH09265113A (ja) * | 1996-03-28 | 1997-10-07 | Nec Corp | アクティブマトリクス型液晶表示装置およびその製造方 法 |

| KR100192447B1 (ko) * | 1996-05-15 | 1999-06-15 | 구자홍 | 액정표시장치의 제조방법 |

| JP2776376B2 (ja) * | 1996-06-21 | 1998-07-16 | 日本電気株式会社 | アクティブマトリクス液晶表示パネル |

| JP3126661B2 (ja) * | 1996-06-25 | 2001-01-22 | 株式会社半導体エネルギー研究所 | 液晶表示装置 |

| JP3634089B2 (ja) * | 1996-09-04 | 2005-03-30 | 株式会社半導体エネルギー研究所 | 表示装置 |

| KR100247493B1 (ko) * | 1996-10-18 | 2000-03-15 | 구본준, 론 위라하디락사 | 액티브매트릭스기판의 구조 |

| KR100251512B1 (ko) | 1997-07-12 | 2000-04-15 | 구본준 | 횡전계방식 액정표시장치 |

| KR100458834B1 (ko) * | 1997-09-09 | 2005-05-27 | 삼성전자주식회사 | 액정표시장치 |

| KR100293436B1 (ko) * | 1998-01-23 | 2001-08-07 | 구본준, 론 위라하디락사 | 횡전계방식액정표시장치 |

| KR100542303B1 (ko) * | 1998-08-24 | 2006-04-06 | 비오이 하이디스 테크놀로지 주식회사 | 액정 표시 장치 |

| US6809787B1 (en) * | 1998-12-11 | 2004-10-26 | Lg.Philips Lcd Co., Ltd. | Multi-domain liquid crystal display device |

| KR100430232B1 (ko) * | 1998-12-21 | 2004-12-31 | 엘지.필립스 엘시디 주식회사 | 액정표시장치및액정표시장치의축적캐패시터 |

| KR100357216B1 (ko) * | 1999-03-09 | 2002-10-18 | 엘지.필립스 엘시디 주식회사 | 멀티도메인 액정표시소자 |

| KR100620845B1 (ko) * | 1999-04-02 | 2006-09-06 | 엘지.필립스 엘시디 주식회사 | 멀티도메인 액정표시소자 제조방법 |

| KR100627107B1 (ko) | 1999-07-31 | 2006-09-25 | 엘지.필립스 엘시디 주식회사 | 멀티 도메인 액정표시소자 및 그 제조방법 |

| KR100348995B1 (ko) * | 1999-09-08 | 2002-08-17 | 엘지.필립스 엘시디 주식회사 | 4 마스크를 이용한 액정표시소자의 제조방법 및 그에 따른 액정표시소자 |

| KR100370800B1 (ko) * | 2000-06-09 | 2003-02-05 | 엘지.필립스 엘시디 주식회사 | 액정표시장치용 어레이기판 제작방법 |

| US7072017B1 (en) * | 2000-06-29 | 2006-07-04 | Lg. Philips Lcd Co., Ltd. | Multi-domain liquid crystal display device having a common-auxiliary electrode and dielectric structures |

| TWI284240B (en) * | 2000-09-27 | 2007-07-21 | Matsushita Electric Ind Co Ltd | Liquid crystal display device |

| KR20020042898A (ko) | 2000-12-01 | 2002-06-08 | 구본준, 론 위라하디락사 | 액정표시장치용 어레이기판과 그 제조방법 |

| KR100776509B1 (ko) * | 2000-12-30 | 2007-11-16 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

| KR20040043116A (ko) | 2001-04-10 | 2004-05-22 | 사르노프 코포레이션 | 유기 박막 트랜지스터를 이용한 고성능 액티브 매트릭스화소 제공방법 및 제공장치 |

| KR100731037B1 (ko) * | 2001-05-07 | 2007-06-22 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 및 그 제조방법 |

| KR100459211B1 (ko) * | 2001-05-25 | 2004-12-03 | 엘지.필립스 엘시디 주식회사 | 폴리실리콘 박막트랜지스터 및 그 제조방법 그리고, 이를적용한 액정표시소자의 제조방법 |

| KR100391157B1 (ko) * | 2001-10-25 | 2003-07-16 | 엘지.필립스 엘시디 주식회사 | 액정 표시 장치용 어레이 기판 및 그의 제조 방법 |

| KR100737702B1 (ko) * | 2002-10-16 | 2007-07-10 | 엘지.필립스 엘시디 주식회사 | 액정표시장치 |

| KR100902244B1 (ko) * | 2002-12-31 | 2009-06-11 | 엘지디스플레이 주식회사 | 박막 트랜지스터형 액정 표시 장치 |

| KR101027866B1 (ko) * | 2003-12-18 | 2011-04-07 | 엘지디스플레이 주식회사 | 액정표시장치 |

| NL1025134C2 (nl) * | 2003-12-24 | 2005-08-26 | Lg Philips Lcd Co | Organische licht emitterende diode-inrichting van de soort met actieve matrix en daarvoor bestemde dunne-filmtransistor. |

| CN100476554C (zh) * | 2004-08-31 | 2009-04-08 | 卡西欧计算机株式会社 | 垂直取向型有源矩阵液晶显示元件 |

| US20060066791A1 (en) * | 2004-09-30 | 2006-03-30 | Casio Computer Co., Ltd. | Vertical alignment active matrix liquid crystal display device |

| CN100492141C (zh) * | 2004-09-30 | 2009-05-27 | 卡西欧计算机株式会社 | 垂直取向型有源矩阵液晶显示元件 |

| TWI290649B (en) * | 2004-11-29 | 2007-12-01 | Casio Computer Co Ltd | Vertical alignment active matrix liquid crystal display device |

| KR100752876B1 (ko) * | 2004-11-30 | 2007-08-29 | 가시오게산키 가부시키가이샤 | 수직배향형의 액정표시소자 |

| US8068200B2 (en) | 2004-12-24 | 2011-11-29 | Casio Computer Co., Ltd. | Vertical alignment liquid crystal display device in which a pixel electrode has slits which divide the pixel electrode into electrode portions |

| JP4639797B2 (ja) * | 2004-12-24 | 2011-02-23 | カシオ計算機株式会社 | 液晶表示素子 |

| KR101127833B1 (ko) * | 2005-06-28 | 2012-03-20 | 엘지디스플레이 주식회사 | 액정 표시 장치 |

| TW200706955A (en) * | 2005-08-08 | 2007-02-16 | Innolux Display Corp | In-plane switching liquid crystal display device |

| US8023054B2 (en) * | 2005-12-30 | 2011-09-20 | Lg Display Co., Ltd. | Flat panel display and fabricating method thereof |

| US9570469B2 (en) | 2012-10-29 | 2017-02-14 | Sharp Kabushiki Kaisha | Active-matrix substrate and liquid-crystal display device |

| CN109377965B (zh) * | 2018-12-21 | 2021-06-25 | 信利半导体有限公司 | 异形像素驱动单元、像素驱动阵列及显示设备 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5327001A (en) * | 1987-09-09 | 1994-07-05 | Casio Computer Co., Ltd. | Thin film transistor array having single light shield layer over transistors and gate and drain lines |

| US5032883A (en) * | 1987-09-09 | 1991-07-16 | Casio Computer Co., Ltd. | Thin film transistor and method of manufacturing the same |

| JP2543286B2 (ja) * | 1992-04-22 | 1996-10-16 | インターナショナル・ビジネス・マシーンズ・コーポレイション | 液晶表示装置 |

| NL194848C (nl) * | 1992-06-01 | 2003-04-03 | Samsung Electronics Co Ltd | Vloeibaar-kristalindicatorinrichting. |

| US5459596A (en) * | 1992-09-14 | 1995-10-17 | Kabushiki Kaisha Toshiba | Active matrix liquid crystal display with supplemental capacitor line which overlaps signal line |

-

1995

- 1995-11-25 KR KR1019950043742A patent/KR0158260B1/ko not_active IP Right Cessation

-

1996

- 1996-04-29 US US08/639,617 patent/US5694185A/en not_active Expired - Lifetime

- 1996-11-22 JP JP31150896A patent/JP3654474B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH09292632A (ja) | 1997-11-11 |

| US5694185A (en) | 1997-12-02 |

| KR0158260B1 (ko) | 1998-12-15 |

| KR970028666A (ko) | 1997-06-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3654474B2 (ja) | アクティブマトリックス液晶表示装置のマトリックスアレイ及び液晶表示装置並びにその製造方法 | |

| US5942310A (en) | Liquid crystal display with increased aperture ratio | |

| JP3941032B2 (ja) | 垂直薄膜トランジスタを有する薄膜トランジスタ液晶表示素子 | |

| JP4304216B2 (ja) | 液晶表示装置用アレイ基板とその製造方法 | |

| US5473168A (en) | Thin film transistor | |

| JP4301259B2 (ja) | 液晶表示装置及びその製造方法 | |

| US6927815B2 (en) | Thin film transistor liquid crystal display and method for manufacturing the same | |

| TWI238370B (en) | Liquid crystal display device | |

| US6812975B2 (en) | Active matrix type display | |

| US5835169A (en) | Liquid crystal display device of thin film transistor and fabrication method thereof | |

| JPH10228035A (ja) | 液晶表示装置及びその製造方法 | |

| JP4716782B2 (ja) | 液晶表示装置及びその製造方法 | |

| JP3924384B2 (ja) | 薄膜トランジスタ | |

| US6411347B1 (en) | Storage capacitor in a liquid crystal display and a method of manufacturing thereof | |

| KR100262404B1 (ko) | 초고개구율 액정 표시 소자 및 그의 제조방법 | |

| JP4900332B2 (ja) | 液晶表示装置の製造方法 | |

| JP4182779B2 (ja) | 表示装置およびその製造方法 | |

| JP2001066633A (ja) | 液晶表示装置および投射型液晶表示装置 | |

| KR100192507B1 (ko) | 티에프티-엘씨디의 구조 및 제조방법 | |

| KR100322965B1 (ko) | 액정표시소자의 제조방법 | |

| JP4946250B2 (ja) | 液晶表示装置 | |

| KR20020034271A (ko) | 액정표시장치용 어레이기판과 그 제조방법 | |

| KR100272309B1 (ko) | 초고개구율 액정 표시 소자 및 그의 제조방법 | |

| JPH08236777A (ja) | 半導体装置 | |

| JP4075220B2 (ja) | 表示パネル及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040512 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20040812 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20040817 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050202 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050224 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080311 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090311 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090311 Year of fee payment: 4 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090311 Year of fee payment: 4 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100311 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120311 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130311 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140311 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |