JP3615979B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP3615979B2 JP3615979B2 JP2000013895A JP2000013895A JP3615979B2 JP 3615979 B2 JP3615979 B2 JP 3615979B2 JP 2000013895 A JP2000013895 A JP 2000013895A JP 2000013895 A JP2000013895 A JP 2000013895A JP 3615979 B2 JP3615979 B2 JP 3615979B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- insulating film

- silicon

- atoms

- oxygen

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

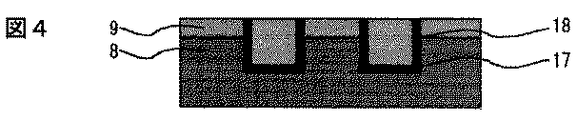

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

- H01L21/76808—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures involving intermediate temporary filling with material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02318—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment

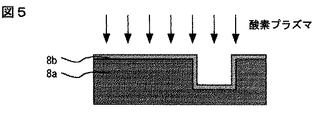

- H01L21/02337—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour

- H01L21/0234—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer post-treatment treatment by exposure to a gas or vapour treatment by exposure to a plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76807—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics for dual damascene structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

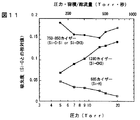

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/5329—Insulating materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

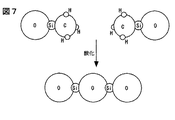

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02211—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02214—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen

- H01L21/02216—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound comprising silicon and oxygen the compound being a molecule comprising at least one silicon-oxygen bond and the compound having hydrogen or an organic group attached to the silicon or oxygen, e.g. a siloxane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Plasma & Fusion (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Formation Of Insulating Films (AREA)

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013895A JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

| TW090101031A TW513763B (en) | 2000-01-18 | 2001-01-17 | Semiconductor device and process for producing the same |

| US09/760,777 US6358838B2 (en) | 2000-01-18 | 2001-01-17 | Semiconductor device and process for producing the same |

| KR1020010002929A KR100689917B1 (ko) | 2000-01-18 | 2001-01-18 | 반도체 장치 및 그 제조 방법 |

| US10/050,859 US6680541B2 (en) | 2000-01-18 | 2002-01-18 | Semiconductor device and process for producing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000013895A JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001203200A JP2001203200A (ja) | 2001-07-27 |

| JP2001203200A5 JP2001203200A5 (enExample) | 2004-12-24 |

| JP3615979B2 true JP3615979B2 (ja) | 2005-02-02 |

Family

ID=18541427

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000013895A Expired - Fee Related JP3615979B2 (ja) | 2000-01-18 | 2000-01-18 | 半導体装置及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US6358838B2 (enExample) |

| JP (1) | JP3615979B2 (enExample) |

| KR (1) | KR100689917B1 (enExample) |

| TW (1) | TW513763B (enExample) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000174123A (ja) * | 1998-12-09 | 2000-06-23 | Nec Corp | 半導体装置及びその製造方法 |

| US6500752B2 (en) * | 2000-07-21 | 2002-12-31 | Canon Sales Co., Inc. | Semiconductor device and semiconductor device manufacturing method |

| JP4270865B2 (ja) * | 2000-08-18 | 2009-06-03 | 三菱電機株式会社 | 実装基板及び実装基板を用いたバルブソケット |

| JP2002329722A (ja) * | 2001-04-27 | 2002-11-15 | Nec Corp | 半導体装置及びその製造方法 |

| US6699792B1 (en) * | 2001-07-17 | 2004-03-02 | Advanced Micro Devices, Inc. | Polymer spacers for creating small geometry space and method of manufacture thereof |

| US6887780B2 (en) * | 2001-08-31 | 2005-05-03 | Intel Corporation | Concentration graded carbon doped oxide |

| JP3913638B2 (ja) * | 2001-09-03 | 2007-05-09 | 東京エレクトロン株式会社 | 熱処理方法及び熱処理装置 |

| JP2003092349A (ja) * | 2001-09-18 | 2003-03-28 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP4063619B2 (ja) * | 2002-03-13 | 2008-03-19 | Necエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP3516446B2 (ja) | 2002-04-26 | 2004-04-05 | 東京応化工業株式会社 | ホトレジスト剥離方法 |

| US7071112B2 (en) * | 2002-10-21 | 2006-07-04 | Applied Materials, Inc. | BARC shaping for improved fabrication of dual damascene integrated circuit features |

| US6867126B1 (en) * | 2002-11-07 | 2005-03-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method to increase cracking threshold for low-k materials |

| US20040152295A1 (en) * | 2003-02-03 | 2004-08-05 | International Business Machines Corporation | Sacrificial metal liner for copper |

| US7279410B1 (en) | 2003-03-05 | 2007-10-09 | Advanced Micro Devices, Inc. | Method for forming inlaid structures for IC interconnections |

| US8137764B2 (en) * | 2003-05-29 | 2012-03-20 | Air Products And Chemicals, Inc. | Mechanical enhancer additives for low dielectric films |

| US6767827B1 (en) | 2003-06-11 | 2004-07-27 | Advanced Micro Devices, Inc. | Method for forming dual inlaid structures for IC interconnections |

| US6919636B1 (en) | 2003-07-31 | 2005-07-19 | Advanced Micro Devices, Inc. | Interconnects with a dielectric sealant layer |

| TWI285938B (en) * | 2003-08-28 | 2007-08-21 | Fujitsu Ltd | Semiconductor device |

| JP4282493B2 (ja) * | 2004-01-15 | 2009-06-24 | 株式会社東芝 | 膜形成方法及び基板処理装置 |

| TW200605220A (en) * | 2004-06-21 | 2006-02-01 | Hitachi Chemical Co Ltd | Organic siloxane film, semiconductor device using same, flat panel display and raw material liquid |

| JP4854938B2 (ja) | 2004-07-06 | 2012-01-18 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US7202564B2 (en) * | 2005-02-16 | 2007-04-10 | International Business Machines Corporation | Advanced low dielectric constant organosilicon plasma chemical vapor deposition films |

| US7332428B2 (en) * | 2005-02-28 | 2008-02-19 | Infineon Technologies Ag | Metal interconnect structure and method |

| US7214612B2 (en) * | 2005-08-31 | 2007-05-08 | United Microelectronics Corp. | Dual damascene structure and fabrication thereof |

| US7410899B2 (en) * | 2005-09-20 | 2008-08-12 | Enthone, Inc. | Defectivity and process control of electroless deposition in microelectronics applications |

| JP5154009B2 (ja) * | 2005-10-21 | 2013-02-27 | 株式会社ジャパンディスプレイイースト | 有機シロキサン系絶縁膜の製造方法、及び、この製造方法で製造した有機シロキサン系絶縁膜を層間絶縁として用いた液晶表示装置の製造方法 |

| JP5168142B2 (ja) * | 2006-05-17 | 2013-03-21 | 日本電気株式会社 | 半導体装置 |

| US8637396B2 (en) * | 2008-12-01 | 2014-01-28 | Air Products And Chemicals, Inc. | Dielectric barrier deposition using oxygen containing precursor |

| EP2306506B1 (en) * | 2009-10-01 | 2013-07-31 | ams AG | Method of producing a semiconductor device having a through-wafer interconnect |

| JP2013020530A (ja) * | 2011-07-13 | 2013-01-31 | Dainippon Printing Co Ltd | タッチセンサパネル部材、タッチセンサパネル部材を備えた表示装置、及びタッチセンサパネル部材の製造方法 |

| US10319630B2 (en) * | 2012-09-27 | 2019-06-11 | Stmicroelectronics, Inc. | Encapsulated damascene interconnect structure for integrated circuits |

| US8980740B2 (en) | 2013-03-06 | 2015-03-17 | Globalfoundries Inc. | Barrier layer conformality in copper interconnects |

| KR102756671B1 (ko) * | 2019-02-21 | 2025-01-17 | 삼성디스플레이 주식회사 | 감광성 수지 조성물, 이를 이용한 표시 장치 및 표시 장치의 제조 방법 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5407529A (en) * | 1992-03-04 | 1995-04-18 | Nec Corporation | Method for manufacturing semiconductor device |

| KR100361043B1 (ko) * | 1993-12-27 | 2003-04-10 | 가와사키 마이크로 엘렉트로닉스 가부시키가이샤 | 반도체장치의절연막및절연막형성용도포액및절연막의제조방법 |

| US6326318B1 (en) * | 1995-09-14 | 2001-12-04 | Sanyo Electric Co., Ltd. | Process for producing semiconductor devices including an insulating layer with an impurity |

| US5989998A (en) * | 1996-08-29 | 1999-11-23 | Matsushita Electric Industrial Co., Ltd. | Method of forming interlayer insulating film |

| JP3726226B2 (ja) | 1998-02-05 | 2005-12-14 | 日本エー・エス・エム株式会社 | 絶縁膜及びその製造方法 |

| US6054379A (en) * | 1998-02-11 | 2000-04-25 | Applied Materials, Inc. | Method of depositing a low k dielectric with organo silane |

| US6068884A (en) * | 1998-04-28 | 2000-05-30 | Silcon Valley Group Thermal Systems, Llc | Method of making low κ dielectric inorganic/organic hybrid films |

| US6383951B1 (en) * | 1998-09-03 | 2002-05-07 | Micron Technology, Inc. | Low dielectric constant material for integrated circuit fabrication |

| US6255232B1 (en) * | 1999-02-11 | 2001-07-03 | Taiwan Semiconductor Manufacturing Company | Method for forming low dielectric constant spin-on-polymer (SOP) dielectric layer |

| US6312793B1 (en) * | 1999-05-26 | 2001-11-06 | International Business Machines Corporation | Multiphase low dielectric constant material |

| US6225238B1 (en) * | 1999-06-07 | 2001-05-01 | Allied Signal Inc | Low dielectric constant polyorganosilicon coatings generated from polycarbosilanes |

| EP1077479A1 (en) * | 1999-08-17 | 2001-02-21 | Applied Materials, Inc. | Post-deposition treatment to enchance properties of Si-O-C low K film |

| US6365528B1 (en) * | 2000-06-07 | 2002-04-02 | Lsi Logic Corporation | Low temperature process for forming a low dielectric constant fluorine and carbon-containing silicon oxide dielectric-material characterized by improved resistance to oxidation and good gap-filling capabilities |

-

2000

- 2000-01-18 JP JP2000013895A patent/JP3615979B2/ja not_active Expired - Fee Related

-

2001

- 2001-01-17 TW TW090101031A patent/TW513763B/zh not_active IP Right Cessation

- 2001-01-17 US US09/760,777 patent/US6358838B2/en not_active Expired - Lifetime

- 2001-01-18 KR KR1020010002929A patent/KR100689917B1/ko not_active Expired - Fee Related

-

2002

- 2002-01-18 US US10/050,859 patent/US6680541B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6358838B2 (en) | 2002-03-19 |

| KR100689917B1 (ko) | 2007-03-09 |

| KR20010076349A (ko) | 2001-08-11 |

| JP2001203200A (ja) | 2001-07-27 |

| TW513763B (en) | 2002-12-11 |

| US20020105085A1 (en) | 2002-08-08 |

| US6680541B2 (en) | 2004-01-20 |

| US20010009295A1 (en) | 2001-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3615979B2 (ja) | 半導体装置及びその製造方法 | |

| TW432476B (en) | A silicon carbide deposition for use as a barrier layer and an etch stop | |

| US7763979B2 (en) | Organic insulating film, manufacturing method thereof, semiconductor device using such organic insulating film and manufacturing method thereof | |

| JP4090740B2 (ja) | 集積回路の作製方法および集積回路 | |

| KR100696033B1 (ko) | 반도체 기판 프로세싱 방법 | |

| US20030089992A1 (en) | Silicon carbide deposition for use as a barrier layer and an etch stop | |

| JP4068072B2 (ja) | 半導体装置及びその製造方法 | |

| WO2000054329A1 (en) | Semiconductor device and production method therefor | |

| US7960279B2 (en) | Semiconductor device and manufacturing method therefor | |

| US20030001278A1 (en) | Method for manufacturing a semiconductor device and a semiconductor device | |

| JP5174435B2 (ja) | ウェットエッチングアンダカットを最小にし且つ超低k(k<2.5)誘電体をポアシーリングする方法 | |

| JP2010267971A (ja) | 窒素含有前駆物質を用いる誘電体バリアの堆積 | |

| CN1186814C (zh) | 扩散阻挡层和带扩散阻挡层的半导体器件及其制造方法 | |

| JP3768480B2 (ja) | 半導体装置及びその製造方法 | |

| US6905909B2 (en) | Ultra low dielectric constant thin film | |

| CN1881577B (zh) | 半导体器件及其制造方法 | |

| JP3184177B2 (ja) | 層間絶縁膜の形成方法、半導体製造装置、及び半導体装置 | |

| JP2006024668A (ja) | 半導体装置の製造方法 | |

| JP4882893B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040114 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040114 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20040309 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041005 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20041012 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20041102 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071112 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081112 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091112 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101112 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111112 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121112 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131112 Year of fee payment: 9 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |